#### Universidade Estadual de Campinas Instituto de Computação

### Rafael Cardoso Fernandes Sousa

### Convolution Tensor Slicing Optimization for Multicore NPUs

Otimização do Particionamento de Tensores para Convolução em NPUs Multicore

#### Rafael Cardoso Fernandes Sousa

### Convolution Tensor Slicing Optimization for Multicore NPUs

### Otimização do Particionamento de Tensores para Convolução em NPUs Multicore

Tese apresentada ao Instituto de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Doutor em Ciência da Computação.

Thesis presented to the Institute of Computing of the University of Campinas in partial fulfillment of the requirements for the degree of Doctor in Computer Science.

Supervisor/Orientador: Prof. Dr. Guido Costa Souza de Araújo Co-supervisor/Coorientador: Dr. Marcio Machado Pereira

Este exemplar corresponde à versão final da Tese defendida por Rafael Cardoso Fernandes Sousa e orientada pelo Prof. Dr. Guido Costa Souza de Araújo.

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Silvania Renata de Jesus Ribeiro - CRB 8/6592

Sousa, Rafael Cardoso Fernandes, 1988-

So85c

Convolution tensor slicing optimization for multicore NPUs / Rafael Cardoso Fernandes Sousa. – Campinas, SP: [s.n.], 2023.

Orientador: Guido Costa Souza de Araújo. Coorientador: Marcio Machado Pereira.

Tese (doutorado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Compiladores (Computadores). 2. Aprendizado de máquina. 3. Programação paralela (Computação). 4. Redes neurais convolucionais. I. Araújo, Guido Costa Souza de, 1962-. II. Pereira, Marcio Machado, 1959-. III. Universidade Estadual de Campinas. Instituto de Computação. IV. Título.

#### Informações Complementares

Título em outro idioma: Otimização do particionamento de tensores para convolução em

NPUs multicore

#### Palavras-chave em inglês:

Compilers (Eletronic computers)

Machine learning

Parallel programming (Computer science)

Convolutional neural networks

**Área de concentração:** Ciência da Computação **Titulação:** Doutor em Ciência da Computação

Banca examinadora:

Guido Costa Souza de Araújo [Orientador]

Márcio Bastos Castro

Alfredo Goldman Vel Lejbman

Hervé Cédric Yviquel Lucas Francisco Wanner

Data de defesa: 24-11-2023

Programa de Pós-Graduação: Ciência da Computação

Identificação e informações acadêmicas do(a) aluno(a)

- ORCID do autor: https://orcid.org/0000-0002-2673-6601

- Currículo Lattes do autor: http://lattes.cnpq.br/1581280350850662

#### Universidade Estadual de Campinas Instituto de Computação

#### Rafael Cardoso Fernandes Sousa

### Convolution Tensor Slicing Optimization for Multicore NPUs

### Otimização do Particionamento de Tensores para Convolução em NPUs Multicore

#### Banca Examinadora:

- Prof. Dr. Guido Costa Souza de Araújo IC/UNICAMP

- Prof. Dr. Márcio Bastos Castro INE/UFSC

- Prof. Dr. Alfredo Goldman vel Lejbman IME/USP

- Prof. Dr. Hervé Cedric Yviquel IC/UNICAMP

- Prof. Dr. Lucas Francisco Wanner IC/UNICAMP

A ata da defesa, assinada pelos membros da Comissão Examinadora, consta no SIGA/Sistema de Fluxo de Dissertação/Tese e na Secretaria do Programa da Unidade.

Campinas, 24 de novembro de 2023

# Acknowledgements

Firstly, I would like to express my deepest gratitude and thanks to my wife, Karina de Oliveira, who supported me throughout my entire Ph.D. process. She was my inspiration and a source of strength; thanks to her, I successfully defended my doctoral thesis. Additionally, a very special thanks to my family, who have also supported me since the beginning.

I would also like to express my sincere gratitude to my advisor, Prof. Guido Araujo, for his constant support, knowledge, and guidance throughout my Ph.D. process. Additionally, I extend my thanks to my co-supervisor, Prof. Marcio Pereira, whom I could consistently rely on for discussions about algorithms and research ideas at various stages.

Furthermore, special thanks to my friends from the Computer Systems Laboratory (LSC), especially to those with whom I had the opportunity to meet and become friends, and to those with whom I had the chance to work and collaborate on their projects. The moments spent in the lab were very important for my Ph.D. process.

I thank the members of my doctoral committee for their significant contributions to my defense, the postgraduate department (sec-pos) for their prompt support, and also the IT support staff of the Institute of Computing (IC).

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Finance Code 001, and by the Electronics and Telecommunications Research Institute (ETRI/South Korea). Additionally, I would like to thank LG Electronics (San Jose Lab) and SilicoNeuro/AiM Future for their contributions to the development of the project.

# Resumo

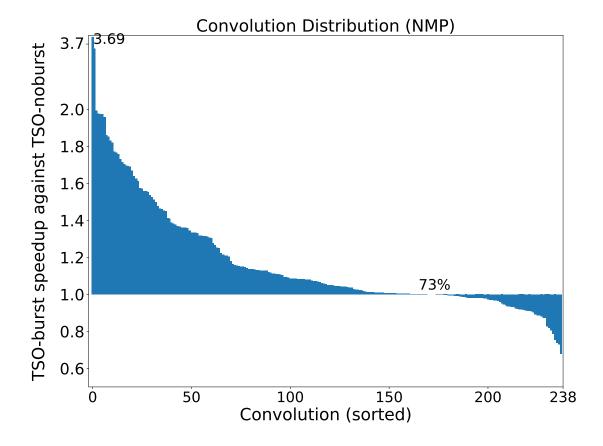

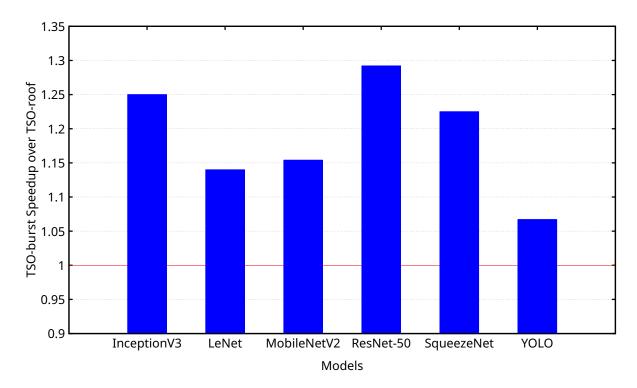

Embora a geração de código para modelos de Redes Neurais Convolucionais (CNNs) tenha sido extensivamente estudada, a realização de divisão eficiente de dados e paralelização para Unidades de Processamento Neural (NPUs) multicore e com memórias internas restritas ainda é um problema desafiador. Dado o tamanho dos tensores de entrada/saída das convoluções e o pequeno espaço das memórias internas das NPUs, minimizar as transações de memória ao mesmo tempo em que se maximiza o paralelismo e a utilização das unidades de multiplicação e acumulação (MAC) são fundamentais para qualquer solução eficaz. Esta tese propõe um passo de otimização no compilador TensorFlow XLA/LLVM para NPUs multicore, chamado Otimização de Divisão de Tensores (TSO), que: (a) maximiza o paralelismo das convoluções e o reuso de memória entre os núcleos das NPUs, (b) maximiza a reutilização de dados em cada núcleo NPU, selecionando a estratégia de agendamento apropriada que minimiza as transferências de dados entre as memórias no chip e a DRAM, e (c) reduz as transferências de dados entre a memória DRAM do hospedeiro (host) e as memórias internas da NPU ao empregar um modelo baseado em rajadas (bursts) de memória DRAM ao avaliar cada solução no espaço de busca, resultando na seleção daquela que oferece o melhor desempenho. Para avaliar a abordagem proposta, foram realizados experimentos usando o Processador Neuromórfico (NMP), uma NPU multicore contendo 32 núcleos RISC-V estendidos com novas instruções de CNN. Os resultados experimentais mostram que o TSO é capaz de identificar a melhor divisão de tensores que minimiza o tempo de execução para um conjunto de modelos de CNN. Acelerações de até 21,7% são observadas ao comparar a técnica baseada em rajada do TSO com uma abordagem de fatiamento de dados sem rajada. Entre as 236 convoluções avaliadas de 6 modelos CNN, o TSO com o modelo de rajadas supera a técnica sem rajadas em 73% delas, alcançando acelerações de até 3,69x. Grande parte da melhoria provém do fato de que o TSO com a técnica baseada em rajada habilitada otimiza o tempo de carga em até 24% e o tempo de armazenamento em até 79% quando comparado à abordagem sem rajadas na execução completa de todo o modelo CNN. Além disso, o TSO com a técnica baseada em rajada foi também comparado a uma abordagem existente que aplica um modelo de custo baseado em um modelo teórico chamado roofline [57], usado para estimar o desempenho das convoluções. Como resultado, o TSO supera todos os modelos CNN, com acelerações de até 29,2%. Para 84% das convoluções, o TSO alcança acelerações de até 5,19x. O algoritmo também foi adaptado para o framework de Aprendizado de Máquina Glow para validar a generalidade da abordagem TSO. O desempenho dos modelos foi medido tanto nos compiladores Glow quanto TensorFlow XLA/LLVM, revelando resultados similares.

### Abstract

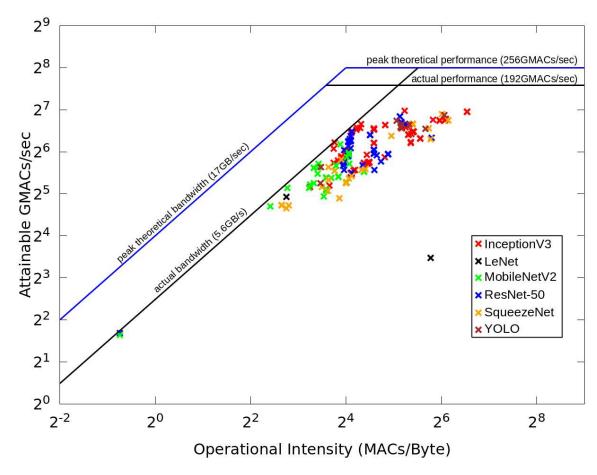

Although code generation for Convolution Neural Network (CNN) models has been extensively studied, performing efficient data slicing and parallelization for highly-constrained Multicore Neural Processor Units (NPUs) is still a challenging problem. Given the size of convolutions' input/output tensors and the small footprint of NPU on-chip memories, minimizing memory transactions while maximizing parallelism and MAC utilization are central to any effective solution. This thesis proposes a TensorFlow XLA/LLVM compiler optimization pass for Multicore NPUs, called Tensor Slicing Optimization (TSO), which: (a) maximizes convolution parallelism and memory usage across NPU cores, (b) maximizes data reuse on each NPU core by selecting the appropriate scheduling strategy that minimizes data transfers between the on-chip memories and DRAM, and (c) reduces data transfers between the host DRAM memory and the NPU on-chip memories by employing a DRAM memory burst modeling when evaluating every solution in the search space, which results in the selection of the one that provides the highest performance. To evaluate the proposed approach, experiments were performed using the NeuroMorphic Processor (NMP), a multicore NPU containing 32 RISC-V cores extended with novel CNN instructions. Experimental results show that TSO is capable of identifying the best tensor slicing that minimizes execution time for a set of CNN models. Speedups of up to 21.7\% result when comparing the TSO burst-based technique to a no-burst data slicing approach. Among the 236 evaluated convolutions from 6 different CNN models, TSO with the burst-modeling outperforms the no-burst approach in 73% of them, achieving speedups of up to 3.69x. Most of the improvement comes from the fact that TSO with the burst-based technique enabled optimizes the load time by up to 24\% and the store time by up to 79\% when compared to the no-burst approach in end-to-end execution of a CNN model. Furthermore, TSO with the burst-based technique was compared against an existing approach that applies a cost model based on a theoretical roofline model [57] to estimate the convolution performance, which resulted in TSO outperforming all CNN models with speedups of up to 29.2%. In this comparison, TSO shows improvements in 84% of the convolutions, achieving speedups of up to 5.19x. The TSO algorithm was also ported to the Glow Machine Learning framework to validate the generality of the TSO approach. The performance of the models was measured on both Glow and TensorFlow XLA/LLVM compilers, revealing similar results.

# List of Figures

| 2.1<br>2.2 | Memory access with different tile shapes                                                                                                                                                                                                                                                       | 21                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2.3        | 8 output tiles                                                                                                                                                                                                                                                                                 | <ul><li>22</li><li>23</li></ul> |

| 3.1        | Illustration of a Convolutional Neural Network (CNN) model comprising Convolution, AddBias, ReLU, MaxPooling, Flatten, Linear, and Softmax operations. The model processes an input image through a sequence of operations to classify it into a predefined set of classes                     | 25                              |

| 3.2        | A Convolution operation where the gray area in the input tensor is computed with a filter to generate the element highlighted in gray in the output tensor. The dashed boxes represent the computation performed by the                                                                        |                                 |

| 3.3        | same filter afterward                                                                                                                                                                                                                                                                          | <ul><li>26</li><li>29</li></ul> |

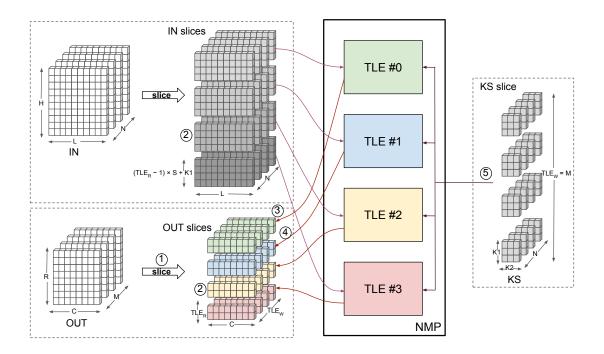

| 4.1<br>4.2 | NMP Architecture                                                                                                                                                                                                                                                                               | 32                              |

| 4.3        | operation                                                                                                                                                                                                                                                                                      | 34<br>35                        |

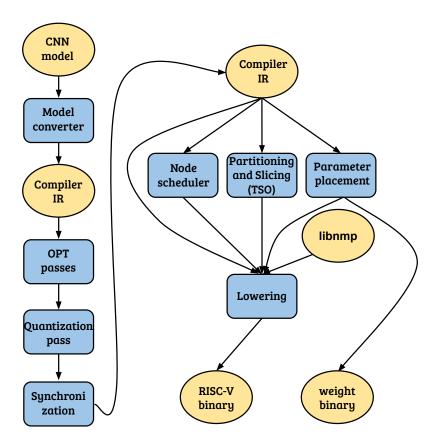

| 5.1        | Common compilation flow required for any ML compiler when targeting code to NMP                                                                                                                                                                                                                | 38                              |

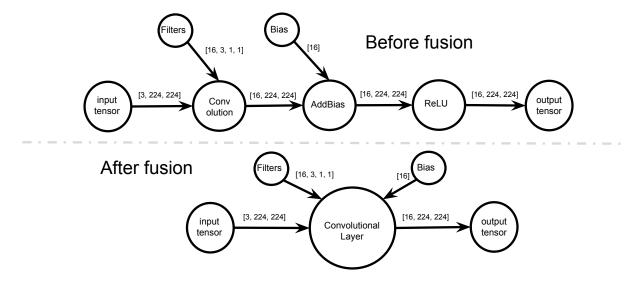

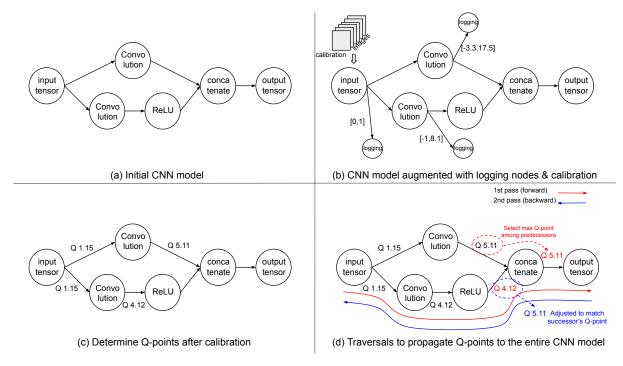

| 5.2<br>5.3 | Before and after applying the compiler pass – Loop/Operation Fusion Quantization pass applied to a CNN model with steps (a)-(d) explaining from the initial model, through the insertion of logging nodes and calibration until the application of the traversal passes (forward and backward) | 39                              |

|            | to propagate the Q-points                                                                                                                                                                                                                                                                      | 40                              |

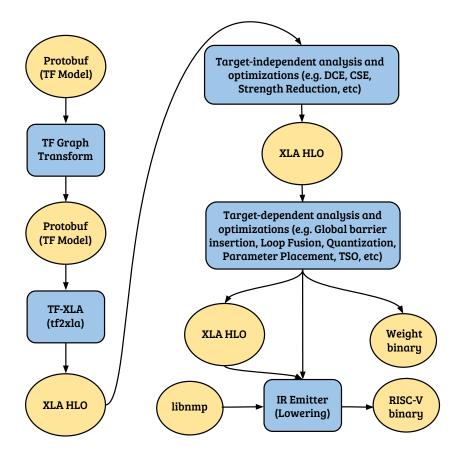

| 5.4        | Tensorflow XLA flow for NMP.                                                                                                                                                                                                                                                                   | 43                              |

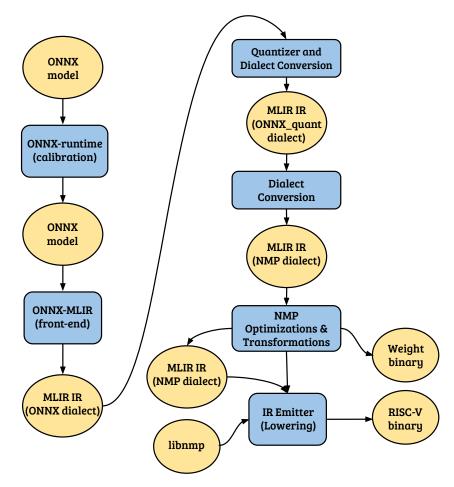

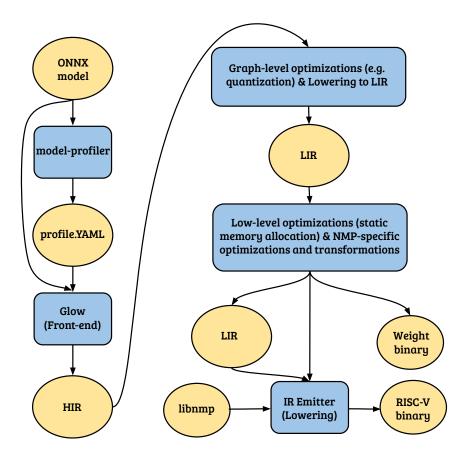

| 5.5<br>5.6 | ONNX-MLIR flow for NMP                                                                                                                                                                                                                                                                         | 44<br>46                        |

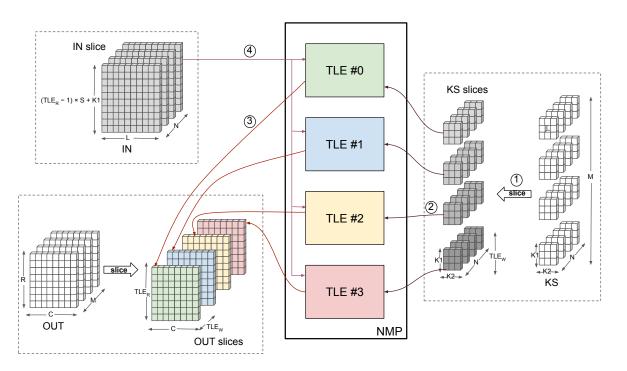

| 6.1        | The TLE KS slicing scheme divides the filters in the KS tensor into slices,                                                                                 |          |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | one for each TLE processor. A single IN slice is created and used by all                                                                                    |          |

|            | TLE processors                                                                                                                                              | 51       |

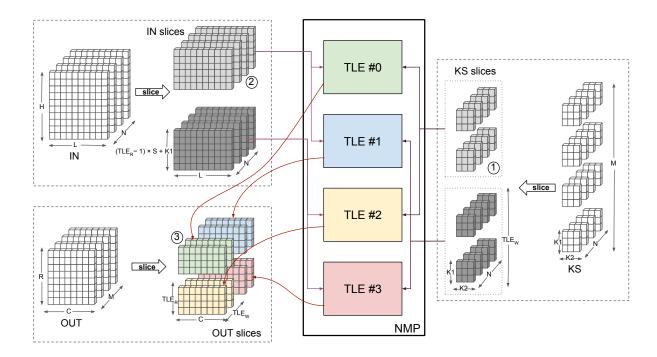

| 6.2        | The TLE KS&OUT slicing scheme divides both the IN tensor and the filters                                                                                    |          |

|            | in the KS tensor into slices. These slices are then combined to generate one                                                                                |          |

|            | OUT slice for each TLE processor                                                                                                                            | 52       |

| 6.3        | The TLE OUT slicing scheme divides the IN tensor into slices, one for each                                                                                  |          |

|            | TLE processor. A single KS slice with all filters is created and used by all                                                                                |          |

|            | TLE processors                                                                                                                                              | 53       |

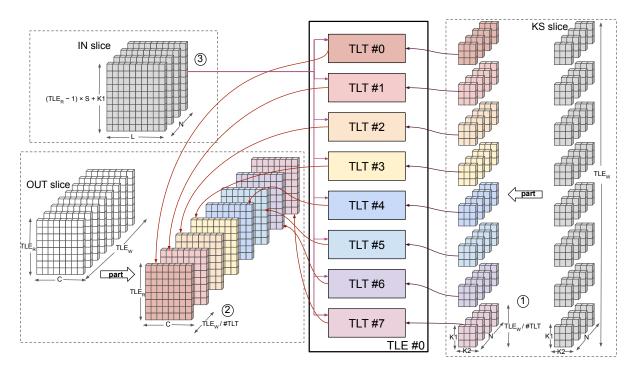

| 6.4        | The TLT Partitioning involves distributing the filters in a TLE slice across                                                                                |          |

|            | the TLTs of the TLE. Additionally, a single input slice is formed and is                                                                                    |          |

|            | necessary for all TLTs. To reduce load time, multicast loads are employed                                                                                   |          |

|            | when loading the input.                                                                                                                                     | 55       |

| 6.5        | Input Stationary.                                                                                                                                           | 57       |

| 6.6        | Output Stationary                                                                                                                                           | 58       |

| 6.7        | Weight Stationary.                                                                                                                                          | 59       |

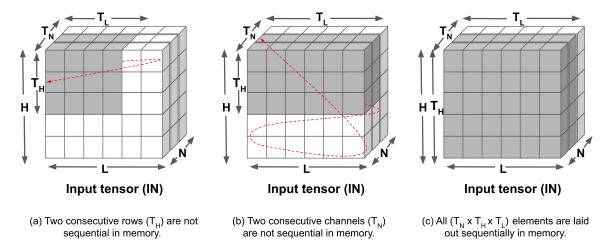

| 6.8        | The three presented scenarios (a) - (c) demonstrate how the input tiles $(TN^T)$ are presented in a second principle of the input the second $(TN)$ and the |          |

|            | $(IN^T)$ are represented in memory within the input tensor $(IN)$ , and the memory access stride applied to each of them (dashed red arrow). Note           |          |

|            | that the third scenario (c) has the elements of the $IN^T$ tile sequentially                                                                                |          |

|            | represented in memory                                                                                                                                       | 63       |

|            | represented in memory                                                                                                                                       | 05       |

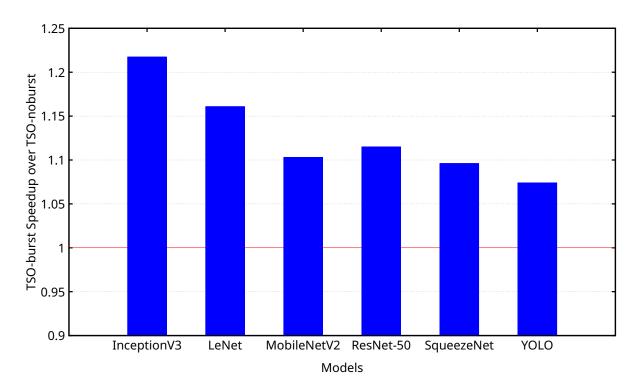

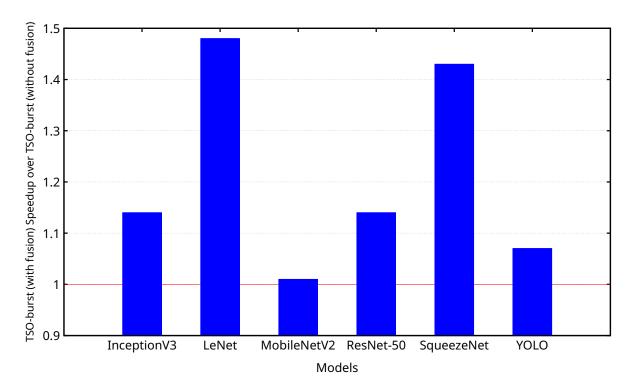

| 7.1        | TSO-burst speedup over TSO-noburst on end-to-end model execution time.                                                                                      |          |

|            | The baseline used in this experiment is the TSO-noburst                                                                                                     | 71       |

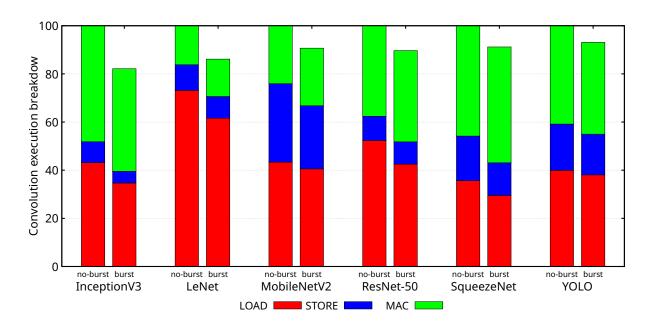

| 7.2        | Convolution execution breakdown with TSO-burst as a relative proportion                                                                                     |          |

|            | of TSO-noburst. The time taken to run the RISC-V instructions is not                                                                                        |          |

|            | included; instead, it is distributed into the LOAD, STORE, and MAC                                                                                          |          |

| <b>-</b> 0 | timings.                                                                                                                                                    | 72       |

| 7.3        | TSO-burst performance speedup against TSO-noburst for each of the 238                                                                                       |          |

|            | individual convolutions from the evaluated CNN models. The x-axis is sorted by speedup (y-axis). TSO-noburst performance is normalized to 1.                |          |

|            | The graphs also indicate the percentage of convolutions in which TSO-burst                                                                                  |          |

|            | outperforms TSO-noburst                                                                                                                                     | 74       |

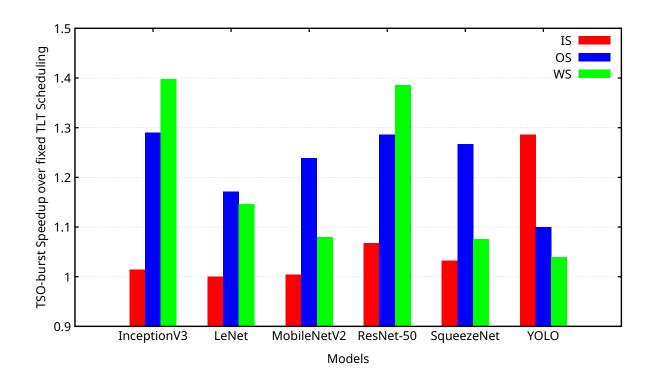

| 7.4        | The three TLT schedulings (IS, OS, and WS) remain fixed during code                                                                                         | 14       |

| 1.1        | generation. Although the TLT scheduling itself is fixed, TSO attempts to                                                                                    |          |

|            | find the best TLE scheme and optimal tiling for that fixed TLT scheduling.                                                                                  | 76       |

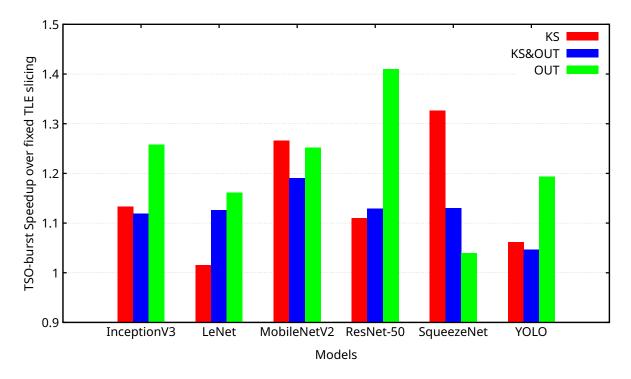

| 7.5        | The three TLE slicing schemes (KS, KS&OUT, and OUT) remain fixed                                                                                            | •        |

|            | during code generation. Although the TLE scheme itself is fixed, TSO                                                                                        |          |

|            | attempts to find the best TLT scheduling and optimal tiling for that fixed                                                                                  |          |

|            | TLE scheme.                                                                                                                                                 | 76       |

| 7.6        | TSO-burst speedup over TSO-roof (an adaption from [57]) on end-to-end                                                                                       |          |

|            | model execution time.                                                                                                                                       | 77       |

|            |                                                                                                                                                             |          |

| 8.1        | TSO-burst with loop fusion enabled compared to TSO-burst without loop                                                                                       | 0.0      |

| 0.0        | fusion enabled.                                                                                                                                             | 80       |

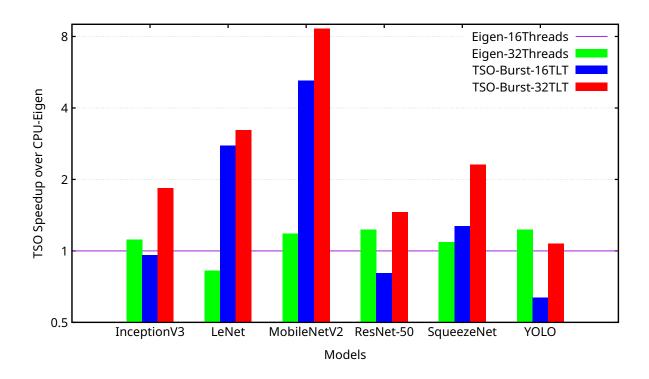

| 8.2        | NMP-TSO-burst vs CPU-Eigen performance speedup, where NMP was                                                                                               | 01       |

| Q 9        | experimented with 16 and 32 TLTs, and the CPU with 16 and 32 threads.                                                                                       | 81       |

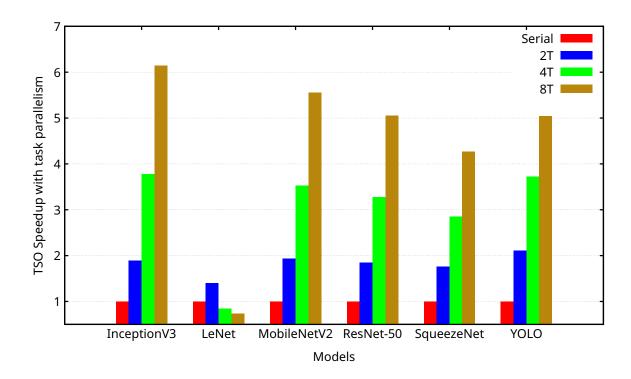

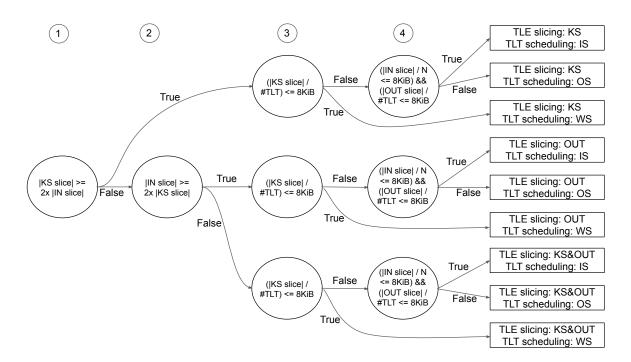

| 8.3<br>8.4 | Evaluating OpenMP parallelization of TSO solution space exploration Using a Decision Tree in TSO for TLE slicing and TLT scheduling                         | 83<br>84 |

| 0.4        | Using a Decision free in 150 for 1DE sheing and 1D1 scheduling                                                                                              | 04       |

| 8.5 | Roofline model for NMP architecture (TSO-burst) with actual execution |    |

|-----|-----------------------------------------------------------------------|----|

|     | time collected from running the CNN models on NMP                     | 85 |

# List of Tables

| 4.1 | Extended instructions supported by NMP                                                                                                                                                                                                       | 33 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 | Model accuracy on CPU (FP32) and NMP (16-bit fixed point). YOLO uses a different metric for accuracy; it measures the precision of the detection, which is 93.53% on NMP while on CPU is 93.03%.                                             | 66 |

| 7.2 | The selection performed by TSO-burst for TLE/TLT slicing, partitioning, scheduling, and tile size                                                                                                                                            | 68 |

| 7.3 | Model execution time of TSO-burst, TSO-noburst, fixed TLE slicing, and fixed TLT scheduling                                                                                                                                                  | 71 |

| 7.4 | Breakdown of how the execution time is distributed for LOAD, STORE, and MAC operations on NMP. In this experiment, the time taken to execute RISC-V instructions is assigned to the operation (e.g., LOAD) that requires those instructions. |    |

| 7.5 | Convolution execution time on each CNN model, along with the respective percentage of time allocated to running these convolutions (time share) for TSO-burst and TSO-noburst                                                                | 73 |

| 8.1 | Execution time of TSO with 16- and 32-TLTs, and CPU Eigen with 16- and 32-threads                                                                                                                                                            | 82 |

| 8.2 | Model accuracy on CPU (FP32) and NMP (16-bit fixed point) from Glow.                                                                                                                                                                         | 86 |

| 9.1 | The TSO algorithm compared to similar works that also seek to minimize DRAM memory access                                                                                                                                                    | 92 |

# List of Symbols and Acronyms

#### Tensor terms

IN Input tensor

N Input/Weight channels

H Input height

L Input width

KS Weight tensor

M Weight/Output channels

K1 Weight height

K2 Weight width

OUT Output tensor

R Output height

C Output width

#### Tile terms

$\mathtt{IN}^T$  Input tile

$T_N$  Input/Weight tile channels

$T_H$  Input tile height

$T_L$  Input tile width

$\mathsf{KS}^T$  Weight tile

$T_M$  Weight/Output tile channels

$\mathtt{OUT}^T$  Output tile

$T_R$  Output tile height

$T_C$  Output tile width

AI terms

AI Artificial Intelligence

CNN Convolutional Neural Network

Conv-Layer Convolutional Layer

FC-Layer Fully Connected Layer

ML Machine Learning

ReLU Rectified Linear Unit

#### Architectural terms

NPU Neural Processing Unit

CPU Central Processing Unit

GPU Graphics Processing Unit

FPGA Field Programmable Gate Array

NMP NeuroMorphic Processor

TLE NMP Tile

TLT NMP Tilelet

DME NMP Data Movement Engine

MB0 NMP MBLOB for input tile

MB1 NMP MBLOB for weight tile

MB2 NMP MBLOB for output tile

MAC Multiplier Accumulator

DRAM Dynamic Random-Access Memory

CAS Column Address Strobe

DDR Double Data Rate

#### Compiler terms

PM Pass Manager

AOT Ahead-Of-Time compilation

JIT Just-In-Time compilation

LLVM Low Level Virtual Machine

LLVM IR LLVM's Intermediate Representation

HLO High Level Operations

ONNX Open Neural Network Exchange

HIR High-level Intermediate Representation

LIR Low-level Intermediate Representation

MLIR Multi-Level Intermediate Representation

DCE Dead Code Elimination

CSE Common Subexpression Elimination

TSO terms

TSO Tensor Slicing Optimization

IS Input Stationary

OS Output Stationary

WS Weight Stationary

TLE KS TLE slicing using KS scheme

TLE KS&OUT TLE slicing using KS&OUT scheme

TLE OUT TLE slicing using OUT scheme

$TLE_R$  Output rows in a TLE slice

$TLE_W$  Filters in a TLE slice

$\alpha_{in}$  Number of reloads of the input tiles

$\alpha_{ks}$  Number of reloads of the weight tiles

$\alpha_{out}$  Number of stores of the output tiles

# Contents

| 1 | Introduction 1            |                                                                                                                                                                                                                                                                                          |                                                     |

|---|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 2 | The 2.1 2.2 2.3           | esis' Research Questions Q <sub>1</sub> : What is the Impact of Tiling on DRAM Burst Usage Q <sub>2</sub> : What is the Impact of Tiling on Scheduling                                                                                                                                   | 21                                                  |

| 3 | Back<br>3.1<br>3.2<br>3.3 | kground Convolutional Neural Network                                                                                                                                                                                                                                                     | 26                                                  |

| 4 | <b>Har</b> 4.1            | rdware Architecture The NMP Architecture                                                                                                                                                                                                                                                 | <b>31</b>                                           |

| 5 | The 5.1                   | Software Framework Code Generation for NMP 5.1.1 Fusion 5.1.2 Quantization 5.1.3 Synchronization 5.1.4 Tiling and Scheduling 5.1.5 RISC-V and Weight Binary Files Generation Compilers for Machine Learning 5.2.1 TF-XLA 5.2.2 ONNX-MLIR 5.2.3 Glow 5.2.4 Extending AI Compilers for NMP | 377<br>40<br>411<br>422<br>422<br>424<br>424<br>445 |

| 6 | 6.1<br>6.2                | TSO Algorithm                                                                                                                                                                                                                                                                            | 50<br>54<br>56                                      |

| 7 | Mai 7.1 7.2 7.3           | Experimental Results  Experimental Setup and Accuracy Analysis                                                                                                                                                                                                                           | 65<br>66<br>67                                      |

|    |                | 7.3.1 Execution Breakdown Analysis               | 72         |

|----|----------------|--------------------------------------------------|------------|

|    |                | 7.3.2 Convolution Time Analysis                  |            |

|    | 7.4            | TLT Scheduling and TLE Slicing Analysis          | 75         |

|    |                | 7.4.1 Fixed TLT Scheduling                       |            |

|    |                | 7.4.2 Fixed TLE Slicing                          |            |

|    | 7.5            | TSO-burst vs TSO-roof Tiling                     |            |

| 8  | $\mathbf{Add}$ | litional Experimental Results                    | <b>7</b> 9 |

|    | 8.1            | Impact of Loop Fusion on NMP                     | 79         |

|    | 8.2            | NMP-TSO vs CPU-Eigen                             | 80         |

|    | 8.3            | Speeding-up TSO Search Space Exploration         | 82         |

|    | 8.4            | Using a Decision Tree in the TSO Algorithm       | 83         |

|    | 8.5            | Plotting Actual NMP Run time on a Roofline Model | 84         |

|    | 8.6            | Evaluating TSO on Glow Compiler & ONNX-MLIR      | 85         |

| 9  | Rela           | ated Works                                       | 87         |

|    | 9.1            | Improving Memory Access and Data Reuse           | 87         |

|    |                | 9.1.1 On FPGAs                                   |            |

|    |                | 9.1.2 On NPUs                                    | 88         |

|    |                | 9.1.3 On CPUs                                    | 89         |

|    |                | 9.1.4 On GPUs                                    | 90         |

|    | 9.2            | Compiler-based Solutions                         | 90         |

|    | 9.3            | Other Optimization Techniques                    | 91         |

|    | 9.4            | Comparative Analysis of Relevant Works           | 92         |

| 10 | Futi           | ure Works and Conclusion                         | 93         |

|    | 10.1           | TSO Algorithm Conclusions                        | 93         |

|    |                | SConv: Inspired by TSO                           | 93         |

|    |                | Future Works with Potential to Improve TSO       | 94         |

| Bi | bliog          | graphy                                           | 97         |

# Chapter 1

# Introduction

Deep Learning using Convolutional Neural Network (CNN) has become a significant Machine Learning (ML) architecture model that considerably increases the accuracy of many modern AI applications. The steady increase in the adoption of CNNs is driven mostly by applications in the Computer Vision domain, where it addresses problems like Object Recognition [29, 75, 90], Object Detection [22, 72], and Video Classification [39, 73]. Other areas, like Speech Recognition and Natural Language Processing (NLP), have also benefited from the application of CNN models [5, 43].

The size and complexity of state-of-the-art CNNs have grown significantly, followed by its accuracy improvements. For instance, LeNet-5 [47], a model that recognizes handwritten digits, has less than 1 million parameters, while more complex models, like InceptionV3 [78], which classifies thousands of different object categories, has more than 23 million parameters. Such an increase in the model complexity and parameters size not only demands more computational power but also produces a significant increase in the data movement between host (off-chip) and the AI accelerator (on-chip) memories, thus considerably impacting energy-consumption and memory traffic [80].

It is well-known that convolution is the most expensive operation of a CNN [53,55,83], accounting for the largest share of a CNN execution. Given the size of its tensor inputs and the wide variety of configuration parameters (e.g., kernel size, stride, etc.), selecting the best data mapping which maximizes convolution parallelism while minimizing memory transactions is a key factor in the performance of any AI accelerator. This is particularly critical for multicore Neural Processing Units (NPUs), which have stringent (on-chip) memory constraints and need to achieve large inference throughput.

Convolution input tensors and weights must be partitioned into small tiles that fit into the NPU on-chip memories. This process is called *tiling*, and once the tiles are defined, these tiles are brought from (slow) external DRAM to (fast) on-chip memories, one pair of input and weight tiles at a time, to compute an output tile of the convolution operation. Depending on how the tile shapes and sizes are selected and the order they are brought to the on-chip memories, the convolution execution time can change drastically.

The tiling process is complex, involving a search space where millions to billions of solutions can be explored. The work presented in this thesis focuses on determining how to efficiently select a solution from this search space. In this sense, three research questions arise:  $(Q_1)$  What is the impact of tiling on DRAM burst usage;  $(Q_2)$  What is

the impact of tiling on scheduling; and  $(Q_3)$  What is the impact of tiling on parallelism. Regarding the first research question  $(Q_1)$ , this thesis explores techniques to efficiently select tile shapes that maximize memory burst usage. Bringing more data from a single memory access can considerably reduce data transfer time to DRAM. This concept is widely explored in GPUs [20,85] and can also be extended to work on multicore NPUs. The next research question  $(Q_2)$  addresses how to explore different scheduling strategies to maximize data reuse in the on-chip memories and reduce reloads in DRAM. Various scheduling strategies have been explored, especially for FPGAs and CPUs [52, 57, 61]. However, the tile sizes explored by these solutions are not always ideal, as fixed tile sizes are used, and maximizing them up to the capacity of the on-chip memories may lead to better performance. Finally, the last research question  $(Q_3)$  explores how to enhance data balance among multiple cores in an NPU to reduce the required memory footprint for each core. Many efforts have been explored in this regard (e.g., [13, 89]), but some may not effectively choose a proper solution due to the use of a unique slicing scheme (e.g., only slicing the filters among the cores), which may consequently lead to more data reload.

This thesis focuses on answering questions  $Q_1 - Q_3$  above and uses these answers to design an LLVM-based optimization for NPU architectures called *Tensor Slicing Optimization* (TSO) that can achieve the following goals:

- To minimize data transfer between the host and NPU's on-chip memory by properly answering Q<sub>1</sub>. In Section 6.5 we explain how a specialized tiling selection algorithm is used to leverage memory burst access. The goal is to choose tile sizes and shapes that maximize memory burst reuse;

- To maximize the reuse of on-chip memory tiles by properly answering Q<sub>2</sub>. In Section 6.4 we explain how a tiling scheduling algorithm is utilized to reuse as much as possible on-chips memory tiles to reduce the number of times a tile needs to be reloaded/stored from/to DRAM;

- To maximize the parallelization of convolution computations by properly answering Q<sub>3</sub>. In Sections 6.2 6.3 we explain an approach to evenly distribute the convolution data among the cores of an NPU, ensuring load balancing;

- By applying  $Q_1$  in TSO, a speedup of up to 21.7% is achieved. Regarding  $Q_2$  in TSO, a speedup of up to 39.8% is observed. Finally, concerning  $Q_3$ , TSO achieves a speedup of up to 41.0%. Additionally, when compared to an existent solution (roofline-based cost model [57]), TSO shows a speedup of up to 29.2%.

TSO should be capable of modeling, at compile-time, the memory utilization of the various NPU cores in the search for the best input/output tensor slicing that minimizes data transfers between the host and the NPU cores' memories. To evaluate this approach, experiments were performed using the LGE NeuroMorphic Processor (NMP), a multicore NPU containing 32 cores, and the TensorFlow XLA LLVM compiling toolchain.

The work in this thesis resulted in the following scientific publications. The first two publications are focused on NPU architectures and are the contributions of this thesis's

author. The other publications target CPU architectures and are joint work with other authors that reused a variation of the *Tensor Slicing Optimization (TSO)* proposed herein (Section 6.1).

- Sousa, R., Jung, B., Kwak, J., Frank, M. and Araujo, G. (2021, October). Efficient tensor slicing for multicore NPUs using memory burst modeling. In 2021 IEEE 33rd International Symposium on Computer Architecture and High-Performance Computing (SBAC-PAD) (pp. 84-93).

- Sousa, R., Pereira, M., Kwon, Y., Kim, T., Jung, N., Kim, C., Frank, M. and Araujo, G. (2023, January). Tensor Slicing and Optimization for Multicore NPUs. Journal of Parallel and Distributed Computing (JPDC), 175, 66-79.

- Ferrari, V., Sousa, R., Pereira, M., de Carvalho, J. P., Amaral, J. N. and Araujo, G. (2022, October). Improving Convolution via Cache Hierarchy Tiling and Reduced Packing. In Proceedings of the International Conference on Parallel Architectures and Compilation Techniques (PACT), pp. 538-539.

- Ferrari, V., Sousa, R., Pereira, M., de Carvalho, Moreira, J., J. P., Amaral, J. N. and Araujo, G. (2023, September). Advancing Direct Convolution using Convolution Slicing Optimization and ISA Extensions. ACM Transactions on Architecture and Code Optimization (TACO), 2023.

The TSO algorithm is well-suited for devices with small on-chip memories, as seen in the case of NMP, where careful management of memory access to DRAM is essential for achieving high performance. A variant of TSO can be applied for CPUs, as demonstrated in SConv [21]. However, for GPUs, where large global memory is available, TSO may not be as efficient as in scenarios like NMP. In the case of FPGAs, there is potential for improvement by implementing TSO, although we have not explored its application on those targets.

This thesis is organized as follows. In Chapter 2, the research questions explored in this thesis are detailed. In Chapter 3, a concise review of Convolutional Neural Networks (CNNs) and their main building blocks is provided. Additionally, an in-depth analysis of convolutions is presented, with a focus on tiling techniques for efficient computation. Moving on to Chapter 4, an overview of the NMP architecture is introduced, which serves as the target device for this thesis. Chapter 5 discusses the integration of the TSO into ML compilers, along with other necessary optimizations for adapting computation to the NMP architecture. The subsequent chapter, Chapter 6, introduces the TSO algorithm, the main contribution of this thesis. This includes slicing and partitioning techniques, and the application of a cost model based on memory burst accesses to determine the most suitable solution. In Chapter 7, the results of comparing the TSO algorithm with two data-volume-based solutions are presented, and a thorough analysis of the three research questions  $(Q_1 - Q_3)$  is provided. A more in-depth analysis to support the TSO effectiveness is presented in Chapter 8. Moving forward to Chapter 9, the main distinctions between TSO and previous research are highlighted. Finally, concluding the thesis in Chapter 10, findings are summarized, and potential future research topics are proposed.

# Chapter 2

# Thesis' Research Questions

This chapter delves into the research questions initially introduced in Section 1, thoroughly examining the advantages associated with the implementation of each one of them in the context of executing convolutions on multicore NPUs. For a deeper clarification of the research questions, refer to the three sections below, where a detailed discussion on the impact of tiling on DRAM burst usage, scheduling, and parallelism on the convolution execution time is presented. This thesis focuses on using the answers to these questions to design an effective compiler-based convolution-slicing optimization algorithm.

### 2.1 Q<sub>1</sub>: What is the Impact of Tiling on DRAM Burst Usage

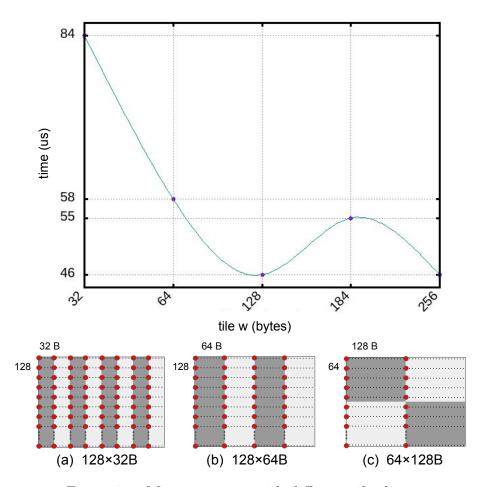

Consider Figure 2.1, which shows the time a Convolution takes when using tiles of different shapes. In that example, the input tensor is a single channel with  $128 \times 128$  16-bit fixed-point elements (row-major) computed over a single kernel of size  $1 \times 1$ . In the figure, tiles are represented as light/dark gray areas, and each red dot represents a (128B) memory burst access to the DRAM. Accessing time in a DRAM can be divided into two components: (a) CAS (Column Address Strobe) latency, which is the time taken to read the first byte of a memory burst from the DRAM Row Buffer; and (b) Access latency, which is the time taken to read the following bytes of the burst. For example, reading the first byte from a 128B burst of a typical DDR3 memory takes  $\sim 14$ ns, the same time it takes to read all the remaining 127 bytes of that burst. Depending on how data is tiled, memory bursts can enormously impact execution time. For example, in Figure 2.1 the Convolution can be divided into: (a) 8  $128 \times 32B$  tiles resulting in 1024 bursts (red dots) and an execution time of 84us; (b) 4  $128 \times 64B$  tiles corresponding to 512 bursts and a reduced 58us execution time; and (c)  $4.64 \times 128B$  tiles which require 256 bursts and 46us execution time, a 45% reduction in the convolution time when comparing to the tiling in (a). As shown in the graph of Figure 2.1, tiling (c)  $(4.64 \times 128B \text{ tiles})$  has the shortest memory access time at w = 128B. From that point on, as the width (w) of the tile continues to increase, memory access time worsens and then improves again at the next memory burst alignment (w = 256). In the area of code generation, the problem of ordering memory accesses so as to maximize burst data usage is known as memory access coalescing [31, 34, 65, 68]. Although memory access coalescing is a common problem in GPU code generation [20,85], it has not been extensively explored in multicore NPUs.

Figure 2.1: Memory access with different tile shapes.

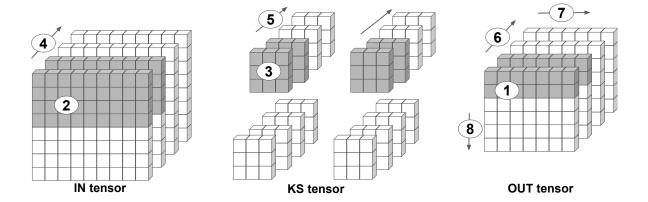

### 2.2 Q<sub>2</sub>: What is the Impact of Tiling on Scheduling

The tile size selection and the scheduling order in which those tiles are executed at runtime are critical factors in optimizing the convolution performance on multicore NPUs. Data movements can be significantly reduced by maximizing the sizes of the input, weight, and output tiles to match (or approximate) the maximum capacity of the NPU's on-chip memories. For instance, consider the execution flow presented in Figure 2.2, where, for simplicity, only a single NPU core is used. Initially, the first input tile (IN<sup>T</sup> #1) is loaded from DRAM into the NPU's on-chip memory (1) and remains stationary while being computed with a set of weight tiles, one at a time, to generate an output tile. Once the computation of the first weight tile  $(KS^T \# 1)$  (2) is finished, an output tile  $(OUT^T \# 1)$  is produced and then stored in the host memory (DRAM) (3). After that, another weight tile ( $KS^T \# 2$ ), which needs to be loaded from the DRAM 4, is placed in its corresponding NPU on-chip memory and then computed with the stationary input tile to generate a new output tile (OUT $^T$  #2), which is subsequently stored in the DRAM 5. After finishing the computation of the stationary input tile with all weight tiles, another input tile  $(IN^T)$ #2) (6) is loaded and kept stationary, and the same set of weight tiles is loaded again from DRAM, one by one, to generate new output tiles. To minimize the need for multiple reloads, maximizing the sizes of the tiles, particularly the one that remains stationary, is essential. In the context of the execution flow illustrated in Figure 2.2, a reduction

Figure 2.2: Scheduling of multiple tiles with the input tile kept stationary. In this example, 4 input tiles are computed with 2 weight tiles in order to generate 8 output tiles.

in the number of input tiles (e.g., from 4 to 2) would result in a proportional decrease in the number of reloads required for the weight tiles from the DRAM. However, it is important to consider that increasing the size of one tile may impact the sizes of the others, as these are interdependent. Hence, given the range of possible solutions that can be selected from a search space, the task of choosing the one that minimizes data transfer while maintaining high utilization of the NPU's cores becomes critical and challenging. This task is essential to produce optimized code.

### 2.3 $Q_3$ : What is the Impact of Tiling on Parallelism

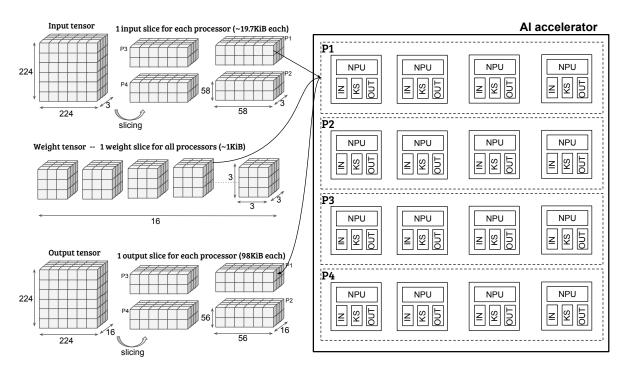

To accelerate the convolution computation on a multicore NPU, the partitioning of the convolution data (input, weight, and output tensors) must consider workload balancing for efficient mapping of the operation. Hence, it is essential to distribute the data evenly among the NPU cores to ensure a balanced data workload across all of them. Furthermore, another crucial aspect to consider involves minimizing data transfers between the DRAM and the NPU on-chip memories during this step, which can be achieved by prioritizing the partitioning of the largest tensor (in terms of size). To show how this can be achieved, consider the example illustrated in Figure 2.3, where the input tensor represents an RGB image with 3 channels of  $224 \times 224$  16-bit fixed-point elements. This input tensor undergoes computation with a weight tensor consisting of 16 filters, each with a size of  $3 \times 3 \times 3$  ( $C \times H \times W$ ). This computation results in an output tensor comprising 16 channels, all of the size  $224 \times 224$ . Assume that all tensors have the same data type and that the input tensor is zero-padded in order to generate an output tensor with matching spatial dimensions. In this example, the partitioning of the convolution data distributes a

Figure 2.3: The input, weight, and output tensors are partitioned to generate slices for the NPU's processors. Note that distinct slices from the input and output tensors are assigned to the NPU's processors. As for the weight tensor, a single slice is extracted and shared among all NPU's processors for computing.

slice of the input tensor and a slice of the weight tensor to each set of interconnected NPU cores, referred to as processors (e.g., P1) in Figure 2.3. These slices are then distributed internally between the NPU cores and then computed so that each NPU processor produces distinct slices of the output tensor. There are many configurations that can be explored in this partitioning step, for instance, the input tensor could be partitioned into four slices, and the weight tensor partitioned into only a single slice so as to have each slice of the input tensor assigned to a distinct processor and the single slice of the weight tensor assigned to all processors. Contrary to that, one could divide the weight tensor into four slices, and the input tensor into just one slice. Lastly, both the input and weight tensors could be divided, into two slices each. Note that at the end, each processor has to basically generate a distinct slice of the output tensor. Depending on how the input and weight tensors are sliced, either by prioritizing the division of the input or weight tensor into slices (or in some cases dividing both in the same proportion), the number of transactions from/to the DRAM can considerably decrease. For the example presented in Figure 2.3, the chosen configuration is the one where the input tensor is divided into one slice for each processor and only a single slice is extracted from the weight tensor and shared among all processors. As a result, a workload of approximately 118KiB is assigned to each processor. Alternatively, if the decision is made to divide the weight tensor instead, the workload would be around 686KiB (5.8x bigger). Although this particular case benefits from slicing the input tensor, it might not be the appropriate solution for other scenarios where the sizes of the convolution tensors may vary. As a result, choosing the correct slicing scheme becomes a crucial factor in minimizing data transfers.

# Chapter 3

# Background

This chapter provides an overview of the main layers that constitute a Convolutional Neural Network (CNN). Furthermore, it introduces the concept of tiling and explains its application in enabling the execution of convolutions with large memory requirements on devices with limited memory, such as NPUs.

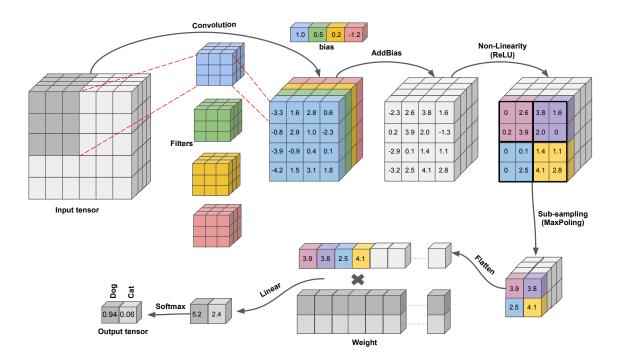

#### 3.1 Convolutional Neural Network

A Convolutional Neural Network (CNN) model can be visualized as a directed acyclic dataflow graph, where nodes represent specific CNN operations and edges represent n-dimensional arrays called tensors. This graph follows a sequential flow, with each node taking one or more input tensors and producing an output tensor. This output tensor becomes the input tensor for subsequent operations in the graph (as shown in Figure 3.1). The CNN model takes an initial input tensor, such as a 3-dimensional image, and applies a series of operations to generate a final output tensor representing the inference result. Typically, this output tensor contains a probability distribution that classifies the input image into predefined classes, such as "dog" or "cat".

The most common operations found in CNN models are illustrated in Figure 3.1. These operations include Convolution, AddBias, ReLU, MaxPooling, Flatten, Linear, and Softmax. Each of these operations plays a crucial role in a CNN model's overall functioning and structure.

The main objective of a convolution operation is to extract features from the input tensor by applying a set of pre-trained filters, also known as kernels. Convolution involves computing a dot product between the filters and local patches of the input tensor. Additionally, a bias term, represented as a 1-dimensional array, is added to the resulting tensor. The bias helps shift the output tensor's elements towards positive or negative values, ensuring that the network does not produce tensors with only zero elements. An activation function is normally applied to the tensor after the convolution and bias addition. The Rectified Linear Unit (ReLU) is commonly used as the activation function in CNN models, which sets all negative elements to zero, effectively deeming them dead or inactive for subsequent operations. Other activation functions, such as ReLU6, which sets a threshold between 0 and 6, can also be employed. By combining these three operations

Figure 3.1: Illustration of a Convolutional Neural Network (CNN) model comprising Convolution, AddBias, ReLU, MaxPooling, Flatten, Linear, and Softmax operations. The model processes an input image through a sequence of operations to classify it into a predefined set of classes.

- convolution, bias addition, and ReLU activation - a Convolutional Layer (referred to as Conv-Layer throughout this thesis) is formed, serving as a fundamental building block in a CNN model.

The Pooling Layer, as depicted by the MaxPool function in Figure 3.1, is responsible for reducing the spatial dimensions (height and width) of the input tensor through a process called sub-sampling. In this layer, a sliding window of a specified size (e.g.,  $2 \times 2$ ) moves over the input tensor, and the maximum element within each window is selected and written to the output tensor. This operation effectively reduces the size of the tensor while preserving the most significant features. A stride value determines the step size for shifting the window over the input tensor. In the case of the example in Figure 3.1, the stride is also  $2 \times 2$ , indicating that each window does not overlap with neighboring windows and skips a certain number of elements in between. By applying non-overlapping windows, the pooling layer achieves dimension reduction without redundancy. In addition to MaxPooling, another commonly used pooling operation in CNN models is AVGPooling. Unlike MaxPooling, AVGPooling calculates the average of the elements within each window, providing a different way to downsample the input tensor. Both MaxPooling and AVGPooling contribute to the overall feature extraction and spatial dimension reduction process within CNN models.

Before performing the computation of a Fully Connected Layer, represented by the Linear operation in Figure 3.1, the input tensor needs to be flattened from a 3-dimensional array to a 1-dimensional array. This flattening operation, also known as the Flatten Layer, reshapes the tensor without modifying the data layout in memory, where only

Figure 3.2: A Convolution operation where the gray area in the input tensor is computed with a filter to generate the element highlighted in gray in the output tensor. The dashed boxes represent the computation performed by the same filter afterward.

the view of the data is changed, and this is done at zero cost. Once the input tensor is flattened, the Linear operation multiplies the resulting 1-dimensional array by a pretrained 2-dimensional weight array. This multiplication process, along with an optional bias addition and activation function (e.g., ReLU), forms the fully connected layer (FC-Layer).

Finally, the Softmax operator is employed for image classification models to compute the probabilistic distribution for each neuron (element) in the output tensor. This distribution assigns a probability to each class label that the network is trained to classify. The neuron with the highest probability is typically considered the Top-1 classification. However, other Top-k values, such as Top-5, can also be extracted to better understand the network's predictions. For instance, in the InceptionV3 model, the resulting output tensor contains 1000 elements, with each element corresponding to the classification probability of a distinct class label.

### 3.2 Convolutional Layer (Conv-Layer)

Among all possible layers composing a CNN, the Conv-Layer usually accounts for more than 90% of the execution time [17] of a model and generates a large amount of data movements. This is especially critical on architectures with small on-chip memories, such as NPUs. Due to the burden imposed by this layer, this work aims to design specialized data tiling/scheduling algorithms for Conv-Layers, focusing on reducing memory transaction overhead. Moreover, since NPUs are used to perform *Inference* on mobile and embedded devices, this work is restricted to optimizing inference on pre-trained models.

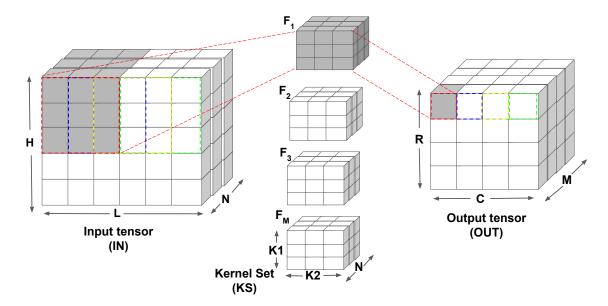

As shown in Figure 3.2, a Conv-Layer is composed of an input (IN) tensor with N input

feature maps of size H (height)  $\times L$  (width) each and a set of pre-trained weights. The weight set (KS) is a set of M multidimensional 3-D array kernels/filters of size  $N \times K1 \times K2$ . Each filter slides over the IN tensor performing a 3-D convolution with a stride factor of S. Note in the IN tensor of Figure 3.2 the presence of red, blue, yellow, and green dashed blocks. They represent the order in which the filter is passed over the IN tensor during the computation. Additionally, note that the dashed blocks are shifted only by a factor of 1, which indicates the stride of the convolution. After sliding a single filter over the entire input image (IN tensor), an  $R \times C$  output feature map is generated in the output (OUT) tensor. In the OUT tensor, it is possible to see the corresponding output to each dashed block of the IN tensor, represented with the same color. A set of M output feature maps results after applying all M filters in KS to the input (IN) tensor. The sequence of operations performed by the Conv-Layer, including the bias addition and activation function (ReLU), is shown in Equation 3.1.

$$\begin{aligned} \text{OUT}[m][r][c] &= \text{ReLU}(\text{Bias}[m] + \sum_{k=0}^{N-1} \sum_{i=0}^{K1-1} \sum_{j=0}^{K2-1} \text{IN}[k][S \times r + i][S \times c + j] \times \text{KS}[m][k][i][j]), \\ where, \begin{cases} 0 \leq m < M, \\ 0 \leq r < R, \\ 0 \leq c < C, \\ R = (H - K1 + S)/S, \\ C = (L - K2 + S)/S \end{cases} \end{aligned} \tag{3.1}$$

The number of operations required to compute a single element in the OUT tensor is  $2 \times N \times K1 \times K2$ , where 2 indicates both multiplication and accumulation. Note that the number of operations is proportional to the size of the filters in KS, which can grow considerably depending on the kernel size, impacting as well as the number of memory transactions required to read both the IN and KS tensors from DRAM. In order to compute the entire convolution, including all elements in the OUT tensor, a total of  $2 \times M \times R \times R$  $C \times N \times K1 \times K2$  operations are required. The computation of each element in the OUT tensor can be performed independently of the others, i.e., in parallel. Thus, in principle, one can schedule the computation of each filter in KS to be processed in parallel with respect to the others. The schedule can be done in various ways, but selecting the appropriate one can lead to better data reuse and better use of the computational resources available on the target device. The computation of the OUT tensor can be formulated using the Equation 3.1. The bias addition (Bias) and activation (ReLU) operations shown in Equation 3.1 are not as computationally expensive as the computation of the convolution itself. Both the bias addition and the activation function (ReLU) perform  $M \times R \times C$ operations. As for the bias addition, it involves element-wise additions, whereas the ReLU entails computing the maximum between zero and the resulting output tensor from the bias addition.

Two other concepts commonly used to define a convolution are batch and padding.

The batch determines the number of input images that are fed to a CNN model to be executed at once. A batch B results in an input tensor of size  $B \times N \times H \times L$ , which in turn produces an output tensor of size  $B \times M \times R \times C$ . In this work, the batch is defined as 1 for all tested CNN models. The other concept is padding, which is necessary when the spatial dimensions (R and C) of the OUT tensor are intended to have the same sizes as the spatial dimensions of the IN tensor (H and L). Padding is used in those cases to increase the H and L dimensions of each input feature map so that new rows and columns filled with zeros are appended to their borders. A special case where the filters have size  $N \times 1 \times 1$  and stride equal to 1 does not require padding, as the OUT tensor is already produced with the same spatial dimensions as the IN tensor. Padding is applicable for the other cases when either K1 or K2 values are bigger than 1. Consider, for example, a filter with a size of  $N \times 3 \times 3$ . In this case, each input feature map (H and L) in the IN tensor is expanded by adding 2 additional rows (one at the top and one at the bottom) and 2 additional columns (one at the left and one at the right). By employing this expansion, sliding the filters over the padded IN tensor results in an OUT tensor with the same feature map dimensions as the original IN tensor. Although zero-padding is the most common case when padding the input (IN) tensor, padding with other constants may also be applied.

### 3.3 Tiled Convolution

Convolutions in a CNN model typically have different kernel sizes and different numbers of input (M) and output (N) feature maps with distinct sizes and variable strides. For instance, the first convolution from the Inception-V3 model [78] has  $3 \times 299 \times 299$  elements in its IN tensor. Considering that this tensor's data type is a 16-bit fixed-point, the total size required to allocate it in memory becomes 524KiB, which is impractical when working with NPUs with constrained on-chip memories. Note that this 524KiB includes only the IN tensor. Hence, if we consider the OUT tensor and the filters in KS, this size would increase considerably more. To circumvent this problem, data tiling becomes a mandatory task when computing convolution.

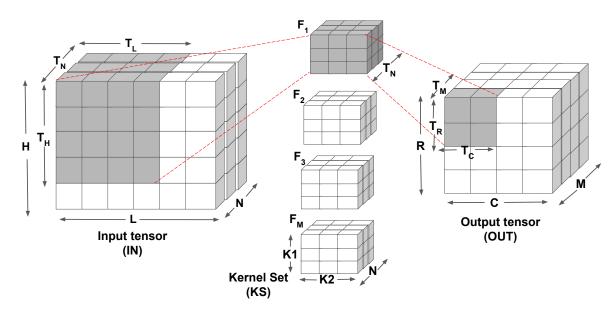

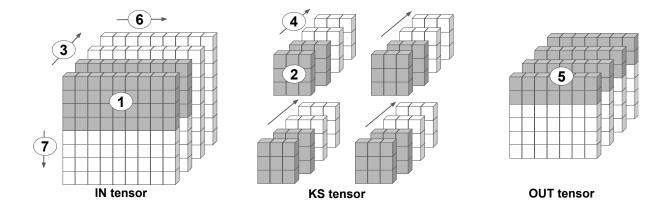

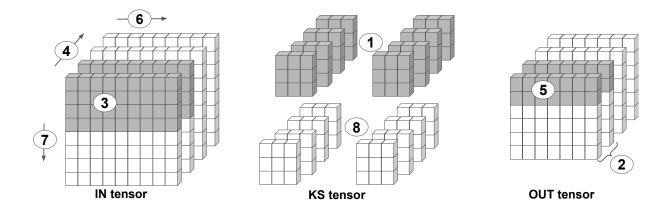

Data tiling of a convolution operation consists in partitioning its IN and OUT tensors into small tiles and dividing the filters in KS so that each IN<sup>T</sup>, OUT<sup>T</sup> and KS<sup>T</sup> tiles fit together at the same time in the NPU on-chip memories. Figure 3.3 shows how the IN and OUT tensors data are respectively divided into IN<sup>T</sup> =  $(T_N, T_H, T_L)$  tiles, and OUT<sup>T</sup> =  $(T_M, T_R, T_C)$  tiles. Notice that the dimensions  $T_H$  and  $T_L$  of the IN<sup>T</sup> can be computed using the dimensions  $T_R$  and  $T_C$  of the OUT<sup>T</sup> tensor through Equation 3.2.

$$T_H = (T_R - 1) \times S + K1$$

$T_L = (T_C - 1) \times S + K2$  (3.2)

, where K1, K2, and S are the kernel sizes and stride, respectively. Moreover, if the filters/kernels in KS do not fit in their respective NPU on-chip memories, KS is also partitioned into KS<sup>T</sup> =  $(T_M, T_N, K1, K2)$  tiles, where  $T_M$  is the number of filters and  $T_N$  the number of channels to be loaded from each filter. In this work, the full values of K1

Figure 3.3: A Convolution operation with tiling applied to it to allow its data to fit in memory-constrained devices. The tiles are formed as follows: (a)  $IN^T = (T_N, T_H, T_L)$ , (b)  $KS^T = (T_M, T_N, K1, K2)$ , and (c)  $OUT^T = (T_M, T_R, T_C)$ .

and K2 are used when defining the  $KS^T$  tile, but tiling could also be applied to these two terms.

As shown in Figure 3.3, data tiling extends beyond a single convolution component, such as the KS tensor, and encompasses all involved components, including the IN, KS, and OUT tensors. Hence, when applying tiling to one component (e.g., the KS tensor), it becomes crucial to consider the memory requirements of the other two components (IN and OUT tensors) as well. This ensures that all three (IN<sup>T</sup>, KS<sup>T</sup>, and OUT<sup>T</sup>) tiles can fit within their respective on-chip memories on the accelerator at the same time when computing an IN<sup>T</sup> tile with a KS<sup>T</sup> tile to generate an OUT<sup>T</sup>. Therefore, a coordinated approach is essential for data tiling, considering the memory constraints of all convolution components and the NPU's memory limitations, in order to optimize their storage and computation on the device (more details in Section 6.3).

When partitioning a convolution for execution on an NPU, it is possible to explore different tile shapes. However, it is essential to consider certain constraints. Firstly, increasing the number of filters  $(T_M)$  in  $KS^T$  will also increase the number of output feature maps in  $T_M$ , by the same amount, as  $T_M$  is also defined in  $OUT^T$  tile. Secondly, increasing the number of filter channels  $(T_N)$  in  $KS^T$  will result in a corresponding increase in the number of channels in the  $IN^T$  tile, as both the  $IN^T$  and  $KS^T$  tiles are determined based on  $T_N$ . Finally, increasing the spatial dimensions  $(T_R \text{ and } T_C)$  of the output feature maps in the  $OUT^T$  tile will lead to an increase in  $T_H$  and  $T_L$  in the  $IN^T$  tile, as they are derived through a linear function of  $T_R$  and  $T_C$  (as depicted in Equation 3.2).

Each tile shape leads to different memory accesses and usage of the resources available on the NPU. Besides that, different scheduling strategies can be explored, each one with a specific memory access pattern that leads to different data reuse. The way computation is mapped can considerably affect the data movement between host and NPU memories leading to poor data re-use. Moreover, if not properly done, tiling can also result in poor utilization of the NPU's Multiplier Accumulator (MAC) units, which can become idle during the computation (more details in Section 6.4).

# Chapter 4

# Hardware Architecture

Although CPUs have been proposed to accelerate CNNs by relying on multicore parallelism and SIMD instructions [48,82], the number and complexity of the layers in modern CNN models make it very difficult to run the entire network on CPUs. To improve inference throughput, (fast) GPU solutions have been proposed to process a large amount of data [16,76]. Field Programmable Gate Arrays (FPGAs), on the other hand, have been extensively used as an alternative to this problem as they offer good performance and reconfigurability [10,14,23,64,71]. Nevertheless, these architectures are not efficient power-performance solutions for critical edge applications, like surveillance cameras and cellphone face recognition, etc., which have stringent execution and power consumption constraints. Several types of accelerators have been proposed to accelerate CNNs in a power-efficient way. Specialized ASICs [9], Neural Processing Units (NPUs) [41,54], and Tensor Processing Units (TPUs) [36] are some examples.

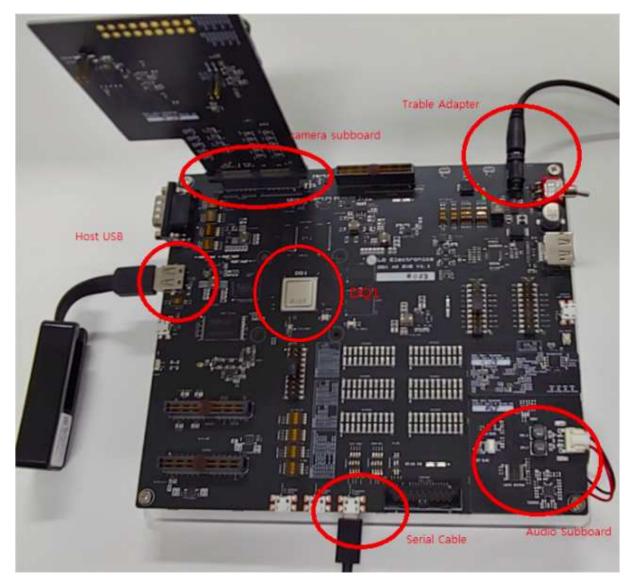

This thesis uses the NeuroMorphic Processor (NMP) by LG Electronics (LGE) as a compiling target. The NMP is an AI accelerator designed primarily for integration into embedded systems, such as televisions and refrigerators. Its architecture was specifically tailored for the execution of CNN models, including tasks like image classification and object detection, thanks to its well-suited computing units and on-chip memories. The key idea behind the NMP architecture is to use RISC-V ISA Extensions to design relevant CNN instructions like Conv-Layers, fully connected layers, pooling layers, element-wise operations, etc.

#### 4.1 The NMP Architecture

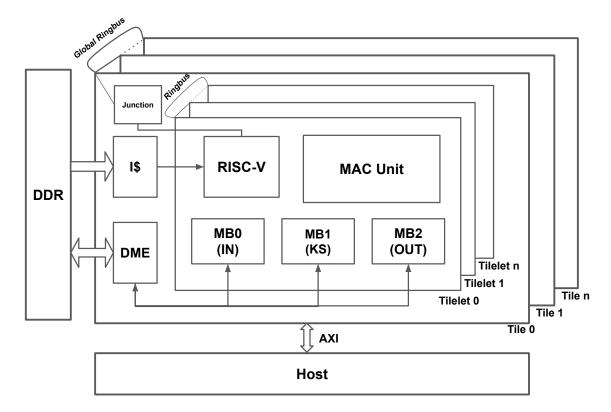

The NMP architecture (Figure 4.1) is a multicore NPU that contains an ARM57 processor that works as a host for a set of multiple Tile (TLE) processors, containing each a set of Tilelet (TLT) cores. Each TLT has one RISC-V core and three on-chip (scratchpad) memories, namely MB0, MB1, and MB2, which respectively store the  $IN^T$ ,  $KS^T$ , and  $OUT^T$  tiles from the IN, KS, and OUT tensors. Besides that, each TLT is also equipped with a MAC acceleration unit to execute CNN operations. The MAC unit execution is triggered by the RISC-V core and is capable of executing 8- and 16-bit fixed-point operations with the memory layout organized in NCHW format. The datapath between the MAC unit

Figure 4.1: NMP Architecture.

and TLT on-chip memories (MBLOBs - MB0, MB1, and MB2) is 128-bit wide, which means that for 8-bit fixed-point, up to 16 MAC operations are executed per cycle, while for 16-bit fixed-point, up to 8 MAC operations per cycle may be executed.

The data transfers between NMP and host happen through a Data Movement Engine (DME) module, as shown in Figure 4.1, with one DME module for each TLE. The DME module slices the memory requests into transactions of up to 128 bytes. The host communicates with the NMP through an AXI interface, and data can be shared between TLTs of different TLEs by using a Global Ringbus. The TLTs of a TLE also have their own Ringbus to communicate data between them. The instructions executed by the RISC-V cores are fetched from the host memory and stored into a cache instruction shared between the TLTs of the same TLE.

To execute computations on the NeuroMorphic Processor (NMP), a CNN model needs to be compiled using an ML compiler like TF-XLA [3]. The compilation process generates two binary files: (1) a binary file containing RISC-V instructions and (2) a binary file containing the weights for both convolutional and fully connected layers (more details in Chapter 5). These files need to be loaded into specific memory addresses using the NMP device descriptor. Once the loading is complete, a system call is invoked to initiate the computation on NMP. The execution of the compiled model starts on the RISC-V cores of each TLT, with each TLT operating independently. Similar to GPUs, each TLT is identified by a unique ID, allowing them to determine the portion of data they are responsible for computing.

TLTs primarily use primitive RISC-V instructions for control flow, such as looping over tiled data. In addition to these instructions, the NMP architecture includes an *extended*

| Type of Instruction | Instructions   |

|---------------------|----------------|

| Data Movement       | nmp_load[3d]   |

|                     | nmp_store[3d]  |

| Layers              | nmp_activation |

|                     | nmp_conv2d     |

|                     | nmp_percept    |

|                     | nmp_pool       |

|                     | nmp_veop       |

| Synchronization     | nmp_wait       |

|                     | nmp_signal     |

Table 4.1: Extended instructions supported by NMP.

set of RISC-V instructions for (refer to Table 4.1): (a) Data movement: these instructions, such as  $nmp\_load$  and  $nmp\_load3d$ , are executed by the RISC-V core to load data from the DRAM to the TLT's on-chip memory. The Data Movement Engine (DME) handles the data transfer. To bring data back from each TLT's on-chip memory to the host DRAM, the RISC-V core executes the extended  $nmp\_store$  and  $nmp\_store3d$  instructions; (b) Layer computation: to perform computations on the Multiply-Accumulate (MAC) units, the RISC-V core invokes one of the following extended instructions:  $nmp\_activation$ ,  $nmp\_conv2d$ ,  $nmp\_percept$ ,  $nmp\_pool$ , and  $nmp\_veop$ ; and (c) Synchronization: two instructions,  $nmp\_wait$  and  $nmp\_signal$ , are used for synchronization.  $nmp\_wait$  represents a barrier that waits until a specific task is completed, such as a data load from the host memory. When the barrier is resolved, a signal is emitted from one RISC-V core to inform other participating RISC-V cores that the task has been completed. Overall, the extended RISC-V instructions in the NMP architecture enable data movement, layer computation, and synchronization to facilitate the execution of CNN computations efficiently.

Despite the independent execution of computations by each TLT within a single TLE, NMP introduces a special instruction called the multicast load. This instruction operates on a single TLT but enables all TLTs within the same TLE to load the same data from the DRAM simultaneously. To illustrate this, consider a scenario where all TLTs within a particular TLE process the same  $IN^T$  tile but compute with different  $KS^T$  tiles. Instead of loading the identical  $IN^T$  tile multiple times, one for each TLT in the TLE, a multicast load can be employed. This capability allows for concurrent processing of the  $IN^T$  tile by different filters in parallel, maximizing performance and throughput. It is important to note that TLTs from distinct TLEs cannot utilize the same multicast load to load the same data. In such cases, multiple multicast loads are required, with each TLE executing its own multicast load to ensure that the same data is loaded into all of its TLTs.

NMP provides three levels of hardware-based semaphores to facilitate synchronization among TLEs and TLTs. These semaphores support various synchronization operations, including: (a) Synchronizing computation within a TLT – after invoking the MAC unit to perform an operation (e.g.,  $nmp\_conv2d$  instruction), the RISC-V execution can be blocked until the MAC unit completes its task. This enables precise coordination between the RISC-V core and the MAC unit; (b) Synchronizing computation between TLTs of the

Figure 4.2: The NMP workflow where a step-by-step execution is shown for a CNN operation.

same TLE – during a multicast load, where all TLTs within a specific TLE load the same data from the DRAM, synchronization plays a crucial role. The semaphores ensure that all TLTs are blocked until their respective on-chip memories receive the data. This guarantees synchronized access to shared data within the TLE; and (c) Synchronizing computation between TLTs of different TLEs – in a multi-layer CNN model, performing proper synchronization among TLTs (of different TLEs) is required before initiating the computation of the next layer. This is because a TLT within a TLE may depend on the data generated by a TLT from a different TLE. To ensure correct sequencing, if a TLT completes its computation before other TLTs working on the same layer, it must be blocked from proceeding to the subsequent layer. This blocking mechanism ensures that the TLT waits until all relevant computations across TLEs are finished, maintaining the integrity of the computation flow within the model. Therefore, the availability of hardware-based semaphores in the NMP architecture enables efficient and reliable synchronization at different levels, ensuring correct execution order and data consistency within and across TLEs and TLTs.

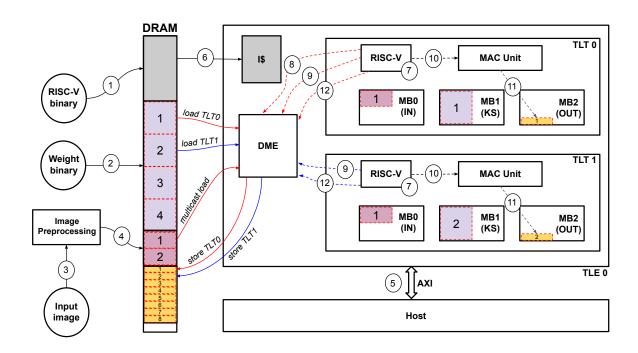

As stated before, the NMP workflow is similar to that of a GPU. To illustrate the NMP workflow, see Figure 4.2, which shows each step in a simplified NMP architecture with 1 TLE containing 2 TLTs (for simplicity). Initially, the host application loads both the RISC-V binary ① and the Weight binary ② files into the host memory (DRAM). The data in the Weight binary file constitutes multiple KS tensors of different operations besides the bias vector that are consumed by the Conv- and FC-Layers. In the sequence, the host application pre-processes the input image according to the range expected by the CNN model ③. As an example of pre-processing, there are models that expect the RGB channels to be within the range of [-1,1], while others expect them to be within the

Figure 4.3: Development board with an NMP DQ1-A0 chip integrated on it.