### UNIVERSIDADE ESTADUAL DE CAMPINAS Faculdade de Engenharia Elétrica e de Computação

### **Mateus Biancarde Castro**

Reconfigurable Sigma Delta Modulator for Analog-to-Digital Converters in Multi-Standard Wireless Receivers in 65-nm Process

Modulador Sigma Delta Reconfigurável para Conversor Analógico-Digital em Receptores Wireless Multi-Padrão em Processo de 65-nm

#### **Mateus Biancarde Castro**

### Reconfigurable Sigma Delta Modulator for Analog-to-Digital Converters in Multi-Standard Wireless Receivers in 65-nm Process

## Modulador Sigma Delta Reconfigurável para Conversor Analógico-Digital em Receptores Wireless Multi-Padrão em Processo de 65-nm

Dissertação apresentada à Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas como parte dos requisitos para a obtenção do título de Mestre em Engenharia Elétrica, na área de Eletrônica, Microeletrônica e Optoeletrônica.

Dissertation presented to the Faculty of Electrical and Computer Engineering of the University of Campinas in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the area of Microelectronics.

Supervisor/Corientador: Fduardo Rodrigues de Lima P

Co-supervisor/Coorientador: Eduardo Rodrigues de Lima, PhD

Este trabalho corresponde à versão final da Dissertação defendida por Mateus Biancarde Castro e orientada pelo Prof. Dr. Leandro Tiago Manêra.

### Ficha catalográfica Universidade Estadual de Campinas Biblioteca da Área de Engenharia e Arquitetura Rose Meire da Silva - CRB 8/5974

Castro, Mateus Biancarde, 1992-

C279r

Reconfigurable Sigma Delta modulator for analog-to-digital converters in multi-standard wireless receivers in 65-nm process / Mateus Biancarde Castro. - Campinas, SP: [s.n.], 2022.

Orientador: Leandro Tiago Manêra.

Coorientador: Eduardo Rodrigues de Lima.

Dissertação (mestrado) – Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Conversão análogo-digital. I. Manêra, Leandro Tiago, 1977-. II. Lima, Eduardo Rodrigues de, 1969-. III. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. IV. Título.

#### Informações Complementares

Título em outro idioma: Modulador Sigma Delta reconfigurável para conversor analógicodigital em receptores wireless multi-padrão em processo 65-nm

Palavras-chave em inglês: Analog to digital conversion

Área de concentração: Eletrônica, Microeletrônica e Optoeletrônica

Titulação: Mestre em Engenharia Elétrica

Banca examinadora:

Leandro Tiago Manêra [Orientador]

Fernando Rangel de Souza

Fabiano Fruett

**Data de defesa:** 11-11-2022

Programa de Pós-Graduação: Engenharia Elétrica

Identificação e informações acadêmicas do(a) aluno(a)

<sup>-</sup> ORCID do autor: https://orcid.org/0000-0002-7738-3690 - Currículo Lattes do autor: http://lattes.cnpq.br/5172485857569930

### COMISSÃO JULGADORA - DISSERTAÇÃO DE MESTRADO

Candidato: Mateus Biancarde Castro RA:228992

Data da Defesa: 11 de Novembro de 2022

**Título da Tese:** "Reconfigurable Sigma Delta Modulator for Analog-to-Digital Converters in Multi-Standard Wireless Receivers in 65-nm Process"

Prof. Dr. Leandro Tiago Manêra (Presidente)

Prof. Dr. Fernando Rangel de Sousa

Prof. Dr. Fabiano Fruett

A ata de defesa, com as respectivas assinaturas dos membros da Comissão Julgadora, encontra-se no SIGA (Sistema de Fluxo de Dissertação/Tese) e na Secretaria de Pós-Graduação da Faculdade de Engenharia Elétrica e de Computação.

# Agradecimentos

Aos meus pais por todo o apoio sempre.

Ao meu irmão por todo o suporte.

Ao Prof. Leandro Manêra por toda a paciência e respaldo durante todo o processo.

A Eduardo Lima pela oportunidade de trabalhar em um projeto de alto nível com um grupo altamente motivado e qualificado.

Aos amigos do LSERF por toda a assistência, em especial Agord e Rafael.

Aos amigos do Instituto Eldorado por todas as dicussões técnicas, criticas e apoio em todas as etapas do desenvolvimento do projeto, em especial Fábio e Leonardo.

# Resumo

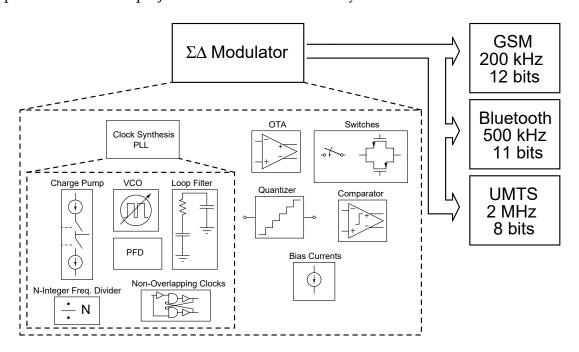

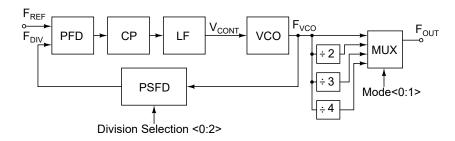

Com o crescente número de padrões de comunicação sem fio nas últimas décadas, reconfigurabilidade de transceptores se torna um recurso interessante e benéfico em dispositivos embarcados System-on-Chip (SoC) que necessitam de uma grande variedade de padrões de Radiofrequência (RF) para processamento de sinais. Com o objetivo de desenvolver um transceptor totalmente reconfigurável, que é capaz de operar em vários padrões com consumo de potência adequado, a reconfigurabilidade de blocos individuais do transceptor se torna um assunto atraente para pesquisa. Especificamente no caso de Conversores Analógico-Digitais (ADCs), a topologia de ADC ΣΔ mostra algumas vantagens com relação a reconfigurabilidade com o objetivo de redução no consumo de potência na faixa de baixas frequências de operação. Este tipo de topologia permite modificações como a redução da frequência de amostragem, a ordem da formatação de ruído e o número de bits do quantizador de saída, tudo em troca da resolução e consumo de potência. O principal objetivo deste trabalho é apresentar o projeto completo de um ADC reconfigurável que opere na faixa de baixas frequências de comunicações móveis sem fio, especificamente GSM (banda de 200 kHz) e UMTS (banda de 2 MHz), e adicionalmente fornecer a operação para Bluetooth com banda de 500 kHz, juntamente com o projeto de um sintetizador de clock baseado em Phase Locked Loop (PLL) para a síntese das frequências de sobreamostragem necessárias para a operação do modulador. Todo o trabalho segue a metodologia top-down/bottom-up, incluindo o desenvolvimento de macro-modelos, implementação a nível de transistor e implementação parcial de layout. Todo projeto de sub-circuitos e modelos em Verilog-A é detalhado, incluindo o amplificador operacional de transcondutância, comparadores, quantizador de 5 níveis, chaves, sintetizador de clock, detector de fase e frequência, bomba de carga, filtro, oscilador controlado por tensão, divisor de frequência N-inteiro e gerador de correntes de polarização. O resultado de cada um dos principais sub-circuitos é destacado. O modulador proposto opera para GSM (banda de 200 kHz), Bluetooth (banda de 500 kHz) e UMTS (banda de 2 MHz), atingindo um número efetivo de bits de 11,51, 10,16 e 8,82 respectivamente, com um consumo de 10,8, 10,8 e 14,5 mW respectivamente e uma figura de mérito de Schreier de 145, 140 e 145 respectivamente. A maior contribuição do trabalho é o design completo e integração de ambos o modulador ΣΔ reconfigurável e do sintetizador de clock.

# **Abstract**

With the rising number of wireless communication standards in the past decades, transceiver reconfigurability becomes an interesting and beneficial feature in System-on-Chip (SoC) embedded devices that require a large variety of Radio Frequency (RF) standards for signal processing. With the aim of developing a fully reconfigurable RF transceiver, that is able to operate in several standards with adequate power consumption, the reconfigurability of the individual building blocks is an enticing research subject. Specifically in the case of the Analog-to-Digital Converters (ADC), the  $\Sigma\Delta$  ADC topology shows a few advantages in regards to reconfigurability with the goal of power consumption reduction in the lower frequency range of operation. This type of topology allows for the reduction of the sampling frequency, the order of the noise shaping and the number of bits in the output quantizer, all in exchange of resolution and power consumption. The main goal of this works is to present the complete design of a reconfigurable ADC that operates in the lower frequency range of mobile wireless communications, specifically GSM (200 kHz bandwidth) and UMTS (2 MHz bandwidth), and additionally provide the operation for Bluetooth with 500 kHz bandwidth, alongside the design of clock synthesizer based Phase Locked Loop (PLL) for the synthesis of the necessary oversampling frequencies for the modulator. This work follows the top-down/bottom-up methodology, including macro-model development, transistor-level and partial layout implementation. Every sub-circuit design and Verilog-A code is detailed, including the operational transconductance amplifier, comparators, 5-level quantizer, switches, clock synthesizer, phase and frequency detector, charge pump, loop filter, voltage-controlled oscillator, N-integer frequency divider and bias currents generator. The results of each of the main sub-circuits is highlighted. The proposed modulator operates for GSM (bandwidth of 200 kHz), Bluetooth (bandwidth of 500 kHz) and UMTS (bandwidth of 2 MHz), achieving an effective number of bits of 11.51, 10.16 and 8.82 bits respectively with a power consumption of 10.8, 10.8 and 14.5 mW respectively and achieving a Schreier Figure of Merit of 145, 140 and 145 respectively. The major contribution of this work is the complete design and integration of both the reconfigurable  $\Sigma\Delta$  modulator and the clock synthesizer.

# **List of Figures**

| 1.1  | 2G, 3G, 4G and 5G utilization in 2019 and forecast for 2025. (GSMA, 2021)                                                                                        | 17 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Comparison between (a) the ideal SDR and (b) the feasible concept implementation for the receiver (adapted from (MORGADO; RIO; ROSA, 2011)).                     | 18 |

| 1.3  | Diagram of sub-circuits developed in this work alongside the target standards                                                                                    |    |

|      | and specifications                                                                                                                                               | 19 |

| 2.1  | Analog-to-Digital conversion diagram for Nyquist rate ADCs (based on                                                                                             |    |

|      | (ROSA, 2018))                                                                                                                                                    | 22 |

| 2.2  | Frequency domain representation of (a) original signal; (b) Sampled signal with $f = 2B$ ; (c) Oversampled signal with $f_s > 2B$ ; (d) Undersampled signal with |    |

|      | $f_s < 2B$                                                                                                                                                       | 23 |

| 2.3  | Quantization process: (a) Multi-bit quantizer block; (b) Single-bit quantizer                                                                                    |    |

|      | block; (c) multi-bit quantization; (d) single-bit quantization; (e) multi-bit                                                                                    |    |

|      | quantization error; (f) single-bit quantization error (ROSA, 2018)                                                                                               | 25 |

| 2.4  | Equivalent quantizatizer linear model                                                                                                                            | 26 |

| 2.5  | Quantization white noise Probability Density Function (PDF) (based on (ROSA,                                                                                     |    |

|      | 2018))                                                                                                                                                           | 26 |

| 2.6  | Complete $\Sigma\Delta$ ADC based on (BAKER, B., 2002)                                                                                                           | 27 |

| 2.7  | Spectrum of a $\Sigma\Delta$ modulated signal (adapted from (ROSA, 2018))                                                                                        | 28 |

| 2.8  | Realization of a first order $\Sigma\Delta$ modulator. (a) Linear model, (b) Circuit realization.                                                                | 29 |

| 2.9  | Higher order single loop $\Sigma\Delta$ modulator (ROSA, 2018)                                                                                                   | 30 |

| 2.10 | General topology of an N-stage cascade $\Sigma\Delta M$ (ROSA, 2018)                                                                                             | 31 |

| 2.11 | Band-pass $\Sigma\Delta$ ADC (PAVAN; SCHREIER; TEMES, 2017)                                                                                                      | 33 |

| 2.12 | Comparison between (a) DT modulator; (b) CT modulator (ROSA, 2018)                                                                                               | 34 |

| 2.13 | Example of implementation of a continuous time $\Sigma \Delta M$                                                                                                 | 34 |

| 2.14 | Block diagram of a k-order $(sinc^k)$ CIC decimation filter (ROSA, 2018)                                                                                         | 35 |

| 2.15 | Successive approximation register ADC. (a) Diagram, (b) flowchart (J.TOCCI;                                                                                      |    |

|      | WIDMER; MOSS, 2007), (c) conversion waveform (MALOBERTI, 2007)                                                                                                   | 36 |

| 2.16 | 2-bits per stage Pipeline ADC diagram (CHIU; GRAY; NIKOLIC, 2004)                                                                                                | 38 |

| 2.17 | Pipeline timing diagram (MALOBERTI, 2007)                                                                                                                        | 38 |

|      | Time-Interleaved architecture diagram (MALOBERTI, 2007)                                                                                                          | 39 |

| 2.19 | Compilation of papers related to ADCs published in the Journal of Solid State                                                                                    |    |

|      | Circuits since 2018.                                                                                                                                             | 40 |

| 2.20 | State-of-the-art ADCs in relation to resolution versus bandwidth from                                                                                            |    |

|      | (MURMANN, 2022)                                                                                                                                                  | 41 |

| 3.1  | Top-down/bottom-up methodology (adapted from (ROSA, 2018))                                                                                                       | 44 |

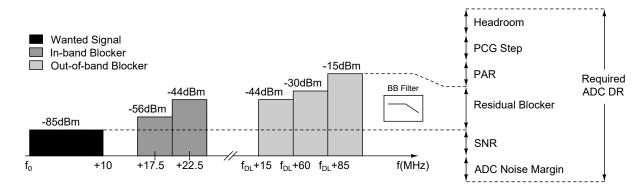

| 3.2  | Blocker template for LTE mode (BW = 10 MHz), and corresponding required ADC DR ( $f_{DL}$ represents the higher end of the downlink operation) (BETTINI          |            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | , ,                                                                                                                                                              | 45         |

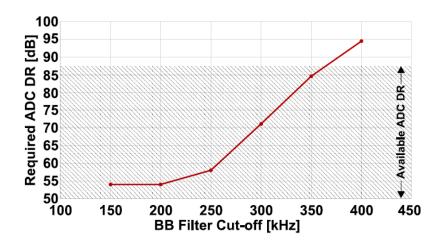

| 3.3  | Required ADC DR versus BB filter cut-off in EDGE mode (Alternate channel                                                                                         |            |

|      | bi , bi. ws , , , , , , , ,                                                                                                                                      | 45         |

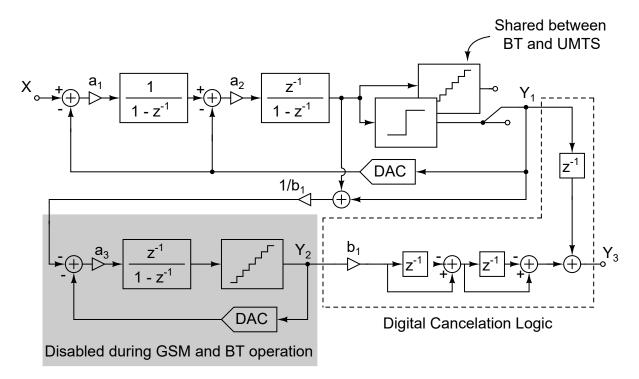

| 3.4  | 1 8                                                                                                                                                              | 46         |

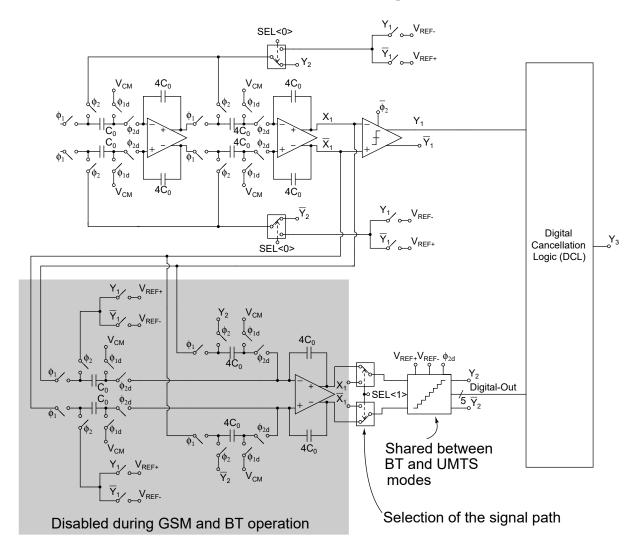

| 3.5  |                                                                                                                                                                  | 48         |

| 3.6  |                                                                                                                                                                  | 49         |

| 3.7  | Fully differential folded-cascode amplifier with positive feedback gain                                                                                          | <b>Г</b> 1 |

| 20   |                                                                                                                                                                  | 51<br>53   |

| 3.8  |                                                                                                                                                                  | วว<br>54   |

| 3.9  | 1                                                                                                                                                                | 54<br>55   |

| 3.10 |                                                                                                                                                                  |            |

| 3.11 |                                                                                                                                                                  | 56<br>56   |

| 3.12 |                                                                                                                                                                  | วธ<br>58   |

| 3.13 | 6                                                                                                                                                                | 58<br>58   |

| 3.14 |                                                                                                                                                                  | эо<br>59   |

| 3.15 |                                                                                                                                                                  | 59<br>62   |

| 3.16 |                                                                                                                                                                  | 62<br>62   |

|      |                                                                                                                                                                  | 02         |

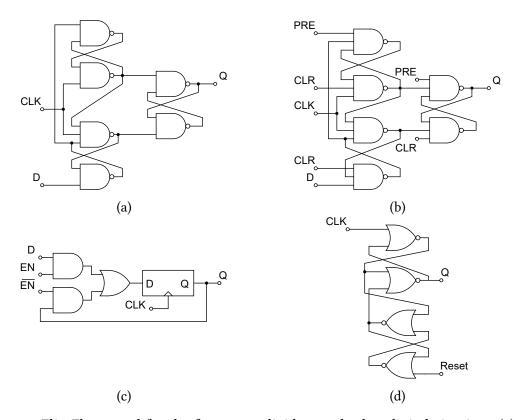

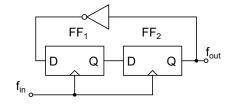

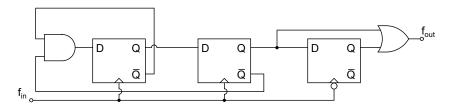

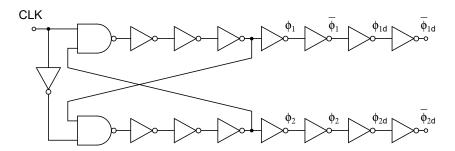

| 5.10 | Flip-Flops used for the frequency dividers and other digital circuitry. (a) D Flip-Flop; (b) D Flip-Flop with Preset and Clear pins; (c) D Flip-Flop with Enable |            |

|      |                                                                                                                                                                  | 63         |

| 3.19 |                                                                                                                                                                  | 63         |

| 3.20 |                                                                                                                                                                  | 64         |

| 3.21 |                                                                                                                                                                  | 65         |

| 3.22 |                                                                                                                                                                  | 65         |

|      |                                                                                                                                                                  | 66         |

| J.4J |                                                                                                                                                                  |            |

| 4.1  | ±                                                                                                                                                                | 68         |

| 4.2  | 1                                                                                                                                                                | 69         |

| 4.3  |                                                                                                                                                                  | 69         |

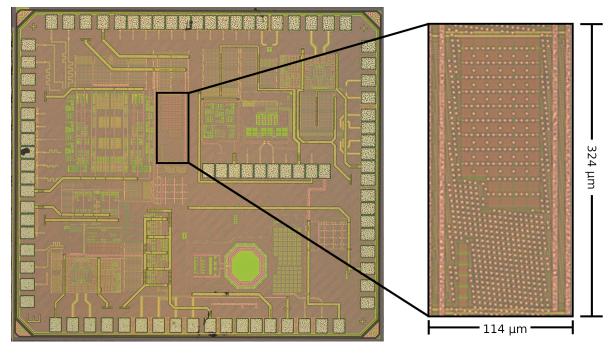

| 4.4  | Die micrograph of the 65-nm chip with a zoomed-in view of the PLL occupying                                                                                      |            |

|      |                                                                                                                                                                  | 70         |

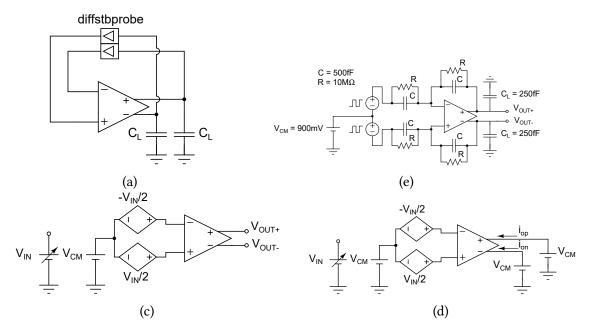

| 4.5  | Operational amplifier test-benches. (a) Stability/freq. response; (b) slew rate;                                                                                 |            |

|      | (c) differential output voltage; (d) differential output current and                                                                                             |            |

|      |                                                                                                                                                                  | 71         |

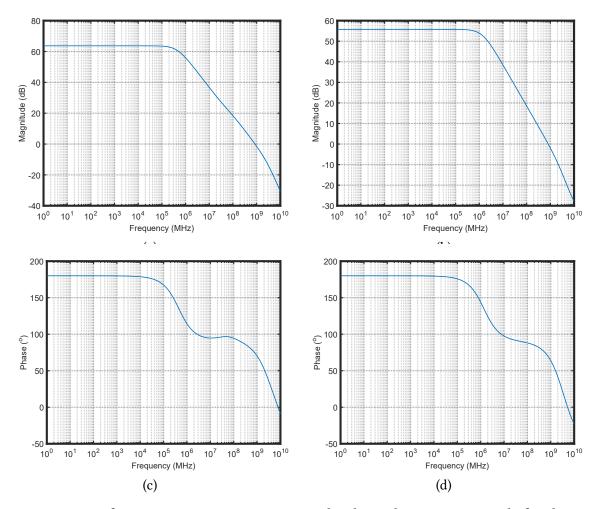

| 4.6  | OTA frequency response in transistor-level simulations. Magnitude for the                                                                                        |            |

|      | OTA with 1.2 V transistors in (a), and the OTA with 1.8 V transistors in (b);                                                                                    |            |

|      | Phase for the OTA with 1.2 V transistors in (c) and for the OTA with 1.8 V                                                                                       |            |

|      |                                                                                                                                                                  | 72         |

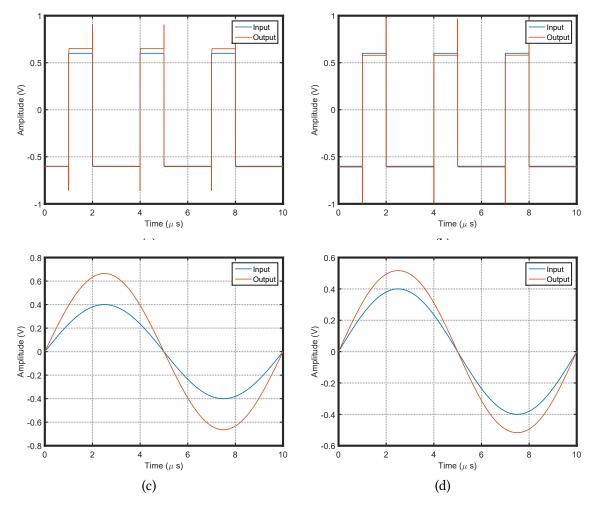

| 4.7  | OTA transient response in transistor-level simulations. Slew Rate for the OTA                                                                                    |            |

|      | with 1.2 V transistors in (a), and the OTA with 1.8 V transistors in (b); Transient                                                                              |            |

|      | with a closed loop configuration to double the gain for the OTA with 1.2 V                                                                                       | <b>-</b> - |

| 4.0  |                                                                                                                                                                  | 73         |

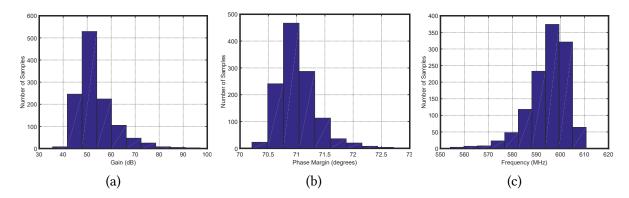

| 4.8  | Monte Carlo $3\sigma$ variation for mismatch and process with 1200 samples for                                                                                   | <b>,</b>   |

|      | transistor-level simulations. (a) Gain; (b) Phase Margin; (c) Gain Bandwidth                                                                                     | 74         |

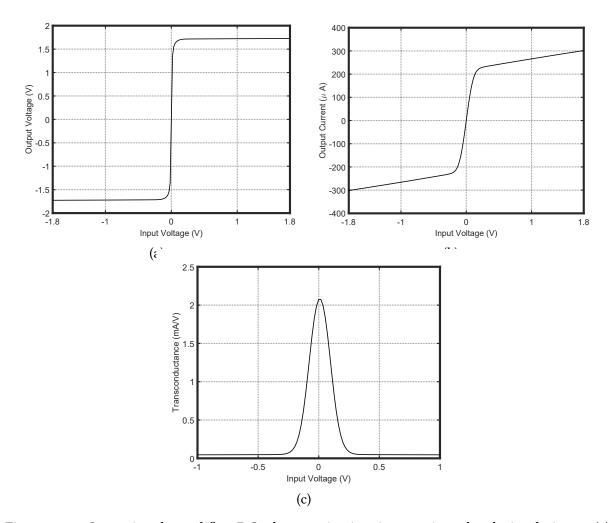

| 4.9  | Operational amplifier DC characterization in transistor-level simulations: (a)       |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | Differential output voltage; (b) Differential output current; (c) Transconductance.  | 75  |

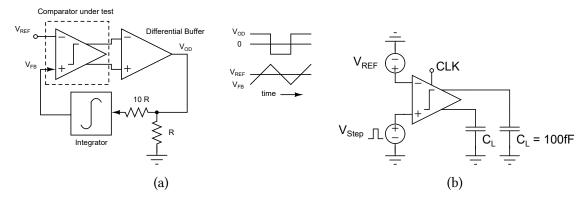

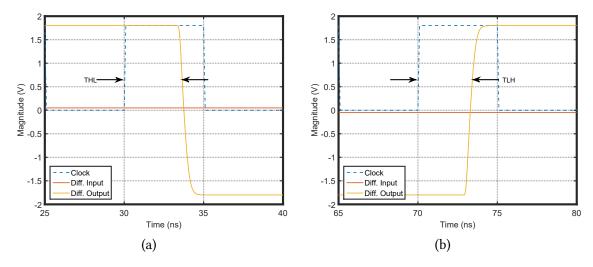

| 4.10 | Comparator test-benches. (a) DOTB; (b) comparison time                               | 76  |

| 4.11 | Comparator comparison time transistor-level simulations. (a) Falling edge; (b)       |     |

|      | rising edge                                                                          | 76  |

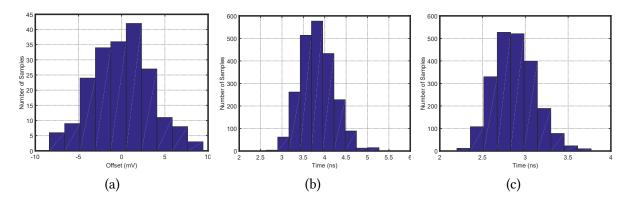

| 4.12 | Monte Carlo $3\sigma$ variation for mismatch and process in transistor-level         |     |

|      | simulations. (a) Offset (200 samples); (b) Falling comparison time (2200             |     |

|      | samples); (c) Rising comparison time (2200) samples                                  | 77  |

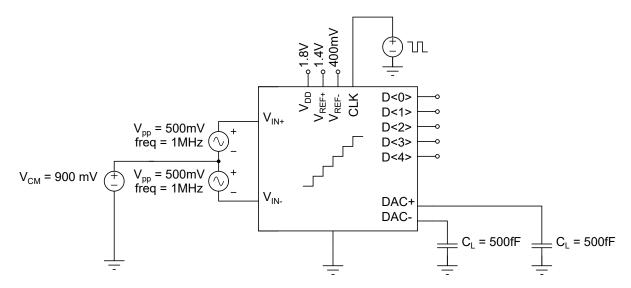

| 4.13 | Multi-bit quantizer test-bench                                                       | 77  |

|      | Quantizer transient operation. (a) Analog output; (b) Digital output                 |     |

| 1111 | (transistor-level simulations)                                                       | 78  |

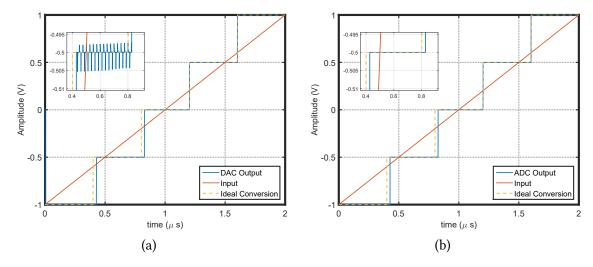

| 4 15 | Quantizer static DA and AD conversions compared to ideal conversions. (a)            | , 0 |

| 1.15 | DAC; (b) ADC (transistor-level simulations)                                          | 78  |

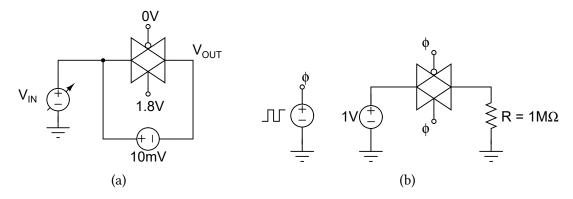

| 4 16 | Switches test-benches. (a) DC; (b) transient.                                        | 79  |

| 4.17 | On-resistance and transient response of the switches from transistor-level           | 1)  |

| 1.17 | simulations. (a) Transmission gate $R_{ON}$ ; (b) Bootstrapped switch transient; (c) |     |

|      | Transmission gate transient                                                          | 79  |

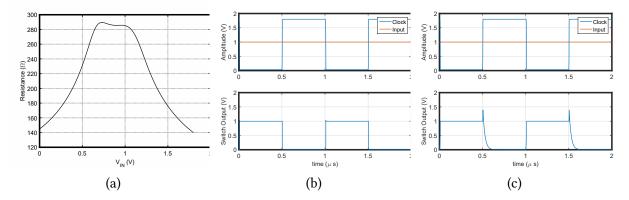

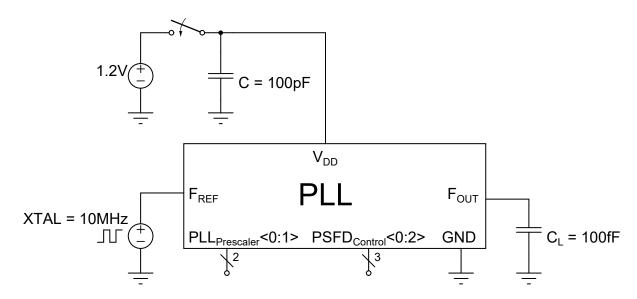

| 4.18 | PLL test-bench.                                                                      | 80  |

|      | Clock synthesizer spectra for main frequencies. Typical: 1.2 V, 27 °C, TT; Worst     | 00  |

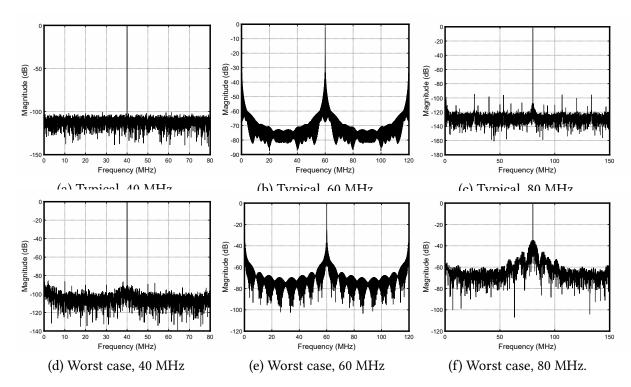

| 4.19 |                                                                                      | 81  |

| 4.00 | case: 1.3 V, 80 °C, FF (obtained from extracted layout simulations)                  | 01  |

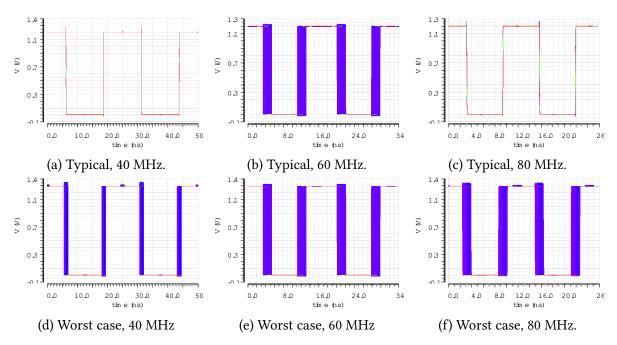

| 4.20 | Clock synthesizer eye diagram for main frequencies. Typical: 1.2 V, 27 °C, TT;       | 0.0 |

| 4.04 | Worst case: 1.3 V, 80 °C, FF (obtained from extracted layout simulations)            | 82  |

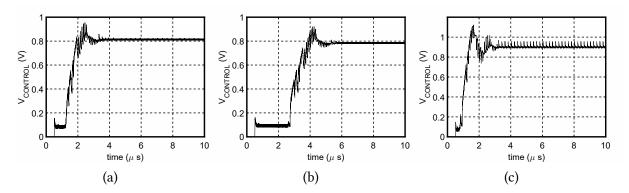

| 4.21 | Control voltage when 200 MHz is selected for (a) TT, 27 °C, 1.2 V supply, (b) SS,    |     |

|      | 0 °C, 1.1 V supply, (c) FF, 80 °C, 1.3 V supply (obtained from extracted layout      | 0.0 |

| 4.00 | simulations)                                                                         | 82  |

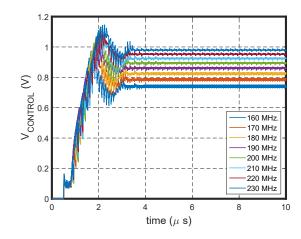

| 4.22 | Control voltage comparison for all frequency selections, varying from 160            |     |

|      | MHz to 230 MHz obtained from extracted layout simulations.                           | 83  |

| 4.23 | Generated clock waveform obtained from extracted layout simulations (a) 40           |     |

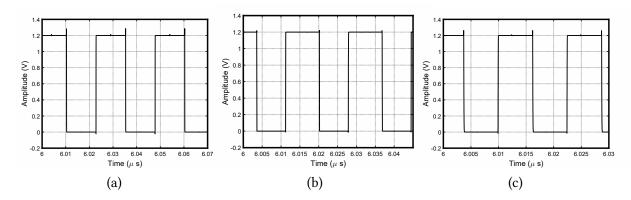

|      | MHz, (b) 60 MHz, (c) 80 MHz                                                          | 83  |

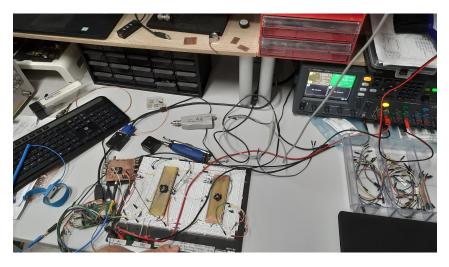

|      | Measurement setup for the PLL                                                        | 84  |

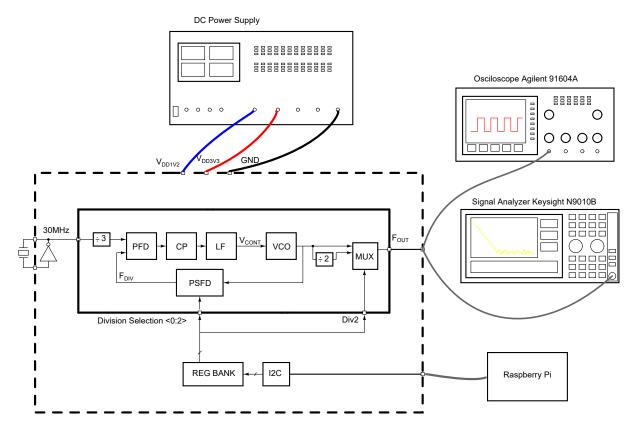

|      | PLL measurement setup diagram                                                        | 85  |

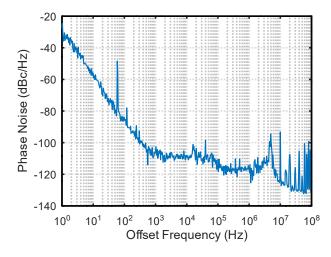

|      | Measured phase noise spectrum of the fabricated PLL prototype                        | 85  |

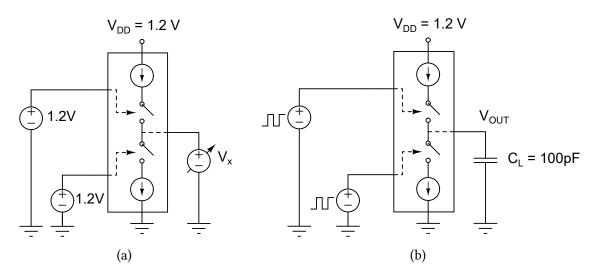

| 4.27 | Charge Pump test-benches. (a) DC; (b) transient                                      | 86  |

| 4.28 | (a) Charge Pump mismatch between UP and DOWN currents. (b)                           |     |

|      | approximation of (a) between 550 mV and 650 mV (extracted layout                     |     |

|      | simulations)                                                                         | 87  |

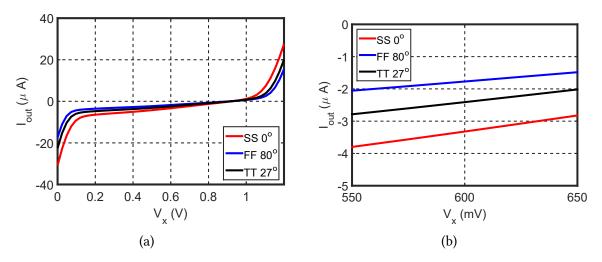

|      | CP transient operation (extracted layout simulations)                                | 87  |

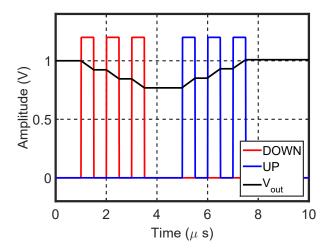

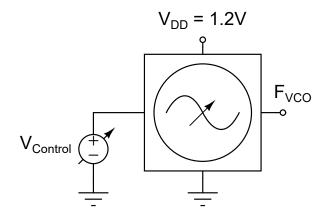

| 4.30 | VCO test-bench                                                                       | 88  |

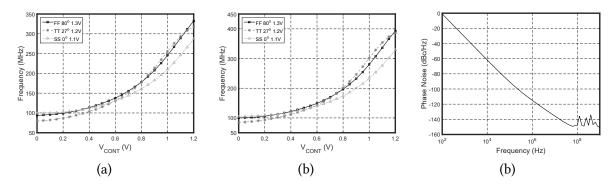

| 4.31 | (a) VCO tunning range from post-layout simulation and (b) transistor-level,          |     |

|      | and (c) phase noise for worst case condition (extracted simulation)                  | 88  |

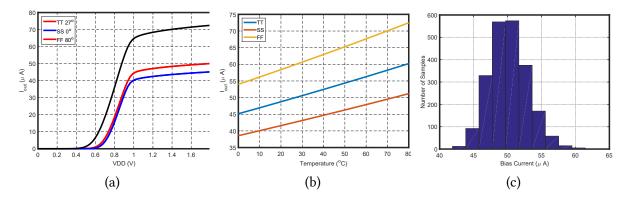

| 4.32 | Bias currents transistor level simulation results: (a) DC sweep, (b) Temperature     |     |

|      | sweep and (c) Monte Carlo process and mismatch variation                             | 89  |

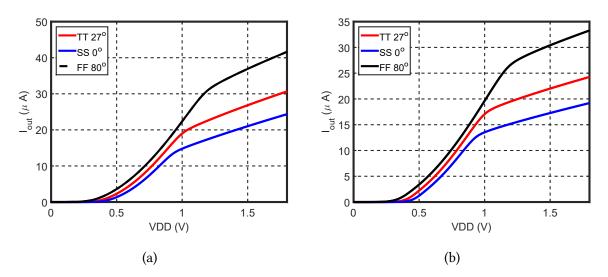

| 4.33 | DC sweep extracted simulation results for process and temperature corners            |     |

|      | for (a) P Bias current (UP current) and (b) N bias current (DOWN current)            | 90  |

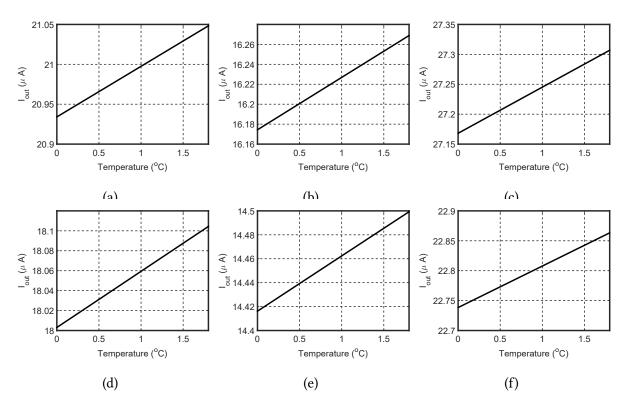

| 4.34 | Extracted simulation results in a temperature sweep for P Bias current (UP           |     |

|      | current) for (a) TT, 1.2 V supply, (b) SS, 1.1 V supply, (c) FF, 1.3 V supply and    |     |

|      | N Bias current (DOWN current) for (d) TT, 1.2 V supply, (e) SS, 1.1 V supply,        |     |

|      | (f) FF, 1.3 V supply                                                                 | 90  |

|      | <del></del> ·                                                                        |     |

| 4.35 | Extracted simulation results for Monte Carlo 3 $\sigma$ process variation with 2200 |    |

|------|-------------------------------------------------------------------------------------|----|

|      | samples for (a) P bias current and (b) N bias current                               | 91 |

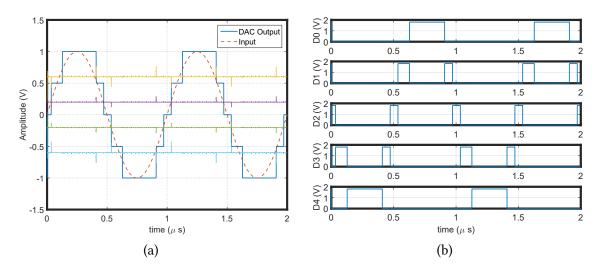

| 4.36 | $\Sigma\Delta M$ test-bench                                                         | 92 |

| 4.37 | SNR with input amplitude variation for each mode obtained from macro-model          |    |

|      | simulations                                                                         | 92 |

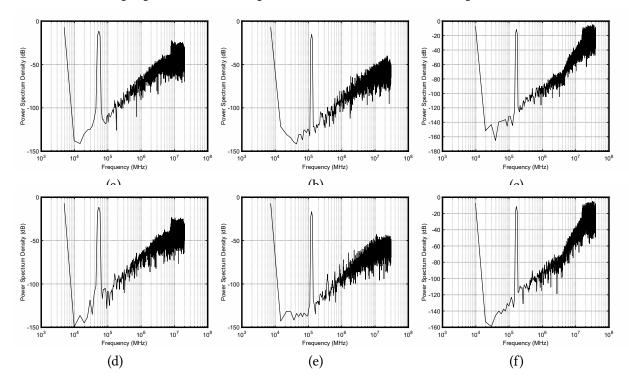

| 4.38 | Power Spectrum Density for each mode of operation (Hanning Window with              |    |

|      | 8192 FFT points). Macro-model results with ideal clocks for (a) 40, (b) 60 and      |    |

|      | (c) 80 MHz; Macro-model results with PLL-generated clock for (d) 40, (e) 60         |    |

|      | and (f) 80 MHz                                                                      | 93 |

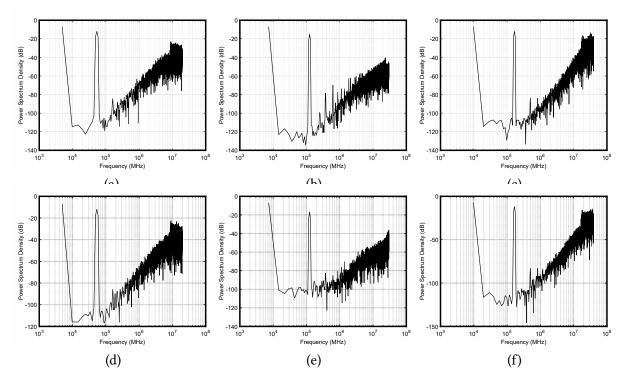

| 4.39 | Power Spectrum Density for each mode of operation (Hanning Window with              |    |

|      | 8192 FFT points). Transistor-level simulation with ideal clock and OTA with         |    |

|      | 1.2 V transistors for (a) 40, (b) 60 and (c) 80 MHz; Transistor-level simulation    |    |

|      | with PLL-generated clock and OTA with 1.2 V transistors for (d) 40, (e) 60 and      |    |

|      | (f) 80 MHz                                                                          | 94 |

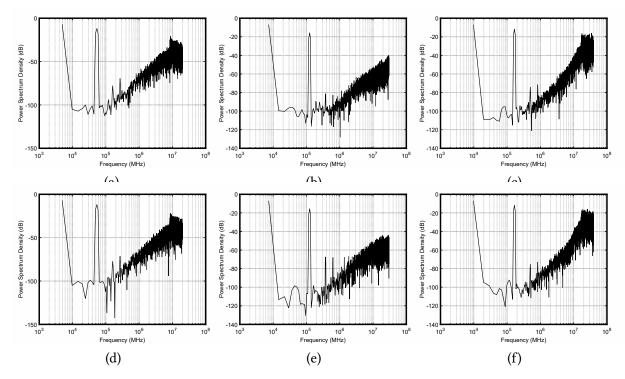

| 4.40 | Power Spectrum Density for each mode of operation (Hanning Window with              |    |

|      | 8192 FFT points). Transistor-level simulation with ideal clock and OTA with         |    |

|      | 1.8 V transistors for (a) 40, (b) 60 and (c) 80 MHz; Transistor-level simulation    |    |

|      | with PLL-generated clock and OTA with 1.8 V transistors for (d) 40, (e) 60 and      |    |

|      | (f) 80 MHz                                                                          | 95 |

|      |                                                                                     |    |

# **List of Acronyms**

$\Sigma\Delta M$   $\Sigma\Delta$  Modulator AD Analog-to-Digital

ADC Analog-to-Digital Converters

BT Bluetooth

CIC Cascade-Integrator-Comb CMFB Common-Mode Feedback

CP Charge Pump CT Continuous Time

DAC Digital-to-Analog Converter

DCL Digital Cancellation Logic

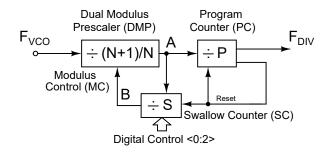

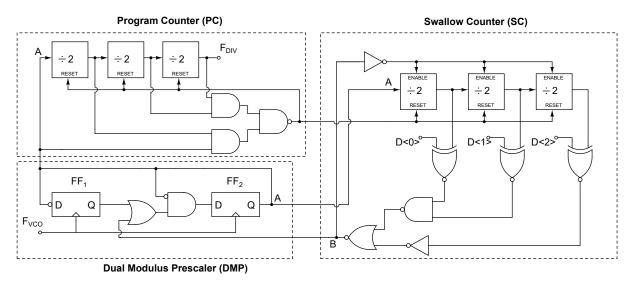

DMP Dual Modulus Prescaler

DOTB Dynamic-Offset Test-Bench

DR Dynamic Range

DSP Digital Signal Processor

DT Discrete Time

DVB-S2 Digital Video Broadcasting - Satellite - Second Generation

ENOB Effective Number of Bits EOC End of Conversion EVM Error Vector Magnitude

FF Fast-Fast

FIR Finite Impulse Response

FoM Figure-of-Merit GBW Gain-Bandwidth

GPS Global Positioning System

GS/s Giga Samples per Second

GSM Global System for Mobile Communications

IBN In-Band NoiseIC Integrated CircuitIF Intermediate FrequencyIIR Infinite Impulse Response

IoT Internet-of-Things

ISSCC International Solid-States Circuits Conference

LF Loop Filter

LNA Low-Noise Amplifier

LR Line Regulation

LTE Long Term Evolution

LTE-A Long Term Evolution-Advanced MASH Multi-Stage Noise Shaping

MC Modulus Control

MSB Most Significant Bit NTF Noise Transfer Function **OSR** Oversampling Ratio

Operational Transconductance Amplifier **OTA**

PA Power Amplifier

**PAR** Peak-to-Average-Power Ratio

**Program Counter** PC

**Probability Density Function PDF PDF Probability Density Function** Phase and Frequency Detector **PFD PGC** Programmable Gain Control Pulse-Swallow Frequency Divider **PSFD**

RF Radio Frequency RF Radio Frequency S&H Sample-and-Hold

Successive Approximation Register SAR

**Swallow Counter** SC

Software Defined Radio **SDR SNR** Signal-to-Noise Ratio SoC System-on-Chip System-on-Chip SoC SR Slew-Rate Slow-Slow

**STF** Signal Transfer Function Temperature Coefficient TC

Typical-Typical TT

SS

Universal Mobile Telecommunications System **UMTS**

Voltage Controlled Oscillator VCO

W-CDMA Wide-Band Code-Division Multiple Access

# **Contents**

| 1 | Intr | oductio                                     | n 16                                              |  |  |  |  |  |

|---|------|---------------------------------------------|---------------------------------------------------|--|--|--|--|--|

|   | 1.1  | Justific                                    | ation                                             |  |  |  |  |  |

|   | 1.2  | Goals a                                     | and Contents                                      |  |  |  |  |  |

| 2 | Bibl | Bibliography Review 21                      |                                                   |  |  |  |  |  |

|   | 2.1  | Analog                                      | g-to-Digital Conversion                           |  |  |  |  |  |

|   |      | 2.1.1                                       | Sampling                                          |  |  |  |  |  |

|   |      | 2.1.2                                       | Quantization                                      |  |  |  |  |  |

|   | 2.2  | The $\Sigma \Delta$                         | A ADC                                             |  |  |  |  |  |

|   |      | 2.2.1                                       | Noise Shaping                                     |  |  |  |  |  |

|   |      | 2.2.2                                       | Classification of $\Sigma\Delta Ms$               |  |  |  |  |  |

|   |      | 2.2.3                                       | Digital Blocks of the $\Sigma\Delta$ ADC          |  |  |  |  |  |

|   | 2.3  | Other 1                                     | Popular AD Conversion Techniques                  |  |  |  |  |  |

|   |      | 2.3.1                                       | Successive Approximation Register                 |  |  |  |  |  |

|   |      | 2.3.2                                       | Pipeline                                          |  |  |  |  |  |

|   |      | 2.3.3                                       | Time-Interleaving                                 |  |  |  |  |  |

|   | 2.4  | Recent                                      | Trends in ADC Design                              |  |  |  |  |  |

|   | 2.5  | Main B                                      | ibliography for the Project                       |  |  |  |  |  |

| 3 | Circ | Circuit Design 4                            |                                                   |  |  |  |  |  |

|   | 3.1  | 1 Methodology                               |                                                   |  |  |  |  |  |

|   | 3.2  | Multi-S                                     | Standard Receiver Considerations                  |  |  |  |  |  |

|   | 3.3  | 3.3 Reconfigurable $\Sigma\Delta$ Modulator |                                                   |  |  |  |  |  |

|   |      | 3.3.1                                       | Operational Transconductance Amplifier            |  |  |  |  |  |

|   |      | 3.3.2                                       | Comparators                                       |  |  |  |  |  |

|   |      | 3.3.3                                       | Multi-bit Quantizer                               |  |  |  |  |  |

|   |      | 3.3.4                                       | Switches                                          |  |  |  |  |  |

|   | 3.4  | PLL-Ba                                      | sed Clock Synthesizer                             |  |  |  |  |  |

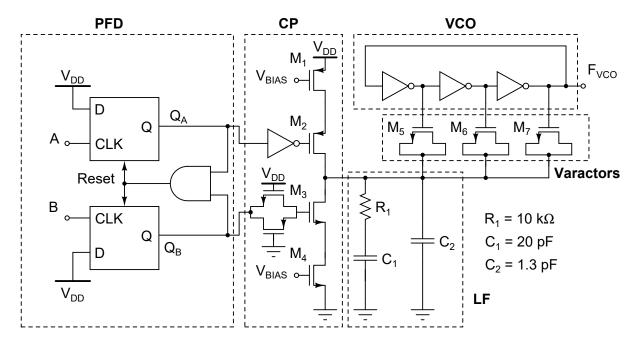

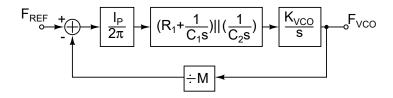

|   |      | 3.4.1                                       | PLL Feedforward Path (PFD, CP, LF and VCO)        |  |  |  |  |  |

|   |      | 3.4.2                                       | Programmable Loop Frequency Divider               |  |  |  |  |  |

|   | 3.5  | Auxilia                                     | ry Blocks                                         |  |  |  |  |  |

|   |      | 3.5.1                                       | D Flip-Flops                                      |  |  |  |  |  |

|   |      | 3.5.2                                       | Frequency Dividers                                |  |  |  |  |  |

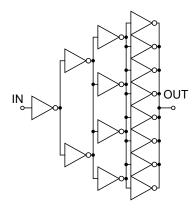

|   |      | 3.5.3                                       | Non-Overlapping Clock Generation and Buffering 64 |  |  |  |  |  |

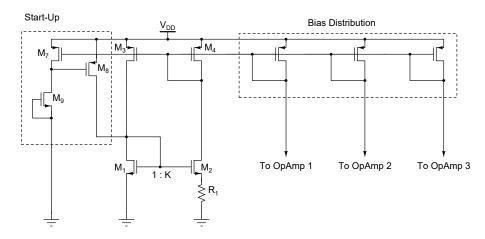

|   |      | 3.5.4                                       | Bias Current Generation                           |  |  |  |  |  |

|   | 3.6  | Summa                                       | nrv                                               |  |  |  |  |  |

| 4  | Results      |        |                                       |    |  |  |  |  |

|----|--------------|--------|---------------------------------------|----|--|--|--|--|

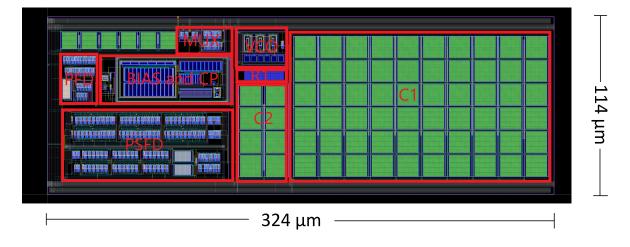

|    | 4.1          | Layou  | t                                     | 67 |  |  |  |  |

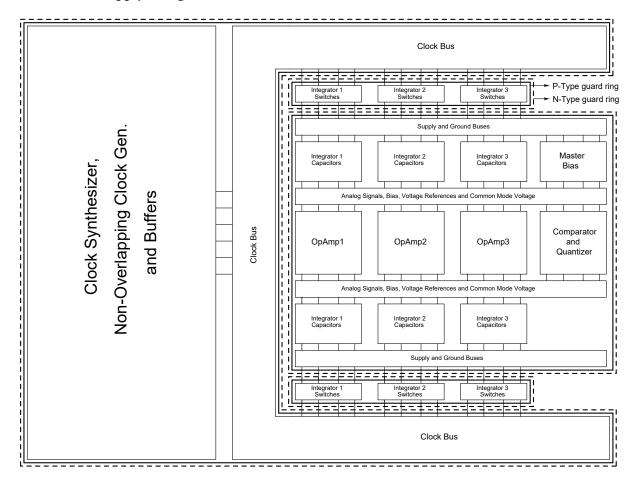

|    |              | 4.1.1  | $\Sigma\Delta$ Modulator              |    |  |  |  |  |

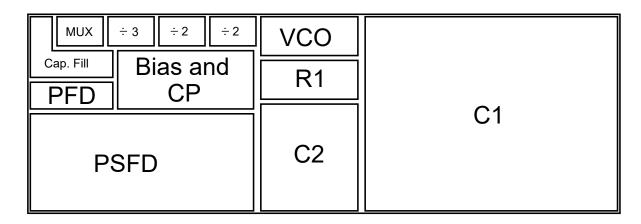

|    |              | 4.1.2  | Clock Synthesizer                     | 68 |  |  |  |  |

|    | 4.2          | Recon  | figurable $\Sigma\Delta$ Modulator    | 70 |  |  |  |  |

|    |              | 4.2.1  | OTA                                   | 70 |  |  |  |  |

|    |              | 4.2.2  | Comparators                           |    |  |  |  |  |

|    |              | 4.2.3  | Multi-bit Quantizer                   |    |  |  |  |  |

|    |              | 4.2.4  | Switches                              |    |  |  |  |  |

|    |              | 4.2.5  | PLL-Based Clock Synthesizer           | 79 |  |  |  |  |

|    |              | 4.2.6  | Charge Pump                           |    |  |  |  |  |

|    |              | 4.2.7  | Voltage Controlled Oscillator         |    |  |  |  |  |

|    |              | 4.2.8  | Auxiliary Blocks                      |    |  |  |  |  |

|    |              | 4.2.9  | Complete Modulator Simulation Results |    |  |  |  |  |

| 5  | Conclusions  |        |                                       |    |  |  |  |  |

|    | 5.1          | Future | Works                                 | 99 |  |  |  |  |

|    | 5.2          |        | hed Works                             |    |  |  |  |  |

| Bi | Bibliography |        |                                       |    |  |  |  |  |

# Chapter 1

# Introduction

With the rising number of wireless standards in the past decades either with the evolution and wide adoption of Bluetooth (BT) and Global Positioning System (GPS) in mobile devices, the continuous use of 2G and 3G technology, popularization of 4G technologies and the recent introduction of 5G in commercial products, transceiver reconfigurability becomes an interesting and beneficial feature in System-on-Chip (SoC) embedded devices that require a large variety of Radio Frequency (RF) standards for signal processing.

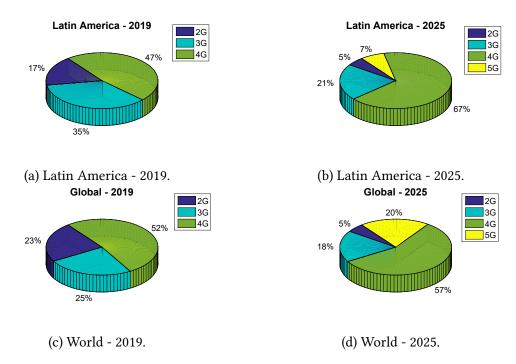

Although smartphones and other communication devices (Internet-of-Things (IoT) devices, GPSs devices, etc.) support a large number of wireless communication protocols, every new standard usually utilizes a dedicated RF module and the innovation in the receiver/transmitter (excluding the Digital Signal Processor (DSP)) stays within the reduction of the Integrated Circuit (IC) technology process node size (MORGADO; RIO; ROSA, 2011). For example, in the reverse engineering work of (EVERYTHINGRF, 2019), the disassembly of the iPhone 11 shows at least 7 RF modules, such as Bluetooth, Wi-Fi, Wide-Band Code-Division Multiple Access (W-CDMA) and Long Term Evolution-Advanced (LTE-A). Besides, the standards from 2G and 3G still retain almost 50% of the usage of mobile networks, and it is expected that in 2025 the combination of 2G, 3G and 4G still retain 80% of all mobile network usage, both in the world and in Latin-America as shown by the graphs of Fig. 1.1 (GSMA, 2021). In summary, receivers that meet bandwidth specifications of the newer technologies while also providing backwards compatibility with older generations supply effective demands of the market (BETTINI et al., 2015), while also providing an easy all-in-one receiver front-end IC solution for prototyping discrete applications that require different wireless standards with efficient power consumption.

Figure 1.1: 2G, 3G, 4G and 5G utilization in 2019 and forecast for 2025. (GSMA, 2021).

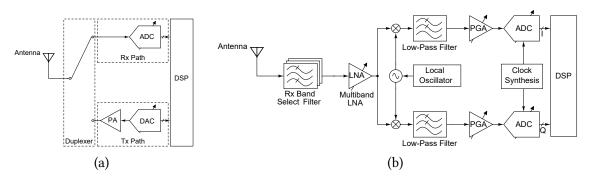

Predicting the rising number of wireless communication standards, the paradigm of Software Defined Radio (SDR) was conceived (III; GERALD Q. MAGUIRE, 1999) (Fig. 1.2a), where, for the receiver, the signal is captured by the antenna and immediately converted by an ADC and is completely processed digitally, or for the transmitter case, the digital signal is directly converted by a Digital-to-Analog Converter (DAC) amplified by a Power Amplifier (PA) and transmitted by the antenna. The ideal SDR remains impractical due to the unfeasible analog-to-digital and digital-to-analog requirements with conversions ranging from 800 MHz to 300 GHz with high resolutions. For this reason the analog/RF front-end of a SDR was transformed into the reconfigurability and adaptability of the analog signal processing steps, as depicted in Fig. 1.2b, where each of the sub-circuits of the receiver are reconfigurable (MORGADO; RIO; ROSA, 2011). A reconfigurable wireless receiver presents an architecture identical to a standard direct conversion receiver, with the only difference being in the reconfigurability of each sub-circuit that builds the system as shown in Fig. 1.2b, where LNA stands for Low-Noise Amplifier, PGA is an acronym for Programmable Gain Amplifier and DSP is the Digital Signal Processor.

One of the main bottlenecks of high-speed state-of-the-art receivers and other communication systems is the ADC. However, for lower speed standards from 2G and 3G, such as Global System for Mobile Communications (GSM) (specifically EDGE), or Universal Mobile Telecommunications System (UMTS) (specifically W-CDMA) that require 200 kHz

Figure 1.2: Comparison between (a) the ideal SDR and (b) the feasible concept implementation for the receiver (adapted from (MORGADO; RIO; ROSA, 2011)).

and 3.84 MHz bandwidth respectively (considering a direct conversion receiver, these bandwidths are reduced by half (MORGADO; DEL RÍO, et al., 2010)), the  $\Sigma\Delta$  ADC topology shows a few advantages in regards to reconfigurability with the goal of power consumption reduction. For example, this type of topology allows for the reduction of the sampling frequency, the order of the noise shaping and the number of bits in the output quantizer, all in exchange of resolution and power consumption. These aspects will be explained in more detail in Sections 2 and 3.

## 1.1 Justification

Considering the predicted usage of wireless cellular communications in (GSMA, 2021) (Fig. 1.1) and the amount of RF modules seen in modern consumer products as described in (EVERYTHINGRF, 2019), a general purpose, reconfigurable RF transceiver that is power-efficient for each mode of operation becomes an enticing research subject. One possible way of reconfiguration in RF receivers is in the ADC. Specifically, in the case of  $\Sigma\Delta$  ADCs its oversampling frequency, order of noise-shaping and number of bits in the quantizer can be adjusted depending on the selected RF standard to be converted with the aim of reducing power consumption, becoming an interesting choice for this type of receivers when operating in the lower frequency range, which encompasses 2G and 3G standards.

### 1.2 Goals and Contents

Taking into account, the limitations in speed of operation of  $\Sigma\Delta$  ADCs, and its advantages in reconfigurability, the main goal of this project is the design of a reconfigurable  $\Sigma\Delta$  Modulator

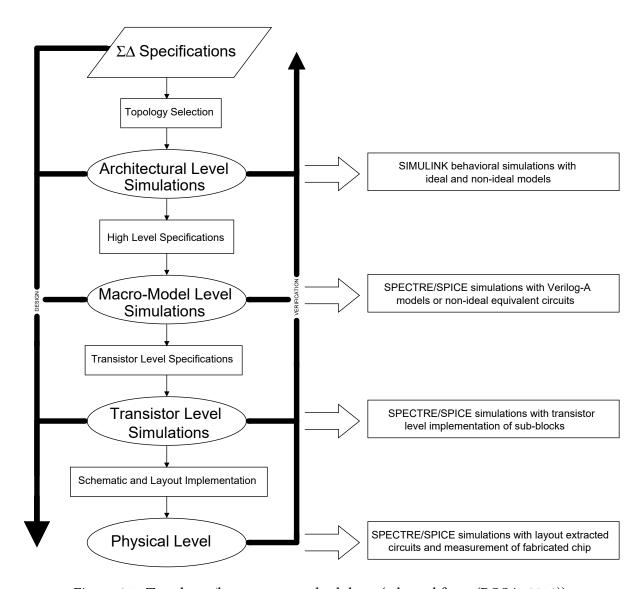

(ΣΔΜ) for the lower frequency spectrum of operation of mobile wireless communication standards, and the inclusion of Bluetooth with 500 kHz bandwidth, with the purpose of providing a general purpose RF module. Thus, the goal of the project is to design a ΣΔ Modulator for the following standards: 1) GSM (with 200 kHz bandwidth), 2) Bluetooth (with 500 kHz bandwidth) and 3) UMTS (with 2 MHz bandwidth - rounded from 1.92 MHz). The design will follow every step of the analog IC design flow starting with high level simulations in SIMULINK, followed by macro-model simulation with Verilog-A in Cadence's Virtuoso Analog Design Environment, followed by the transistor implementation of every sub-circuit, also in in Cadence's Virtuoso Analog Design Environment and finally the layout implementation of the project in Cadence's Virtuoso Layout Suite.

Figure 1.3: Diagram of sub-circuits developed in this work alongside the target standards and specifications.

This work is organized as follows: Chapter 2 will present a detailed bibliography review of analog-to-digital conversion concepts, a review of  $\Sigma\Delta$  modulation and  $\Sigma\Delta$  ADCs, a brief review of other ADC topologies, followed by a general overview of the current trends in ADC design and examples of reconfigurability in ADCs. Chapter 3 will detail the design steps of every major sub-circuit of the  $\Sigma\Delta$ M following the top-down/bottom-up methodology, detailing transistor implementation of every sub-circuit (e.g. operational amplifier, quantizers, clock synthesizer, etc.) alongside macro-model implementation in Verilog-A of critical sub-circuits. Chapter 4 will detail the obtained results of the circuits in Chapter 3, highlighting with more

detail the  $\Sigma\Delta M$  and the clock synthesizer systems. Finally, the conclusions will be presented in Chapter 5.

# **Chapter 2**

# **Bibliography Review**

# 2.1 Analog-to-Digital Conversion

With the exponential increase of computational power during the past decades, digital-signal processing became the norm for the majority of electronic devices-based applications. However, signals of the real world are analog, meaning that they are continuous both in time and amplitude, and to be processed digitally, a converter is required to transform this signals in digital words, discrete both in time and amplitude. For this reason, ADCs and DACs are essential interfaces between the Digital-Signal Processor (DSP) and the real world analog signals.

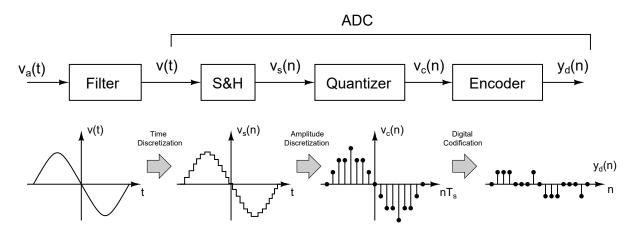

The basic concept of a Nyquist-rate Analog-to-Digital (AD) conversion is shown in Fig. 2.1, where the analog signal  $v_a(t)$  is initially filtered to suppress any unwanted high frequency components, resulting in v(t). v(t) is, then, sampled by the Sample-and-Hold (S&H) circuit at a rate  $f_s$  and is discretized in time resulting in  $v_s(n)=v_s(nT_s)$ , where  $T_s=1/f_s$ . Then, the amplitude is quantized by the quantizer block with N bits, to a value closest to the  $2^N$  division of the full-scale input range resulting in  $v_c(n)$ . Finally, a digital code is assigned to each of the output levels (ROSA, 2018).

The main operations performed by the analog part of the ADC are the sampling and quantization. These operations are a common feature in Nyquist-rate and oversampled ADCs and will be reviewed in the next sections.

Figure 2.1: Analog-to-Digital conversion diagram for Nyquist rate ADCs (based on (ROSA, 2018)).

### 2.1.1 Sampling

The sampling operation is performed by periodically sampling the input analog signal in the time domain. The sampling can be represented by the periodic impulse train s(t) or the Dirac impulse train (2.1)

$$s(t) = \sum_{n=-\infty}^{\infty} \delta(t - nT_s). \tag{2.1}$$

Meaning that, the sampled signal representation in the time domain will be given by  $v_s(t) = v(t)s(t)$ . Thus, the frequency domain representation will be obtained by the convolution of the Fourier transforms of v(t) and s(t), which are respectively V(f) and S(f). The Fourier transform of the impulse train is given by (2.2)

$$S(f) = \frac{1}{T_s} \sum_{k=-\infty}^{\infty} \delta(f - nf_s)$$

(2.2)

Since

$$V_s(f) = V(f) * S(f), \tag{2.3}$$

the Fourier transform of the sampled signal will be given by (2.4)

$$V_s(f) = \frac{1}{T_s} \sum_{k=-\infty}^{\infty} V(f - nf_s)$$

(2.4)

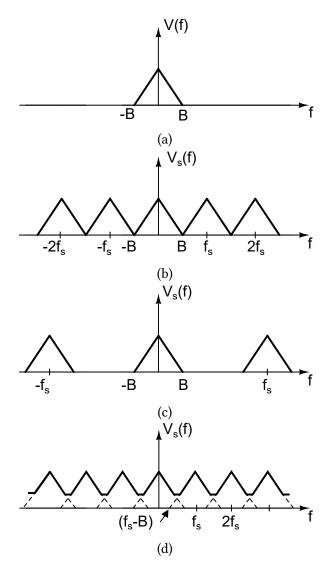

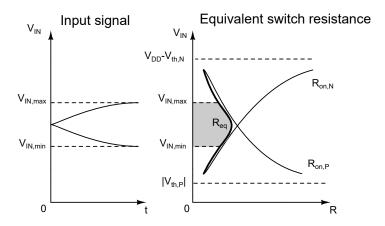

Fig. 2.2a represents the original signal spectrum where the signal band is equal to 2B. If sampled with  $f_s = 2B$ , the resulting spectrum is shown in Fig. 2.2. From this spectrum it is easy to observe the Nyquist-Shannon theorem (PAVAN; SCHREIER; TEMES, 2017) which

Figure 2.2: Frequency domain representation of (a) original signal; (b) Sampled signal with f = 2B; (c) Oversampled signal with  $f_s > 2B$ ; (d) Undersampled signal with  $f_s < 2B$ .

states that

$$f_s = \frac{1}{T_s} \ge 2B. \tag{2.5}$$

Fig. 2.2c shows a signal sampled in a frequency greater than the Nyquist rate, therefore the signal is considered oversampled. Fig. 2.2d shows a signal sampled in frequency lower than the Nyquist rate, in this case there is an overlap between the spectrum replicas, resulting in aliasing, and the original signal cannot be perfectly recovered.

$\Sigma\Delta$  modulators take advantage in oversampling the original analog signal. In this case the anti-alias filter needed for the signal recovery is relaxed, and the filter design is easier. The ratio in which a signal is oversampled is known as Oversampling Ratio (OSR) and is given by

(2.6) (PAVAN; SCHREIER; TEMES, 2017)

$$OSR = \frac{f_s}{2B} \tag{2.6}$$

where  $f_s$  is the sampling frequency and B is the signal bandwidth in Hz.

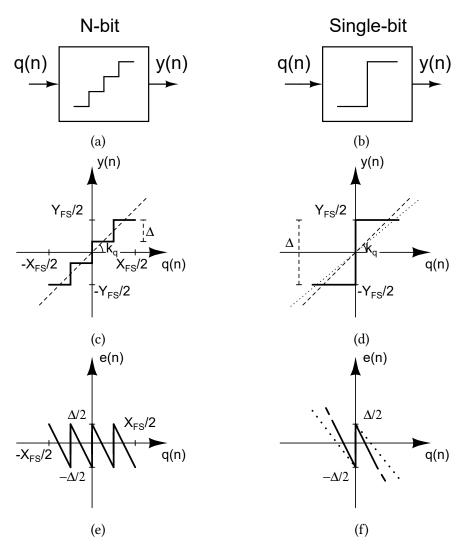

### 2.1.2 Quantization

Quantization is a nonlinear memoryless operation where the output y(n) has a staircase characteristic for a given input q(n), that is ideally uniform, so that two adjacent output levels differ by a fixed spacing  $\Delta = Y_{FS}/(2^N - 1)$ , as depicted in Figs. 2.3c and 2.3d for multi-bit and single-bit quantizer respectively (PAVAN; SCHREIER; TEMES, 2017). The quantizer symbols are shown in Fig. 2.3a for multi-bit quantizers and in Fig. 2.3b for single-bit quantizers.

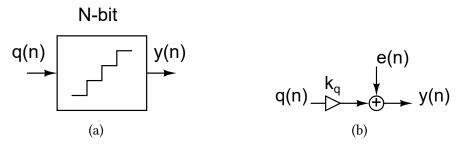

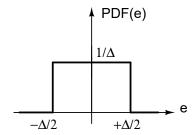

The difference between the input and output is called quantization error, and is given by e(n) = y(n)-q(n). Its transfer curve is shown in Figs. 2.3e and 2.3f for multi-bit and single-bit quantizers respectively. Quantizers have a strongly non-linear behavior and a few assumptions have to be made in regards to the nature of the quantization error (PAVAN; SCHREIER; TEMES, 2017) reaching the conclusion that e(n) is assumed to be an additive "noise" sequence as depicted in Fig. 2.4 and can be viewed as a random process with a uniform probability distribution in the range  $[-\Delta/2, \Delta/2]$  as shown in Fig. 2.5. Thus the power associated with the quantization error can be easily computed (ROSA, 2018):

$$\overline{e^2} = \sigma^2 = \int_{-\infty}^{\infty} e^2 PDF(e) de = \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} e^2 de = \frac{\Delta^2}{12}$$

(2.7)

From (2.7) the peak Signal-to-Noise Ratio (SNR) at the output of an N-bit quantizer for a sinusoidal input can be obtained. The peak-to-peak amplitude of the sinusoid is  $2^N \Delta$  and its power will be given by (2.8) (MALOBERTI, 2007):

$$P_{sin} = \frac{1}{T} \int_0^T \frac{X_{FS}^2}{4} sin^2 (2\pi f t) dt = \frac{X_{FS}^2}{8} = \frac{(\Delta 2^N)^2}{8}.$$

(2.8)

From (2.8), the SNR of a N-bits ADC measured from an input sine wave is obtained by (2.9)

$$SNR = 10log \frac{P_{sin}}{P_{noise}} = 10log(2^{N}(12/8)) = 6.02N + 1.78 \ dB.$$

(2.9)

Figure 2.3: Quantization process: (a) Multi-bit quantizer block; (b) Single-bit quantizer block; (c) multi-bit quantization; (d) single-bit quantization; (e) multi-bit quantization error; (f) single-bit quantization error (ROSA, 2018).

Thus, the expected Effective Number of Bits (ENOB) of an ADC measured from an input sine wave will be given by (2.10)

$$ENOB = \frac{SNR - 1.78}{6.02}. (2.10)$$

Meaning that for the increase in 6.02 dB in SNR, the ADC will effectively show 1 bit increase in resolution approximately.

Figure 2.4: Equivalent quantizatizer linear model.

Figure 2.5: Quantization white noise Probability Density Function (PDF) (based on (ROSA, 2018)).

### 2.2 The $\Sigma\Delta$ ADC

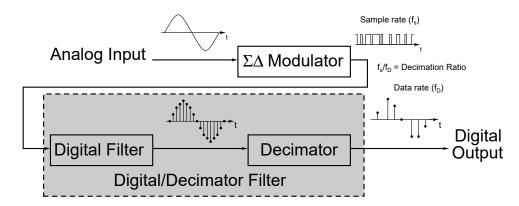

The complete diagram of a  $\Sigma\Delta$  ADC is shown in Fig. 2.6. The initial analog input is modulated by the  $\Sigma\Delta$  Modulator as a pulse density in a sampling frequency much higher than the Nyquist rate, where the average of this pulses corresponds to initial input analog signal. To obtain the digital word, the oversampled signal must be filtered by a digital filter and its sample rate reduced by the decimator. This type of modulation allows for a phenomenon called "noise shaping" where the quantization error is amplified in the oversampled frequency, and suppressed on the signal band. Since the oversampling frequency is much higher than the Nyquist rate, the digital filter parameters are not demanding, simplifying its design.

This section will start with a more detailed explanation of the noise shaping, followed by the circuit realization of this phenomenon with a first order modulator and then, review several different types of implementation of  $\Sigma\Delta$ Ms classified by the type of quantizer, the modulators order, cascaded modulators, band-pass modulators, discrete time and continuous time modulators, and the digital blocks of a  $\Sigma\Delta$  ADC.

Figure 2.6: Complete  $\Sigma\Delta$  ADC based on (BAKER, B., 2002).

### 2.2.1 Noise Shaping

Recalling to the discussion of quantization error in section 2.1.2, by oversampling the input signal, the SNR of the ADC is improved compared to what is described in equation (2.9) and is approximately (ROSA, 2018)

$$SNR \approx 6.02N + 1.78 + 10\log_{10}(OSR).$$

(2.11)

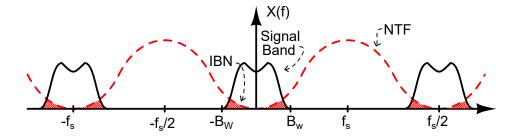

To improve the ADCs performance even further, an operation known as noise shaping is performed and shows the biggest advantage of the  $\Sigma\Delta$  modulation. This phenomena is obtained both through oversampling the input signal and by subtracting it from the output and then passing through a filter transfer function called the Noise Transfer Function (NTF). For low-pass  $\Sigma\Delta$ Ms, the NTF must present a high-pass characteristic and is obtained from a differentiator filter with Z-domain transfer function given by (ROSA, 2018)

$$NTF = (1 - z^{-1})^{L}, (2.12)$$

where L stands for the filter or shaping order. The noise shaping is depicted in Fig. 2.7 where the NTF is shown in red, separated from the original signal spectrum. The remaining quantization noise inside the original signal band is called the In-Band Noise (IBN).

From (2.12), considering  $z = e^{j2\pi f/f_s}$  the NTF, if  $f \ll f_s$  can be approximated to

$$|NTF(f)| = |1 - e^{j2\pi f/f_s}|^L = \left[2\sin\left(\frac{\pi f}{f_s}\right)\right]^L \approx \left(\frac{\pi f}{f_s}\right)^L \tag{2.13}$$

Figure 2.7: Spectrum of a  $\Sigma\Delta$  modulated signal (adapted from (ROSA, 2018)).

and the IBN is

$$IBN = \int_{B_{w}}^{-B_{w}} S_{E}(f) |NTF(f)|^{2} df \approx \frac{\Delta^{2}}{12} \frac{\pi^{2L}}{(2L+1)OSR^{2L+1}}$$

(2.14)

Combining the obtained IBN with the SNR equation from (2.9), the SNR of a  $\Sigma\Delta$  ADC is

$$SNR \approx 6.02N + 1.76 + 10log_{10}(\frac{2L+1}{\pi^{2L}}) + (2L+1)10log_{10}(OSR)$$

(2.15)

A noticeable improvement compared to equation (2.9). Now the SNR increases with the OSR by approximately 3(2L+1) dB/octave (ROSA, 2018).

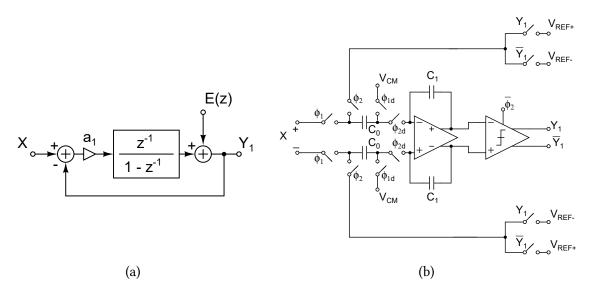

#### First Order $\Sigma\Delta$ Modulator

The circuit realization of a first order DT- $\Sigma\Delta$  modulator is shown in Fig. 2.8. Fig. 2.8 also shows the ideal linear model of the same modulator replacing the quantizer and feedback DAC by a additive noise source E(z) and the integrator by

$$H(z) = \frac{z^{-1}}{1 - z^{-1}}. (2.16)$$

From the linear model the system's transfer function can be easily be obtained:

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z)$$

(2.17)

Renaming and replacing  $z^{-1}$  by the Signal Transfer Function (STF) and  $(1 - z^{-1})$  by NTF the equation becomes

$$Y(z) = STF(z)X(z) + NTF(z)E(z)$$

(2.18)

meaning that the quantization error is multiplied by the NTF(z) which presents a high-pass characteristic, while the input signal is multiplied by the STF(z) which presents a low-pass

Figure 2.8: Realization of a first order  $\Sigma\Delta$  modulator. (a) Linear model, (b) Circuit realization.

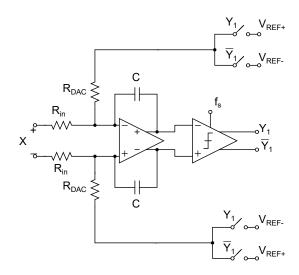

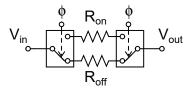

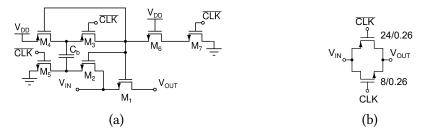

characteristic. The realization of a first order, single-bit  $\Sigma\Delta M$  is shown in Fig. 2.8 where the integrator function is performed by a switched-capacitor integrator, the single-bit ADC is a comparator and the feedback DAC is realized with two switches and two voltage references.

### 2.2.2 Classification of $\Sigma \Delta Ms$

#### **Multi-Bit Modulators**

The SNR of a  $\Sigma\Delta M$  can be improved with the increase in the number of bits in the output quantizer. Fig. 2.7a and Fig. 2.7b show the diagram block of a multi-bit and single-bit quantizer respectively, and the transfer characteristics for each block are shown in Fig. 2.7c and Fig. 2.7d, while the quantization error is shown in Fig. 2.7e and Fig. 2.7f.

In more detail, the advantages of multi-bit quantizers are: 1)The in-band quantization noise power is reduced by approximately 6 dB per additional bit in the embedded quantizer, thanks to the smaller quantization step  $\Delta$ , becoming essential in high-speed applications where impractical oversampling frequencies impose limited SNR, and are traded by the increase in the number of bit in the quantizer. 2) Internal non-linearities are weaker in multi-bit  $\Sigma\Delta$ Ms than in their single-bit counterparts. The quantizer operation better fits the additive white noise model, and phenomena caused by nonlinear dynamics are less evident. 3) For a given order in the loop filter, the stability properties of multi-bit  $\Sigma\Delta$ Ms are better than for single-bit  $\Sigma\Delta$ Ms (ROSA, 2018).

Figure 2.9: Higher order single loop  $\Sigma\Delta$  modulator (ROSA, 2018).

The disadvantages of multi-bit quantizers are the increased complexity both in the feedforward ADC and the feedback DAC circuitry, also leading to non-linearities caused by device mismatching. Usually the resolution of multi-bit quantizers does not surpass 4-bits with few exceptions such as (STRAAYER; PERROTT, 2008) which presents a 5-bit Voltage Controlled Oscillator (VCO)-based quantizer, due to the high speed and high complexity required by these circuits.

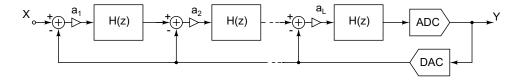

### **High Order Modulators**

Another way to improve a  $\Sigma\Delta M$  performance without altering its OSR is by increasing the noise shaping order as described by equation (2.15). The order of a modulator can be increased simply by adding integrators in series in the modulators feedback loop as shown in Fig. 2.9.

Ideally the NTF would be equal to (2.12), however in practice this is not possible as pure Finite Impulse Response (FIR) NTFs are prone to instability if L>2, exhibiting unbounded states (saturation) due to the high out-of-band gain of NTFs with order above 2. Usually, for higher order loops, the Infinite Impulse Response (IIR) NTFs are used in the form of  $NTF(z) = (z - 1)^L/D(z)$ , with D(z) being a polynomial defined by the modulators scaling coefficients. The approximate stability criterion for higher order noise shaping states that the gain of the NTF is (ROSA, 2018):

$$||NTF(z)||_{\infty} = max||NTF(z)|| \approx 1.5.$$

(2.19)

Although general stability conditions for modulators with order above 2 have not been defined, higher order  $\Sigma\Delta Ms$  are conditionally stable with the proper selection of scaling coefficients (ROSA, 2018) and input amplitude (PAVAN; SCHREIER; TEMES, 2017), and have been widely adopted.

### **Cascade Modulators**

Another way to achieve higher order noise shaping without the hindrance of complex stability criteria of single loop higher order modulator, is to cascade loops which present

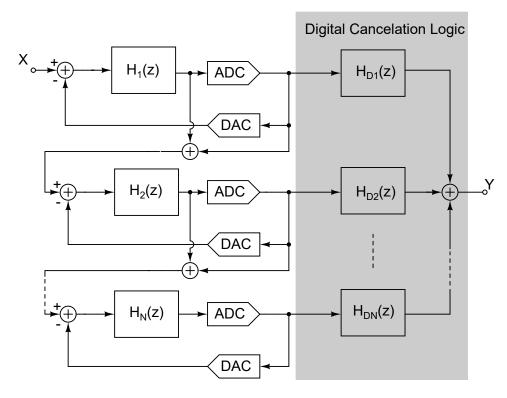

Figure 2.10: General topology of an N-stage cascade  $\Sigma\Delta M$  (ROSA, 2018).

general stability conditions, such as first and second order modulators. By cascading stable feedback loops, unconditionally stable higher order modulators can be obtained. These types of modulators are know as cascade modulators or Multi-Stage Noise Shaping (MASH)  $\Sigma\Delta$  modulators.

Fig. 2.10 shows the general topology of a N-stage cascaded  $\Sigma\Delta M$  where each of the stages performs part of the quantization error modulation and passes to the next stage. The disadvantage of this implementation is that the cascading of the modulated signal does not result in a perfect higher order filter, therefore a Digital Cancellation Logic (DCL) must also be used to cancel inter-stage quantization error. This operation is performed in the digital domain as the output of each stage is already in a digital format.

For example a two stage cascade modulator would present the following transfer functions for the first and second stages respectively:

$$Y_1(z) = STF_1(z)X_1(z) + NTF_1(z)E_1(z)$$

(2.20)

$$Y_2(z) = STF_2(z)X_2(z) + NTF_2(z)E_2(z)$$

(2.21)

The overall output Y(z) is equal to:

$$Y(z) = H_1(z)Y_1 + H_2(z)Y_2, (2.22)$$

choosing  $H_1(z)$  and  $H_2(z)$  as to cancel the first stage quantization error  $E_1(z)$ ,  $H_1(z) = STF_2(z)$  and  $H_2(z) = +NTF_1(z)$ , resulting in:

$$Y(z) = STF_1(z)STF_2(z)X(z) + NTF_1(z)NTF_2(z)E_2(z).$$

(2.23)

Assuming second order loop for both stages,  $STF_1(z) = STF_2(z) = z^{-2}$  and  $NTF_1(z) = NTF_2(z) = (1 - z^{-1})^2$ , resulting in

$$Y(z) = z^{-4}X(z) + (1 - z^{-1})^4 E_2(z). (2.24)$$

Thus, achieving a 4<sup>th</sup> order noise shaping with unconditional stability provided by the cascade of two second order loops (PAVAN; SCHREIER; TEMES, 2017). Limitations in this implementation come from the imperfections of the transfer functions, not perfectly canceling the error of previous stages. The nomenclature of this type of implementation describes each of the stages order, for example, 2-1 MASH  $\Sigma\Delta M$  (LONGO; COPELAND, 1988) stands for a second order loop followed by a first order loop, or 2-1-1 MASH  $\Sigma\Delta M$  (ORTMANNS; GERFERS; MANOLI, 2005) stands for a second order loop followed by two first order loops.

### **Band-Pass Modulators**

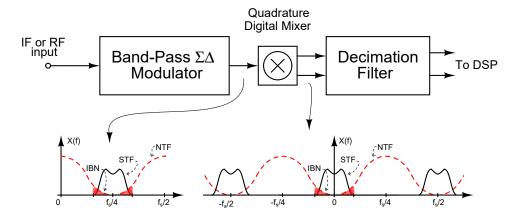

The quantization noise can also be shaped as a band-pass filter as opposed to a high-pass filter described in the previous sections. This type of  $\Sigma\Delta$  ADC is usually employed in the digitization of Intermediate Frequency (IF) or RF signals in wireless receivers due to its frequency selectivity, allowing for more modest requirements (PAVAN; SCHREIER; TEMES, 2017).

As depicted in Fig. 2.11, the IF or RF signal goes through the band-pass modulator where the quantization noise surrounds the desired signal spectrum, then a digital quadrature mixer shifts the signal band to DC, resulting both in the in-phase and quadrature components. Next the resulting signal goes through a digital low-pass filter and the decimation process occurs.

Figure 2.11: Band-pass ΣΔ ADC (PAVAN; SCHREIER; TEMES, 2017).

According to (PAVAN; SCHREIER; TEMES, 2017), the advantage of band-pass  $\Sigma\Delta M$  in wireless receivers, is that the first IF is digitized, reducing the complexity of a superheterodyne architecture to that of a direct conversion receiver without incurring the power and complexity penalties of adaptive digital processing.

#### Continuous Time Modulators

Continuous Time (CT) integrators can also be used in  $\Sigma\Delta M$ . CT- $\Sigma\Delta M$  can achieve higher sampling rates with lower power consumption compared to equivalent Discrete Time (DT)  $\Sigma\Delta M$  (ROSA, 2018) and for this reason have become more common in state-of-the-art high speed  $\Sigma\Delta M$ s. In general DT modulators are more common in high precision  $\Sigma\Delta$  ADCs where a high resolution is required.

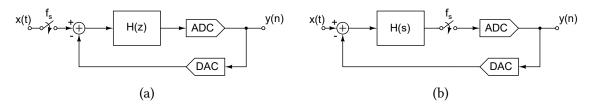

The most significant difference between DT and CT is the location of the sampling operation, depicted in Fig. 2.12, where for DT modulators it occurs at the input of the system, performed by S&H circuit, whereas for CT modulators it is performed before the quantization operation, allowing for CT integrators to be used.

Fig. 2.8 shows the circuit implementation of a first order CT- $\Sigma\Delta M$ . Compared to the its DT counterpart of Fig. 2.8, the only difference is the use of a CT integrator. Combined with the amount of DT- $\Sigma\Delta M$ s reported in the literature compared to CT- $\Sigma\Delta M$ s and the relative simplicity in the changes from DT to CT modulators, transformations from the Z-domain to S-domain have been developed for designing CT- $\Sigma\Delta M$ s starting from the DT loop filter (ORTMANNS; GERFERS, 2006).

Figure 2.12: Comparison between (a) DT modulator; (b) CT modulator (ROSA, 2018).

Figure 2.13: Example of implementation of a continuous time  $\Sigma \Delta M$ .

### 2.2.3 Digital Blocks of the $\Sigma\Delta$ ADC

For a complete ADC a decimation filter is required, as depicted in the complete ADC scheme of Fig. 2.6. The output of the modulator, although, already a digital signal, presents an oversampled waveform containing both the original signal band, and the noise shaped quantization error. To remove the quantization error, a low-pass filter (for high-pass noise shaping) is required, and to reduce the output data rate down to the Nyquist rate, a decimation operation must be performed.

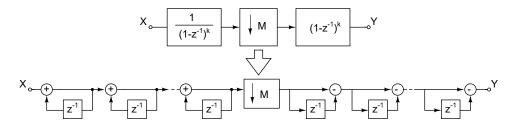

These operations (filtering and decimation) are implemented in the same digital block, by Cascade-Integrator-Comb (CIC) structures shown in Fig. 2.14, only requiring digital delays and adders. The Z-domain transfer function of the CIC structures is given by

$$H_{CIC}(z) = \frac{1 - z^{-M}}{1 - z^{-1}}. (2.25)$$

This transfer function is also known as the SINC filter

$$SINC_M^k(z) = \left(\frac{1-z^{-M}}{1-z^{-1}}\right)^k,$$

(2.26)

Figure 2.14: Block diagram of a k-order ( $sinc^k$ ) CIC decimation filter (ROSA, 2018).

where M is the decimation factor and k is the order of the filter. (PAVAN; SCHREIER; TEMES, 2017).

# 2.3 Other Popular AD Conversion Techniques

In this section, a few of the main topologies and techniques being used today in state-of-the-art non- $\Sigma\Delta$  ADCs will be reviewed, describing its basic operation, highlighting its advantages and challenges during the design. Due to the context of this works, examples of reconfigurability in different topologies will also be highlighted.

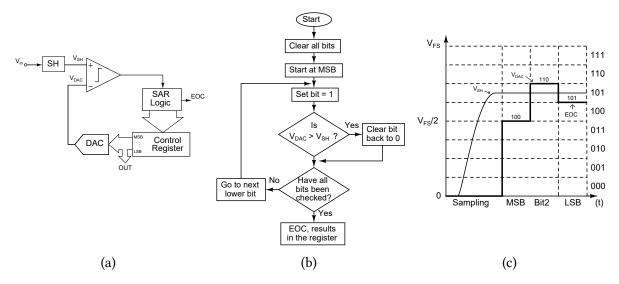

### 2.3.1 Successive Approximation Register

The Successive Approximation Register (SAR) ADC is by far the most popular topology for Analog-to-Digital conversion. Its operation is very simple, basically performing a binary search though all quantization levels successively until it reaches its final digital answer (BAKER, R. J., 2010). In detail, its operation based on Fig.2.15a is: first the analog input  $V_{in}$  is sampled by a sample and hold circuit. At the first sample the voltage  $V_{SH}$  will be compared with the result of the conversion of the Most Significant Bit (MSB) by the DAC  $V_{DAC}$ . If  $V_{DAC} > V_{SH}$  the SAR logic will register this bit as 1 and select the next MSB. If  $V_{DAC} < V_{SH}$  the logic will register the bit as 0. The process is repeated with the next MSB until all bits are checked. Then an End of Conversion (EOC) bit will flag 1, indicating the end of conversion. The flowchart of the SAR operation is described in Fig. 2.15b (J.TOCCI; WIDMER; MOSS, 2007). The waveform of a 3-bit SAR ADC is depicted in Fig. 2.15c where an analog input between  $6V_{FS}/8$  and  $5V_{FS}/8$  is converted. Each step of the conversion increases the precision of the comparison totaling  $(N + 1) \times$  clock cycles as the total conversion time.

Due to its reliance on high precision and high speed of comparison, the design bottleneck of this topology relies on the accuracy of the analog circuitry containing the S&H

Figure 2.15: Successive approximation register ADC. (a) Diagram, (b) flowchart (J.TOCCI; WIDMER; MOSS, 2007), (c) conversion waveform (MALOBERTI, 2007).

(non-linearity), comparator (offset, hysteresis and comparison time) and DAC (mismatch). SAR ADCs often require complex bootstrapping circuits for the S&H switches, and calibration techniques for both the comparator and the DAC. The accuracy requirements also affect the layout implementation, demanding careful matching of the analog components.

The SAR topology is the most versatile topology achieving both high resolutions and high speeds with relatively simple design, reaching up to 18 bits of resolution in lower sampling rates (HUMMERSTON; HURRELL, 2017) and sample rates in the scale of GHz with lower resolutions (7 bits) (RAMKAJ et al., 2018) without the use of time-interleaved techniques. For this reason the SAR ADC is the most popular topology for applications in any frequency range that require resolutions below 20 bits.

#### **Examples of Reconfigurability**

There are few reported works on reconfigurability in SAR ADCs. An example is found in (LIU et al., 2021) where the ADC trades 1 bit of resolution to double its data rate, where one mode presents 60 MS/s with 9 bits resolution mode and another mode with 120 MS/s with 8 bits resolution. Another interesting example is found in (SHEN et al., 2018) where a SAR topology varying the resolution from 10 to 12 bits and the sampling rate from 20 to 80 MS/s. However the bandwidth variation is achieved through the time-interleaving technique, which can be employed in other ADC topologies as well. Other works such as (HU et al., 2019) and (YIP; CHANDRAKASAN, 2013) propose reconfigurability only through the

resolution variation, not varying the output data rate. Another solution found in (TANG et al., 2021) employs a pipelined SAR topology to achieve 0.4 to 40 MS/s with linear power consumption scaling with 12.3 bits of resolution.

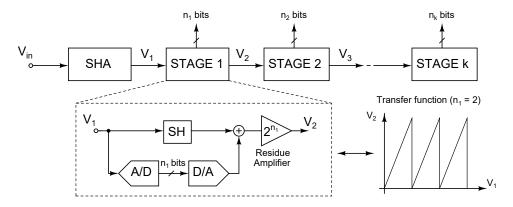

### 2.3.2 Pipeline

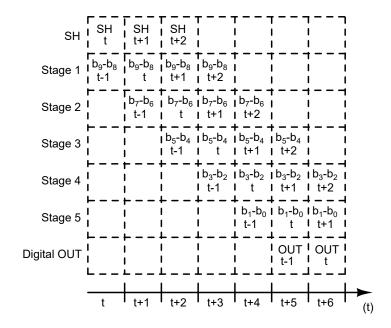

The pipeline converter uses a cascade of conversion stages where each of this stages performs the low-resolution conversion of a fraction of the total number of bits of the complete ADC. Fig. 2.16 (CHIU; GRAY; NIKOLIC, 2004) shows the diagram of a k-Stages Pipeline ADC where each stage converts two bits and the total number of bits is defined by  $n_1 + n_2 + ... + n_k$ .

The basic operation of each stage is also highlighted in Fig. 2.16 where the input voltage  $V_1$  is subtracted from the Analog-to-Digital-to-Analog conversion of the same signal. The result of this operation is passed to the subsequent stage, amplified by the residue amplifier to the full-scale range of the ADC. This is important because it allows the sharing of and identical reference throughout the pipeline stages. This reliance on the amplification in each stage also relaxes the impact of circuit non-idealities such as noise, non-linearity and offset, in the later stages of the pipeline (CHIU; GRAY; NIKOLIC, 2004). The timing diagram of Fig. 2.17 taken from (MALOBERTI, 2007) shows the sequential control of a 10-bit, 5 stages, 2-bit per stage pipeline ADC. The analog input is sampled at the t-th clock cycle, the first stage converts bits  $b_9$  and  $b_8$  at the (t+1)-th clock cycle, bits  $b_7$  and  $b_6$  are converted at the next clock cycle and so on, until the 10 bit conversion of the initial analog input signal is achieved at the (t+6)-th clock cycle. The total conversion time is dependent on the total number stages.

The conversion accuracy of Pipeline ADCs depend on the precision of the residual signal, thus mismatch on the D/A conversion components, offset of comparators and amplifiers are the main limiting factors in pipeline ADC resolution. Also for the conversion speed the settling time of the residue amplifiers are the main limiting factors (CHIU; GRAY; NIKOLIC, 2004).

#### **Examples of Reconfigurability**

Reconfigurability in Pipeline ADCs are more common when compared to SAR topologies. A recent example is (HERSHBERG et al., 2020) where the Pipeline ADC maintains its 11 bit target with a SNR of 59.8 across a sampling frequency range varying from 1MS/s up to 1GS/s. In this example, however, the power consumption does not scale with sampling frequency variation, staying at 10.9 mW for every frequency.

Figure 2.16: 2-bits per stage Pipeline ADC diagram (CHIU; GRAY; NIKOLIC, 2004).

Figure 2.17: Pipeline timing diagram (MALOBERTI, 2007).

### 2.3.3 Time-Interleaving

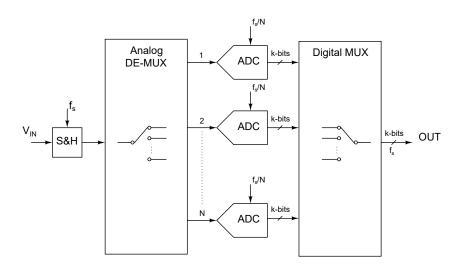

Time-Interleaving is technique applied to ADCs to increase the conversion speed by using a number of parallel slower speed ADCs simultaneously. The architecture is shown in Fig 2.18. The input is sampled at a frequency  $f_s$  higher than what the individual ADCs are capable of converting. The analog demultiplexer distributes the input signal to each parallel ADCs, and the digital multiplexer sequentially selects the output of each channel to obtain the full speed digital word (MALOBERTI, 2007). The maximum conversion rate is dependent on the number of parallel ADCs.

This technique is becoming ubiquitous in state-of-the-art ultra high speed ADCs due to the challenges of reaching high speeds in traditional topologies such as SAR, Pipeline and  $\Sigma\Delta$ . The technique is often used to multiply the output data rate achieving speeds in the magnitude

Figure 2.18: Time-Interleaved architecture diagram (MALOBERTI, 2007).

of tens of Giga Samples per Second (GS/s). An example is (XU; ZHOU; CHIU, 2017) where 24 GS/s is achieved with 6 bit resolution using time-interleaving with SAR ADCs with 23 mW of power consumption. (SUN et al., 2019) achieves 56 GS/s with 8 bits with 702 mW of power consumption also using SAR ADCs. An example of Pipeline ADCs being used with time-interleaving is found in (WANG, X. et al., 2019) where 14 bits of resolution with 500 MS/s are obtained. Now for  $\Sigma\Delta$  ADCs, (DAYANIK; WEYER; FLYNN, 2017) shows an ADC achieving 5 GS/s with 11 bits of resolution and 233 mW of power comsumption.

#### **Examples of Reconfigurability**

Reconfigurability becomes an obvious opportunity for time-interleaved ADCs due to its parallel nature. The work in (DANESH et al., 2011) shows a reconfigurable ADC employing the time-interleaved technique to achieve 1GSps 7-bit, 500MSps 8-bit, and 250MSps 9-bit with 400 fJ/step for each configuration. (HSU et al., 2007) presents a pipeline ADC using time-interleaving to achieve reconfigurability with 1.1 GS/s with 7 bits, 550 MS/s with 7 bits and 550 MS/s with 5 bits with a power consumption of 46 mW, 30 mW and 13 mW respectively.

# 2.4 Recent Trends in ADC Design

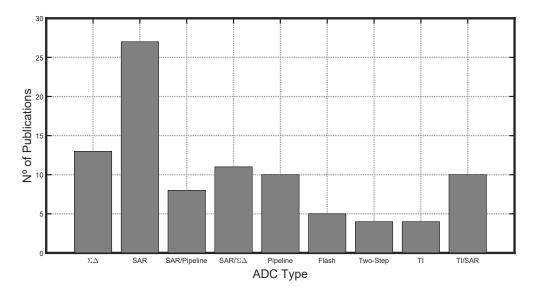

In regards to the recent trends in state-of-the-art Analog-to-Digital Converters, a review of publications in the Journal of Solid State Circuits from January of 2018 to December 2021 was carried out, totaling 48 issues. Fig. 2.19 shows the results. In total 95 ADC papers were

Figure 2.19: Compilation of papers related to ADCs published in the *Journal of Solid State Circuits* since 2018.

published, with a notorious advantage to projects that employ SAR type ADCs. A very interesting trend is the use of topologies that use two or three techniques, for example, the use of SAR with noise shaping ( $\Sigma\Delta$  modulation), or SAR and Pipeline, and even examples of Pipelined ADCs that employ SAR with noise shaping. Overall, the  $\Sigma\Delta$  topology still is very popular, ranking in second, and the noise shaping technique is very popular in SAR ADCs. A few examples of techniques that only appeared once or twice (for example ramp ADC and a  $\Delta$  modulation ADC) were not included in the graph.

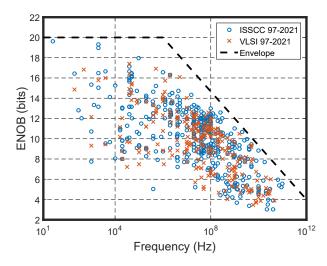

$\Sigma\Delta$  ADCs, due to its necessity of an oversampling frequency much larger than Nyquist, are not the best alternative for applications that require high frequency (e.g. hundreds of MHz to GHz) as shown by Fig. 2.20 from (MURMANN, 2022) where a survey of all reported ADCs in the International Solid-States Circuits Conference (ISSCC) and the IEEE Symposium on VLSI Technology and Circuits are documented since 1997. Generally the  $\Sigma\Delta$  topology is dominant in low frequency applications such as audio devices, CMOS camera sensors and instrumentation, where high precision is more important. Nevertheless, this type of ADC is still viable for wireless receivers up to 4G standards (e.g. LTE-A with 20 MHz bandwidth), as shown by (BETTINI et al., 2015), (LI et al., 2013) e (CROMBEZ et al., 2010). To obtain even higher frequencies in reconfigurable ADCs, innovations employing hybrid topologies have been reported in (JIE; ZHENG; FLYNN, 2012) and (TAO; RUSU, 2015) combining  $\Sigma\Delta$  with Pipeline, SAR with noise shapping in (JIE; ZHENG; FLYNN, 2019) and (SONG et al., 2020), and of course time-interleaving using  $\Sigma\Delta$  ADCs in (DAYANIK; WEYER; FLYNN, 2017).

Figure 2.20: State-of-the-art ADCs in relation to resolution versus bandwidth from (MURMANN, 2022).

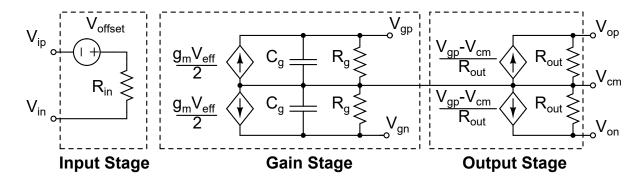

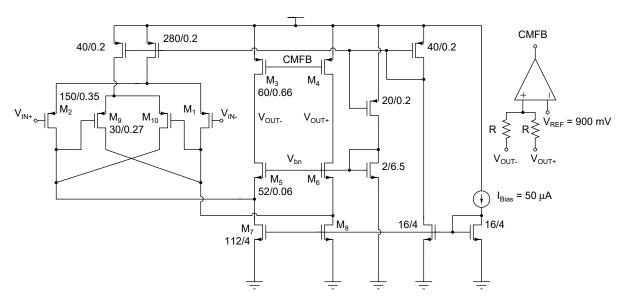

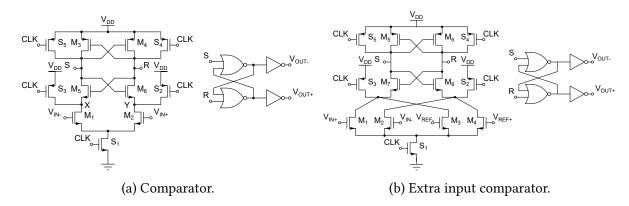

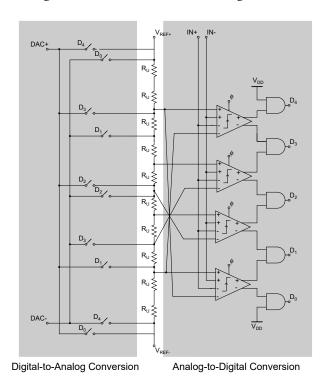

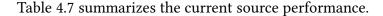

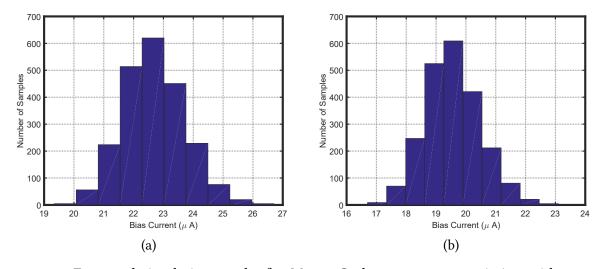

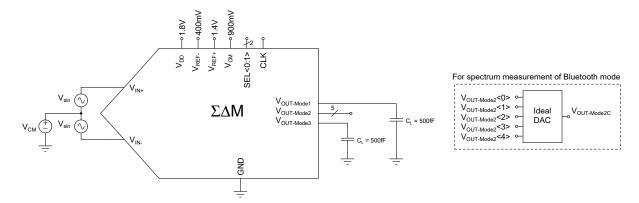

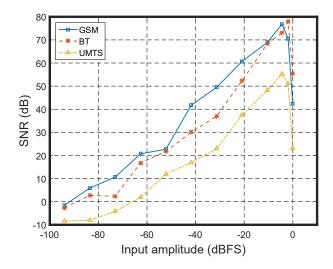

# 2.5 Main Bibliography for the Project