## Bruno Cardoso Lopes

"Design and evaluation of compact ISAs"

"Estudo e avaliação de conjuntos de instruções compactos"

CAMPINAS 2014

#### University of Campinas Institute of Computing

#### Universidade Estadual de Campinas Instituto de Computação

#### Bruno Cardoso Lopes

### "Design and evaluation of compact ISAs"

Supervisor: Orientador(a):

Prof. Dr. Rodolfo Jardim de Azevedo

# "Estudo e avaliação de conjuntos de instruções compactos"

PhD Thesis presented to the Post Graduate Program of the Institute of Computing of the University of Campinas to obtain a Doutor degree in Computer Science.

Tese de Doutorado apresentada ao Programa de Pós-Graduação em Ciência da Computação do Instituto de Computação da Universidade Estadual de Campinas para obtenção do título de Doutor em Ciência da Computação.

This volume corresponds to the final version of the Thesis defended by Bruno Cardoso Lopes, under the supervision of Prof. Dr. Rodolfo Jardim de Azevedo.

ESTE EXEMPLAR CORRESPONDE À VERSÃO FINAL DA TESE DEFENDIDA POR BRUNO CARDOSO LOPES, SOB ORIENTAÇÃO DE PROF. DR. RODOLFO JARDIM DE AZEVEDO.

Supervisor's signature / Assinatura do Orientador(a)

Kodola Amido

CAMPINAS 2014

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca do Instituto de Matemática, Estatística e Computação Científica Maria Fabiana Bezerra Muller - CRB 8/6162

Lopes, Bruno Cardoso, 1985-

L881d Design and evaluation of compact ISAs / Bruno Cardoso Lopes. – Campinas,

SP: [s.n.], 2014.

Orientador: Rodolfo Jardim de Azevedo.

Tese (doutorado) – Universidade Estadual de Campinas, Instituto de Computação.

1. Arquitetura de computador. 2. Sistemas embutidos de computador. 3. Compressão de dados (Computação). 4. Compiladores (Computadores). I. Azevedo, Rodolfo Jardim de,1974-. II. Universidade Estadual de Campinas. Instituto de Computação. III. Título.

#### Informações para Biblioteca Digital

**Título em outro idioma:** Estudo e avaliação de conjuntos de instruções compactos **Palavras-chave em inglês:**

Computer architecture

Embedded computer systems

Data compression (Computer science)

Compiling (Electronic computers)

**Área de concentração:** Ciência da Computação **Titulação:** Doutor em Ciência da Computação

Banca examinadora:

Rodolfo Jardim de Azevedo [Orientador]

Jorge Luiz e Silva Roberto A Hexel

Guido Costa Souza de Araujo

Mario Lucio Cortes

**Data de defesa:** 14-03-2014

Programa de Pós-Graduação: Ciência da Computação

## TERMO DE APROVAÇÃO

Defesa de Tese de Doutorado em Ciência da Computação, apresentada pelo Doutorando **Bruno Cardoso Lopes**, aprovada em 14 de março de 2014, pela Banca examinadora composta pelos professores doutores:

Prof. Dr. Jorge Luiz e Silva ICMC / USP

Prof. Dr. Roberto Andre Hexsel DI / UFPR

Prof. Dr. Guido Costa Souza De Araujo IC / UNICAMP

> Prof. Dr. Mario Lucio Cortes IC / UNICAMP

Prof. Dr. Rodolfo Jardim de Azevedo

## Design and evaluation of compact ISAs

#### Bruno Cardoso Lopes<sup>1</sup>

March 14, 2014

#### Examiner Board/Banca Examinadora:

- Prof. Dr. Rodolfo Jardim de Azevedo (Supervisor/Orientador)

- Prof. Dr. Jorge Luis e Silva ICMC - USP São Carlos

- Prof. Dr. Roberto A. Hexsel DI UFPR

- Prof. Dr. Guido Araújo IC - UNICAMP

- Prof. Dr. Mário Lúcio Côrtes IC - UNICAMP

$<sup>^{1}</sup>$ Financial support: CNPQ 131894/2008-0, CAPES 2009 and FAPESP 2009/02270-0

## Abstract

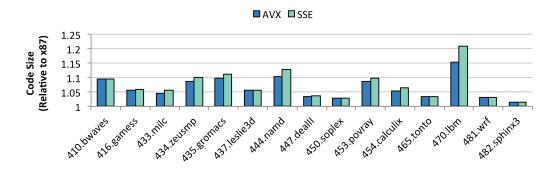

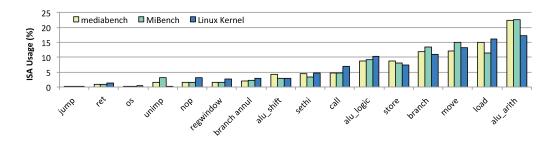

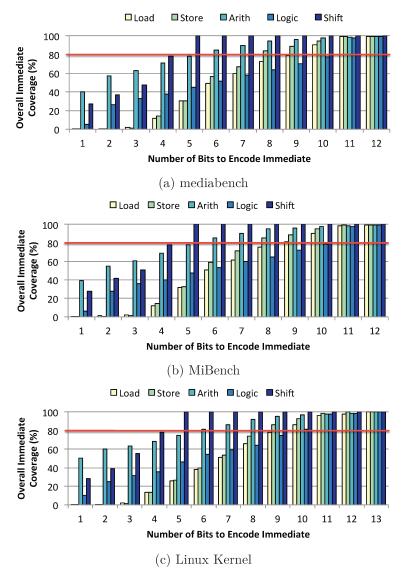

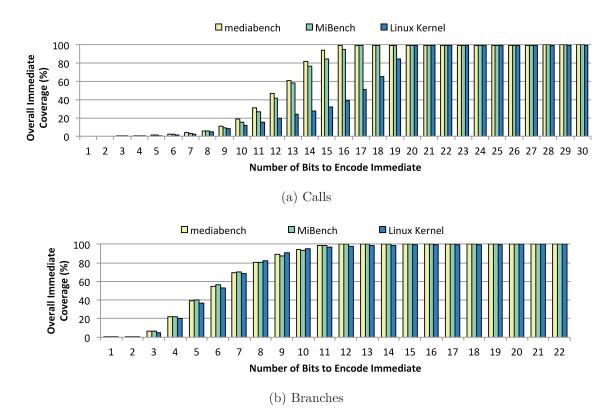

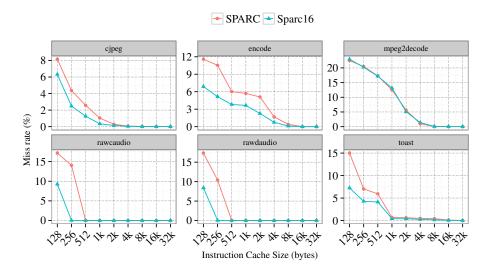

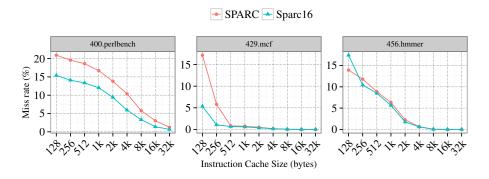

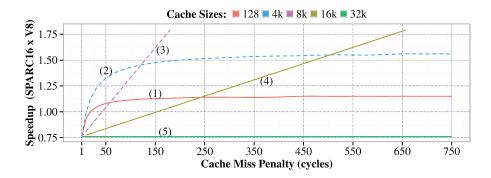

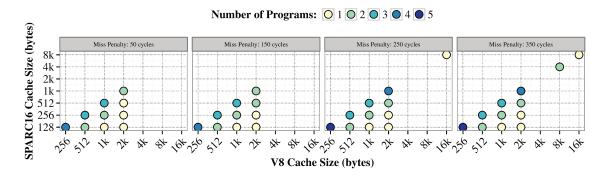

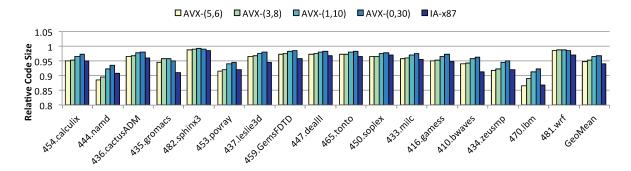

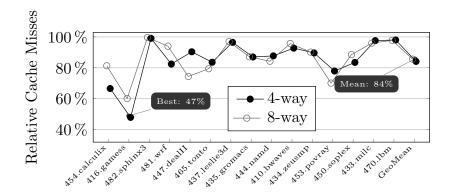

Modern embedded devices are composed of heterogeneous SoC systems ranging from low to high-end processor chips. Although RISC has been the traditional processor for these devices, the situation changed recently; manufacturers are building embedded systems using both RISC - ARM and MIPS - and CISC processors (x86). New functionalities in embedded software require more memory space, an expensive and rare resource in SoCs. Hence, executable code size is critical since performance is directly affected by instruction cache misses. CISC processors used to have a higher code density than RISC since variable length encoding benefits most used instructions, yielding smaller programs. However, with the addition of new extensions and longer instructions, CISC density in recent applications became similar to RISC. In this thesis, we investigate compressibility of RISC and CISC processors, namely SPARC and x86. We propose a 16-bit extension to the SPARC processor, the SPARC16. Additionally, we provide the first methodology for generating 16-bit ISAs and evaluate compression among different 16-bit extensions. SPARC16 programs can achieve better compression ratios than other ISAs, attaining results as low as 67%. SPARC16 also reduces cache miss rates up to 9%, requiring smaller caches than SPARC processors to achieve the same performance; a cache size reduction that can reach a factor of 16. Furthermore, we study how new extensions are constantly introducing new functionalities to x86, leading to the ISA bloat at the cost a complex microprocessor front-end design, area and energy consumption - the x86 ISA reached over 1300 different instructions in 2013. Moreover, analyzed x86 code from 5 Windows versions and 7 Linux distributions in the range from 1995 to 2012 shows that up to 57 instructions get unused with time. To solve this problem, we propose a mechanism to recycle instruction opcodes through legacy instruction emulation without breaking backward software compatibility. We present a case study of the AVX x86 SIMD instructions with shorter instruction encodings from other unused instructions to yield up to 14% code size reduction and 53% instruction cache miss reduction in SPEC CPU2006 floating-point programs. Finally, our results show that up to 40% of the x86 instructions can be removed with less than 5% of overhead through our technique without breaking any legacy code.

## Resumo

Sistemas embarcados modernos são compostos de SoC heterogêneos, variando entre processadores de baixo e alto custo. Apesar de processadores RISC serem o padrão para estes dispositivos, a situação mudou recentemente: fabricantes estão construindo sistemas embarcados utilizando processadores RISC - ARM e MIPS - e CISC (x86). A adição de novas funcionalidades em software embarcados requer maior utilização da memória, um recurso caro e escasso em SoCs. Assim, o tamanho de código executável é crítico, porque afeta diretamente o número de misses na cache de instruções. Processadores CISC costumavam possuir maior densidade de código do que processadores RISC, uma vez que a codificação de instruções com tamanho variável beneficia as instruções mais usadas, os programas são menores. No entanto, com a adição de novas extensões e instruções mais longas, a densidade do CISC em aplicativos recentes tornou-se similar ao RISC. Nesta tese de doutorado, investigamos a compressibilidade de processadores RISC e CISC; SPARC e x86. Nós propomos uma extensão de 16-bits para o processador SPARC, o SPARC16. Apresentamos também, a primeira metodologia para gerar ISAs de 16-bits e avaliamos a compressão atingida em comparação com outras extensões de 16-bits. Programas do SPARC16 podem atingir taxas de compressão melhores do que outros ISAs, atingindo taxas de até 67%. O SPARC16 também reduz taxas de cache miss em até 9%, podendo usar caches menores do que processadores SPARC mas atingindo o mesmo desempenho; a redução pode chegar à um fator de 16. Estudamos também como novas extensões constantemente introduzem novas funcionalidades para o x86, levando ao inchaço do ISA com o total de 1300 instruções em 2013. Além disso, 57 instruções se tornam inutilizadas entre 1995 e 2012. Resolvemos este problema propondo um mecanismo de reciclagem de opcodes utilizando emulação de instruções legadas, sem quebrar compatibilidade com softwares antigos. Incluímos um estudo de caso onde instruções x86 da extensão AVX são recodificadas usando codificações menores, oriundas de instruções inutilizadas, atingindo até 14% de redução no tamanho de código e 53% de diminuição do número de cache misses. Os resultados finais mostram que usando nossa técnica, até 40% das instruções do x86 podem ser removidas com menos de 5% de perda de desempenho.

# Agradecimentos

Dedico esta tese aos meus avós, meus grandes ídolos: João, Carmem, José Galino e Dulce. Vocês me ensinaram a importância da humildade, da fé e da conexão entre as pessoas que amamos. Esta conquista é um pedaço de cada um de vocês.

#### אין עוד מלבדו

- Não existem palavras suficientes para expressar a gratidão e admiração que tenho pelos meus pais Salso e Lídia e à minha irmã Lívia. Meus espelhos. Vos agradeço por tudo, especialmente por acreditarem em mim e me apoiarem por todo esse caminho. Amo vocês. À Aninha, que participou de perto e carinhosamente sempre me incentivou a seguir em frente. À toda minha família, tios e primos, por todo carinho e suporte.

- Ao meu irmão Thiago, que me introduziu à computação na infância, me mostrando os primeiros *hacks*. Sem sua influência eu nunca teria me tornado um cientista. Sem tua companhia, meu amigo, jamais haveria um primeiro passo em direção aos degraus do Altíssimo.

- 3 Ao Leonardo Ecco e ao Rafael Auler pela amizade e por toda dedicação ao trabalho em equipe. Esta tese é fruto do nosso trabalho.

- 7 Aos meus amigos de laboratório: Ecco, Piga, Max, Gabs, Janjão, Auler, Baldas, Klein, George, Nicácio, Raoni e Luiz. Aprendi e me diverti muito com vocês.

- Aos meus amigos da Mansão Wayne: Thiago, João, Gabriel, Ferrugem e Dilly. Depois de tantos anos de conversas sinceras noite adentro, companheirismo e amizade, mais um ciclo se fecha. Vocês me ensinaram muito, serei sempre grato, a lembrança destes tempos será eterna.

- 1 Ao meu orientador Rodolfo, pela qualidade da orientação e por me ensinar a fazer ciência. Às agências de fomento à pesquisa Capes 03/2009-06/2009 e Fapesp 2009/02270-0.

- Às Nuvens Invisíveis; não existe inspiração sem música.

# Contents

| A                | bstra | et :                              | ix  |

|------------------|-------|-----------------------------------|-----|

| R                | esum  |                                   | xi  |

| $\mathbf{A}_{i}$ | grade | cimentos                          | iii |

| 1                | Intr  | oduction                          | 1   |

|                  | 1.1   | RISC: SPARC16                     | 2   |

|                  | 1.2   | CISC: The x86 recycling mechanism | 3   |

|                  | 1.3   | Contributions                     | 4   |

|                  | 1.4   | Organization                      | 5   |

|                  | 1.5   | Considerations                    | 5   |

| 2                | Bas   | c Concepts and Related Work       | 7   |

|                  | 2.1   | Definitions                       | 7   |

|                  | 2.2   | The SPARC Architecture            | 8   |

|                  |       | 2.2.1 Instructions                | 8   |

|                  |       | 2.2.2 Registers                   | 10  |

|                  |       | 2.2.3 ABI                         | 11  |

|                  | 2.3   | The x86 ISA                       | 13  |

|                  |       | 2.3.1 Instructions                | 13  |

|                  |       | 2.3.2 Execution Modes             | 14  |

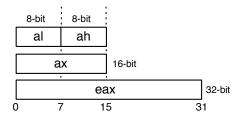

|                  |       | 2.3.3 Registers                   | 14  |

|                  |       | 2.3.4 ISA Extensions              | 15  |

|                  |       | 2.3.5 Implementation              | 15  |

|                  | 2.4   | Code Compression                  | 16  |

|                  |       | 2.4.1 Software                    | 16  |

|                  |       | 2.4.2 Hardware                    | 17  |

|                  | 2.5   | ISA re-encoding                   | 19  |

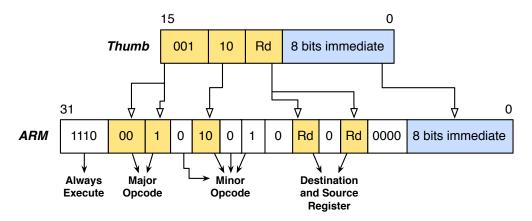

|                  |       | 2.5.1 Thumb and Thumb2            | 20  |

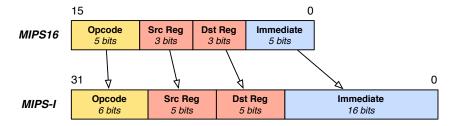

|   |     | 2.5.2 MIPS16 and MicroMIPS                 | 1 |

|---|-----|--------------------------------------------|---|

|   | 2.6 | Compiler Optimizations                     | 2 |

|   | 2.7 | Compression techniques summary             | 4 |

| 3 | Mot | tivation 29                                | 9 |

|   | 3.1 | Code Size Evaluations                      | 9 |

|   | 3.2 | ISA aging problem                          | 1 |

| 4 | An  | nethodology to create 16-bit extensions 38 | 5 |

| - | 4.1 | Methodology                                |   |

|   | 4.2 | Static Analysis                            |   |

|   | 1.2 | 4.2.1 ISA Usage                            |   |

|   |     | 4.2.2 Immediate and Register Encoding      |   |

|   | 4.3 | Dynamic analysis                           |   |

|   | 4.4 | Integer Linear Programming Model           |   |

|   | 4.5 | Considerations                             |   |

|   | 4.0 | Considerations                             | J |

| 5 | SPA | ARC16 4'                                   | 7 |

|   | 5.1 | Instructions                               | 7 |

|   |     | 5.1.1 Calls and Branches                   | 8 |

|   |     | 5.1.2 Load and Store                       | 8 |

|   |     | 5.1.3 Mode exchange                        | 9 |

|   |     | 5.1.4 The EXTEND mechanism                 | 0 |

|   |     | 5.1.5 SETHI instruction                    | 1 |

|   |     | 5.1.6 Alignment restrictions               | 1 |

|   | 5.2 | Registers                                  | 1 |

|   | 5.3 | Application Binary Interface               | 2 |

|   | 5.4 | Hardware                                   | 3 |

|   | 5.5 | Emulator                                   | 4 |

|   | 5.6 | Toolchain                                  | 5 |

|   |     | 5.6.1 Compiler Frontend and Backend        | 5 |

|   |     | 5.6.2 Linker                               | 5 |

|   |     | 5.6.3 C Library                            | 6 |

|   |     | 5.6.4 The compilation and execution flow   | 6 |

|   | 5.7 | Compiler Optimizations                     | 7 |

|   |     | 5.7.1 Delay slots                          | 7 |

|   |     | 5.7.2 Instruction size reducer             | 8 |

|   |     | 5.7.3 Assembler relaxation                 | 8 |

|   |     | 5.7.4 Mixed Stack Access                   | 9 |

|   | 5.8 | Evalua     | ation                                          | 61 |

|---|-----|------------|------------------------------------------------|----|

|   |     | 5.8.1      | Compression Ratios                             | 61 |

|   |     | 5.8.2      | Instruction Cache Behavior                     | 63 |

|   |     | 5.8.3      | Performance Estimation                         | 64 |

|   | 5.9 | Consid     | derations                                      | 67 |

| 6 | The | <b>X86</b> | Recycling Mechanism                            | 69 |

|   | 6.1 | Radica     | al Approaches                                  | 69 |

|   |     | 6.1.1      | (A) Reduce all Operation Codes to 2 bytes      | 70 |

|   |     | 6.1.2      | (B) Reduce all Operation Codes to 1 or 2 bytes | 70 |

|   |     | 6.1.3      | (C) Convert to a RISC-like ISA encoding        | 71 |

|   |     | 6.1.4      | Evaluation                                     | 71 |

|   |     | 6.1.5      | Re-encoding and Backward Compatibility         | 72 |

|   | 6.2 | Recyc      | ling mechanism                                 | 73 |

|   |     | 6.2.1      | Instruction lifetime cycle                     | 73 |

|   |     | 6.2.2      | Operation Code Revisions and Orthogonality     | 74 |

|   |     | 6.2.3      | Backward compatibility                         | 76 |

|   |     | 6.2.4      | Revision Vector and Trap Mask                  | 76 |

|   |     | 6.2.5      | Trap Mechanism                                 | 78 |

|   | 6.3 | Hardy      | vare                                           | 80 |

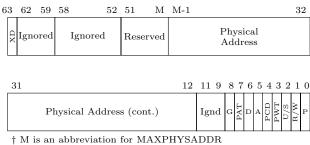

|   |     | 6.3.1      | Page Table extension                           | 80 |

|   |     | 6.3.2      | Processor Front-end                            | 81 |

|   |     | 6.3.3      | Verification                                   | 82 |

|   |     | 6.3.4      | ISA Domain Specialization                      | 82 |

|   | 6.4 | Softwa     | are                                            | 82 |

|   |     | 6.4.1      | Assembler and Linker                           | 82 |

|   |     | 6.4.2      | Operating System Loader                        | 82 |

|   |     | 6.4.3      | Emulation Routines                             | 83 |

|   | 6.5 | Securi     | ity implications                               | 83 |

|   | 6.6 |            | ations                                         | 84 |

|   | 6.7 | Evalua     | ation                                          | 84 |

|   |     | 6.7.1      | Methodology                                    | 84 |

|   |     | 6.7.2      | Static Analysis                                | 86 |

|   |     | 6.7.3      | Dynamic Analysis                               | 88 |

|   |     | 6.7.4      | Performance Impact                             | 89 |

|   |     | 6.7.5      | Case study: AVX Re-encoding                    | 93 |

|   | 6.8 |            | derations                                      | 95 |

|   | ٠.٠ |            |                                                |    |

| 7            | Con   | clusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97 |

|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | 7.1   | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98 |

|              | 7.2   | Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 99 |

|              | 7.3   | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 |

| Bi           | bliog | raphy 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01 |

| $\mathbf{A}$ | Stat  | ic Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 |

|              | A.1   | Instruction Usage By Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11 |

| В            | SPA   | ARC16 ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15 |

|              | B.1   | List of SPARC16 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 |

|              |       | $B.1.1  ADDCCri\_ext, \ ADDCCrr, \ ADDri\_ext, \ ADDrr\_ext, \ ADDRR_ext, \ ADDRR_ex$ | 15 |

|              |       | B.1.2 ADDFP, ADDFP_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16 |

|              |       | B.1.3 ADDSP, ADDSP_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16 |

|              |       | B.1.4 ADDXri, ADDXri_ext, ADDXrr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16 |

|              |       | B.1.5 ANDri, ANDri_ext, ANDrr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17 |

|              |       | B.1.6 ANDNrr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

|              |       | B.1.7 BCC, BCC_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18 |

|              |       | B.1.8 BA, BA_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18 |

|              |       | B.1.9 BE, BE_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18 |

|              |       | B.1.10 BNE, BNE_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19 |

|              |       | B.1.11 CALL, CALL_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19 |

|              |       | B.1.12 CALLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 |

|              |       | B.1.13 CALLRX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19 |

|              |       | B.1.14 CALLX, CALLX_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20 |

|              |       | B.1.15 CMPri, CMPri_ext, CMPrr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20 |

|              |       | B.1.16 JMPR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20 |

|              |       | B.1.17 JMPRX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21 |

|              |       | B.1.18 LDri, LDri_ext, LDrr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21 |

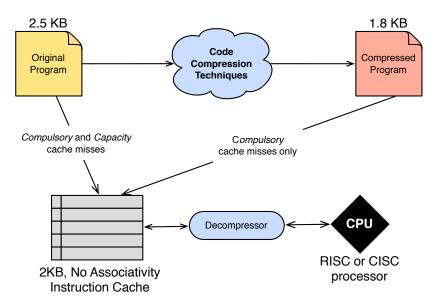

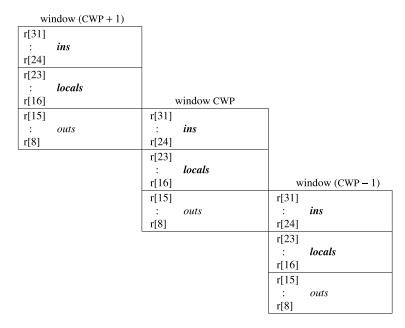

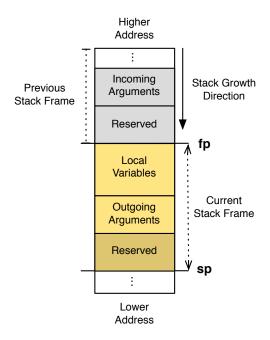

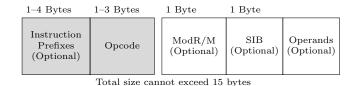

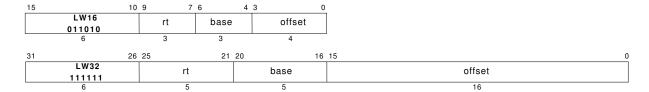

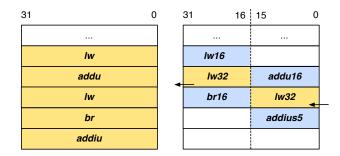

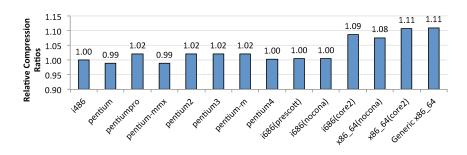

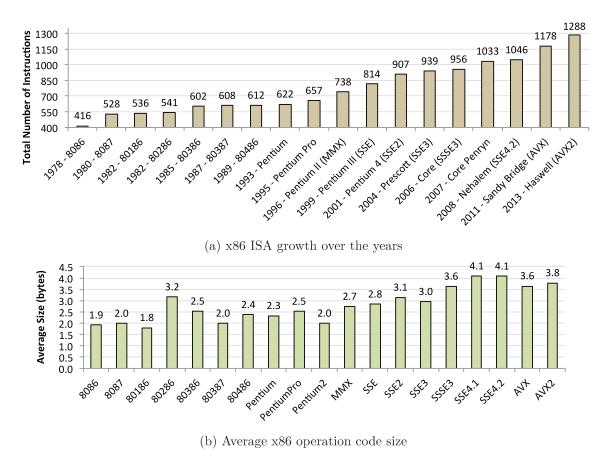

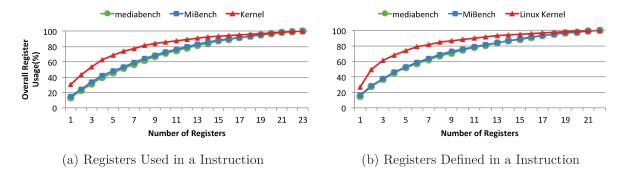

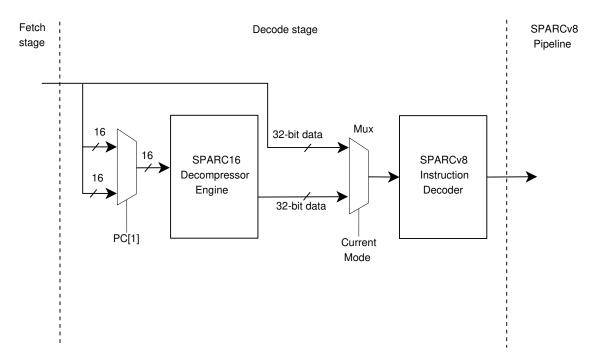

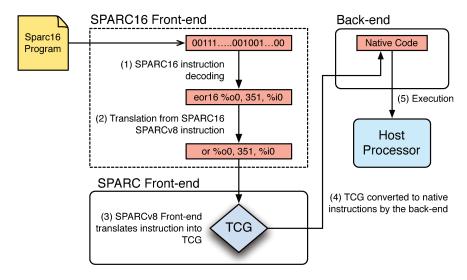

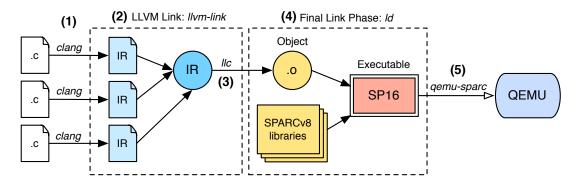

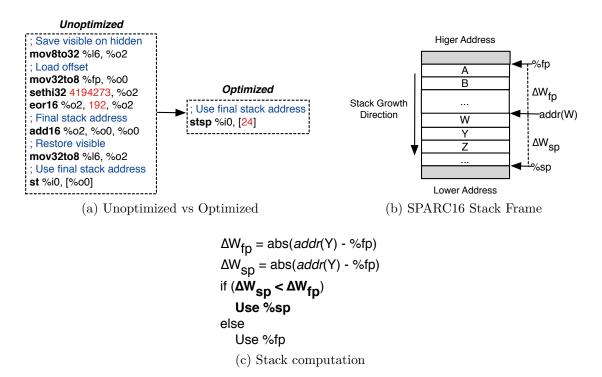

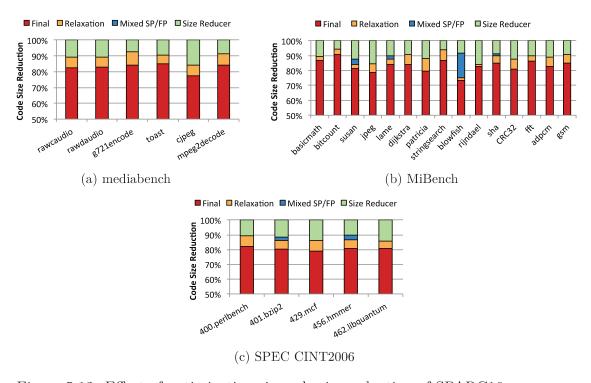

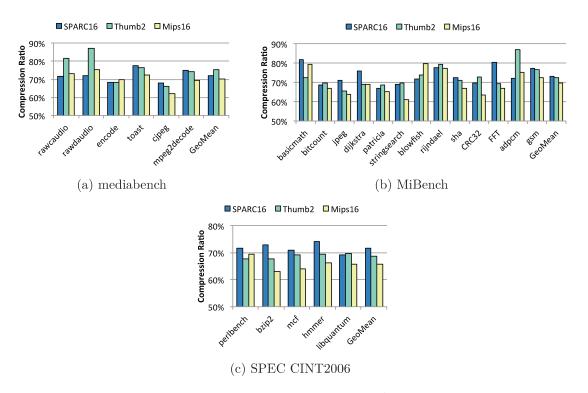

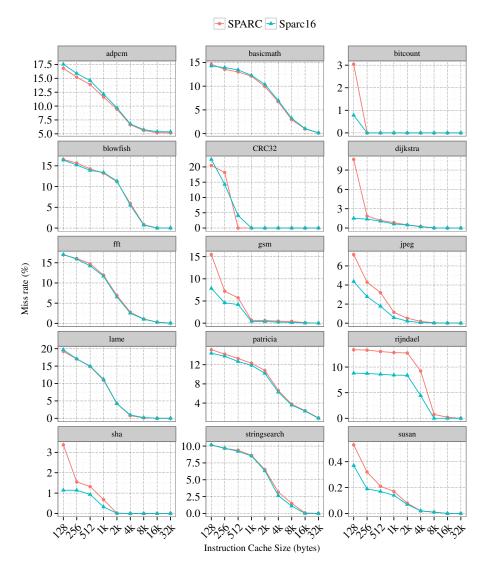

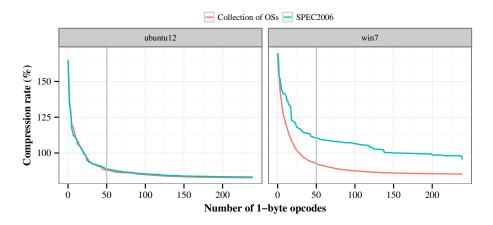

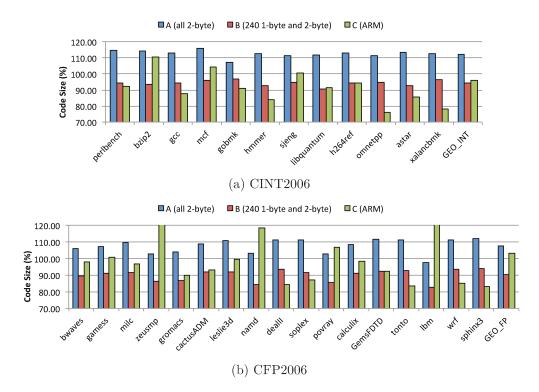

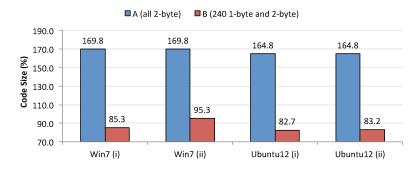

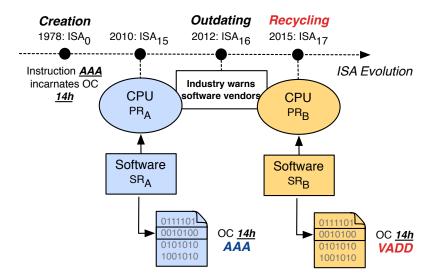

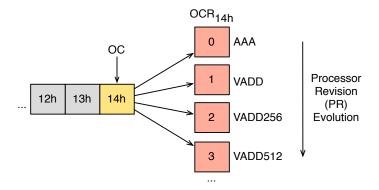

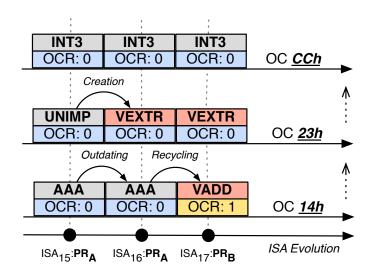

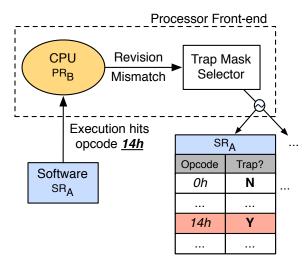

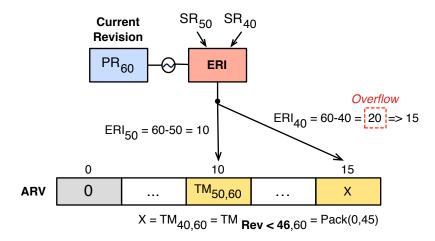

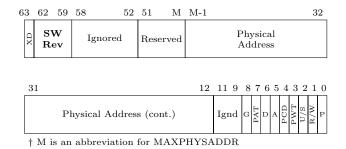

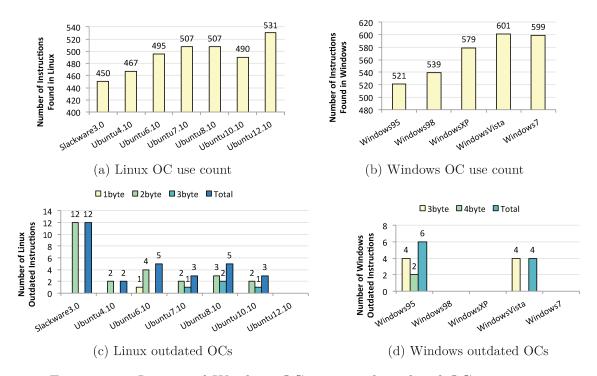

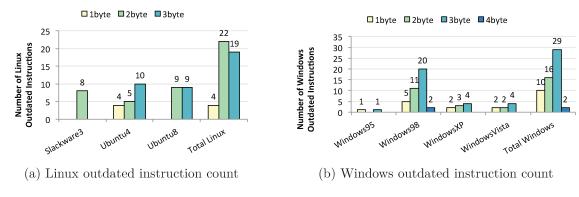

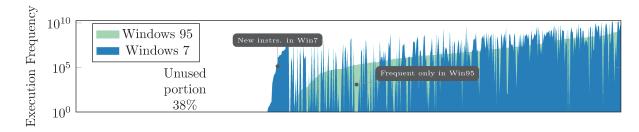

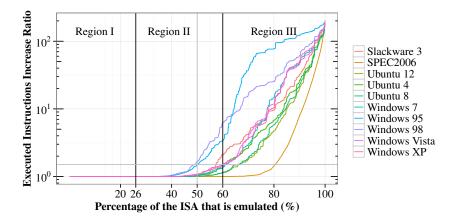

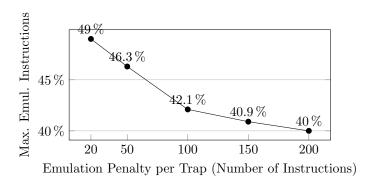

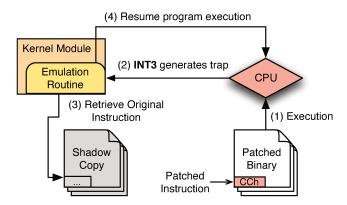

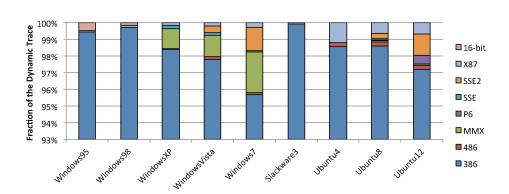

|              |       | B.1.19 LDFP, LDFP_ext                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |