| Este      | exemplar                    | correspo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | onda s   | redação     | defandida            |

|-----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|----------------------|

| Tese/     | Dissertaçã                  | o devidan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Jandy    | 1 constant  |                      |

| por:      | 10                          | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | -           | -                    |

|           |                             | da Banca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Examin   | edora.      | 1-20                 |

|           | provada                     | de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | anline   |             | _ de _4024           |

| Cam       | plnas,                      | Tue -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | F.)         |                      |

|           | 1                           | Je                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - No     | DADUAC      | 50                   |

|           | code                        | DENADOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DE PUS-C | MADUAY      |                      |

|           | 1.00                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CFG-IC   | No. Members | CONTRACTOR OF STREET |

| - Indiana | ARREST OF PERSONS ASSESSED. | and the same of th | 1        |             | 1                    |

Uma Arquitetura para Execução de Código Comprimido em Sistemas Dedicados

Rodolfo Jardim de Azevedo

Tese de Doutorado

#### Instituto de Computação Universidade Estadual de Campinas

### Uma Arquitetura para Execução de Código Comprimido em Sistemas Dedicados

### Rodolfo Jardim de Azevedo<sup>1</sup>

18 de junho de 2002

#### Banca Examinadora:

- Guido Costa Souza de Araújo (Orientador)

- Claudionor José Nunes Coelho Júnior

Departamento de Ciência da Computação UFMG

- Edil Severiano Tavares Fernandes COPPE - UFRJ

- Edna Natividade da Silva Barros Centro de Informática - UFPE

- Mario Lúcio Côrtes

Instituto de Computação UNICAMP

- Paulo Cesar Centoducatte

Instituto de Computação UNICAMP

- Ricardo Pannain (suplente)

Instituto de Computação UNICAMP

<sup>&</sup>lt;sup>1</sup>Financiado pela FAPESP, processo 99/09462-8

| UNIDADE  | BR             |

|----------|----------------|

| Nº CHAMA | DATTUNICAMP    |

|          | A325a          |

| V        | _EX_C          |

| TOMBO BO | 149955         |

| PROC 16  | -837/00        |

| C        | DΧ             |

| PREÇO R  | \$11,00        |

| DATA     |                |

| Nº CPD   | CONTROL DIVINE |

CMO0170466-2

BIB 10 246 997

# FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DO IMECC DA UNICAMP

Azevedo, Rodolfo Jardim de

Az25a Uma Arquitetura para Execução de Código Comprimido em Sistemas Dedicados / Rodolfo Jardim de Azevedo -- Campinas, [S.P.:s.n.], 2002.

Orientador: Guido Costa Souza de Araújo

Tese (doutorado) - Universidade Estadual de Campinas, Instituto de Computação.

Arquitetura de computadores.

Sistemas embutidos de computador.

Circuitos integrados.

Compressão de dados (Computação).

Araújo, Guido Costa Souza de. II. Universidade Estadual de Campinas. Instituto de Computação. III. Título.

## Uma Arquitetura para Execução de Código Comprimido em Sistemas Dedicados

Este exemplar corresponde à redação final da Tese devidamente corrigida e defendida por Rodolfo Jardim de Azevedo e aprovada pela Banca Examinadora.

Campinas, 20 de junho de 2002.

Guido Costa Souza de Araújo (Orjentador)

Tese apresentada ao Instituto de Computação, UNICAMP, como requisito parcial para a obtenção do título de Doutor em Ciência da Computação.

### TERMO DE APROVAÇÃO

Tese defendida e aprovada em 18 de junho de 2002, pela Banca Examinadora composta pelos Professores Doutores:

| Cas Culing                                                                                          |  |

|-----------------------------------------------------------------------------------------------------|--|

| Claudionor José Nunes Coelho Júnior<br>DCC - UFMG                                                   |  |

| Felif S. T. Fernandes                                                                               |  |

| Prof. Dr. Edil Severiano Tavares Fernandes<br>COPPE - UFRJ                                          |  |

|                                                                                                     |  |

| Edua Matridade da John Bay<br>Prof <sup>a</sup> . Dr <sup>a</sup> . Edna Natividade da Silva Barros |  |

| Prof <sup>a</sup> . Dr <sup>a</sup> . Edna Natividade da Silva Barros<br>Cln <sub>-</sub> UFPE      |  |

| Mansport                                                                                            |  |

| Prof. Dr. Mário Lúcio Côrtes<br>IC - UNICAMP                                                        |  |

|                                                                                                     |  |

| - Lower Lower to                                                                                    |  |

| Prof. Dr. Paulo César Centoducatte<br>IC - UNICAMP                                                  |  |

|                                                                                                     |  |

Prof. Dr. Guido Costa Souza de Araújo

IC - UNICAMP

© Rodolfo Jardim de Azevedo, 2002. Todos os direitos reservados.

### Resumo

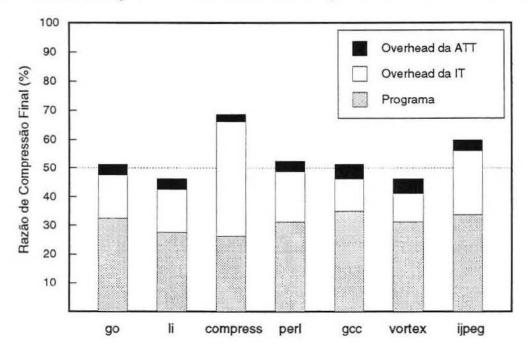

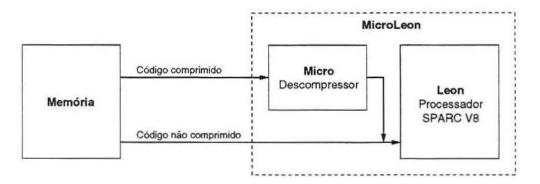

Projetos de sistemas dedicados modernos têm exigido cada vez mais memória de programa para incluir novas funcionalidades como interface com o usuário, suporte a novos componentes. etc. O aumento no tamanho dos programas tem feito com que a área ocupada pela memória em um circuito integrado moderno seja um dos fatores determinantes no seu custo final bem como um dos maiores responsáveis pelo consumo de potência nestes dispositivos. A compressão de código de programa vem sendo considerada como uma estratégia importante na minimização deste problema. Esta tese trata da compressão de programas para execução em sistemas dedicados baseados em arquiteturas RISC. Um amplo estudo demonstra que a utilização do método proposto neste trabalho, Instruction Based Compression (IBC), resulta em boas razões de compressão e implementações eficientes de descompressores. Para a arquitetura MIPS foi obtida a melhor razão de compressão (tamanho final do programa comprimido e do descompressor em relação ao programa original) conhecida (53,6%) utilizando como benchmark programas do SPEC CINT'95. Uma arquitetura pipelined para o descompressor é proposta e um protótipo foi implementado para o processador Leon (SPARC V8). Esta é a primeira implementação em hardware de um descompressor para a arquitetura SPARC, tendo produzido uma razão de compressão de 61,8% para o mesmo benchmark e uma queda de apenas 5,89% no desempenho médio do sistema.

### Abstract

The demand for program memory in embedded systems has grown considerably in recent years, as a result of the need to accommodate new system functionalities such as novel user interfaces, additional hardware devices, etc. The increase in program size has turned memory into the largest single factor in the total area and power dissipation of a modern System-on-a-Chip (SoC). Program code compression has been considered recently a central technique in reducing the cost of memory in such systems. This thesis studies the code compression problem for RISC architectures. A thorough experimental study shows that the Instruction Based Compression (IBC) technique proposed herein results in very good compression ratios and efficient decompressor engine implementations. For the MIPS architecture this approach results in the best compression ratio (size of the compressed program divided by the size of the original program) known in the literature (53.6%), when it is evaluated using the SPEC CINT'95 benchmark programs. A decompressor pipelined architecture was developed and prototyped for the Leon (SPARC V8) processor. This is the first implementation of a hardware decompressor on the SPARC architecture, having resulted in a 61.8% compression ratio for the same benchmark, at the expense of a fairly small performance overhead (5.89% on average).

## Agradecimentos

Gostaria de agradecer ao meu orientador, Guido Araújo, pelo apoio, dedicação, direcionamento, críticas e sugestões durante o doutorado.

Ao professor Paulo Centoducatte pelas críticas e sugestões durante o desenvolvimento deste trabalho e pelas revisões desta tese.

Ao professor Pedro Rezende por ter confiado em mim e pela ajuda na matrícula como aluno especial no segundo semestre de 1998.

À minha família, por todo apoio que recebi e a Deus, pois sem ele nada seria possível.

Aos amigos de república, do Laboratório de Sistemas de Computação e do Instituto de Computação pela ótima convivência, apoio e pelos momentos de descontração.

Ao Instituto de Computação, pelo ambiente de pesquisa do qual participei e pela infra-estrutura que utilizei.

Ao CNPQ, pela bolsa que recebi em 1999 (processo 146200/1999-3). À FAPESP pela bolsa a partir de 2000 (processo 1999/09462-8) e pelos equipamentos fornecidos (processos 1997/10982-0 e 2000/15083-9). À FAEP também pelos equipamentos fornecidos (processos 1123/01 e 1124/01).

$\grave{A}$  minha família.

# Sumário

| R | esum  | 10       |                                          |    |     |   |     |   |   |   |    |    |   |   |   |      | vi   |

|---|-------|----------|------------------------------------------|----|-----|---|-----|---|---|---|----|----|---|---|---|------|------|

| A | bstra | act      |                                          |    |     |   |     |   |   |   |    |    |   |   |   |      | vii  |

| A | grad  | ecimen   | itos                                     |    |     |   |     |   |   |   |    |    |   |   |   | 3    | viii |

| 1 | Intr  | oduçã    | o                                        |    |     |   |     |   |   |   |    |    |   |   |   |      | 1    |

|   | 1.1   | Comp     | ressão de Código e Compressão de Dados   |    |     |   |     |   |   |   | *  |    | , |   |   |      | 3    |

|   | 1.2   | Custo    | s e Benefícios da Compressão de Código . |    |     |   |     |   |   |   |    |    |   |   |   | 1901 | 6    |

|   | 1.3   | Contri   | ibuição                                  |    |     |   | (8) | * | × | k | *  |    | * |   |   |      | 7    |

|   | 1.4   |          | ização                                   |    |     |   |     |   |   |   |    |    |   |   |   |      | 9    |

| 2 | Tra   | balhos   | Relacionados                             |    |     |   |     |   |   |   |    |    |   |   |   |      | 11   |

|   | 2.1   | Parân    | netros de Comparação                     |    | . , |   |     |   |   |   |    | ٠  | ٠ | • | ٠ | *    | 12   |

|   | 2.2   | Traba    | lhos Relacionados                        |    |     |   | *   |   |   |   |    |    | ٠ |   |   | w.,  | 14   |

|   |       | 2.2.1    | Utilizando Instruções Menores            |    |     |   | ٠   |   |   | ÷ |    |    |   | ٠ |   |      | 14   |

|   |       | 2.2.2    | Utilizando Alterações no Software        |    |     |   |     |   | × |   |    | *  |   | ٠ | ٠ | ٠    | 19   |

|   |       | 2.2.3    | Utilizando Compressão do Programa        | 4  |     |   |     |   |   | ¥ | •  |    |   |   |   | ٠    | 23   |

|   |       | 2.2.4    | Outros Trabalhos                         |    |     |   |     |   | , |   |    |    | ¥ |   |   | *    | 30   |

|   | 2.3   | Quadr    | o Comparativo                            | ٠  |     | ٠ |     |   |   | ٠ | ٠  |    | ٠ |   |   | ٠    | 34   |

| 3 | Ana   | álise de | e Técnicas de Compressão                 |    |     |   |     |   |   |   |    |    |   |   |   |      | 39   |

|   | 3.1   | Comp     | ressão Baseada em Árvores (TBC)          |    |     |   |     |   |   |   |    | ٠  |   |   | * |      | 41   |

|   |       | 3.1.1    | Análise do Método TBC                    |    |     |   | -   |   |   |   |    |    |   |   | ٠ |      | 41   |

|   |       | 3.1.2    | O Descompressor Baseado em TBC           |    |     |   |     |   | * |   |    |    |   |   | • |      | 45   |

|   | 3.2   | Comp     | ressão Baseada em Árvores Fatoradas (PB  | C) |     |   |     |   |   |   |    | £3 |   |   |   |      | 47   |

|   |       | 3.2.1    | Análise do Método PBC                    |    |     |   |     |   |   |   | ,  | *  |   |   | * | ٠    | 47   |

|   |       | 3.2.2    | O Descompressor Baseado em PBC           |    |     |   |     |   |   |   | ů. |    | 2 |   |   |      | 53   |

| 4 | Cor   | npressão Baseada em Instruções (MIPS) 57     |

|---|-------|----------------------------------------------|

|   | 4.1   | Análise do Método                            |

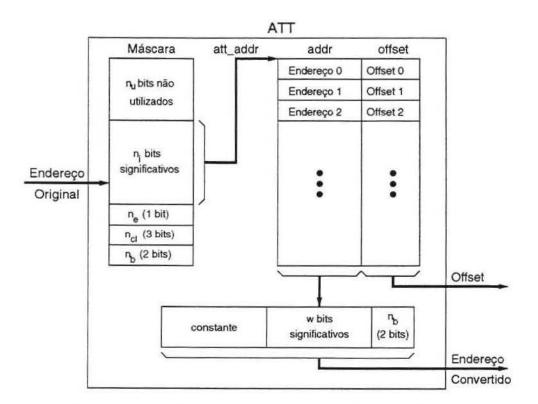

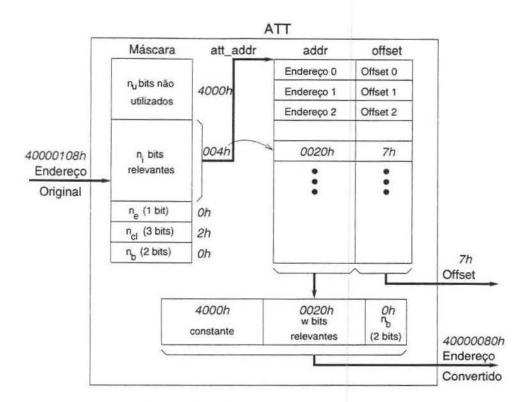

|   | 4.2   | Tabela de Conversão de Endereços             |

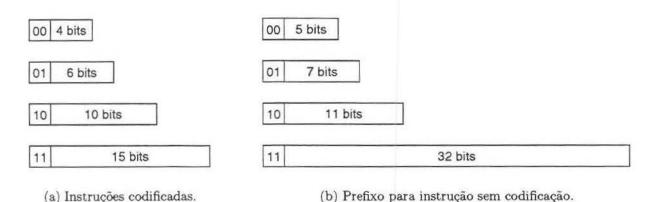

|   | 4.3   | Tabela de Instruções                         |

|   | 4.4   | Descompressor IBC Pipelined para MIPS R4000  |

|   | 4.5   | Um Exemplo do Funcionamento do Descompressor |

|   | 4.6   | Comparação dos Métodos IBC vs. TBC e PBC     |

|   | 4.7   | Comparação entre IBC e Outros Métodos        |

| 5 | Cor   | npressão Baseada em Instruções (SPARC) 95    |

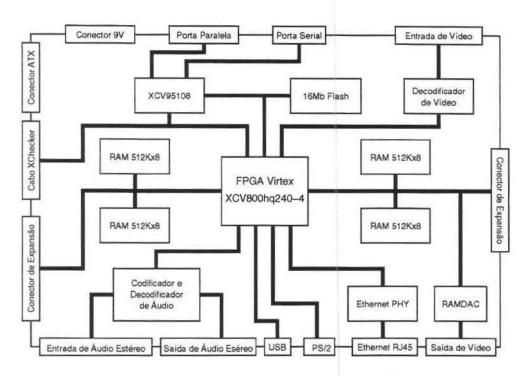

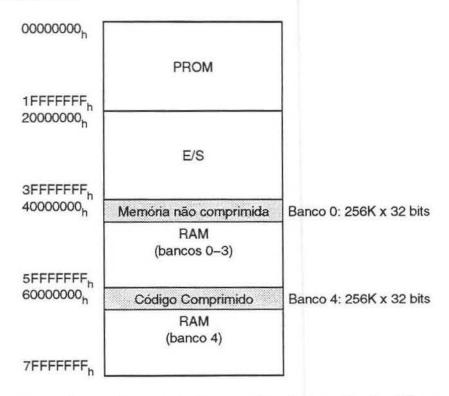

|   | 5.1   | Ambiente de Prototipagem                     |

|   | 5.2   | Análise do Método para SPARC                 |

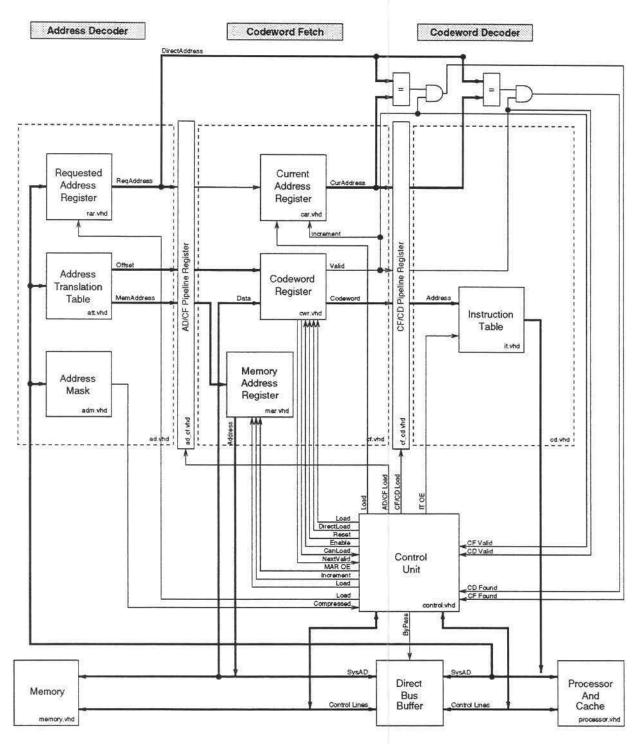

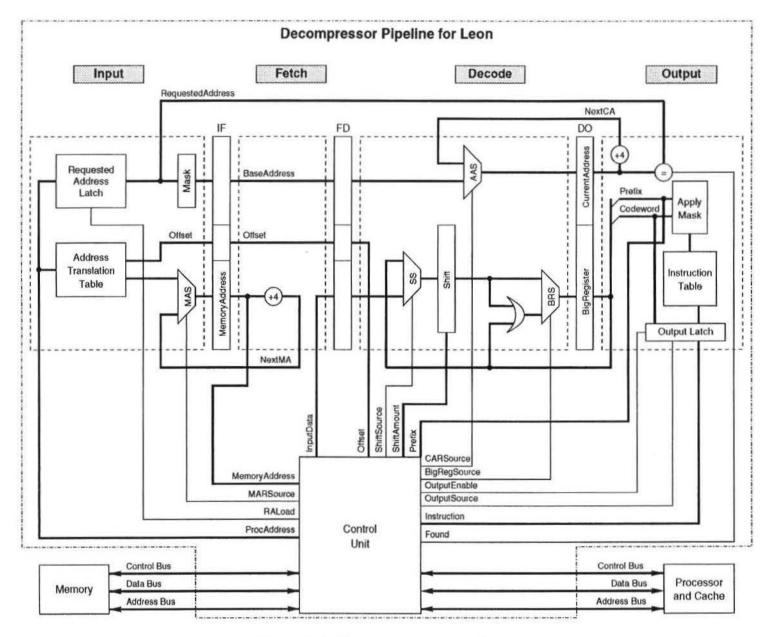

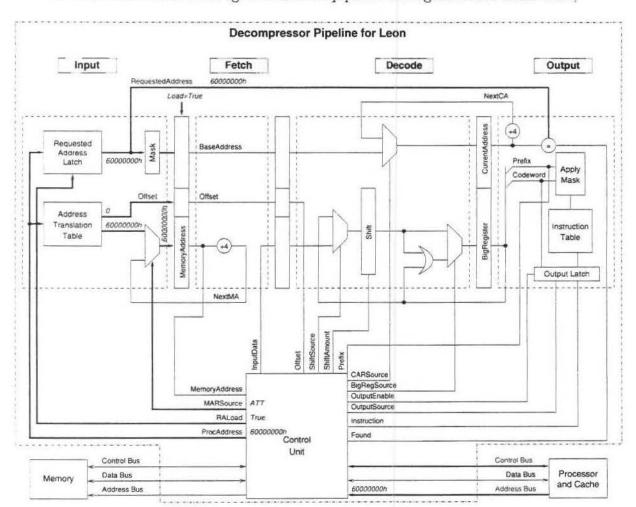

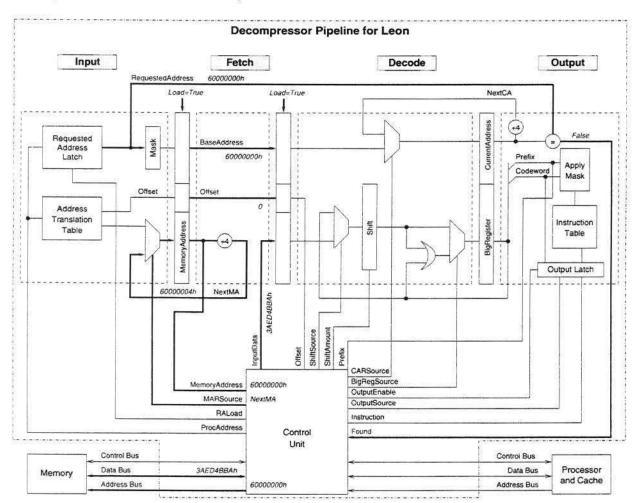

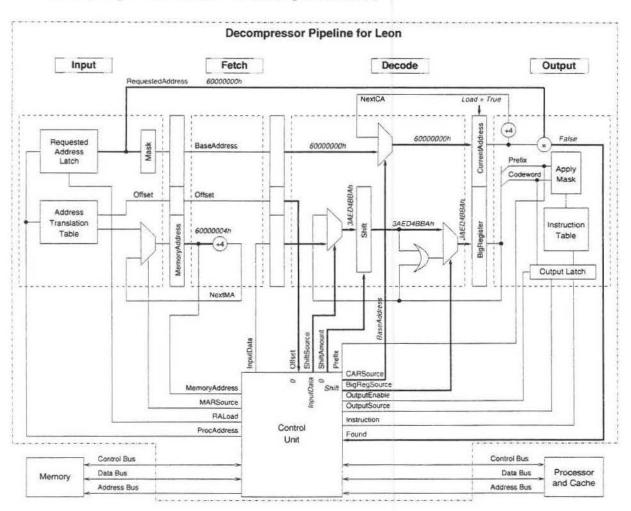

|   | 5.3   | Descompressor IBC pipelined para SPARC V8    |

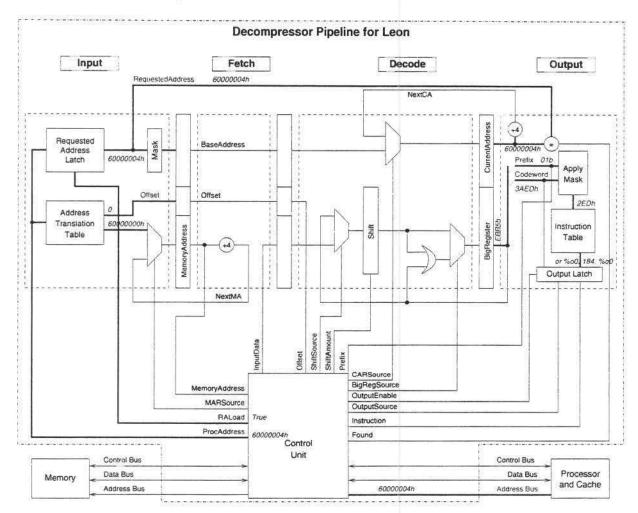

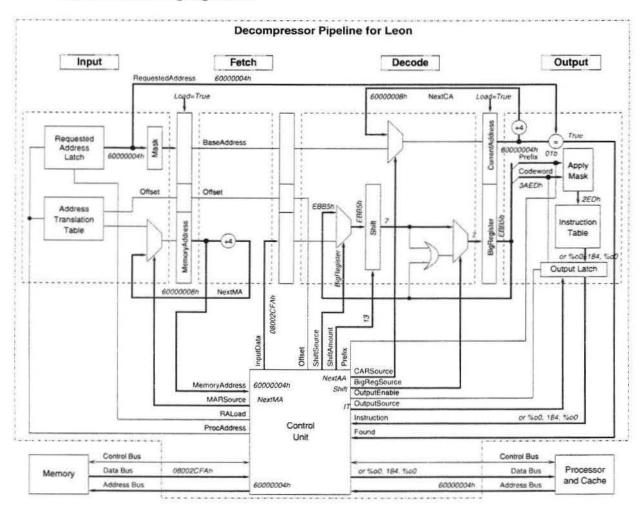

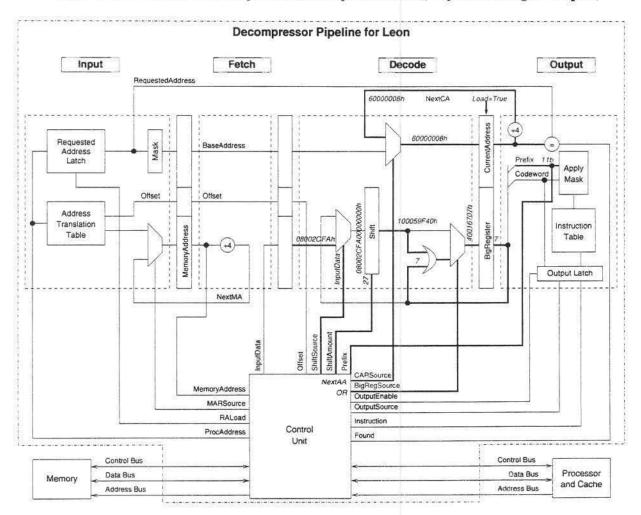

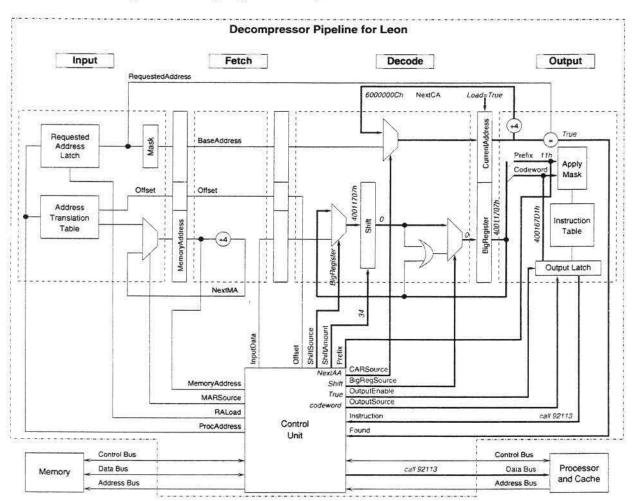

|   | 5.4   | Um Exemplo do Funcionamento do Descompressor |

|   | 5.5   | Análise de Desempenho do Descompressor       |

|   | 5.6   | Comparação entre IBC e Outros Métodos        |

| 6 | Cor   | nclusões e Trabalhos Futuros 127             |

|   | 6.1   | Trabalhos Futuros                            |

| В | iblio | grafia 131                                   |

# Lista de Tabelas

| 2.1 | Quadro comparativo do conjunto de instruções DLXe e D16                   | 15    |

|-----|---------------------------------------------------------------------------|-------|

| 2.2 | Resultados comparativos considerando D16=1.00                             | 15    |

| 2.3 | CodePack: Codificação dos 16 bits mais significativos                     | 28    |

| 2.4 | CodePack: Codificação dos 16 bits menos significativos                    | 28    |

| 2.5 | Quadro comparativo dos métodos de compressão de código                    | 35    |

| 3.1 | Parâmetros utilizados e número de instruções geradas                      | 41    |

| 3.2 | Número de árvores distintas nos programas. Os números entre parênteses    |       |

|     | indicam a porcentagem em relação ao total                                 | 42    |

| 3.3 | Todas as combinações de tamanhos de codewords para o programa li utili-   |       |

|     | zando 4 classes                                                           | 44    |

| 3.4 | Partições que resultam nos melhores resultados para 4 classes e as razões |       |

|     | de compressão obtidas                                                     | 45    |

| 3.5 | Número de padrões de árvores e de operandos. Os números entre parênteses  |       |

|     | mostram a porcentagem em relação ao total de árvores de expressões        | 48    |

| 3.6 | Razão de compressão composta quando os padrões de árvore e de operando    | 14000 |

|     | são combinados                                                            | 53    |

| 4.1 | Número de instruções únicas para a arquitetura MIPS                       | 59    |

| 4.2 | Resultados obtidos para a arquitetura MIPS                                | 67    |

| 4.3 | Exemplo de código a ser comprimido                                        | 82    |

| 4.4 | Quadro comparativo dos métodos de compressão de código                    | 93    |

| 5.1 | Programas específicos para implementação IBC/Leon                         | 97    |

| 5.2 | Rotinas do programa Stanford                                              | 98    |

| 5.3 | Número de instruções únicas para SPARC                                    | 100   |

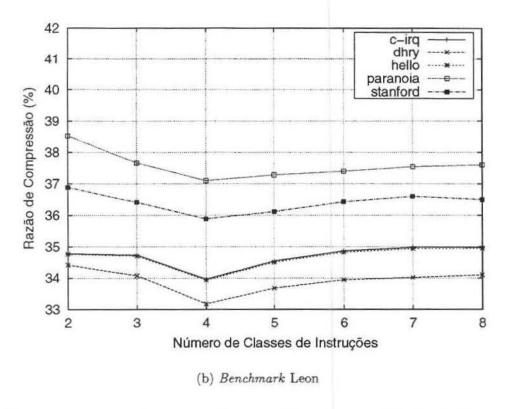

| 5.4 | Resultado da divisão em classes para SPARC                                | 104   |

| 5.5 | Número de instruções que ocorrem uma ou duas vezes no programa            | 105   |

| 5.6 | Razão de compressão para tamanhos diferentes da IT (benchmark SPEC        |       |

|     | CINT'95)                                                                  | 106   |

| 5.7 | Razão de compressão para tamanhos diferentes da IT (benchmark Leon)       | 107   |

|     |                                                                           |       |

| 5.8  | Comparação dos Resultados para as arquiteturas MIPS e SPARC 10 |

|------|----------------------------------------------------------------|

| 5.9  | Exemplo de código a ser comprimido                             |

| 5.10 | Resultados do programa stanford                                |

| 5.11 | Quadro comparativo dos métodos de compressão de código         |

# Lista de Figuras

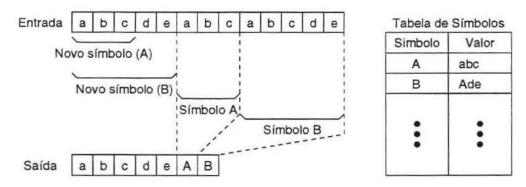

| 1.1  | Exemplo de compressão pelo método Lempel-Ziv                            | 4  |

|------|-------------------------------------------------------------------------|----|

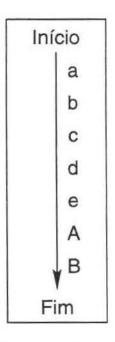

| 1.2  | Seqüência de descompressão de dados e código                            | 5  |

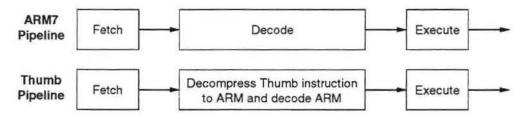

| 2.1  | Pipeline do Thumb e do ARM                                              | 16 |

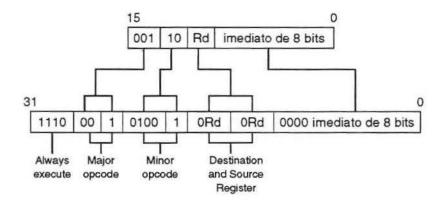

| 2.2  | Instrução ARM ADD Rd, #constante representada nos dois formatos         | 16 |

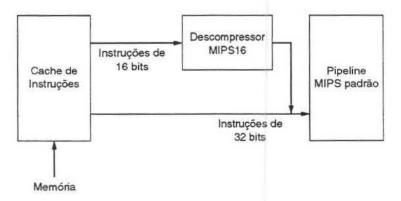

| 2.3  | Diagrama de blocos de um processador MIPS com suporte ao conjunto de    |    |

|      | instruções MIPS16                                                       | 17 |

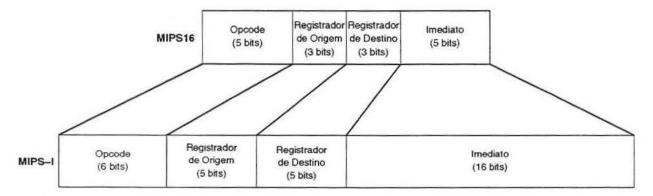

| 2.4  | Conversão de uma instrução MIPS16 para o formato MIPS-I (32 bits)       | 18 |

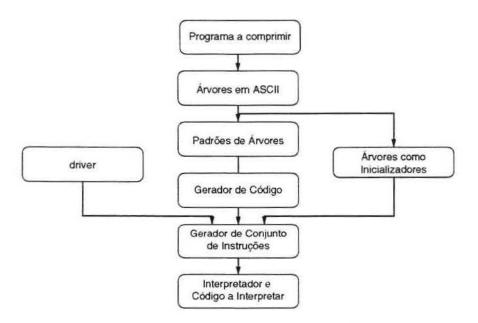

| 2.5  | Sequencia de passos do compilador modificado por Fraser                 | 20 |

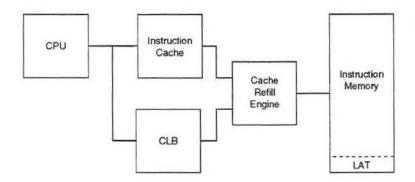

| 2.6  | CCRP: Compressed Code RISC Processor                                    | 24 |

| 2.7  | Organização de uma linha da Line Address Table (LAT)                    | 24 |

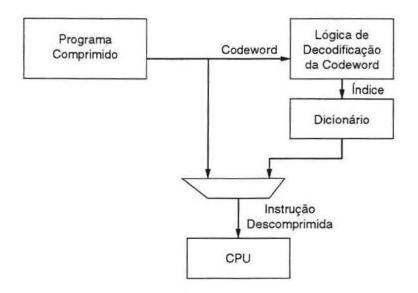

| 2.8  | Processador para execução de programas comprimidos proposto por Lefurgy | 26 |

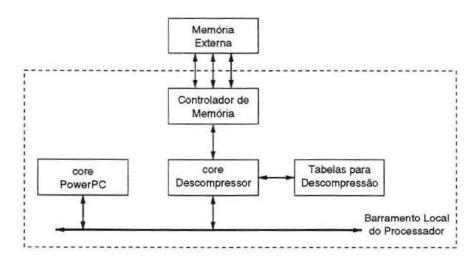

| 2.9  | Arquitetura do IBM CodePack                                             | 28 |

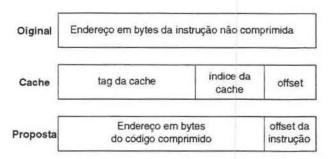

| 2.10 | Interpretações para o Instruction Pointer dadas por Breternitz          | 31 |

| 2.11 | Mapas de memória equivalentes                                           | 32 |

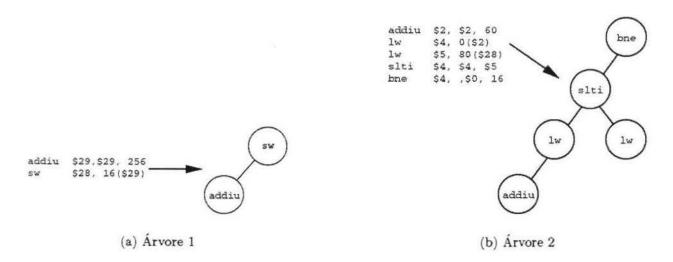

| 3.1  | Exemplos de árvore de Expressão                                         | 40 |

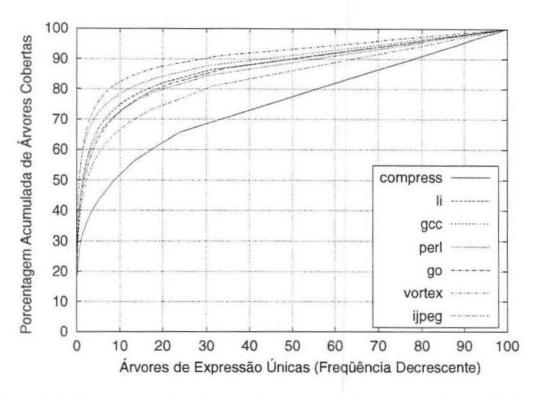

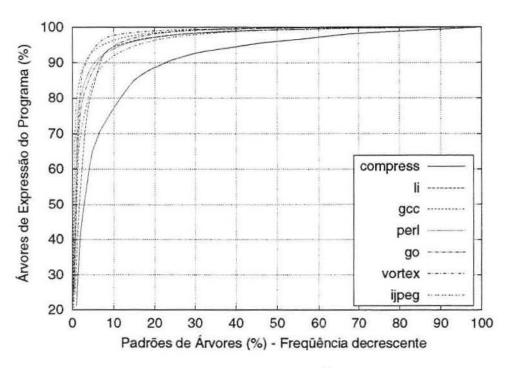

| 3.2  | Porcentagem das árvores do programa cobertas por árvores distintas      | 43 |

| 3.3  | Codificação das árvores                                                 | 43 |

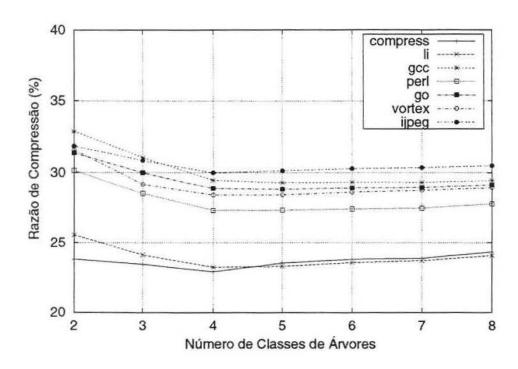

| 3.4  | Razão de compressão para diferentes quantidades de classes de árvores   | 44 |

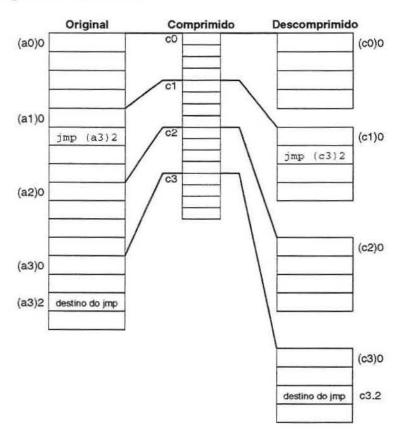

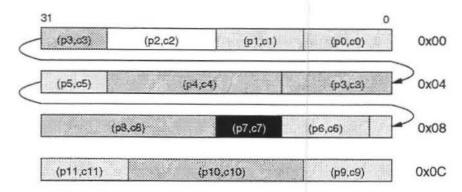

| 3.5  | Árvores comprimidas na memória                                          | 45 |

| 3.6  | Descompressor para o Método de Compressão Baseado em Árvores            | 46 |

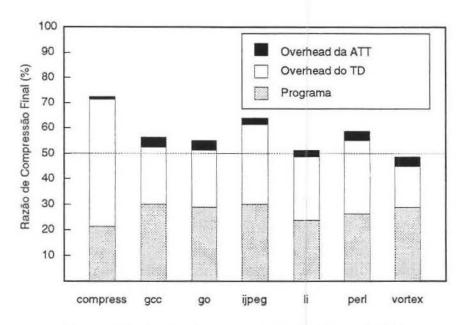

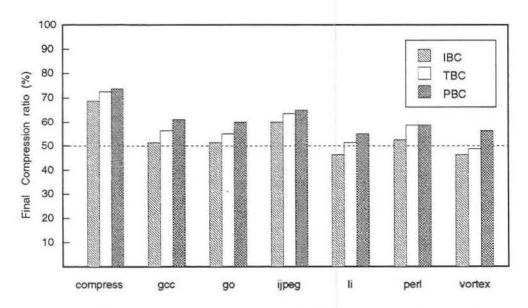

| 3.7  | Razão de compressão final para TBC                                      | 47 |

| 3.8  | (a) Árvore de Expressão; (b) Padrão de árvore; (c) Padrão de operandos  | 48 |

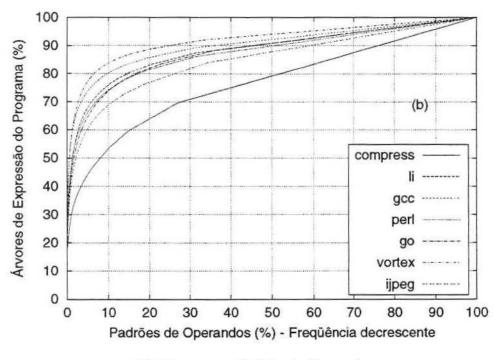

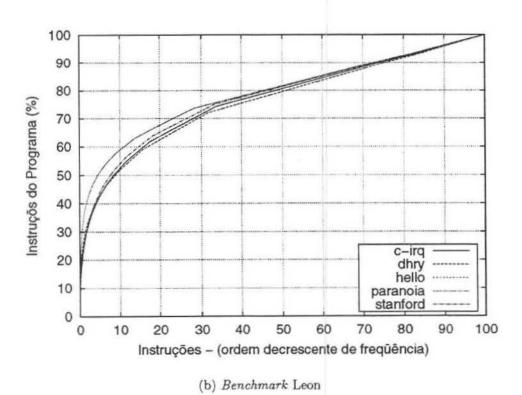

| 3.9  | Porcentagem acumulada das árvores de expressão                          | 50 |

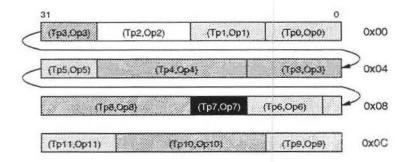

| 3.10 | Padrões de árvores comprimidos na memória.                              | 51 |

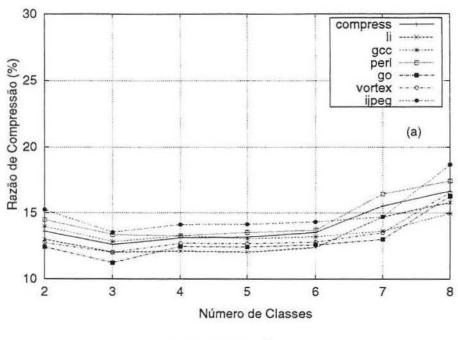

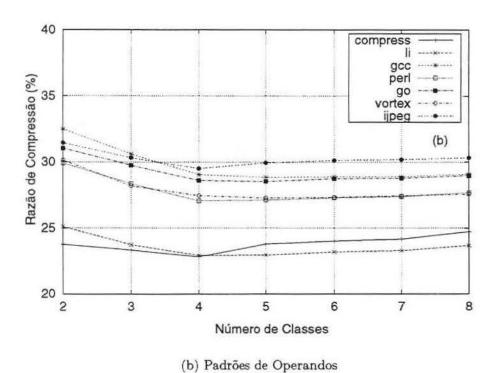

| 3.11 | Razões de compressão com diferentes números de classes                  | 52 |

| 3.12 | Descompressor para o método de Compressão Baseado em Árvores Fato-      |    |

|      | radas (PBC)                                                             | 54 |

| 3.13 | Razão de compressão final para o PBC                                    | 56 |

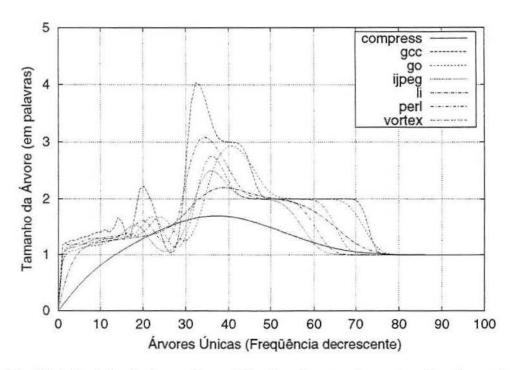

| 4.1  | Distribuição do tamanho médio das árvores de expressões (aproximação de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Bezier)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58 |

| 4.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 |

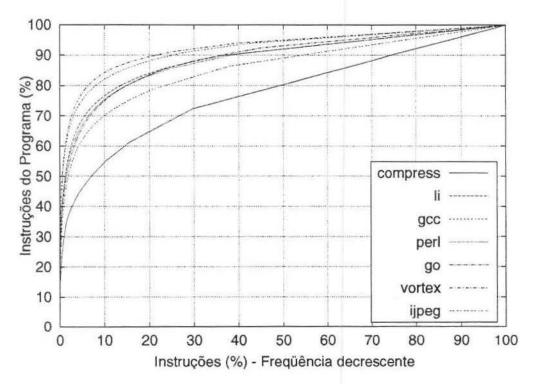

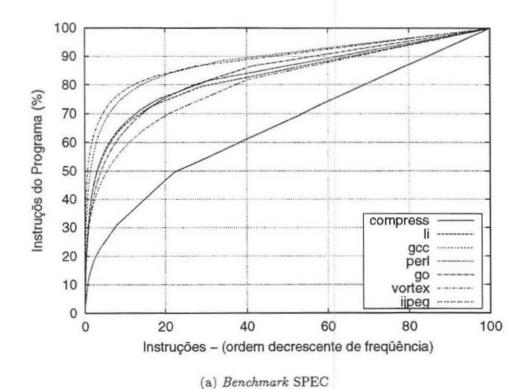

| 4.3  | Porcentagem do programa coberta por instruções distintas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61 |

| 4.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62 |

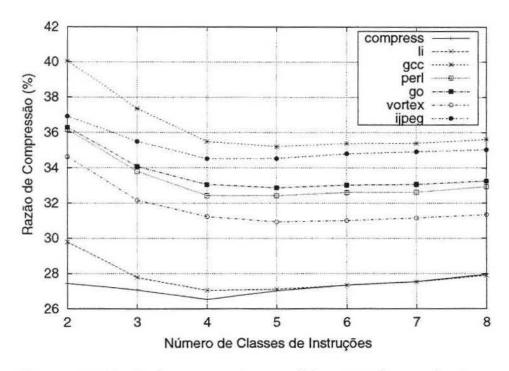

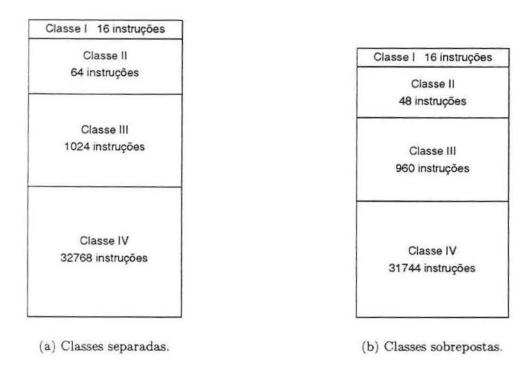

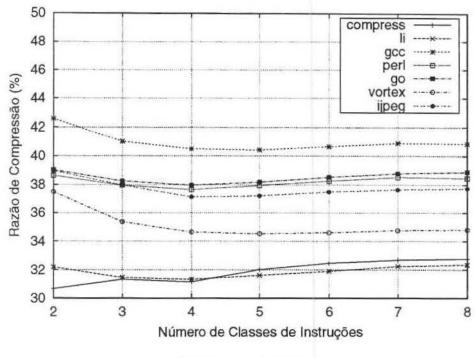

| 4.5  | Razão de compressão para diferentes números de classes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64 |

| 4.6  | 144 No. 14 No. 1 | 65 |

| 4.7  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66 |

| 4.8  | The same of the sa | 68 |

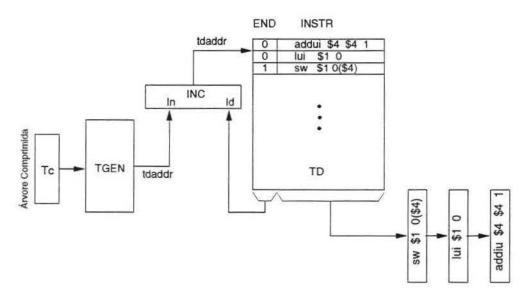

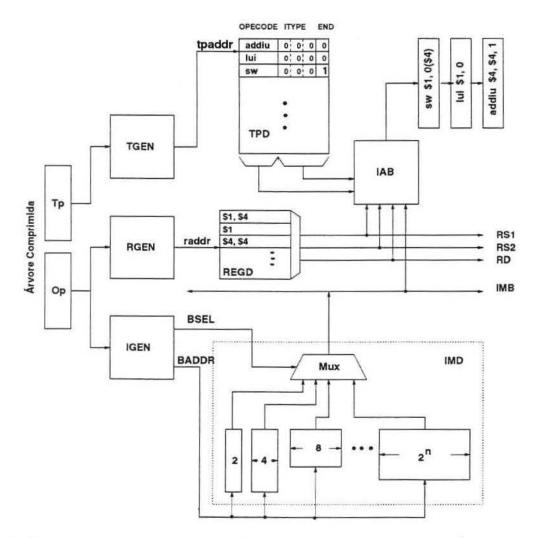

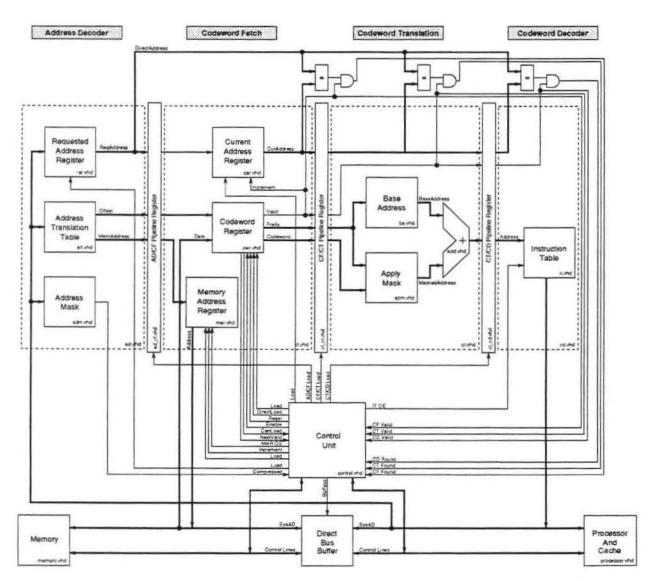

| 4.9  | ALLY DESCRIPTION OF THE PROPERTY OF THE PROPER | 71 |

| 4.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73 |

| 4.11 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74 |

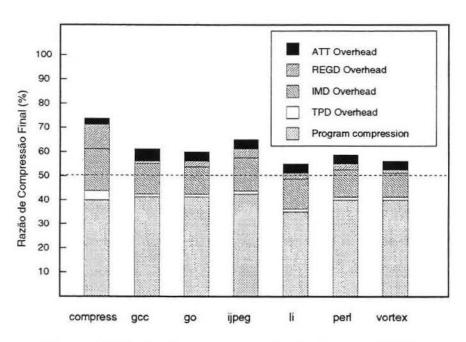

|      | Table to the interpretation of the control of the c | 76 |

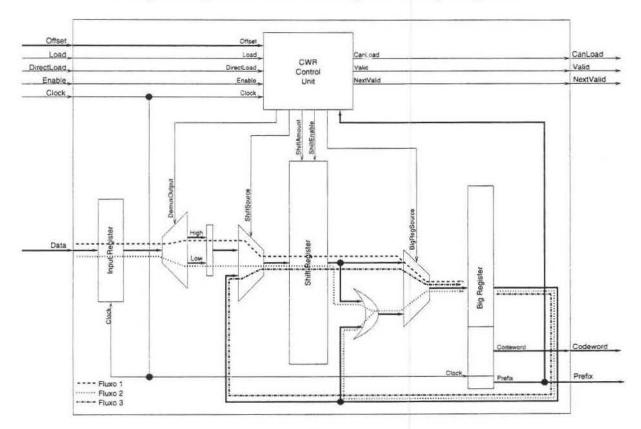

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82 |

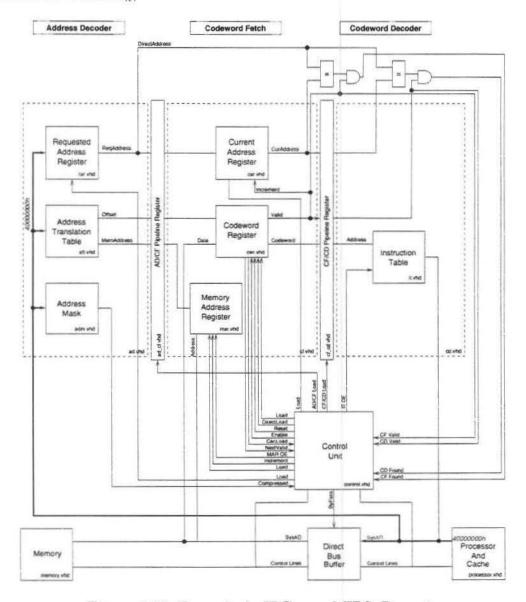

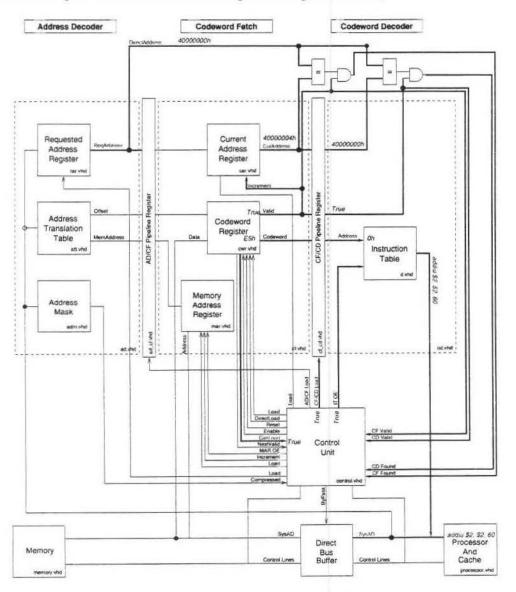

| 4.16 | Exemplo do IBC para MIPS: Passo 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83 |

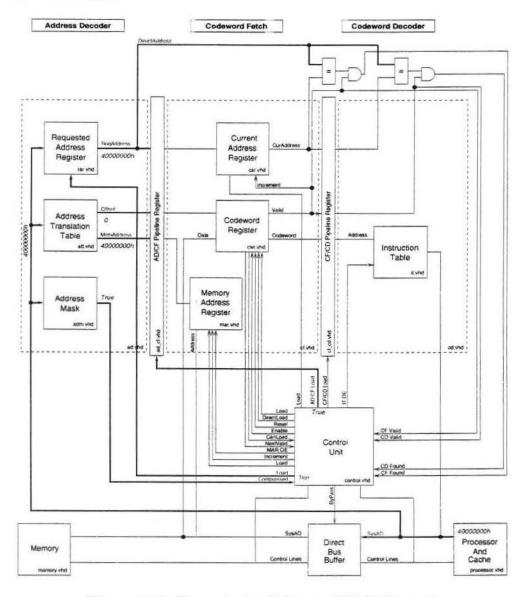

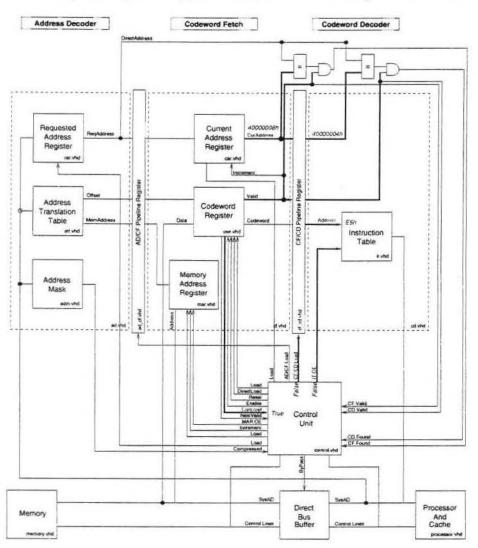

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84 |

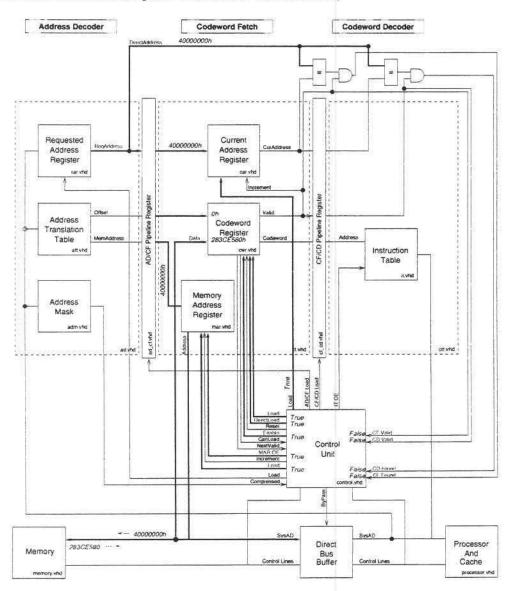

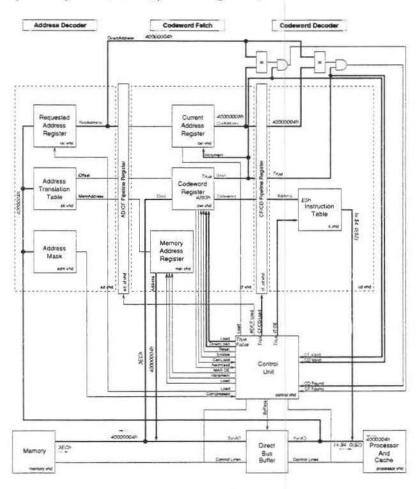

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85 |

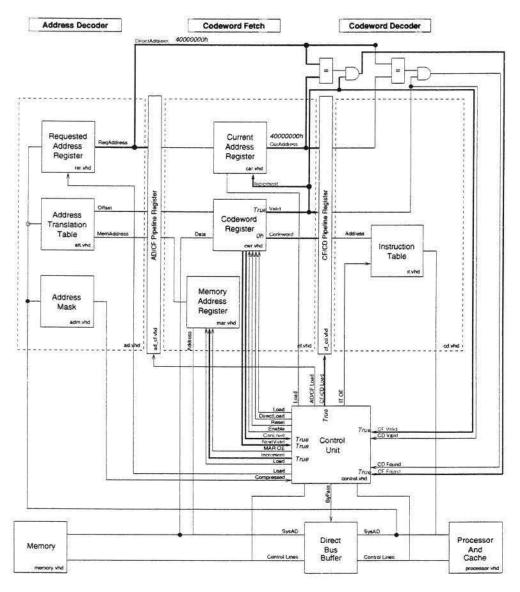

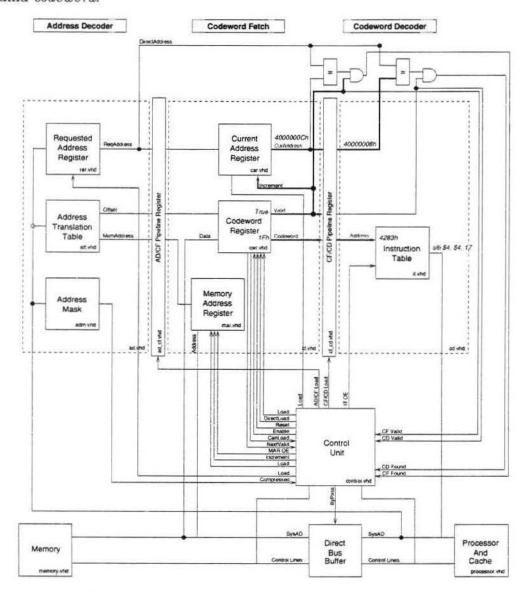

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86 |

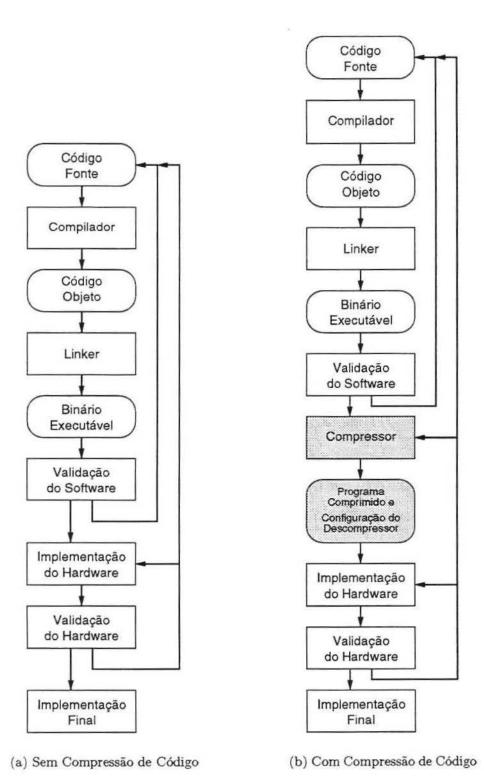

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87 |