#### Instituto de Computação Universidade Estadual de Campinas

# Implementação eficiente em software de curvas elípticas e emparelhamentos bilineares

## Diego de Freitas Aranha

Este exemplar corresponde à redação final da Tese devidamente corrigida e defendida por Diego de Freitas Aranha e aprovada pela Banca Examinadora.

Campinas, 26 de Agosto de 2011.

Prof. Dr. Julio César López Hernández (Orientador)

Tese apresentada ao Instituto de Computação, UNICAMP, como requisito parcial para a obtenção do título de Doutor em Ciência da Computação.

#### FICHA CATALOGRÁFICA ELABORADA POR ANA REGINA MACHADO – CRB8/5467 BIBLIOTECA DO INSTITUTO DE MATEMÁTICA, ESTATÍSTICA E COMPUTAÇÃO CIENTÍFICA – UNICAMP

Ar14i

Aranha, Diego de Freitas, 1982-

Implementação eficiente em software de curvas elípticas e emparelhamentos bilineares / Diego de Freitas Aranha. - Campinas, SP: [s.n.], 2011.

Orientador: Júlio César Lopez Hernández. Tese (doutorado) - Universidade Estadual de Campinas, Instituto de Computação.

- 1. Curvas elípticas. 2. Emparelhamentos bilineares. 3. Criptografia de chave-pública.

- 4. Algoritmos paralelos. 5. Aritmética de computador.

- I. Lopez Hernández, Júlio César, 1961-.

- II. Universidade Estadual de Campinas, Instituto de Computação. III. Título.

#### Informações para Biblioteca Digital

**Título em Inglês**: Efficient software implementation of elliptic curves and bilinear pairings

#### Palavras-chave em Inglês:

Elliptic curves

Bilinear pairings

Public key cryptography

Parallel algorithms

Computer arithmetic

**Área de concentração**: Ciência da Computação **Titulação**: Doutor em Ciência da Computação

Banca examinadora:

Júlio César Lopez Hernández [Orientador] Paulo Sérgio Licciardi Messeder Barreto Anderson Clayton Alves Nascimento Ricardo Dahab

Marco Aurélio Amaral Henriques **Data da defesa:** 26-08-2011

Programa de Pós-Graduação: Ciência da Computação

### TERMO DE APROVAÇÃO

Tese Defendida e Aprovada em 26 de agosto de 2011; pela Banca examinadora composta pelos Professores Doutores:

Prof. Dr. Anderson Clayton Alves Nascimento

Prof. Dr. Paulo Sérgio Licciardi Messeder Barreto LARC / USP

Prof. Dr. Marco Aurélio Amaral Henriques FEEC / UNICAMP

Prof. Dr. Ricardo Dahab IC / UNICAMP

ENE / UnB

Prof. Dr. Julio César López Hernández IC / UNICAMP

#### Instituto de Computação Universidade Estadual de Campinas

# Implementação eficiente em *software* de curvas elípticas e emparelhamentos bilineares

## Diego de Freitas Aranha<sup>1</sup>

26 de Agosto de 2011

#### Banca Examinadora:

- Prof. Dr. Julio César López Hernández (Orientador)

- Prof. Dr. Paulo Sérgio Licciardi Messeder Barreto

Departamento de Engenharia de Computação e Sistemas Digitais (Poli-USP)

- Prof. Dr. Anderson Clayton Alves Nascimento Departamento de Engenharia Elétrica (UnB)

- Prof. Dr. Ricardo Dahab

Instituto de Computação (UNICAMP)

- Prof. Dr. Marco Aurélio Amaral Henriques Faculdade de Engenharia Elétrica e de Computação (UNICAMP)

$<sup>^1{\</sup>rm Financiado}$ por Bolsa CAPES em 2007, Bolsa FAPESP (processo 2007/06950-0) em 2008–2010, Bolsa Sanduíche CAPES PDEE (processo 5551-09-9) em 2010–2011.

## Resumo

O advento da criptografia assimétrica ou de chave pública possibilitou a aplicação de criptografia em novos cenários, como assinaturas digitais e comércio eletrônico, tornando-a componente vital para o fornecimento de confidencialidade e autenticação em meios de comunicação. Dentre os métodos mais eficientes de criptografia assimétrica, a criptografia de curvas elípticas destaca-se pelos baixos requisitos de armazenamento para chaves e custo computacional para execução. A descoberta relativamente recente da criptografia baseada em emparelhamentos bilineares sobre curvas elípticas permitiu ainda sua flexibilização e a construção de sistemas criptográficos com propriedades inovadoras, como sistemas baseados em identidades e suas variantes. Porém, o custo computacional de criptossistemas baseados em emparelhamentos ainda permanece significativamente maior do que os assimétricos tradicionais, representando um obstáculo para sua adoção, especialmente em dispositivos com recursos limitados.

As contribuições deste trabalho objetivam aprimorar o desempenho de criptossistemas baseados em curvas elípticas e emparelhamentos bilineares e consistem em: (i) implementação eficiente de corpos binários em arquiteturas embutidas de 8 bits (microcontroladores presentes em sensores sem fio); (ii) formulação eficiente de aritmética em corpos binários para conjuntos vetoriais de arquiteturas de 64 bits e famílias mais recentes de processadores desktop dotadas de suporte nativo à multiplicação em corpos binários; (iii) técnicas para implementação serial e paralela de curvas elípticas binárias e emparelhamentos bilineares simétricos e assimétricos definidos sobre corpos primos ou binários. Estas contribuições permitiram obter significativos ganhos de desempenho e, conseqüentemente, uma série de recordes de velocidade para o cálculo de diversos algoritmos criptográficos relevantes em arquiteturas modernas que vão de sistemas embarcados de 8 bits a processadores com 8 cores.

## Abstract

The development of asymmetric or public key cryptography made possible new applications of cryptography such as digital signatures and electronic commerce. Cryptography is now a vital component for providing confidentiality and authentication in communication infra-structures. Elliptic Curve Cryptography is among the most efficient public-key methods because of its low storage and computational requirements. The relatively recent advent of Pairing-Based Cryptography allowed the further construction of flexible and innovative cryptographic solutions like Identity-Based Cryptography and variants. However, the computational cost of pairing-based cryptosystems remains significantly higher than traditional public key cryptosystems and thus an important obstacle for adoption, specially in resource-constrained devices.

The main contributions of this work aim to improve the performance of curve-based cryptosystems, consisting of: (i) efficient implementation of binary fields in 8-bit microcontrollers embedded in sensor network nodes; (ii) efficient formulation of binary field arithmetic in terms of vector instructions present in 64-bit architectures, and on the recently-introduced native support for binary field multiplication in the latest Intel microarchitecture families; (iii) techniques for serial and parallel implementation of binary elliptic curves and symmetric and asymmetric pairings defined over prime and binary fields. These contributions produced important performance improvements and, consequently, several speed records for computing relevant cryptographic algorithms in modern computer architectures ranging from embedded 8-bit microcontrollers to 8-core processors.

## Agradecimentos

Gostaria primeiramente de agradecer à minha noiva Fernanda Alcântara Andaló, que mesmo compartilhando das dificuldades da vida de um doutorando, sempre encontrou tempo para me escutar, compreender e transmitir carinho. Sua dedicação ao nosso projeto conjunto de vida me emociona e espero que estejamos próximos de forma definitiva muito em breve. Agradeço também aos meus bichos de estimação Jaiminho, Peta e Bruno, que souberam providenciar momentos de distração mesmo sem ter muita consciência do quanto isso era às vezes necessário.

Meu muito obrigado aos meus pais, José, Maria José, e irmãos, Pablo e Rodrigo, pelo suporte contínuo e pelo enorme esforço em percorrer um grande trajeto para assistir à minha defesa. Agradeço também à família Andaló, de minha noiva, pelos votos constantes de sucesso e à família Wagner pelas refeições esporádicas porém deliciosas que me ajudaram a atravessar o inverno canadense com saúde e disposição.

Agradeço a todos os membros da banca, pois é uma grande honra receber suas constribuições; aos meus co-autores, em especial Patrick Longa, Koray Karabina, Francisco Henríquez-Rodríguez, Darrel Hankerson, Conrado P. L. Gouvêa, Leonardo B. Oliveira e Jérémie Detrey por sua paciência e generosidade; aos colegas do Laboratório de Criptografia Aplicada da UNICAMP pelas discussões pertinentes; aos colegas do Center for Applied Cryptographic Research, em especial Márcio Juliato, e companheiros de escritório da Universidade de Waterloo pelo acolhimento hospitaleiro.

Um agradecimento especial ao Prof. Julio López, um grande orientador que não só me ajudou a percorrer os caminhos necessários para tornar esta tese possível, como soube me transmitir de forma eficiente sua paixão por aritmética criptográfica. Agradeço também ao Prof. Ricardo Dahab, sempre perspicaz em seus inúmeros conselhos, e ao Prof. Alfred Menezes, pelo exemplo incrível de competência e profissionalismo.

Fico particularmente feliz em agradecer aos meus amigos pela companhia e pela sabedoria em desviar estrategicamente o assunto de nossas conversas sempre que eu transparecia demasiada dedicação ao meu tema de pesquisa.

Registro meu reconhecimento à FAPESP, CNPq e CAPES pelo auxílio financeiro e aos demais que, de alguma maneira, me ajudaram na conclusão deste trabalho: docentes, funcionários e colegas do Instituto de Computação da UNICAMP.

# Sumário

| R            | Resumo vii<br>Abstract ix |          |                                                   |    |  |  |

|--------------|---------------------------|----------|---------------------------------------------------|----|--|--|

| $\mathbf{A}$ |                           |          |                                                   |    |  |  |

| $\mathbf{A}$ | $\operatorname{grad}$     | ecimen   | tos                                               | xi |  |  |

| 1            | Intr                      | rodução  | 0                                                 | 1  |  |  |

|              | 1.1                       | Justific | cativa e objetivo                                 | 2  |  |  |

|              | 1.2                       | Metod    | ologia                                            | 3  |  |  |

|              | 1.3                       | Arquit   | seturas computacionais modernas                   | 5  |  |  |

|              |                           | 1.3.1    | Multiprocessamento                                | 5  |  |  |

|              |                           | 1.3.2    | Vetorização                                       | 7  |  |  |

|              |                           | 1.3.3    | Sistemas embarcados                               | 7  |  |  |

|              |                           | 1.3.4    | Métricas de desempenho                            | 7  |  |  |

|              | 1.4                       | Funda    | mentação matemática                               | 8  |  |  |

|              |                           | 1.4.1    | Curvas elípticas                                  | 8  |  |  |

|              |                           | 1.4.2    | Emparelhamentos bilineares                        | 10 |  |  |

|              |                           | 1.4.3    | Problemas subjacentes                             | 11 |  |  |

|              |                           | 1.4.4    | Cálculo de emparelhamentos                        | 12 |  |  |

|              |                           | 1.4.5    | Algoritmo de Miller                               | 14 |  |  |

|              |                           | 1.4.6    | Emparelhamento de Tate                            | 15 |  |  |

|              |                           | 1.4.7    | Emparelhamento de Weil                            | 16 |  |  |

|              |                           | 1.4.8    | Emparelhamento $\eta_T$ [1]                       | 17 |  |  |

|              |                           | 1.4.9    | Emparelhamento ate [2]                            | 18 |  |  |

|              |                           | 1.4.10   | Emparelhamento $R$ -ate [3]                       | 18 |  |  |

|              |                           | 1.4.11   | Emparelhamento otimal                             | 19 |  |  |

|              | 1.5                       | Contri   | buições                                           | 19 |  |  |

|              |                           | 1.5.1    | Implementação de criptografia de curvas elípticas | 19 |  |  |

|   |                                              | neares                                                                                           | . 22                                                     |

|---|----------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   |                                              | 1.5.3 Biblioteca criptográfica                                                                   |                                                          |

|   | 1.6                                          | Organização do documento                                                                         | . 25                                                     |

| 2 | Effic                                        | cient implementation of elliptic curve cryptography in wireless sen                              | 1-                                                       |

|   | sors                                         | 3                                                                                                | 27                                                       |

|   | 2.1                                          | Introduction                                                                                     | . 28                                                     |

|   | 2.2                                          | Related work                                                                                     | . 29                                                     |

|   | 2.3                                          | Elliptic curve cryptography                                                                      | . 31                                                     |

|   | 2.4                                          | The platform                                                                                     | . 32                                                     |

|   | 2.5                                          | Algorithms for finite field arithmetic                                                           | . 33                                                     |

|   |                                              | 2.5.1 Multiplication                                                                             | . 33                                                     |

|   |                                              | 2.5.2 Modular reduction                                                                          | . 37                                                     |

|   |                                              | 2.5.3 Squaring                                                                                   | . 40                                                     |

|   |                                              | 2.5.4 Inversion                                                                                  | . 40                                                     |

|   | 2.6                                          | Algorithms for elliptic curve arithmetic                                                         | . 42                                                     |

|   | 2.7                                          | Implementation results                                                                           | . 43                                                     |

|   |                                              |                                                                                                  |                                                          |

|   | 2.8                                          | Conclusions                                                                                      | . 46                                                     |

| 3 |                                              | Conclusions                                                                                      |                                                          |

| 3 | Effic                                        |                                                                                                  |                                                          |

| 3 | Effic                                        | cient Software Implementation of Binary Field Arithmetic Usin                                    | g<br>49                                                  |

| 3 | Effic<br>Vec                                 | cient Software Implementation of Binary Field Arithmetic Usin<br>tor Instruction Sets            | <b>g</b><br>49                                           |

| 3 | Efficiency Vec 3.1                           | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets  Introduction | <b>g</b><br>49<br>. 50                                   |

| 3 | Effice Vec: 3.1 3.2                          | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets  Introduction | <b>g</b> 49 . 50 . 51 . 52                               |

| 3 | Effice Vec: 3.1 3.2                          | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets Introduction  | <b>g</b> 49 . 50 . 51 . 52 . 53                          |

| 3 | Effice Vec: 3.1 3.2                          | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets Introduction  | <b>g</b> 49 . 50 . 51 . 52 . 53                          |

| 3 | Effice Vec: 3.1 3.2                          | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets Introduction  | <b>g 49</b> . 50  . 51  . 52  . 53  . 53                 |

| 3 | Effice Vec: 3.1 3.2                          | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets Introduction  | <b>g</b> 49  50  51  52  53  53  56  56                  |

| 3 | Effice Vec 3.1 3.2 3.3                       | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets Introduction  | <b>g 49</b> . 50  . 51  . 53  . 53  . 56  . 56           |

| 3 | Effice Vec 3.1 3.2 3.3                       | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets Introduction  | <b>g</b> 49 . 50 . 51 . 52 . 53 . 53 . 56 . 56 . 60      |

| 3 | Effice Vec 3.1 3.2 3.3                       | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets Introduction  | <b>g</b> 49  50  51  52  53  56  60  64                  |

| 4 | Effication Vec 3.1 3.2 3.3 3.4 3.4 Soft      | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets  Introduction | <b>g</b> 49 . 50 . 51 . 52 . 53 . 56 . 56 . 60 . 64      |

|   | Effication Vec 3.1 3.2 3.3 3.4 3.5 Soft less | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets  Introduction | <b>g</b> 49 . 50 . 51 . 52 . 53 . 56 . 60 . 60 . 64      |

|   | Effice Vec 3.1 3.2 3.3 3.4 3.5 Soft less 4.1 | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets  Introduction | <b>g</b> 49 . 50 . 51 . 52 . 53 . 56 . 60 . 60 . 64 . 65 |

|   | Effication Vec 3.1 3.2 3.3 3.4 3.5 Soft less | cient Software Implementation of Binary Field Arithmetic Usin tor Instruction Sets  Introduction | <b>g</b> 49 . 50 . 51 . 52 . 53 . 56 . 60 . 60 . 64 . 65 |

|   |      | 4.2.2 Squaring, square-root and multi-squaring 71                     |

|---|------|-----------------------------------------------------------------------|

|   |      | 4.2.3 Inversion                                                       |

|   |      | 4.2.4 Half-trace                                                      |

|   | 4.3  | Random binary elliptic curves                                         |

|   |      | 4.3.1 Sequential algorithms for random binary curves                  |

|   |      | 4.3.2 Parallel scalar multiplication on random binary curves          |

|   |      | 4.3.3 Side-channel resistant multiplication on random curves          |

|   | 4.4  | Koblitz elliptic curves                                               |

|   |      | 4.4.1 Sequential algorithms for Koblitz curves                        |

|   |      | 4.4.2 Parallel algorithm for Koblitz curves                           |

|   | 4.5  | Experimental results                                                  |

|   | 4.6  | Conclusion and future work                                            |

| 5 | Hig  | h-speed Parallel Software Implementation of the $\eta_T$ Pairing 85   |

|   | 5.1  | Introduction                                                          |

|   | 5.2  | Finite Field Arithmetic                                               |

|   |      | 5.2.1 Vector Instruction Sets                                         |

|   |      | 5.2.2 Squaring                                                        |

|   |      | 5.2.3 Square Root                                                     |

|   |      | 5.2.4 Multiplication                                                  |

|   |      | 5.2.5 Modular Reduction                                               |

|   |      | 5.2.6 Inversion                                                       |

|   |      | 5.2.7 Implementation Timings                                          |

|   | 5.3  | Pairing Computation                                                   |

|   |      | 5.3.1 Preliminary Definitions                                         |

|   |      | 5.3.2 Related Work                                                    |

|   |      | 5.3.3 Parallelization                                                 |

|   |      | 5.3.4 Parallel $\eta_T$ Pairing                                       |

|   |      | 5.3.5 Performance Analysis                                            |

|   | 5.4  | Experimental Results                                                  |

|   | 5.5  | Conclusion and Future Work                                            |

| 6 | Fast | ter Explicit Formulas for Computing Pairings over Ordinary Curves 105 |

|   | 6.1  | Introduction                                                          |

|   | 6.2  | Preliminaries                                                         |

|   | 6.3  | Tower Extension Field Arithmetic                                      |

|   |      | 6.3.1 Lazy Reduction for Tower Fields                                 |

|   |      | 6.3.2 Selecting a Field Size Smaller than the Word-Size Boundary 111  |

|   |      | 6.3.3 Analysis for Selected Parameters                                |

|                  | 6.4    | Miller Loop                                                                                              |

|------------------|--------|----------------------------------------------------------------------------------------------------------|

|                  | 6.5    | Final Exponentiation                                                                                     |

|                  |        | 6.5.1 Removing the Inversion Penalty                                                                     |

|                  |        | 6.5.2 Computing $u$ -th powers in $\mathbb{G}_{\phi_6}(\mathbb{F}_{p^2})$                                |

|                  | 6.6    | Computational Cost                                                                                       |

|                  | 6.7    | Implementation Results                                                                                   |

|                  | 6.8    | Conclusion                                                                                               |

| 7                | Par    | allelizing the Weil and Tate Pairings 125                                                                |

|                  | 7.1    | Introduction                                                                                             |

|                  | 7.2    | Background on pairings                                                                                   |

|                  |        | 7.2.1 Miller functions                                                                                   |

|                  |        | 7.2.2 The Tate pairing                                                                                   |

|                  |        | 7.2.3 The optimal ate pairing                                                                            |

|                  |        | 7.2.4 The eta pairing                                                                                    |

|                  | 7.3    | Parallelizing the optimal ate pairing                                                                    |

|                  | 7.4    | Optimal Weil pairings                                                                                    |

|                  |        | 7.4.1 Hess's Weil pairing construction                                                                   |

|                  |        | 7.4.2 The $\alpha$ Weil pairing                                                                          |

|                  |        | 7.4.3 The $\boldsymbol{\beta}$ Weil pairing                                                              |

|                  | 7.5    | Parallel implementation of the BN pairings                                                               |

|                  | 7.6    | Parallel implementation of the eta pairing                                                               |

|                  |        | 7.6.1 Algorithm 1                                                                                        |

|                  |        | 7.6.2 Algorithm 2                                                                                        |

|                  |        | 7.6.3 Algorithm 3                                                                                        |

|                  |        | 7.6.4 Algorithm 4                                                                                        |

|                  |        | 7.6.5 Implementation report                                                                              |

|                  | 7.7    | Concluding remarks                                                                                       |

|                  | 7.A    | Relationship between $\mathbb{G}_1$ , $\mathbb{G}_2$ , $\tilde{\mathbb{G}}_1$ and $\tilde{\mathbb{G}}_2$ |

| 8                | Con    | nclusões 147                                                                                             |

| $\mathbf{B}^{i}$ | ibliog | grafia 150                                                                                               |

# Capítulo 1

# Introdução

A descoberta da criptografia de chave pública [4] revolucionou a forma de se construir sistemas criptográficos e possibilitou, de forma definitiva, a integração entre teoria criptográfica e implementação em aplicações reais. Particularmente, trouxe a possibilidade de se estabelecer serviços criptográficos como sigilo e assinatura irretratável em ambientes onde não existe qualquer relação de confiança entre os envolvidos ou canal seguro para distribuição de chaves. O antigo problema da distribuição de chaves converteu-se então na dificuldade de obtenção de uma chave pública autêntica. Como solução para este novo problema, um repositório público foi inicialmente proposto como ponto de distribuição de chaves [4]. Entretanto, não há como um repositório deste tipo fornecer autenticidade, pois possibilita que atacantes participem em protocolos personificando entidades legítimas. A autenticação mútua das chaves é crucial para que tais intervenções possam ser detectadas e evitadas.

O surgimento de infra-estruturas de chaves públicas [5] solucionou o problema de tituaridade de chaves públicas e impulsionou o comércio eletrônico. Por outro lado, criou diversos problemas adicionais. Em primeiro lugar, infra-estruturas de chaves públicas são concebidas para representar entidades do mundo real, suas filiações a organizações e serviços que fornecem. Os tipos de relações presentes são diversos, o que traz sérios problemas para o projeto de infra-estruturas que sejam tanto genéricas o suficiente para representar qualquer tipo de relação, quanto simples o suficiente para terem ampla aceitação, possibilidade de padronização e eficiência. Operações de validação de certificados e revogação de chaves públicas tendem a representar situações extremas [6].

A descoberta de sistemas criptográficos baseados no problema do logaritmo discreto em curvas elípticas [7, 8] produziu uma nova revolução na área. Ao apresentarem desempenho superior e exigirem chaves mais curtas para um mesmo nível de segurança que os métodos tradicionais de criptografia assimétrica, especialmente o algoritmo RSA [9] e variantes baseadas no problema da fatoração, alguns dos problemas inerentes às infra-estruturas de

chaves públicas foram minimizados. Contudo, a dificuldade de gerência e a sobrecarga de desempenho decorrentes da utilização de certificados ainda impõe obstáculos na adoção de criptografia assimétrica em ambientes restritos, como computação móvel e em dispositivos de baixo poder computacional [10].

A busca de alternativas ao paradigma tradicional de infra-estruturas de chave pública resultou na descoberta de sistemas baseados em identidade. Foram concebidos inicialmente por Shamir [11], em 1984, para assinaturas digitais, mas as primeiras realizações funcionais e eficientes para cifração só foram apresentadas em 2001, por Boneh e Franklin [12], e Sakai, Ohgishi e Kasahara [13], a partir de emparelhamentos bilineares sobre curvas elípticas. A motivação original para sistemas baseados em identidade era aproveitar a autenticidade de informação publicamente conhecida para simplificar a autenticação de chaves públicas. Até então, a única aplicação de emparelhamentos bilineares em criptografia era atacar sistemas criptográficos de curvas elípticas [14, 15]. Após a aplicação de emparelhamentos para concretizar cifração baseada em identidade, uma gama de novos protocolos com propriedades inovadoras e especiais foi desenvolvida. Isto levou a uma flexibilização enorme das primitivas criptográficas conhecidas e ampliou os cenários de aplicação de criptografia assimétrica de forma considerável. Entre os protocolos baseados em problemas sobre grupos bilineares, destacam-se: acordo de chaves eficientes para múltiplas entidades [16], assinaturas curtas e agregadas [17] e paradigmas alternativos de certificação implícita [18].

## 1.1 Justificativa e objetivo

Apesar das propriedades inovadoras, o desempenho de sistemas criptográficos baseados em emparelhamentos ainda representa um obstáculo. Tipicamente, o cálculo de um emparelhamento bilinear ainda é comparável a uma decifração/assinatura RSA [19], e uma ordem de magnitude menos eficiente que uma multiplicação de ponto em curvas elípticas [20, 21]. Isto é natural, visto que os métodos mais estabelecidos de criptografia assimétrica puderam receber maior esforço de pesquisa, produzindo algoritmos cada vez mais eficientes. Esforço similar já é consistente em criptografia baseada em emparelhamentos [22], resultando em novos algoritmos [23, 1, 3, 24] e novas curvas adequadas à sua instanciação [25].

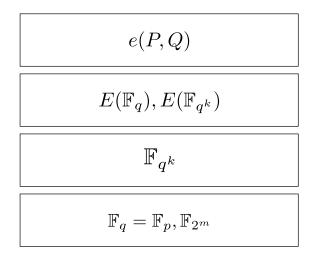

Este projeto teve como finalidade desenvolver algoritmos eficientes (seqüenciais e paralelos) e implementações em software otimizadas para criptografia de curvas elípticas e criptografia baseada em emparelhamentos. Vários níveis de aritmética são empregados: [19]: algoritmos para o cálculo do emparelhamento e(P,Q) propriamente dito [23, 1], aritmética na curva elíptica onde o emparelhamento bilinear encontra-se definido [26], aritmética no corpo finito onde a curva elíptica está definida [27] e aritmética nas extensões

Figura 1.1: Níveis de aritmética envolvidos no cálculo de um emparelhamento bilinear.

deste corpo finito [28]. Estes níveis de aritmética encontram-se visualmente representados na Figura 1.1 em uma organização descendente partindo do cálculo do emparelhamento.

O objetivo principal deste trabalho consistiu em tornar estes métodos de criptografia mais eficientes nas arquiteturas modernas, abrangendo tanto pesquisa algorítmica quanto pesquisa aplicada de implementação. A implementação exigiu o projeto de técnicas de otimização de algoritmos em arquiteturas modernas (embarcadas, multiprocessadas) e concretizou os algoritmos em código funcional eficiente, fazendo o melhor uso possível dos recursos disponibilizados pelo *hardware*. Para isso, paralelismo em nível de tarefas e em nível de dados foram extensamente utilizados, incluindo a aplicação de multiprocessamento e conjuntos de instruções vetoriais.

## 1.2 Metodologia

Para atender os objetivos previamente mencionados, a metodologia utilizada compreendeu os seguintes passos:

1. Levantamento ferramental: pesquisar e experimentar com *frameworks*, linguagens e ferramentas para programação em arquiteturas multiprocessadas, incluindo compiladores, bibliotecas, simuladores e *profilers*.

Como ferramenta principal para programação paralela em arquiteturas homogêneas, a tecnologia OpenMP [29] foi selecionada. O suporte à tecnologia encontra-se incluído em dois compiladores distintos, o GNU Compiler Collection, versão 4.2.0 e o Intel C++ Compiler, versão 10.01. O framework OpenMP

suporta construções tanto para paralelismo de dados como para paralelismo de tarefas. A implementação dos algoritmos foi realizada principalmente na linguagem C e as rotinas críticas foram codificadas em Assembly.

2. Análise e seleção de arquiteturas: selecionar arquiteturas modernas relevantes e analisar características das arquiteturas selecionadas que possam posteriormente ser utilizadas para otimização das implementações dos algoritmos desenvolvidos.

Dentre as opções de arquitetura multiprocessadas, destacam-se as arquiteturas Intel Core [30] e AMD K10 [31], que oferecem alto desempenho e as melhores ferramentas de desenvolvimento disponíveis. Para ambientes embutidos e computação móvel, destacam-se as arquiteturas AVR ATmega128 [32] e Intel XScale [33]. Não houve tempo suficiente para se explorar o processador Cell [34] ou processamento em placas gráficas [35], apesar dos mesmos serem importantes no segmento de computação de alto desempenho.

- 3. Levantamento bibliográfico: determinar precisamente os componentes da aritmética em curvas elípticas e para o cálculo de emparelhamentos bilineares que são mais exigidos. Em busca de aperfeiçoamento das alternativas já propostas, pesquisar artigos que propõem algoritmos para criptografia de curvas elípticas e baseada em emparelhamentos. Pesquisar algoritmos relevantes que ainda não foram adaptados para ambientes paralelos.

- 4. Desenvolvimento de novos algoritmos: propor otimizações, variantes paralelas de algoritmos existentes ou novos algoritmos para criptografia de curvas elípticas e criptografia baseada em emparelhamentos bilineares, abrangendo os níveis de aritmética citados anteriormente.

- 5. Implementação eficiente dos algoritmos: a implementação em *software* de cada algoritmos desenvolvido utilizou a metodologia abaixo.

- (a) Detecção de gargalos: detectar porções do algoritmo que correspondem ao maior custo computacional;

- (b) Otimização: elaborar técnicas para otimizar as implementações dos algoritmos, considerando principalmente os gargalos de desempenho detectados;

- (c) Transformações algébricas: investigar os fundamentos matemáticos do algoritmo em busca de modificações que acelerem o tempo de execução de sua implementação ou permitam a extração de mais paralelismo;

- (d) Implementação: concretizar os algoritmos em implementações de alto desempenho que utilizem os recursos do processador com máxima eficiência.

- 6. Validação: a partir da análise de complexidade do algoritmo e de sua implementação concreta, observar e analisar os resultados em termos de tempo de execução, eficiência na utilização de recursos e escalabilidade. Demonstrar a correção das otimizações propostas também é desejável.

- 7. Construção de uma biblioteca em *software* contendo os algoritmos implementados. Esta biblioteca é descrita brevemente na seção 1.5.3.

## 1.3 Arquiteturas computacionais modernas

Tradicionalmente, cada nova geração de processadores de propósito geral obtém ganhos de desempenho significativos de duas formas: aprimoramentos no processo de fabricação e mudanças arquiteturais. Estas últimas são comumente relacionadas à extração de paralelismo em nível de instruções, ou seja, à execução concorrente de instruções que não possuem dependências de dados. Entretanto, estas otimizações atualmente se deparam com limitações críticas. A extração de paralelismo em nível de instrução claramente apresenta um limite superior, e muitas aplicações possuem um alto grau de dependência de dados que restringe este paralelismo [36]. O aperfeiçoamento do processo de fabricação também atinge limitações físicas, já que componentes cada vez menores dissipam potência em uma área cada vez menor [37]. Como obstáculo adicional, o poder de processamento vem crescendo muito mais do que a velocidade da memória, e o acesso à memória já é reconhecido como o maior gargalo de execução nas arquiteturas atuais [38]. Estas três limitações provocaram uma mudança radical no projeto de arquiteturas modernas, transportando a ênfase antes colocada em mecanismos para extração automática de paralelismo para mecanismos explícitos, na forma de multiprocessamento e vetorização. A disponibilidade crescente de componentes em áreas cada vez menores tem simultaneamente permitido o desenvolvimento de sistemas embarcados com poder computacional crescente.

## 1.3.1 Multiprocessamento

Arquiteturas multiprocessadas de propósito geral são chamadas multi-core. Em uma arquitetura multi-core, diversas unidades de processamento independentes conectam-se ao sistema de memória, compartilhando opcionalmente recursos do hardware [39]. Apesar de parecer uma forma barata e escalável de se aumentar desempenho, a introdução de paralelismo em nível de thread impõe uma mudança de paradigma de programação [40].

Enquanto nas máquinas uniprocessadas e seqüenciais, o desempenho dos programas crescia automaticamente a cada nova geração de processadores, em arquiteturas *multi-core*, o desempenho dos programas está diretamente relacionado ao grau de paralelismo em nível de *thread* que o programa apresenta. Como esse paralelismo é extraído explicitamente e requer análise profunda do problema e solução sendo tratados, e o modelo de execução em *multithreading* é não-determinístico, paralelizar algoritmos é uma tarefa não-trivial [41].

A exploração com sucesso do paralelismo também requer conhecimento da organização das unidades de processamento e da hierarquia de memória [42]. Quanto à organização das unidades de processamento, pode-se classificar as arquiteturas multiprocessadas em:

- Homogêneas: as unidades de processamento são idênticas e contam com os mesmos recursos. A extração de paralelismo torna-se mas simples, mas a divisão do problema deve produzir tarefas com as mesmas características;

- Heterogêneas: as unidades de processamento são especializadas para execução de tarefas com naturezas distintas. Permite-se tipicamente um maior controle do fluxo de execução mas pode-se introduzir dificuldade na exploração de paralelismo.

Já quanto à organização da hierarquia de memória, há a divisão em duas vertentes:

- Acesso uniforme: níveis inferiores de memória cache são compartilhados e o acesso

à memória é uniforme a partir de um barramento único. Esta abordagem pressiona

os níveis inferiores de memória cache, pois a ocupação é disputada por unidades de

processamento distintas.

- Acesso não-uniforme: cada unidade ou subconjunto de unidades de processamento conta com memórias dedicadas de rápido acesso e latências variadas a porções distintas da memória global. Esta abordagem promete escalabilidade da hierarquia de memória, mas exige afinidade de tarefas por unidade de processamento;

Estas organizações definem o espectro de abordagens utilizadas no projeto de arquiteturas multiprocessadas modernas. A arquitetura Core [30] da Intel é composta por unidades de processamento idênticas e acesso uniforme à memória. A arquitetura Opteron [43] utiliza unidades de processamento também idênticas, mas acesso não-uniforme à memória. A arquitetura UltraSparc T1 [44] da Sun emprega 8 unidades homogêneas e acesso uniforme, mas cada unidade é superescalar e capaz de executar 4 threads distintas, totalizando 32 threads simultâneas. O processador Cell [34] da IBM é um exemplo típico de arquitetura heterogênea que dispõe de um processador de propósito geral e 8 unidades de processamento adicionais especializadas em aritmética de alto desempenho. Esta especialização naturalmente impõe acesso não-uniforme à memória.

Os mesmos princípios regem o projeto de arquiteturas multiprocessadas no segmento de computação embutida. A heterogeneidade muitas vezes manifesta-se na presença de co-processadores [45, 33] e o acesso não-uniforme à memória é empregado a partir de memórias de rascunho locais [46] ou transferências explícitas de dados por um canal de comunicação dedicado [47].

#### 1.3.2 Vetorização

As arquiteturas modernas também contam com instruções especializadas para processamento de múltiplos objetos de dados simultaneamente. Essas instruções são classificadas como SIMD (Simple Instruction - Multiple Data) [48], e são extremamente úteis na otimização de programas com alta densidade aritmética. Instruções vetoriais são outro recurso para exploração de paralelismo de dados, mas com uma granularidade muito mais fina do que o multiprocessamento. Conjuntos de instruções vetoriais bastante difundidos e presentes em arquiteturas modernas são MMX [49], SSE [50, 51] e AVX [52]. Há um incentivo ainda maior para a utilização de instruções dessa natureza, visto que a latência de execução dessas instruções tem diminuído a cada nova geração de processadores.

#### 1.3.3 Sistemas embarcados

A disponibilidade farta de transístores têm também provocado uma expansão das funcionalidades possíveis em sistemas dedicados de pequeno porte. Esta tendência tecnológica é geralmente descrita através do termo *Internet of Things* [53], que captura precisamente a noção de um conjunto de inúmeros dispositivos distintos, cada um com sua função, interligados por um substrato compartilhado de comunicação. Sistemas embarcados ocupam os segmentos de menor custo do espectro de arquiteturas modernas e muitas vezes executam funções importantes que carecem naturalmente de serviços de segurança como autenticação e confidencialidade. Exemplos diretos de sistemas embarcados que desempenham funcionalidade crítica são nós de uma rede sensores [54] e etiquetas *RFID*(*Radio-Frequency IDentification*) [55].

### 1.3.4 Métricas de desempenho

A métrica tradicional para comparar o desempenho de diferentes implementações é a contagem direta de ciclos, desde que as implementações sejam executadas em plataformas representantes da mesma microarquitetura. A contagem de ciclos é tipicamente realizada através de um simulador de arquiteturas embarcadas ou pela leitura de registradores especiais nas arquiteturas de maior porte. Cabe a ressalva de que, dada a complexidade dos processadores atuais, envolvendo múltiplos componentes funcionando em paralelo a

freqüências oscilantes de processamento, registrar a passagem de cada ciclo torna-se um problema complexo. A alternativa encontrada recentemente pelos fabricantes para manter razoavelmente a noção convencional de ciclo foi estabelecer o ciclo como uma medida de tempo real correspondente ao inverso da freqüência nominal do processador [56]. Há, portanto, que se ter o cuidado de realizar tomadas de tempo em ciclos com o processador ocioso e funcionando em sua freqüência nominal. Este procedimento simples foi utilizado para obtenções de resultados experimentais na maioria dos trabalhos apresentados nesta tese, com exceção da microarquitetura Intel Westmere. Esta microarquitetura possui suporte autônomo à gerência de freqüência do processador, podendo a freqüência inclusive superar a freqüência nominal (overclocking). Esta funcionalidade depende de diversos efeitos, como temperatura e a quantidade de trabalho distribuído entre as várias unidades de processamento, tornando difícil a determinação precisa da freqüência atual de execução e potencialmente distorcendo as tomadas de tempo. Foi possível contornar este obstáculo apenas a partir do desligamento desta funcionalidade na configuração das máquinas utilizadas para tomadas de tempo.

## 1.4 Fundamentação matemática

Nesta seção, apresentamos as áreas de criptografia de curvas elípticas e baseada em emparelhamentos bilineares, a fundamentação matemática para o Algoritmo de Miller [57, 58], empregado no cálculo de emparelhamentos, e a aplicação deste algoritmo para o cálculo de emparelhamentos bilineares propostos na literatura.

## 1.4.1 Curvas elípticas

Uma curva elíptica sobre um corpo K é definida pela equação de Weierstraβ:

$$E: y^2 + a_1 x y + a_3 y = x^3 + a_2 x^2 + a_4 x + a_6,$$

(1.1)

onde  $a_1, a_2, a_3, a_4, a_5, a_6 \in \mathbb{K}$ , com discriminante  $\Delta \neq 0$ . Se  $\overline{\mathbb{K}}$  é o fecho algébrico de  $\mathbb{K}$  e  $\mathbb{L}$  é uma extensão algébrica  $\mathbb{K} \subset \mathbb{L} \subset \overline{\mathbb{K}}$ , o conjunto de pontos  $\mathbb{L}$ -racionais em E é:

$$E(\mathbb{L}) = \{(x,y) \in \mathbb{L} \times \mathbb{L} : y^2 + a_1 xy + a_3 y - x^3 - a_2 x^2 - a_4 x - a_6 = 0\} \cup \{\infty\},\$$

onde  $\infty$  é o ponto no infinito.

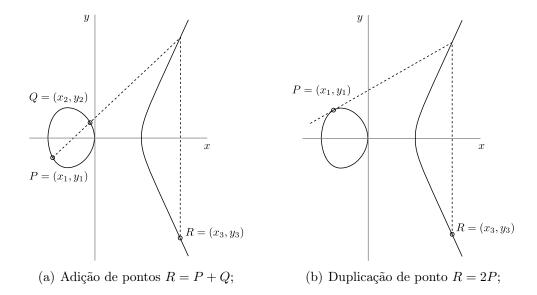

Curvas elípticas fornecem uma regra geométrica para a adição de pontos. Sejam  $P = (x_1, y_1)$  e  $Q = (x_2, y_2)$  pontos distintos racionais sobre uma curva elíptica E. A soma R = P + Q é definida como a reflexão sobre o eixo x do ponto R' de intersecção entre a

Figura 1.2: Adição e duplicação geométrica de pontos em curvas elípticas.

curva E e a linha que passa por P e Q. Quando P = Q, toma-se a intersecção R' entre a curva E e a tangente à curva E no ponto P. A figura 1.2 apresenta as regras para adição e duplicação de pontos em sua forma geométrica. O conjunto de pontos  $E(\mathbb{K})$  em conjunção com a regra de adição forma o grupo abeliano  $(E(\mathbb{K}), +)$  com o ponto no infinito  $\infty$  como elemento de identidade.

O número de pontos da curva  $E(\mathbb{K})$ , denotado por  $\#E(\mathbb{K})$ , é chamado de ordem da curva sobre o corpo  $\mathbb{K}$ . A condição de Hasse afirma que  $\#E(\mathbb{F}_{q^k}) = q^k + 1 - t$ , onde  $|t| \leq 2\sqrt{q^k}$  é chamado de traço de Frobenius. Curvas em que a característica q divide t são chamadas de curvas supersingulares.

A partir de substituição de variáveis, a equação (1.1) pode ser simplificada dependendo da característica q do corpo  $\mathbb{K}$  [59]:

• Se  $q \neq 2,3$  primo, a curva elíptica é dita curva prima e tem equação:

$$E(\mathbb{F}_q): y^2 = x^3 + ax + b;$$

(1.2)

• Se q=2 e  $a_1\neq 0$ , a curva elíptica é dita curva binária ordinária e tem equação:

$$E(\mathbb{F}_{2^m}): y^2 + xy = x^3 + ax^2 + b; \tag{1.3}$$

• Se q = 2 e  $a_1 = 0$ , a curva elíptica é dita curva binária supersingular e tem equação:

$$E(\mathbb{F}_{2^m}): y^2 + cy = x^3 + ax + b. \tag{1.4}$$

Dado um ponto elíptico  $P \in E(\mathbb{F}_q)$  e um número inteiro l, a operação lP, chamada multiplicação de ponto por escalar, é definida pela relação de recorrência:

$$lP = \begin{cases} \infty, & \text{se } l = 0; \\ (-l)(-P) & \text{se } l \le -1; \\ (l-1)P + P & \text{se } l \ge 1. \end{cases}$$

A multiplicação de ponto é a operação fundamental utilizada por protocolos baseados em curvas elípticas. Este operação pode ser calculada em diferentes sistemas de coordenadas [60, 61, 21] e com diferentes algoritmos, dependendo se há ou não conhecimento prévio do ponto a ser multiplicado [62, 63, 64, 65]. Os Capítulos 2, 3 e 4 discutem brevemente a escolha de algoritmos para multiplicação de ponto. Informações detalhadas para estes algoritmos podem ser encontradas em [59, 66].

Seja  $n = \#E(\mathbb{F}_{q^k})$ . A ordem de um ponto  $P \in E$  é o menor inteiro r > 0 tal que  $rP = \infty$ . Temos que r|n. O conjunto de pontos de torção r de E, denotado por  $E(\mathbb{K})[r]$ , é o conjunto de pontos cuja ordem divide r, ou seja, o conjunto  $\{P \in E(\mathbb{K})|rP = \infty\}$ . Destas definições, segue que  $\langle P \rangle$ , o grupo de pontos gerado por P, é um subgrupo de  $E(\mathbb{K})[r]$ , que por sua vez é um subgrupo de  $E(\mathbb{K})[n]$ . Dizemos que o subgrupo  $\langle P \rangle$  tem grau de mergulho k se k é o menor inteiro tal que  $r|q^k - 1$  [23].

#### 1.4.2 Emparelhamentos bilineares

Sejam  $\mathbb{G}_1$  e  $\mathbb{G}_2$  grupos cíclicos aditivos e  $\mathbb{G}_T$  um grupo cíclico multiplicativo tais que  $|\mathbb{G}_1| = |\mathbb{G}_2| = |\mathbb{G}_T|$ . Seja P o gerador de  $\mathbb{G}_1$  e Q o gerador de  $\mathbb{G}_2$ . Um mapeamento  $e: \mathbb{G}_1 \times \mathbb{G}_2 \to \mathbb{G}_T$  é dito um emparelhamento bilinear admissível [12] se satisfaz as seguintes propriedades:

1. Bilinearidade: dados  $(V, W) \in \mathbb{G}_1 \times \mathbb{G}_2$ , temos

$$e(P,Q+Z) = e(P,Q) \cdot e(P,Z) \text{ e } e(P+V,Q) = e(P,Q) \cdot e(V,Q).$$

Conseqüentemente, para quaisquer  $a, b \in \mathbb{Z}_{|\mathbb{G}_T|}$ , temos:

$$e(aV, bW) = e(V, W)^{ab} = e(abV, W) = e(V, abW) = e(bV, aW).$$

- 2. Não-degeneração:  $e(P,Q) \neq 1_{\mathbb{G}_T}$ , onde  $1_{\mathbb{G}_T}$  é a identidade do grupo  $\mathbb{G}_T$ .

- 3. *Eficiência:* O mapeamento *e* pode ser calculado eficientemente, ou seja, tem complexidade polinomial.

Tipicamente,  $\mathbb{G}_1$  e  $\mathbb{G}_2$  são subgrupos do grupo de pontos de uma curva elíptica sobre o fecho algébrico de um corpo finito  $\mathbb{F}_q$  e  $\mathbb{G}_T$  é um subgrupo do grupo multiplicativo de um corpo finito relacionado a  $\mathbb{F}_q$  (uma de suas extensões, por exemplo). Esta definição genérica define um emparelhamento assimétrico [67]. A instanciação mais comum de um emparelhamento assimétrico é escolher  $\mathbb{G}_1$  como um subgrupo de pontos na curva elíptica  $E(\mathbb{F}_q)$ ,  $\mathbb{G}_2$  como um subgrupo de pontos na curva elíptica  $E(\mathbb{F}_{q^k})$  e  $\mathbb{G}_T$  como o subgrupo de raízes da unidade em  $\mathbb{F}_{q^k}^*$ .

Se E é uma curva supersingular definida sobre  $\mathbb{F}_q$  com grau de mergulho k > 1 e r é um divisor primo de  $\#E(\mathbb{F}_q)$ , o emparelhamento simétrico associado com E é o mapa bilinear  $\hat{e}: \mathbb{G}_1 \times \mathbb{G}_1 \to \mathbb{G}_T$  definido por  $e(P_1, \psi(P_2))$ , onde  $\psi$  é um mapa de distorção. O mapa de distorção é um homomorfismo de  $\mathbb{G}_1$  em  $\mathbb{G}_2$  cuja função é garantir que  $\langle P \rangle$  e  $\langle \psi(P) \rangle$  sejam conjuntos linearmente independentes [67].

#### 1.4.3 Problemas subjacentes

Um conjunto de problemas clássicos dos quais se tem evidência de intratabilidade são utilizados explicitamente ou implicitamente por sistemas criptográficos de chave pública:

Problema do Logaritmo Discreto (Discrete Logarithm Problem – DLP): Seja  $\mathbb{G}$  um grupo cíclico finito e g um gerador de  $\mathbb{G}$ . Dado  $\langle g, g^a \rangle$ , com escolha uniformemente aleatória de  $a \in \mathbb{Z}_{|\mathbb{G}|}$ , encontrar a.

Problema Diffie-Hellman Computacional (Computational Diffie Hellman Problem – CDHP): Seja  $\mathbb{G}$  um grupo cíclico finito e g um gerador de  $\mathbb{G}$ . Dado  $\langle g, g^a, g^b \rangle$  com escolha uniformemente aleatória de  $a, b \in \mathbb{Z}_{|\mathbb{G}|}$ , encontrar  $g^{ab} \in \mathbb{G}$ .

O algoritmo mais eficiente para cálculo de logaritmos discretos [68] é uma variação do algoritmo de cálculo de índices [69] e apresenta complexidade sub-exponencial. Para um grupo de pontos em curva elíptica, o DLP consiste em obter a a partir do resultado da operação de multiplicação de ponto aP. Existem evidências de que a técnica de cálculo de índices não possa ser estendida para grupos de pontos em curvas elípticas e, assim, a complexidade do problema DLP em curvas elípticas (*Elliptic Curve Discrete Logarithm Problem* – ECDLP) mantém-se estritamente exponencial [70].

A derivação de problemas análogos aos problemas ditos convencionais, no contexto de emparelhamentos bilineares, é direta:

Problema Diffie-Hellman Bilinear (Bilinear Diffie-Hellman Problem – BDHP): Seja  $\mathbb{G}_1$ ,  $\mathbb{G}_2$ ,  $\mathbb{G}_T$  grupos adequados à instanciação de um emparelhamento bilinear admissível e e sejam P um gerador de  $\mathbb{G}_1$  e Q um gerador de  $\mathbb{G}_2$ . Dado  $\langle P, aP, bP, cP, Q, aQ, bQ, cQ \rangle$ , com escolhas uniformemente aleatórias de  $a, b, c \in \mathbb{Z}_{|\mathbb{G}_T|}$ , calcular  $e(P, Q)^{abc} \in \mathbb{G}_T$  [66].

Pode-se perceber que a intratabilidade do BDHP implica a dificuldade do DLP em  $\mathbb{G}_1$ ,  $\mathbb{G}_2$  e  $\mathbb{G}_T$ , visto que o cálculo de logaritmos discretos em  $\mathbb{G}_T$  fornece um oráculo para

o cálculo do ECDLP. Assim, a dificuldade do ECDLP nos grupos aditivos deve ser tal que o cálculo subexponencial do DLP em  $\mathbb{G}_T$  permaneça difícil [71].

#### 1.4.4 Cálculo de emparelhamentos

Por ser uma área de pesquisa nova, a criptografia baseada em emparelhamentos apresenta uma infinidade de opções do ponto de vista algorítmico. A escolha de parâmetros e algoritmos ainda encontra-se particularmente longe de consolidação. Desta forma, os trabalhos publicados na literatura refletem uma extensa experimentação com diversas escolhas de parâmetros, a fim de encontrar um ponto ótimo entre a escolha da curva e o desempenho da aritmética [25].

São conhecidos dois algoritmos para o cálculo de emparelhamentos bilineares: o algoritmo de Miller [57, 58] e as redes elípticas [72], tendo o primeiro recebido significativa atenção na literatura. Duas das instanciações de emparelhamentos consideradas mais eficientes são o emparelhamento  $\eta_T$  [1], uma modificação do emparelhamento de Tate [22] para curvas supersingulares definidas sobre um corpo finito binário; e o emparelhamento R-ate [3] sobre curvas ordinárias primas. Entretanto, diversas famílias de curvas são adequadas para instanciação de emparelhamentos, apresentando características distintas que influenciam o desempenho da aritmética empregada para o cálculo de emparelhamentos. Uma dessas características é o grau de mergulho da curva que controla diretamente o tamanho do corpo finito subjacente à curva e o grau da extensão do corpo utilizado na aritmética. Na literatura, já foram relatadas as descobertas de curvas com graus de mergulho diversos, como curvas MNT (k = 3, 4, 6) [73], curvas BN (k = 12) [74] e mais recentemente, curvas com grau de mergulho significativamente maior (k = 8, 16, 18, 32, 36, 40) [75]. O grau de mergulho representa um compromisso direto entre complexidade da aritmética na extensão do corpo e eficiência na aritmética do corpo base, sendo estes níveis de aritmética estimados como os mais solicitados durante o cálculo de um emparelhamento [19].

O cálculo de um emparelhamento bilinear pelo Algoritmo de Miller emprega teoria de divisores de pontos em curvas elípticas. Esta seção esboça as principais definições e fornece uma forma contemporânea do algoritmo.

#### **Divisores**

Um divisor é uma soma formal de pontos na curva  $E(\bar{\mathbb{F}}_q)$ :

$$\mathcal{D} = \sum_{P \in E} d_P(P),\tag{1.5}$$

onde  $d_P$  é um inteiro e (P) é um símbolo formal. O grau de um divisor é a soma de seus coeficientes não-nulos  $deg(\mathcal{D}) = \sum_{P \in E} d_P$ . Divisores podem envolver símbolos formais

para vários pontos na curva elíptica, mas limita-se o enfoque a divisores de funções, por possuírem poucos símbolos. O divisor de uma função f(x,y) = 0 contém apenas os termos  $d_P(P)$  tais que P = (x,y) está na curva E(x,y) = 0 e na função f(x,y) = 0, ou seja, os pontos em que E e f se encontram. Para qualquer ponto P na curva elíptica tal que E e f não têm intersecção,  $d_p = 0$ . O suporte de um divisor  $\mathcal{D}$  é o conjunto de pontos com coeficientes não-nulos  $supp(\mathcal{D}) = \{P \in E | n_P \neq 0\}$ .

Uma estrutura de grupo abeliano aditivo é definida no conjunto dos divisores pela soma dos coeficientes correspondentes em suas somas formais. Assim:

$$\sum_{P \in E} m_P(P) + \sum_{P \in E} n_P(P) = \sum_{P \in E} (m_P + n_P)(P)$$

$$n\mathcal{D} = \sum_{P \in E} (nd_P)(P). \tag{1.6}$$

#### Funções racionais sobre uma curva elíptica

Uma função f(x,y) em um corpo finito  $\mathbb{F}_q$  é dita racional se f pode ser escrita como a razão entre polinômios P(x,y) e Q(x,y) em  $\mathbb{F}_q$ . Um função racional está sobre uma curva  $E(\mathbb{F}_q)$  se f(x,y)=0 e E(x,y)=0 têm ao menos uma solução em comum. Utiliza-se a notação  $P \in f \cap E$  para um ponto P=(x,y) que satisfaz esta condição.

Seja f(x,y) uma função racional sobre E(x,y)=0. Para um ponto  $P\in f\cap E, P$  é chamado zero se f(P)=0 e pólo se  $f(P)=\infty$ . Para todo ponto  $P\in E(\mathbb{F}_q)$ , existe uma função racional u com u(P)=0 tal que toda função racional não-nula f pode ser escrita como  $f(P)=u^ds(P)$  para algum inteiro d e uma função racional s, tal que  $s(P)\notin\{0,\infty\}$ . A função u é chamada uniformizador e pode ser qualquer reta ax+by+c=0 que passa por P sem ser tangente a E em P. Define-se a ordem de f em P, denotada por  $ord_P(f)$  como d. Se P é um zero da função f, então  $ord_P(f)>0$  e P tem multiplicidade  $ord_P(f)$ . Se P é um pólo de f, então a  $ord_P(f)<0$  e P tem multiplicidade  $-ord_P(f)$  [76].

#### Divisor de uma função racional

O divisor de uma função racional f é chamado divisor principal:

$$div(f) = \sum_{P \in E} ord_P(P). \tag{1.7}$$

Sabe-se que  $deg(\mathcal{D}) = 0$  e  $\sum_{P \in E} d_P P = \infty$  se e somente se  $\mathcal{D}$  é principal. Dois divisores  $\mathcal{C}$  e  $\mathcal{D}$  são equivalentes  $(\mathcal{C} \sim \mathcal{D})$  se a diferença  $\mathcal{C} - \mathcal{D}$  é um divisor principal. Para avaliar uma função racional f em um divisor  $\mathcal{D}$  com suporte disjunto ao suporte de div(f), calcula-se [76]:

$$f(\mathcal{D}) = \prod_{P \in supp(\mathcal{D})} f(P)^{n_P}.$$

(1.8)

Seja  $P \in E(\mathbb{F}_q)[r]$  e seja  $\mathcal{D}_P$  um divisor equivalente a  $(P) - (\infty)$ . O divisor  $r\mathcal{D}_P$  é principal e existe uma função  $f_{r,P}$  tal que  $div(f_{r,P}) = r\mathcal{D}_P = r(P) - r(\infty)$  [23].

#### 1.4.5Algoritmo de Miller

O Algoritmo de Miller [57, 58] constrói  $f_{r,P}$  em estágios e avalia esta função sobre um divisor  $\mathcal{D} \sim (Q) - (\infty)$  utilizando um método recursivo.

Primeiramente, seja  $P \in E(\mathbb{F}_q)[r]$  e  $Q \in \mathbb{F}_{q^k}$ . Seja  $\mathcal{D}$  o divisor (Q+R)-(R) equivalente a  $(Q) - (\infty)$ . Para qualquer inteiro c, existe uma função de Miller  $f_{c,P}$  com divisor  $(f_{c,P}) = c(P) - (cP) - (c-1)(\infty)$ . Então, para quaisquer inteiros  $a, b, \text{ com } g_{aP,bP}$  a linha entre os pontos aP e bP, temos que [23]:

$$f_{a+b,P}(\mathcal{D}) = f_{a,P}(\mathcal{D}) \cdot f_{b,P}(\mathcal{D}) \cdot \frac{g_{aP,bP}(\mathcal{D})}{g_{(a+b)P,-(a+b)P}(\mathcal{D})}.$$

(1.9)

Para calcular  $\langle P, Q \rangle_r = f_{r,P}(\mathcal{D})$ , o Algoritmo de Miller utiliza esta relação para construir e avaliar aplicações de funções de Miller no divisor  $\mathcal{D}$ , como mostrado no Algoritmo 1.1.

#### Algoritmo 1.1 Algoritmo de Miller [57, 58].

```

Entrada: r = \sum_{i=0}^{\log_2(r)} r_i 2^i, P, \mathcal{D} \sim (Q) - (\infty).

Saída: f_{r,P}(\mathcal{D}).

1: T \leftarrow P

2: f \leftarrow 1

3: for i = \lfloor \log_2(r) \rfloor - 1 downto 0 do

f \leftarrow 2I

f \leftarrow f^2 \cdot \frac{g_{T,T}(\mathcal{D})}{g_{2T,-2T}(\mathcal{D})}

if r_i = 1 then

6:

T \leftarrow T + P

f \leftarrow f \cdot \frac{g_{T,P}(\mathcal{D})}{g_{T+P,-(T+P)}(\mathcal{D})}

7:

8:

10: end for

11: return f

```

Considerando que  $g_{T,P}(\mathcal{D}) = l((Q+R)-(R)) = \frac{l(Q+R)}{l(R)}$ , com l a linha que passa por Te P na adição T+P; e  $g_{T,T}(\mathcal{D})=\frac{v(Q+R)}{v(R)}$ , com v a vertical que passa por T na duplicação 2T, pode-se reescrever o Algoritmo de Miller na forma do Algoritmo 1.2.

#### Algoritmo 1.2 Algoritmo de Miller [57, 58].

```

Entrada: r = \sum_{i=0}^{\log_2 r} r_i 2^i, P, Q + R, R.

Saída: \langle P, Q \rangle_r.

1: T \leftarrow P

2: f \leftarrow 1

3: for i = \lfloor \log_2(r) \rfloor - 1 downto 0 do

4: T \leftarrow 2T

5: f \leftarrow f^2 \cdot \frac{l(Q+R)v(R)}{v(Q+R)l(R)}

6: if r_i = 1 then

7: T \leftarrow T + P

8: f \leftarrow f \cdot \frac{l(Q+R)v(R)}{v(Q+R)l(R)}

9: end if

10: end for

11: return f

```

#### 1.4.6 Emparelhamento de Tate

O emparelhamento de Tate de ordem r é o mapa:

$$e_r$$

:  $E(\mathbb{F}_q)[r] \times E(\mathbb{F}_{q^k})[r] \to \mathbb{F}_{q^k}^*$

$e_r(P,Q) = f_{r,P}(\mathcal{D})^{(q^k-1)/r},$  (1.10)

para algum divisor  $\mathcal{D} \sim (Q) - (\infty)$ . Se escolhemos R com coordenadas em um subcorpo de  $\mathbb{F}_{q^k}$ , a potência com expoente  $(q^k-1)/r$  elimina todos os fatores l(R), v(R) no Algoritmo 1.2. Isto acontece porque  $(q-1)|(q^k-1)/r$  e, pelo pequeno Teorema de Fermat,  $a^{(q-1)}=1$ . Fazendo  $R=\infty$  no Algoritmo 1.2, temos ainda que  $e_r(P,Q)=f_{r,P}(Q)^{(q^k-1)/r}$  [23].

Para um emparelhamento simétrico, pode-se escolher o mapa de distorção de forma que a coordenada x de  $\psi(P)$  esteja em um subcorpo de  $\mathbb{F}_{q^k}$ . Assim, os fatores v(Q) também serão eliminados pela exponenciação final [1].

$E^t(\mathbb{F}_q)$  de uma curva  $E(\mathbb{F}_q)$  é dado por  $y^2=x^3+z^2ax+z^3b$  para todo não-resíduo z de grau d.

Finalmente, pode-se eliminar a última contribuição do laço de Miller, pois necessariamente esta contribuição ao acumulador irá estar em um subcorpo [23]. O Algoritmo 1.3 apresenta a especialização do Algoritmo de Miller para o cálculo do emparelhamento de Tate [19].

```

Algoritmo 1.3 Emparelhamento de Tate [19].

```

```

Entrada: r = \sum_{i=0}^{\log_2 r} r_i 2^i, P, Q.

Saída: e_r(P,Q).

1: T \leftarrow P

2: f \leftarrow 1

s \leftarrow r - 1

4: for i = |\log_2(s)| - 1 downto 0 do

T \leftarrow 2T

f \leftarrow f^2 \cdot l_{T,T}(Q)

6:

if s_i = 1 then

T \leftarrow T + P

f \leftarrow f \cdot l_{T,P}(Q)

9:

10:

11: end for

12: return f^{(q^k-1/r)}

```

## 1.4.7 Emparelhamento de Weil

O emparelhamento de Weil [58] é definido classicamente como:

$$e_w : E(\mathbb{F}_{q^k})[r] \times E(\mathbb{F}_{q^k})[r] \to \mathbb{F}_{q^k}^*$$

$$e_r(P,Q) = \frac{f_{r,Q}(\mathcal{D}_{\mathcal{P}})}{f_{r,P}(\mathcal{D}_{\mathcal{Q}})}, \qquad (1.11)$$

para divisores  $\mathcal{D}_{\mathcal{P}} \sim (P) - (\infty)$  e  $\mathcal{D}_{\mathcal{Q}} \sim (Q) - (\infty)$ . Uma das funções de Miller pode ser acelerada escolhendo o acumulador  $P \in E(\mathbb{F}_q)[r]$ , quando é comumente chamada de Miller leve, em contraste à função com acumulador  $Q \in E(\mathbb{F}_{q^k})[r]$  chamada de Miller completa [77]. A princípio, não há exponenciação final como no emparelhamento de Tate, mas introduzir um expoente  $(q^k - 1)$  permite eliminar as linhas verticais, como no caso anterior. O emparelhamento de Weil é examinado no Capítulo 7.

### 1.4.8 Emparelhamento $\eta_T$ [1]

O emparelhamento  $\eta_T$ , proposto por Barreto et al. em 2004 é uma especialização do emparelhamento de Tate exclusiva para curvas supersingulares sobre corpos de característica pequena (2 ou 3). Esta especialização aplica o método *eta* desenvolvido por Duursma e Lee para curvas hiperelípticas [78]. Restringindo a definição para curvas supersingulares binárias da forma  $y^3 + y = x^3 + x + b$ , este emparelhamento define o mapa:

$$\eta_T : E(\mathbb{F}_{2^m})[r] \times E(\mathbb{F}_{2^{km}})[r] \to \mathbb{F}_{2^{km}}^*,$$

$$\eta_T(P,Q) = f_{T,P}(Q)^{(2^{km}-1)/r}, \tag{1.12}$$

O Algoritmo de Miller pode ser também especializado para o cálculo do emparelhamento  $\eta_T$ . Para isso, é preciso explorar a forma simples dos divisores de funções em curvas supersingulares e embutir a definição do mapa de distorção associado no cálculo do emparelhamento. O Algoritmo 1.4 descreve o método proposto por [79] para calcular a fórmula fechada do emparelhamento apresentada em [1]. Este emparelhamento é revisitado nos Capítulos 5 e 7.

#### **Algoritmo 1.4** Emparelhamento $\eta_T$ em curva supersingular binária

```

Entrada: P = (x_P, y_P), Q = (x_Q, y_Q) \in E(\mathbb{F}_{2^m})[r].

```

Saída:  $\eta_T(P,Q) \in \mathbb{F}_{2^{4m}}^*$ .

**Nota:**  $\delta = b$  se  $m \equiv 1,7 \pmod 8$ ,  $\delta = (1-b)$  caso contrário;  $\alpha = 0$  se  $m \equiv 3 \pmod 4$ ,  $\alpha = 1$  caso contrário;  $\beta = b$  se  $m \equiv 1,3 \pmod 8$ ,  $\beta = (1-b)$  caso contrário.

```

1: y_P \leftarrow y_P + 1 - \delta

```

2:

$$u \leftarrow x_P + \alpha, v \leftarrow x_Q + \alpha$$

3:

$$g_0 \leftarrow u \cdot v + y_P + y_Q + \beta$$

4:

$$g_1 \leftarrow u + x_Q, g_2 \leftarrow v + x_P^2$$

5:

$$G \leftarrow g_0 + g_1 s + t$$

6:

$$L \leftarrow (g_0 + g_2) + (g_1 + 1)s + t$$

7:

$$F \leftarrow L \cdot G$$

8: for

$$i \leftarrow 1$$

to  $\frac{m-1}{2}$  do

9:

$$x_P \leftarrow \sqrt{x_P}, y_P^2 \leftarrow \sqrt{y_P}, x_Q \leftarrow x_Q^2, y_Q \leftarrow y_Q^2$$

10:

$$u \leftarrow x_P + \alpha, v \leftarrow x_Q + \alpha$$

11:

$$g_0 \leftarrow u \cdot v + y_P + y_Q + \beta$$

12:

$$g_1 \leftarrow u + x_Q$$

13:

$$G \leftarrow g_0 + g_1 s + t$$

14:

$$F \leftarrow F \cdot G$$

15: end for

16: **return**

$$F^{(2^{2m}-1)(2^m+1\pm 2^{\frac{m+1}{2}})}$$

## 1.4.9 Emparelhamento ate [2]

O emparelhamento ate proposto por Hess et al. em 2005 permuta os argumentos do emparelhamento de Tate e generaliza o emparelhamento eta para curvas não-supersingulares com traço de Frobenius pequeno. Seja  $\pi_q: E \to E$  o endomorfismo de Frobenius definido por  $\pi_q(x,y) = (x^q,y^q)$ . Seja  $\mathbb{G}_1 = E[r] \cap Ker(\pi_q - [1])$ ,  $\mathbb{G}_2 = E[r] \cap Ker(\pi_q - [q])$ , T = t - 1. Seja  $N = \gcd(T^k - 1, q^k - 1)$ ,  $T^k - 1 = LN$ . O emparelhamento ate é o mapa [2]:

$$a_T$$

:  $\mathbb{G}_1 \times \mathbb{G}_2 \to \mathbb{F}_{q^k}^*$

$a_T(Q, P) = f_{T,Q}(P)^{c_T(q^k - 1)/N},$  (1.13)

onde  $c_T = \sum_{i=0}^{k-1-i} q^i \equiv kq^{k-1} \pmod{r}$ . O emparelhamento ate é bilinear e não-degenerado se r não divide L. O Algoritmo 1.5 apresenta a especialização do Algoritmo de Miller para o cálculo do emparelhamento ate [19].

#### Algoritmo 1.5 Emparelhamento ate [19]

```

Entrada: t = \sum_{i=0}^{\log_2 t} t_i 2^i, Q, P.

Saída: a_T(Q, P).

1: T \leftarrow P

2: f \leftarrow 1

3: s \leftarrow t-1

4: for i = |\log_2(s)| - 1 downto 0 do

f \leftarrow f^2 \cdot l_{T,T}(P)

6:

if t_i = 1, i \neq 0 then

T \leftarrow T + P

f \leftarrow f \cdot l_{T,O}(T)

9:

end if

10:

11: end for

12: return f^{(q^k-1/r)}

```

### 1.4.10 Emparelhamento R-ate [3]

O emparelhamento R-ate, proposto por Lee, Lee e Park em 2008 é, por sua vez, uma generalização do emparelhamento ate que aprimora sua eficiência. Este emparelhamento calcula um emparelhamento bilinear a partir da razão entre dois emparelhamentos bilineares e requer duas aplicações do Algoritmo de Miller com um número pequeno de interações [3]. Para uma escolha cuidadosa de inteiros a, b, A, B, com A = aB + b, o emparelhamento R-ate é o mapa [3]:

$$e_{a} : E(\mathbb{F}_{q}^{k})[r] \times E(\mathbb{F}_{q})[r] \to \mathbb{F}_{q^{k}}^{*}$$

$$e_{a}(Q, P) = f_{a,BQ}(P) \cdot f_{b,Q}(P) \cdot \frac{g_{aBQ,bQ}(P)}{g_{AQ}(P)}$$

$$e_{a}(Q, P) = (f \cdot (f \cdot l_{aQ,Q}(P))^{q} \cdot l_{\pi(aQ+Q)}(P)^{(q^{k}-1)/r}.$$

(1.14)

#### 1.4.11 Emparelhamento otimal

Pode-se perceber que a principal otimização aplicada ao Algoritmo de Miller é a diminuição do número de iterações do laço principal do algoritmo. Vercauteren [24] estabelece que qualquer emparelhamento cujo laço de Miller pode ser truncado para  $\log_2(r)/\phi(k)$  é chamado de emparelhamento otimal e prova ainda que  $\log_2(r)/\phi(k)$  iterações é uma cota mínima para qualquer emparelhamento não-degenerado em curvas elípticas sem endomorfismos eficientemente computáveis que não sejam potências de Frobenius. Neste sentido, os emparelhamentos  $\eta_T$  e R-ate são otimais. O emparelhamento ate otimal estudado no Capítulo 6 é outro exemplo de emparelhamento otimal.

## 1.5 Contribuições

Esta seção apresenta uma relato não-cronológico dos resultados obtidos durante a execução deste trabalho, organizados em duas partes: implementação de criptografia de curvas elípticas e de criptografia baseada em emparelhamentos. Estas contribuições foram disponibilizadas na forma de uma biblioteca de *software* descrita ao final da seção. Nem todos os trabalhos discutidos nessa seção estão incluídos na tese, mas decidiu-se por divulgá-los para manter um relatório do progresso do autor.

### 1.5.1 Implementação de criptografia de curvas elípticas

A primeira etapa do trabalho consistiu na implementação de corpos e curvas elípticas binárias em sensores em fio. O baixo poder computacional dos sensores torna inviável a utilização de algoritmos convencionais de criptografia de chave pública (RSA/DSA, por exemplo) e, até recentemente, primitivas de segurança como sigilo, autenticação e integridade em RSSFs eram alcançadas apenas através de técnicas de criptografia simétrica [80, 81]. Atualmente, criptografia de curvas elípticas [8, 7] e criptografia baseada em emparelhamentos [10] têm sido apontadas como alternativas promissoras aos métodos convencionais de criptografia assimétrica em redes de sensores [82], por exigir requisitos

menores de processamento e armazenamento para o mesmo nível de segurança. Estas características estimulam a busca de algoritmos cada vez mais eficientes para implementação nestes dispositivos.

Durante a execução desta etapa, foram detectadas otimizações para aritmética de curvas elípticas sobre corpos binários, ampliando os seus limites de eficiência e viabilidade de aplicação. Particularmente, os resultados experimentais demonstram que o desempenho de curvas elípticas sobre corpos binários pode equiparar-se ao desempenho de curvas sobre corpos primos em implementações cuidadosas que consideram as características da plataforma. Este resultado contraria a observação de que dispositivos tão escassos em recursos não são suficientemente equipados para implementação de criptografia de curvas elípticas definidas sobre corpos binários [82, 83].

Como resultados obtidos decorrentes desta etapa, pode-se citar os trabalhos [84, 85, 86] que implementam curvas elípticas em microcontroladores AVR ATmega128 de 8 bits:

- D. F. Aranha, D. Câmara, J. López, L. Oliveira, R. Dahab. Implementação eficiente de criptografia de curvas elípticas em sensores sem fio. 80. Simpósio Brasileiro em Segurança da Informação e de Sistemas Computacionais (SBSEG 2008), 173–186, Gramado, Brasil, 2008;

- 2. **D. F. Aranha**, J. López, L. Oliveira, R. Dahab. *Efficient implementation of elliptic curves on sensor nodes*. Conference on Hyperelliptic curves, discrete Logarithms, Encryption, etc. (CHiLE 2009), Frutillar, Chile, 2009;

- 3. **D. F. Aranha**, R. Dahab, J. López, L. Oliveira. *Efficient implementation of elliptic curve cryptography in wireless sensors*. Advances in Mathematics of Communications, vol. 4, no. 2, 169–187, 2010.

Os dois primeiros aprimoram o estado-da-arte de implementações de criptografia de curvas elípticas em redes de sensores sem fio. Nós sensores representam um extremo no espectro de arquiteturas modernas, por terem recursos particularmente limitados e natureza descartável. Aproveitando as características peculiares da plataforma alvo, particularmente a configuração da hierarquia de memória, foi possível desenvolver otimizações para aritmética nos corpos finitos  $\mathbb{F}_{2^{163}}$  e  $\mathbb{F}_{2^{233}}$  e curva elípticas associadas, produzindo as implementações mais eficientes de quadrado, multiplicação, inversão e redução modular já publicadas para esta plataforma. A aritmética eficiente no corpo permitiu o cálculo de uma mutiplicação de ponto 61% mais rápida que a melhor implementação de curvas elípticas sobre corpos binários e 57% mais rápida que a melhor implementação para o caso primo, considerando o mesmo nível de segurança. O terceiro trabalho consolida estes resultados e é apresentado como Capítulo 2 desta tese.

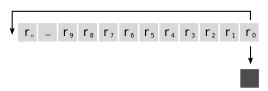

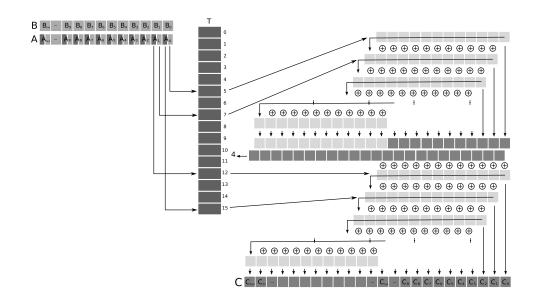

O segundo conjunto de resultados trata da implementação de corpos binários em conjuntos de instruções vetoriais. Em particular, havia interesse em se aproveitar explicitamente instruções de permutação de bytes que codificam implicitamente acessos simultâneos a tabelas de constantes. Cronologicamente, este estudo foi iniciado com a implementação de um corpo razoavelmente grande ( $\mathbb{F}_{2^{1223}}$ ) para o cálculo do emparelhamento  $\eta_T$  em arquiteturas de 64 bits. Posteriormente, verificou-se que as mesmas otimizações eram aplicáveis a corpos muito menores e foi desenvolvida uma formulação da aritmética com granularidade de 4 bits que emprega vastamente as instruções de permutação, produzindo inclusive um novo ainda que ineficiente algoritmo de multiplicação. Esta formulação foi complementada com um estudo detalhado dos impactos algorítmicos da disponibilidade repetina de suporte nativo à multiplicação em um corpo binário recentemente introduzida na arquitetura Intel [87]. A aceleração significativa da operação de multiplicação forçou uma reavaliação de estratégias de implementação para a operação de halving em curvas elípticas binárias e de paralelizações da operação de multiplicação de ponto. Estes resultados são apresentados nos artigos a seguir [88, 89]:

- D, F. Aranha, J. López, D. Hankerson. Efficient Software Implementation of Binary Field Arithmetic Using Vector Instruction Sets. 1st International Conference on Cryptology and Information Security (LATINCRYPT 2010), 144–161, Puebla, Mexico, 2010.

- J. Taverne, A. Faz-Hernández, D. F. Aranha, F. Rodríguez-Henríquez, D. Hankerson, J. López. Software Implementation of Binary Elliptic Curves: Impact of the Carry-less Multiplier on Scalar Multiplication. 13th International Workshop on Cryptographic Hardware and Embedded Systems (CHES 2011), em publicação.

O primeiro trabalho é apresentado como o Capítulo 3 desta tese e obtém ganhos de desempenho em 8%-84% para diversas operações em um corpo binário. Esta formulação eficiente da aritmética permitiu aprimorar o estado da arte [90] para multiplicação de ponto em 27%-30%, desconsiderando o modo de operação em lote [61]. O custo médio de uma multiplicação de ponto em modo lote no nível de segurança de 128 bits foi superado em 10% apenas no segundo trabalho, após a introdução de suporte nativo à multiplicação em um corpo binário. Este último trabalho, apresentado como Capítulo 4, apresenta ainda resultados experimentais para implementações seriais e paralelas da operação de multiplicação de ponto nos níveis de segurança de 112, 128 e 192 bits.

# 1.5.2 Implementação de criptografia baseada em emparelhamentos bilineares

Em seguida, buscou-se estudar protocolos úteis para o fornecimento de serviços de segurança em redes de sensores sem fio. Um exemplos com estas características é o protocolo Sakai-Ohgishi-Kasahara [13] para acordo de chaves não-interativo, providenciando o acordo autenticado de chaves simétricas entre nós sensores sem exigir qualquer comunicação, o que permite importante economia de energia. Outro exemplo é o emprego de assinaturas digitais para transmissão autenticada de mensagens entre um nó específico da rede de sensores e um usuário ou aplicação final. Esta linha de pesquisa produziu os resultados abaixo [91, 92, 93]:

- 1. **D. F. Aranha**, L. B. Oliveira, J. López, R. Dahab. *NanoPBC: implementing cryptographic pairings on an 8-bit platform*. Conference on Hyperelliptic curves, discrete Logarithms, Encryption, etc. (CHiLE 2009), Frutillar, Chile, 2009;

- L. B. Oliveira, D. F. Aranha, C. P. L. Gouvêa, Danilo F. Câmara, M. Scott, J. López, R. Dahab. TinyPBC: Pairings for Authenticated Identity-Based Non-Interactive Key Distribution in Sensor Networks. Computer Communications, vol. 34, no. 3, 485–493, 2011;

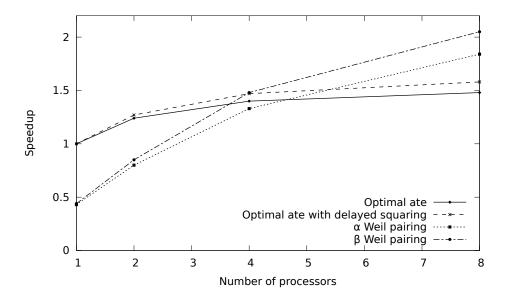

- 3. L. B. Oliveira, A. Kansal, C. P. L. Gouvêa, **D. F. Aranha**, J. López, B. Priyantha, M. Goraczko, F. Zhao. Secure-TWS: Authenticating Node to Multi-user Communication in Shared Sensor Networks. The Computer Journal, em publicação.