#### Instituto de Computação Universidade Estadual de Campinas

## Impacto de Técnicas de Redução do Consumo de Energia no Projeto de SoCs Multimedia

Este exemplar corresponde à redação final da Dissertação devidamente corrigida e defendida por Yang Yun Ju e aprovada pela Banca Examinadora.

Campinas, Junho, 16, 2011.

Prof. Dr. Guido Costa Souza de Araújo (Orientador)

Dissertação apresentada ao Instituto de Computação, UNICAMP, como requisito parcial para a obtenção do título de Mestre em Ciência da Computação.

#### FICHA CATALOGRÁFICA ELABORADA POR ANA REGINA MACHADO – CRB8/5467 BIBLIOTECA DO INSTITUTO DE MATEMÁTICA, ESTATÍSTICA E COMPUTAÇÃO CIENTÍFICA – UNICAMP

Yang, Yun Ju, 1980-

Y16i

Impacto de técnicas de redução do consumo de energia no projeto de SoCs Multimedia / Yang Yun Ju. – Campinas, SP : [s.n.], 2011.

Orientador: Guido Costa Souza de Araújo. Dissertação (mestrado) - Universidade Estadual de Campinas, Instituto de Computação.

1. Circuitos integrados de baixa tensão - Projeto auxiliado por computador. 2. Circuitos integrados - Integração em escala muito ampla - Projeto auxiliado por computador. 3. Circuitos integrados - Integração em escala muito ampla -Projetos e construção. I. Araújo, Guido Costa Souza de, 1962-. II. Universidade Estadual de Campinas. Instituto de Computação. II. Título.

#### Informações para Biblioteca Digital

**Título em Inglês**: The impact of design techniques in the reduction of power consumption of SoCs Multimedia

#### Palavras-chave em Inglês:

Low voltage integrated circuits - Computer-aided design

Integrated circuits - Very large scale integration - Computer-aided design Integrated circuits - Very large scale integration - Design and construction

**Área de concentração:** Ciência da Computação **Titulação:** Mestre em Ciência da Computação

Banca examinadora:

Guido Costa Souza de Araújo [Orientador]

Elmar Uwe Kurt Melcher Paulo Cesar Centoducatte **Data da defesa:** 16-06-2011

Programa de Pós Graduação: Ciência da Computação

### TERMO DE APROVAÇÃO

Dissertação Defendida e Aprovada em 16 de junho de 2011, pela Banca examinadora composta pelos Professores Doutores:

F. Kelce

Prof. Dr. Elmar Uwe Kurt Melcher

LAD / UFCG

Prof. Dr. Paulo Cesar Centoducatte

IC / UNICAMP

Prof. Dr. Guido Costa Souza de Araujo

Juido Aray/

IC / UNICAMP

### Instituto de Computação Universidade Estadual de Campinas

## Impacto de Técnicas de Redução do Consumo de Energia no Projeto de SoCs Multimedia

### Yang Yun Ju

Junho, 16, 2011

#### Banca Examinadora:

- Prof. Dr. Guido Costa Souza de Araújo (Orientador)

- Prof. Dr. Elmar Uwe Kurt Melcher

Departamento de Sistema de Computação, UFCG

- Prof. Dr. Paulo Cesar Centoducatte Instituto de Computação, UNICAMP

- Prof. Dr. Mário Lúcio Côrtes(Suplente) Instituto de Computação, UNICAMP

- Prof. Dr. Norian Marranghello(Suplente)

Departamento de Ciências de Computação e Estatística, UNESP

## Resumo

A indústria de semicondutores sempre enfrentou fortes demandas em resolver problema de dissipação de calor e reduzir o consumo de energia em dispositivos. Esta tendência tem sido intensificada nos últimos anos com o movimento de sustentabilidade ambiental.

A concepção correta de um sistema eletrônico de baixo consumo de energia é um problema de vários níveis de complexidade e exige estratégias sistemáticas na sua construção. Fora disso, a adoção de qualquer técnica de redução de energia sempre está vinculada com objetivos especiais e provoca alguns impactos no projeto. Apesar dos projetistas conheçam bem os impactos de forma qualitativa, as detalhes quantitativas ainda são incognitas ou apenas mantidas dentro do 'know-how' das empresas.

Neste trabalho, de acordo com resultados experimentais baseado num plataforma de SoC¹ industrial, tentamos quantificar os impactos derivados do uso de técnicas de redução de consumo de energia. Nós concentramos em relacionar o fator de redução de energia de cada técnica aos impactos em termo de área, desempenho, esforço de implementação e verificação.

Na ausência desse tipo de dados, que relacionam o esforço de engenharia com as metas de consumo de energia, incertezas e atrasos serão frequentes no cronograma de projeto. Esperamos que este tipo de orientações possam ajudar/guiar os arquitetos de projeto em selecionar as técnicas adequadas para reduzir o consumo de energia dentro do alcance de orçamento e cronograma de projeto.

<sup>&</sup>lt;sup>1</sup>System on Chip

## Abstract

The semiconductor industry has always faced strong demands to solve the problem of heat dissipation and reduce the power consumption in electronic devices. This trend has been increased in recent years with the action of environmental sustainability.

The correct conception of an electronic system for low power consumption is an issue with multiple levels of complexities and requires systematic approaches in its construction. However, the adoption of any technique for reducing the power consumption is always linked with some specific goals and causes some impacts on the project. Although the designers know well that these impacts can affect the design in a quality aspect, the quantitative details are still unknown or just be kept inside the company's know-how.

In this work, according to the experimental results based on an industrial  $SoC^2$  platform, we try to quantify the impacts of the use of low power techniques. We will relate the power reduction factor of each technique to the impact in terms of area, performance, implementation and verification effort.

In the absence of such data, which relates the engineering effort to the goals of power consumption, uncertainties and delays are frequent. We hope that such guidelines can help/guide the project architects in selecting the appropriate techniques to reduce the power consumption within the limit of budget and project schedule.

<sup>&</sup>lt;sup>2</sup>System On Chip

## Agradecimentos

# Sumário

| $\mathbf{R}$     | esum  | ıO     |                                                | vii |

|------------------|-------|--------|------------------------------------------------|-----|

| $\mathbf{A}$     | bstra | ıct    |                                                | ix  |

| $\mathbf{A}_{:}$ | grade | ecimen | atos                                           | xi  |

| 1                | Intr  | oduçã  | 0                                              | 1   |

|                  | 1.1   | Roadr  | nap de Tecnologia de Projeto de Semicondutores | 2   |

|                  | 1.2   | Motiv  | ação                                           | 3   |

|                  | 1.3   | Public | cação                                          | 4   |

|                  | 1.4   | Organ  | ização de Dissertação                          | 4   |

| <b>2</b>         | Low   | Powe   | er Fundamentals and Techniques                 | 7   |

|                  | 2.1   | Power  | dissipation in CMOS technology                 | 7   |

|                  |       | 2.1.1  | Dynamic power dissipation                      | 7   |

|                  |       | 2.1.2  | Static power dissipation                       | 9   |

|                  |       | 2.1.3  | Power-Related Effects                          | 13  |

|                  | 2.2   | Power  | Analysis Model and Estimation Method           | 16  |

|                  |       | 2.2.1  | Internal Power Analysis                        | 17  |

|                  |       | 2.2.2  | Leakage Power Analysis                         | 19  |

|                  |       | 2.2.3  | Net Power Analysis                             |     |

|                  |       | 2.2.4  | Power Estimation Methods                       |     |

|                  | 2.3   | Low F  | Power Techniques Fundamentals                  | 22  |

|                  |       | 2.3.1  | Clock Gating                                   | 22  |

|                  |       | 2.3.2  | Operand Isolation                              | 25  |

|                  |       | 2.3.3  | Multiple Threshold Voltage                     | 28  |

|                  |       | 2.3.4  | Multiple Supply Voltage                        | 29  |

| 3                | Rel   | ated w | vorks                                          | 35  |

|                  | 3.1   | NEC :  | mobile phone system SoC                        | 35  |

|   | 3.2 | Fujitsu | ı low-power test chip                  | 37        |

|---|-----|---------|----------------------------------------|-----------|

|   |     | 3.2.1   | NXP Low-Power SoC                      | 37        |

| 4 | Low | , Powe  | r Design Flow                          | 41        |

| - | 4.1 |         | ard cell based design flow             | 41        |

|   | 4.2 |         | Ower Design Flow                       | 44        |

|   | 1.2 | Low 1   | ower Besign Flow                       |           |

| 5 | Cas | e stud  | y results                              | <b>51</b> |

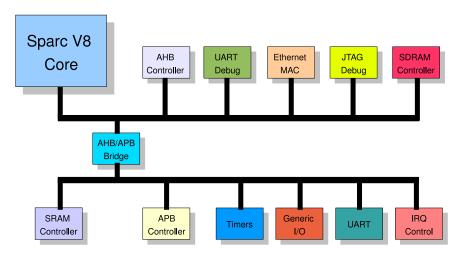

|   | 5.1 | Leon3   | Multiple Processor Platform            | 52        |

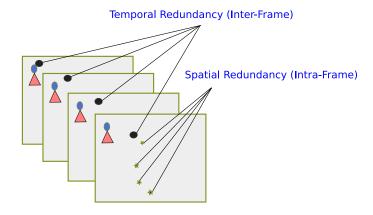

|   | 5.2 | The M   | IPEG-2 Video Decoder                   | 54        |

|   | 5.3 | Platfo  | rm Configuration (Hardware/Software)   | 56        |

|   |     | 5.3.1   | Sparc V8 Core                          | 58        |

|   |     | 5.3.2   | SRAM and SDRAM Memory Controller       | 61        |

|   |     | 5.3.3   | Timers                                 | 62        |

|   |     | 5.3.4   | Generic Input/Output Ports             | 63        |

|   |     | 5.3.5   | UART Controller                        | 63        |

|   |     | 5.3.6   | IRQ Controller                         | 63        |

|   |     | 5.3.7   | External Memory Simulation Model       | 63        |

|   |     | 5.3.8   | MPEG-2 Decoder Modification            | 64        |

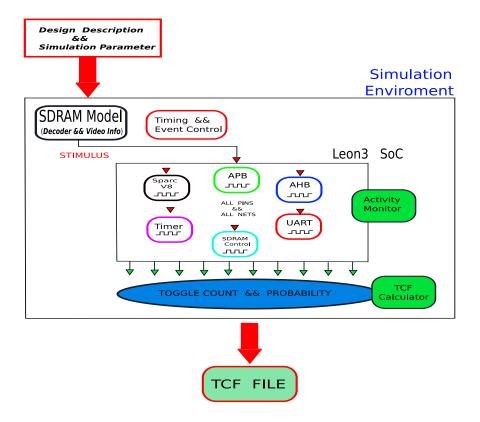

|   |     | 5.3.9   | Extract Switching Activity             | 67        |

|   | 5.4 | Manuf   | facturing Process                      | 69        |

|   |     | 5.4.1   | General Purpose Node                   | 70        |

|   |     | 5.4.2   | Low Power Node                         | 72        |

|   | 5.5 | Baselin | ne Flow                                | 73        |

|   |     | 5.5.1   | System Requirement and Spec Definition | 73        |

|   |     | 5.5.2   | Library Qualification                  | 73        |

|   |     | 5.5.3   | Register Transfer Level Simulation     | 75        |

|   |     | 5.5.4   | Logic Synthesis                        | 75        |

|   |     | 5.5.5   | Design For Test                        | 75        |

|   |     | 5.5.6   | Gate Level Co-Simulation               | 76        |

|   |     | 5.5.7   | Placement and Routing                  | 76        |

|   |     | 5.5.8   | Static Timing Analysis                 | 76        |

|   |     | 5.5.9   | Parasitic Extraction                   | 76        |

|   |     | 5.5.10  |                                        | 76        |

|   |     | 5.5.11  | Baseline Power Estimation              | 77        |

|   |     |         | Experimental Results                   | 77        |

|   | 5.6 |         | Gating Optimization                    | 88        |

|   |     | 5.6.1   | Logic Synthesis                        | 88        |

|   |     | 5.6.2   | Design for Test                        | 88        |

|                           |        | 5.6.3  | Gate Level Co-Simulation                         | . 89  |

|---------------------------|--------|--------|--------------------------------------------------|-------|

|                           |        | 5.6.4  | Placement and Routing                            | . 89  |

|                           |        | 5.6.5  | Static Timing Analysis                           | . 89  |

|                           |        | 5.6.6  | Parasitic Extraction                             | . 90  |

|                           |        | 5.6.7  | Post Layout Co-Simulation                        | . 90  |

|                           |        | 5.6.8  | Power Estimation                                 | . 90  |

|                           |        | 5.6.9  | Experimental Results                             | . 90  |

|                           |        | 5.6.10 | Impacts of Clock Gating                          | . 99  |

|                           | 5.7    | Operar | nd Isolation                                     | . 100 |

|                           |        | 5.7.1  | Details of Implementation and Results            | . 101 |

|                           | 5.8    | Multip | ble Threshold Voltage Optimization               | . 101 |

|                           |        | 5.8.1  | System Specification and Requirement             | . 102 |

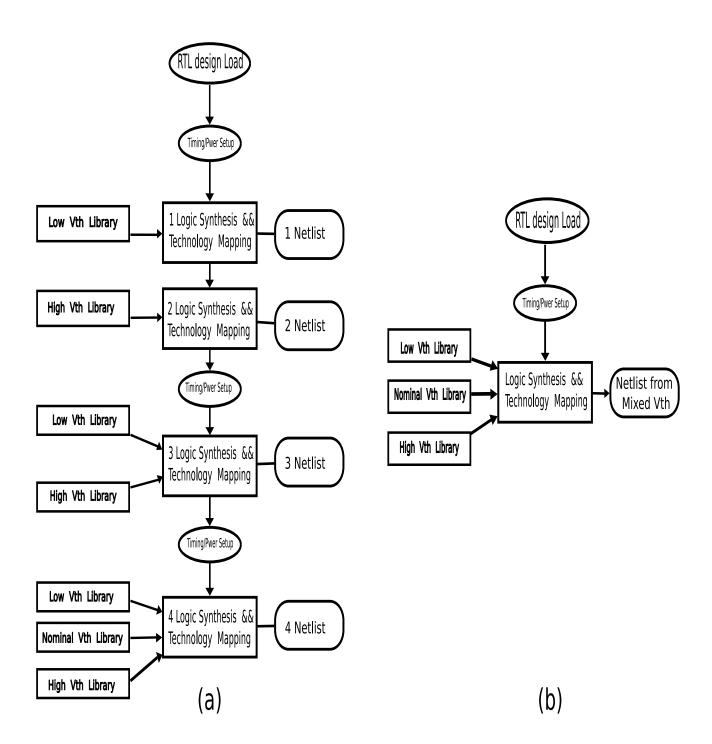

|                           |        | 5.8.2  | Logic Synthesis (Mixed and Incremental Strategy) | . 102 |

|                           |        | 5.8.3  | Design For Test                                  | . 104 |

|                           |        | 5.8.4  | Static Timing Analysis                           | . 105 |

|                           |        | 5.8.5  | Post-Layout Co-Simulation                        | . 105 |

|                           |        | 5.8.6  | Backend Tasks                                    | . 105 |

|                           |        | 5.8.7  | Experimental Results and Impacts                 | . 105 |

|                           | 5.9    | Multip | ole Supply Voltage Optimization                  | . 108 |

|                           |        | 5.9.1  | System Specification and Requirement             | . 108 |

|                           |        | 5.9.2  | Library Qualification of Level Shifters          | . 109 |

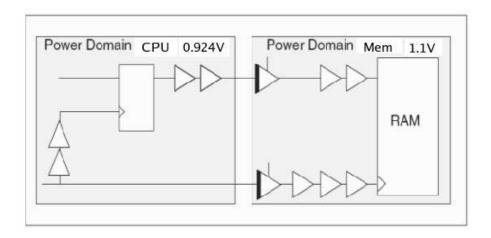

|                           |        | 5.9.3  | Power Architecture and Power Domain Definition   | . 110 |

|                           |        | 5.9.4  | Register Transfer Level Co-Simulation            | . 112 |

|                           |        | 5.9.5  | Logic Synthesis                                  | . 112 |

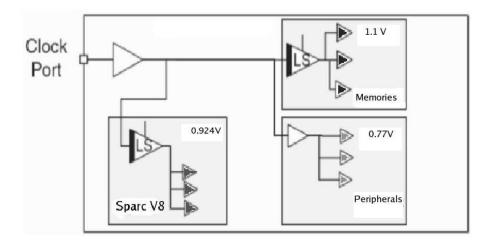

|                           |        | 5.9.6  | Power Rail Planning and Power Grids              | . 113 |

|                           |        | 5.9.7  | Placement and Routing                            | . 114 |

|                           |        | 5.9.8  | Clock Tree Synthesis                             | . 117 |

|                           |        | 5.9.9  | Power Sign-Off                                   | . 118 |

|                           |        | 5.9.10 | Post-layout Co-simulation                        | . 119 |

|                           |        | 5.9.11 | Power Estimation                                 | . 119 |

|                           |        | 5.9.12 | Experimental Results and Impacts                 | . 119 |

|                           | 5.10   | Summa  | ary of all the experimental results              | . 122 |

| 6                         | Con    | clusão | e Trabalhos Futuros                              | 123   |

|                           | 6.1    | Conclu | ısão                                             | . 123 |

|                           | 6.2    | Trabal | lhos Futuros                                     | . 124 |

| $\mathbf{B}_{\mathbf{i}}$ | ibliog | rafia  |                                                  | 126   |

# Lista de Tabelas

| 3.1  | Fujitsu SoC Table                                                 |

|------|-------------------------------------------------------------------|

| 5.1  | Library Corner Case Table                                         |

| 5.2  | Low Power Library Corner Case Table                               |

| 5.3  | Low Power Design Library Qualification Table                      |

| 5.4  | Baseline Power Result at 300MHz                                   |

| 5.5  | Baseline Power Result at 100MHz                                   |

| 5.6  | Clock Gating Power Result at 300MHz                               |

| 5.7  | Impact Comparison between Baseline Flow and Clock Gating Flow 100 |

| 5.8  | Result of the Mixed Synthesis                                     |

| 5.9  | Power distribution of the Mixed Synthesis                         |

| 5.10 | Result of the Incremental Synthesis                               |

| 5.11 | Power distribution of the Incremental Synthesis                   |

| 5.12 | Multiple Power Supply result at 300MHz                            |

| 5.13 | Summary of All the Experimental Results                           |

# Lista de Figuras

| 2.1  | Simplified Inverter Model                                               | 8  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | N-Type MOSFET in (a) Cut-Off Region (b) Linear Region                   | 10 |

| 2.3  | (a) High K Metal Gate (b) Oxide layer modeled as capacitor              | 12 |

| 2.4  | Long term impact of electromigration effect                             | 15 |

| 2.5  | EDA tools power estimation model                                        | 16 |

| 2.6  | Internal Power Model (2 Input AND)                                      | 18 |

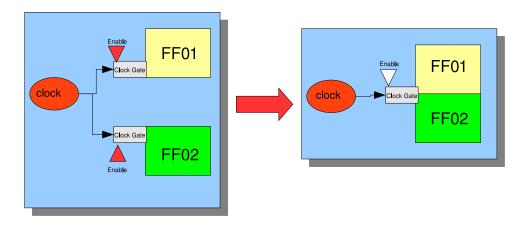

| 2.7  | Clock Gating concept                                                    | 22 |

| 2.8  | Clock Gating cell with DFT feature                                      | 25 |

| 2.9  | Operand Isolation Concept                                               | 26 |

| 2.10 | (a) Current leakage x Timing Delay (b) Library, Leakage and Delay Graph | 29 |

| 2.11 | Multiple $V_{dd}$ Example                                               | 30 |

| 2.12 | Voltage variation vs. Timing delay                                      | 33 |

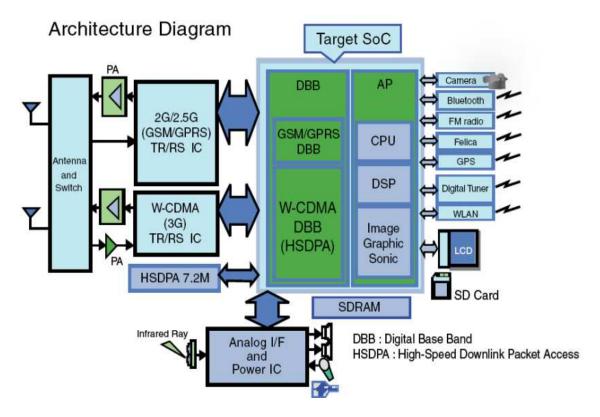

| 3.1  | Architecture of NEC 65nm Cell Phone SoC                                 | 36 |

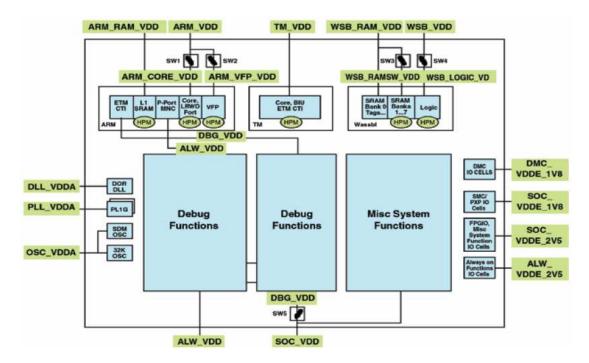

| 3.2  | Architecture of NXP 65nm SoC                                            | 38 |

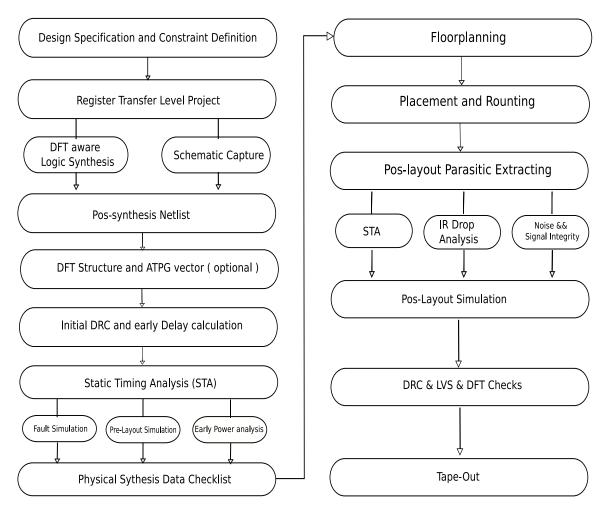

| 4.1  | Cell Based Design Flow                                                  | 42 |

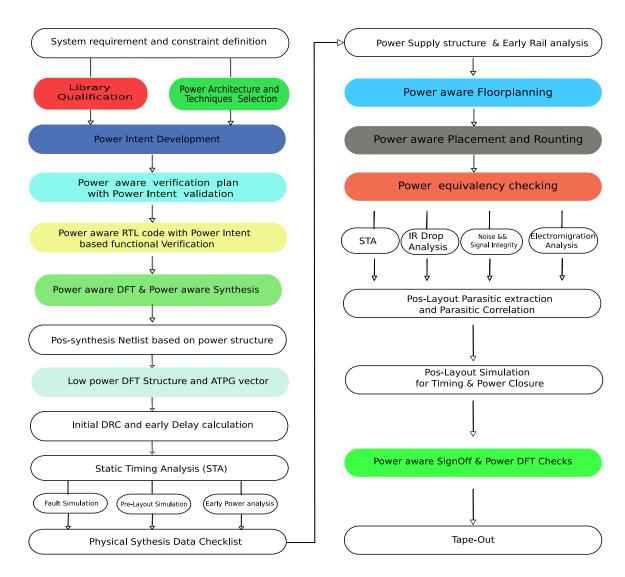

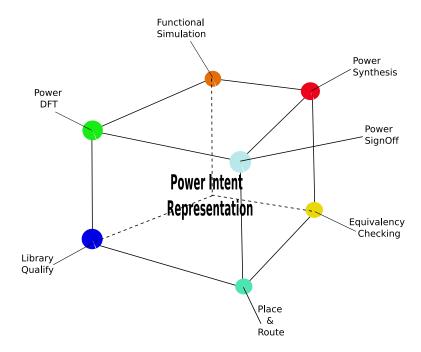

| 4.2  | Low Power Design Flow                                                   | 46 |

| 4.3  | Power Intent Representation in the Low Power Design                     | 47 |

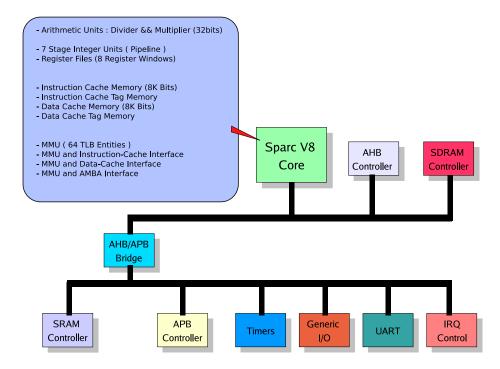

| 5.1  | Leon3 SoC example                                                       | 53 |

| 5.2  | Temporal and Spatial Redundancy of Frame Pictures                       | 55 |

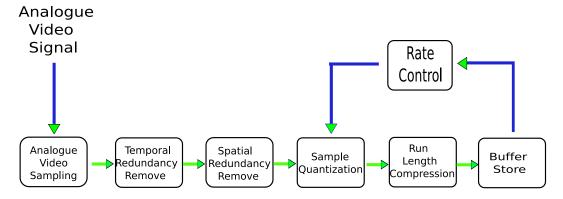

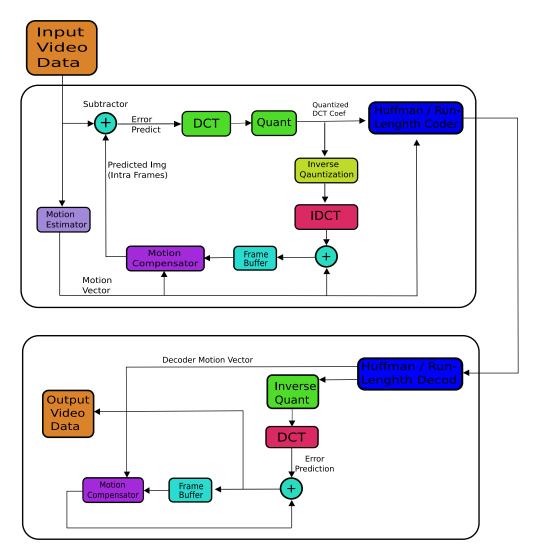

| 5.3  | Basic Operations of MPEG-2 Encoder                                      | 56 |

| 5.4  | MPEG-2 Video Encoder/Decoder Operations                                 | 57 |

| 5.5  | Leon3 System for Power Estimation                                       | 58 |

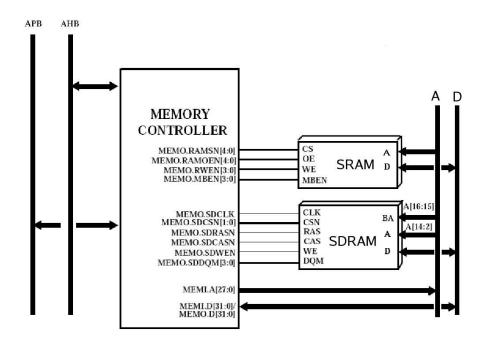

| 5.6  | Leon3 Combined Memory Controller Unit                                   | 61 |

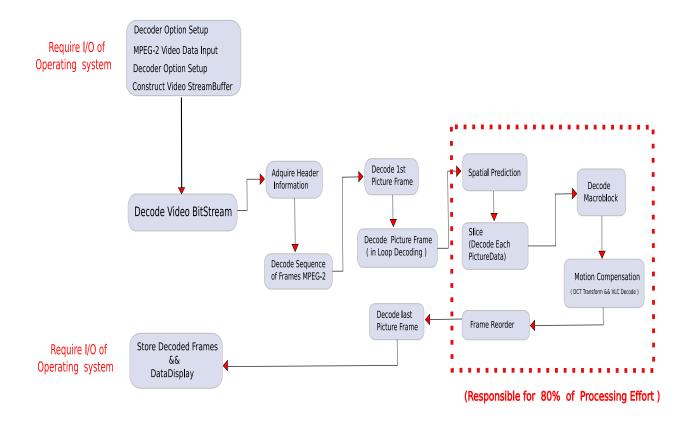

| 5.7  | MPEG-2 Decoder Data Flow                                                | 65 |

| 5.8  | System Simulation and TCF File Construction                             | 69 |

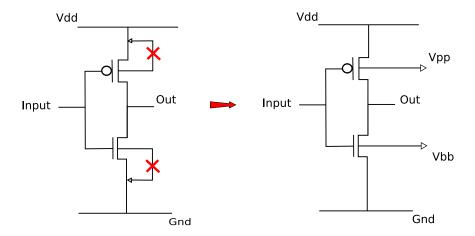

| 5.9  | Inverter Circuit with Well-Bias                                         | 73 |

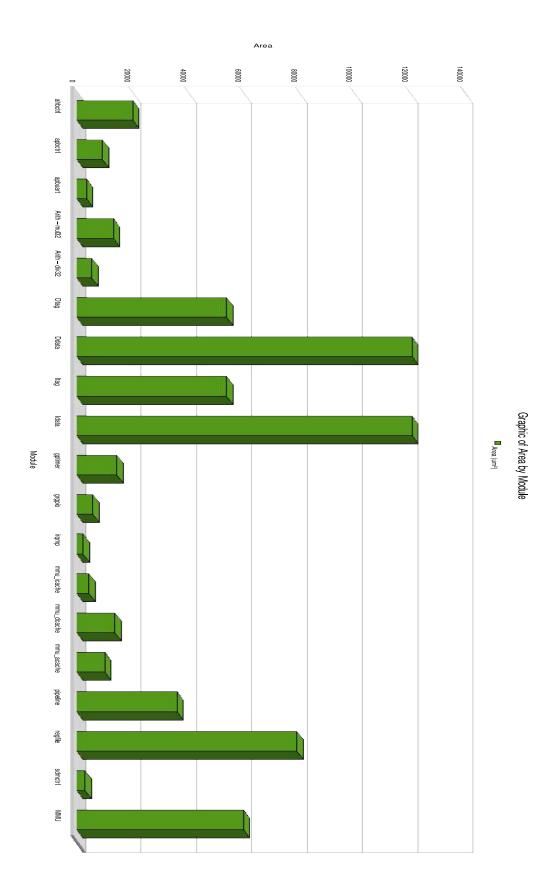

| 5.10 | Baseline at 300MHz - Area by Module                                     | 81 |

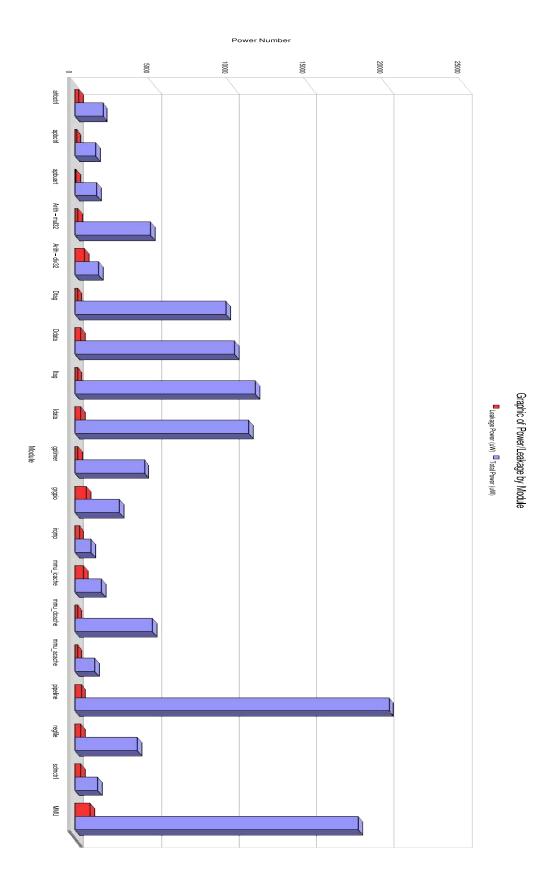

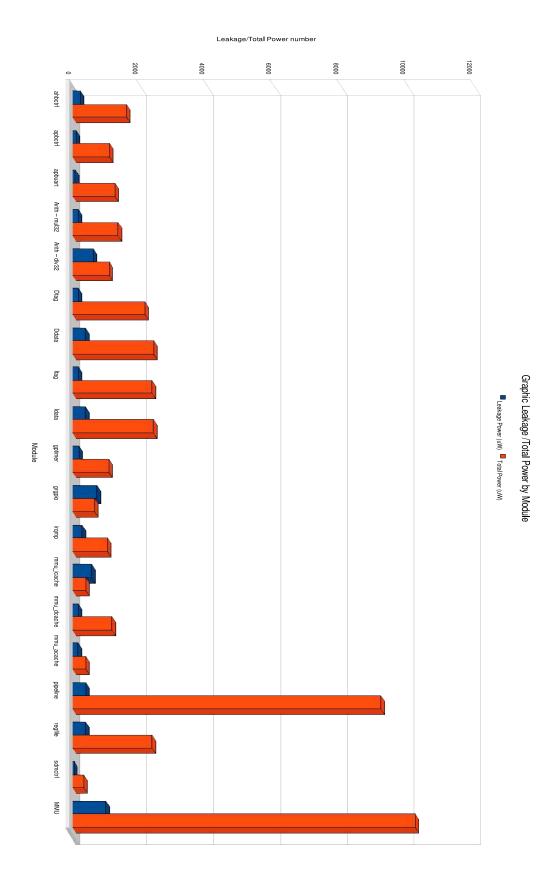

| 5.11 | Baseline at 300MHz - Total Power/Leakage Power by Module                | 82 |

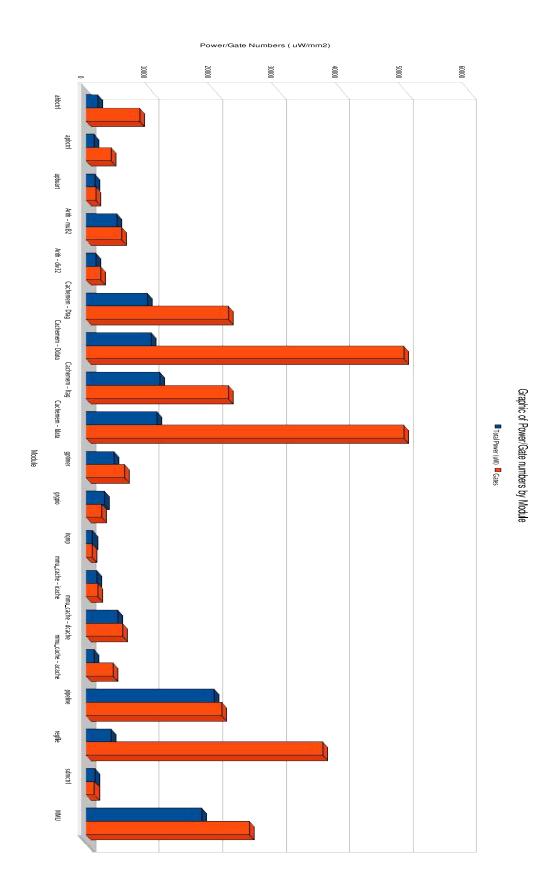

| 5.12 | Baseline at 300MHz - Power and Gate Numbers by Module 83              |

|------|-----------------------------------------------------------------------|

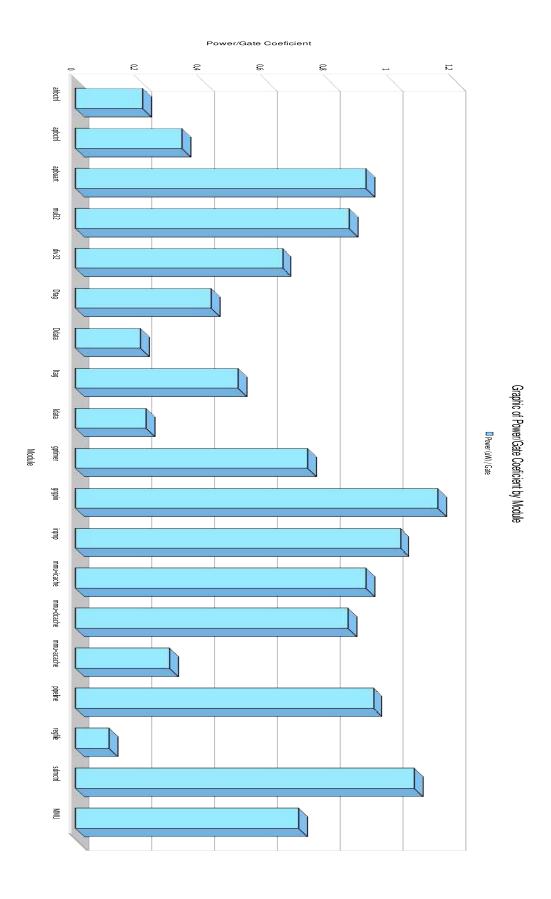

| 5.13 | Baseline at 300MHz - Power/Gate Coefficient by Module 84              |

| 5.14 | Baseline at 100MHz - Total Power/Leakage Power by Module 85           |

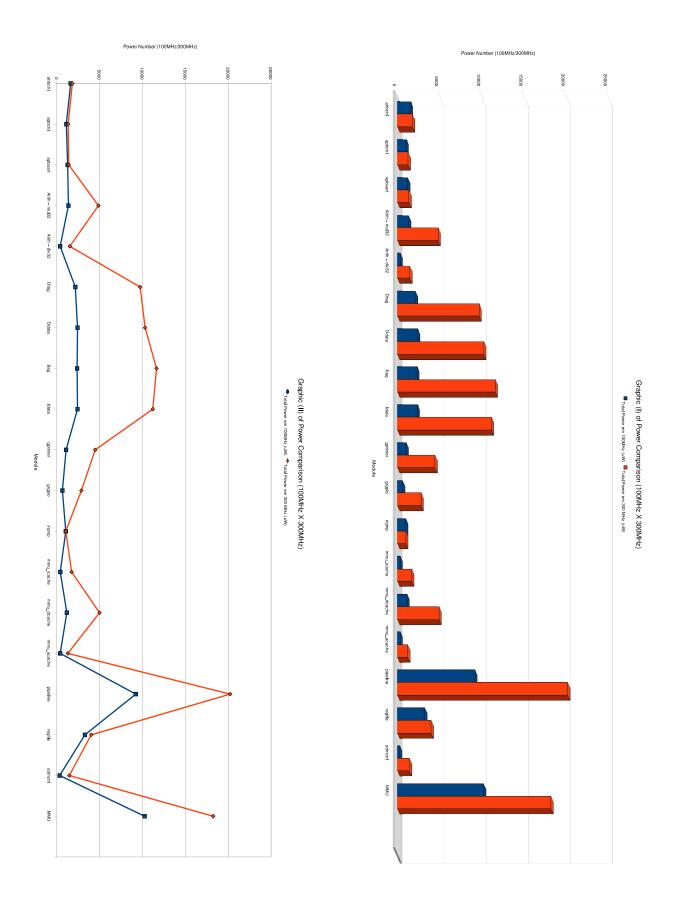

| 5.15 | Baseline Power Comparison(100MHz X 300MHz)                            |

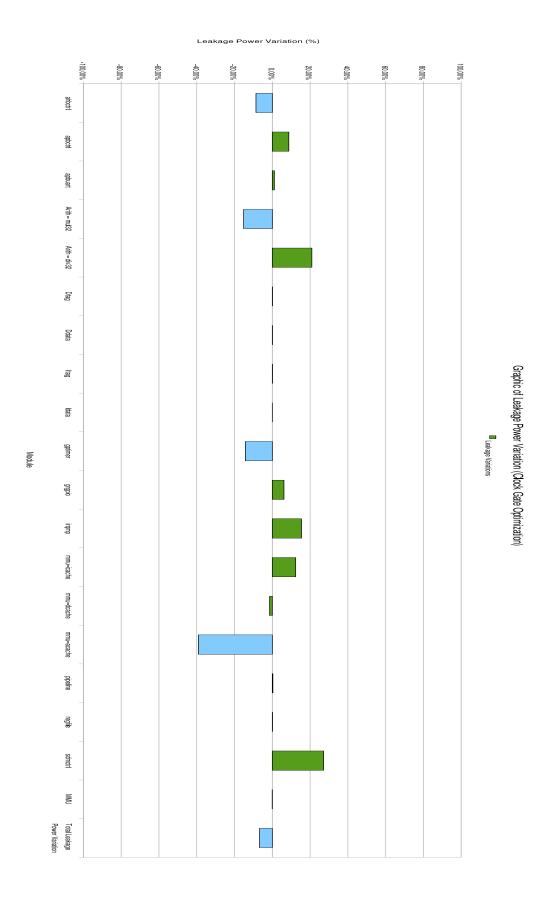

| 5.16 | Leakage Power Variation of Clock Gating Optimization                  |

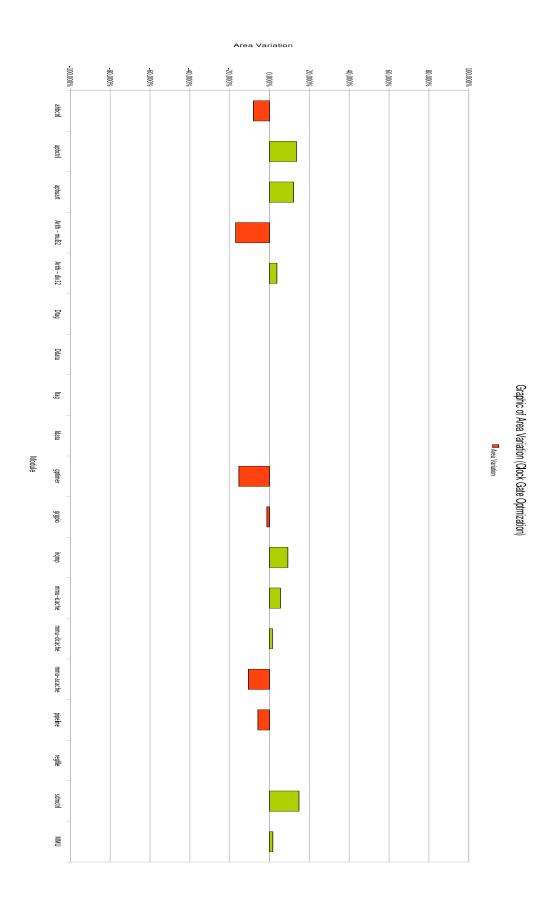

| 5.17 | Area Variation of Clock Gating Optimization                           |

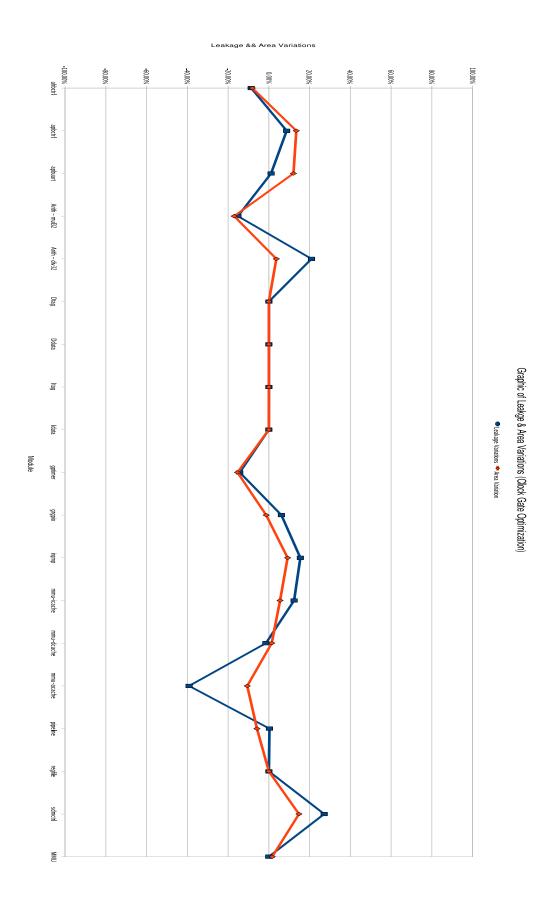

| 5.18 | Area and Leakage Power Variation of Clock Gating Optimization 94      |

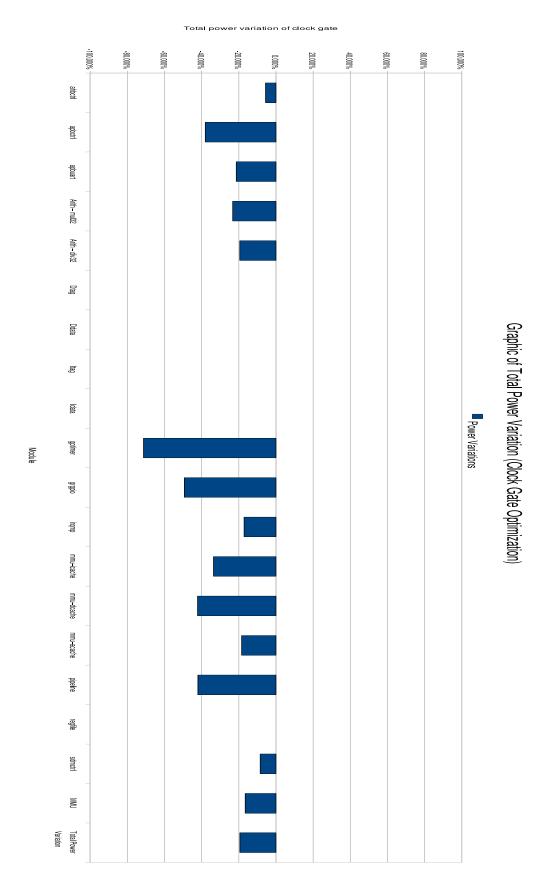

| 5.19 | Total Power Variation of Clock Gating Optimization                    |

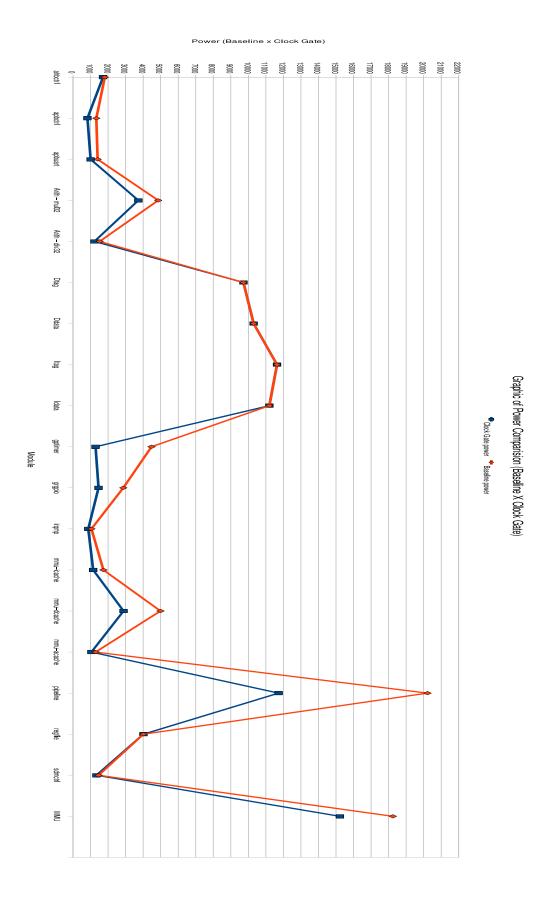

| 5.20 | Total Power Comparison between Clock Gating and Baseline Flow 96      |

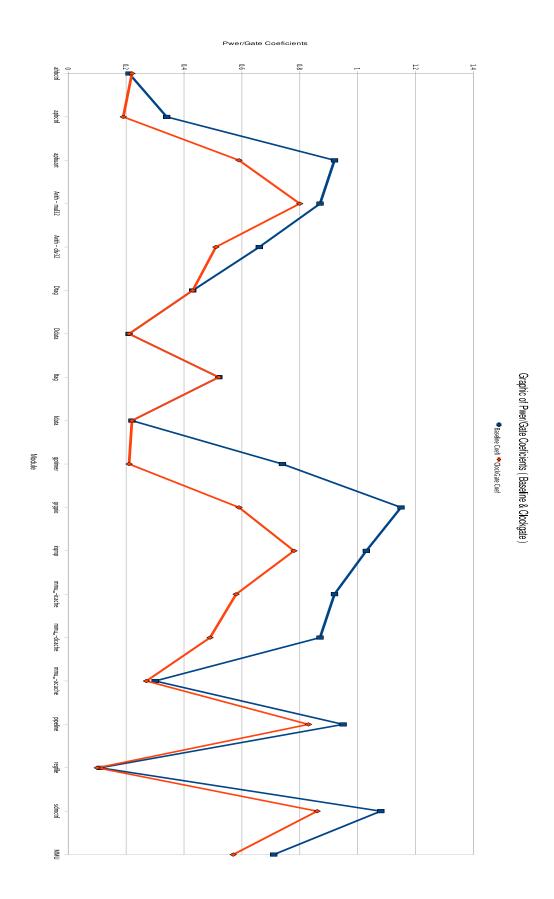

| 5.21 | Power/Gate Coefficient Variations (Clock Gating and Baseline Flow) 97 |

| 5.22 | Clock Gating Descloning                                               |

| 5.23 | (a) Incremental $V_{th}$ Synthesis (b) Mixed $V_{th}$ Synthesis       |

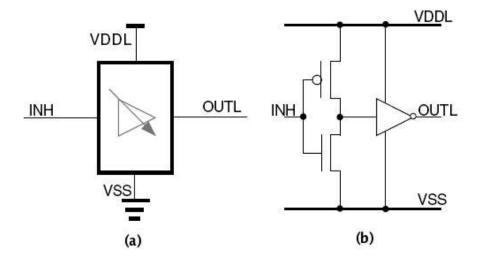

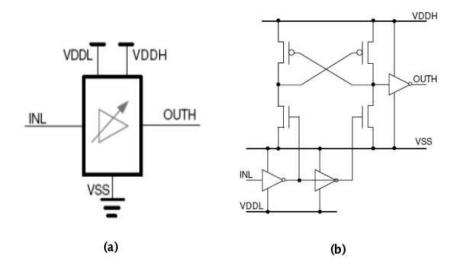

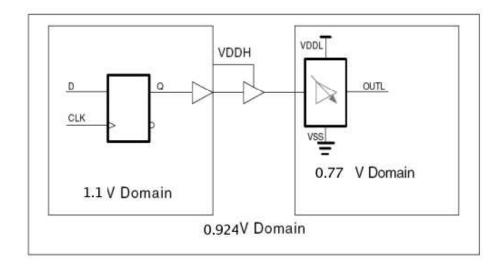

| 5.24 | High-to-Low Level Shifter                                             |

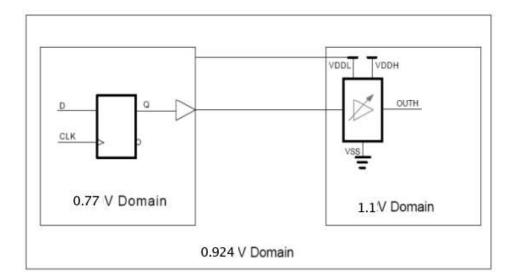

| 5.25 | Low-to-High Level Shifter                                             |

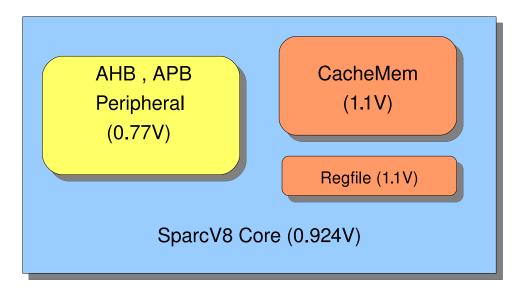

| 5.26 | Power Domain of Leon3 System                                          |

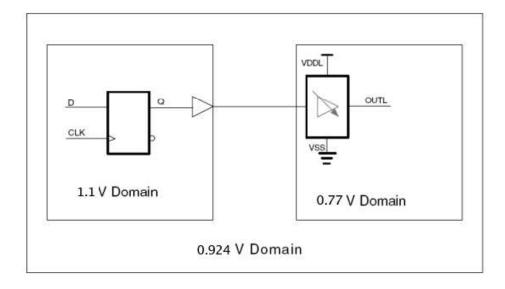

| 5.27 | High-to-Low Level Shifter in Destine Domain                           |

| 5.28 | Placement of Level Shifters during the Clock Tree Synthesis           |

| 5.29 | Level Shifter Placement                                               |

|      | Clock Tree of Multiple Power Domain                                   |

|      | Clock Tree Synthesis at Multiple Power Domain                         |

## Capítulo 1

## Introdução

A indústria de semicondutores sempre enfrentou fortes demandas em resolver problema de dissipação de calor e reduzir o consumo de energia em dispositivos. Esta tendência tem sido intensificada nos últimos anos com o movimento de sustentabilidade ambiental. Cada vez mais, a indústria semicondutora é obrigadas a aplicar técnicas de redução de energia no nível do circuito e do sistema.

A demanda por baixo consumo de energia é um aspecto bem relevante no domínio de dispositivos móveis. Apesar de tempo de operação ativa dos equipamentos m<sup>7</sup>oveis ainda é limitado pela capacidade das baterias, o número de vendas deste segmento chega em centenas de milhões de unidades anuais. Mais do que nunca, junto com a preocupação crescente sobre o uso de recursos naturais, o redução de consumo de energia é um aspecto crítico em quase todos os imagináveis mercados de usuários finais.

Outro tipo de aplicação que também exige baixo consumo de energia é o centro de dados formado por sistema de fazenda de servidores ('Server Farm System'). Estes sistemas são compostos pelos numerosos poderosos servidores, isolados numa sala que deve ser mantida sob uma temperatura razoável. Considerando que cada servidor consome entre 100 ~ 200 W de potência, a maior parte deste consumo transforma-se em calor, que exige grandes sistemas de ar condicionado na refrigeração. Cerca de um terço a metade de energia consumida por uma fazenda de servidores é usada para resfriar os equipamentos[20]. Na maioria dos centros de dados (85%), o sistema de refrigeração é responsável por 65% do consumo de energia e os equipamentos de TI <sup>1</sup> são responsáveis por apenas 33%. Os últimos 2% de consumo são perdidos nos sistemas de conversão de energia [20].

Os automóvéis também incorporam grande quantidade de produtos eletrônicos, que são capazes de suportar até centenas de unidades de micro controladores. Eles controlam a força de tração dos motores, detectam as falhas, controlam a frenagem, o painel

<sup>&</sup>lt;sup>1</sup>Tecnologia da Informação

de instrumentos, o sistema de navegação, o sistema de entretenimento e garantem a alimentação do sistema em situações críticas. Quanto menor fica o consumo de energia que estes sistemas requerem, menor será o consumo de energia desses veículos.

No mercado de PC, os laptops e notebooks podem ser vistos como um computador que não deve ficar muito longe das tomadas elétricas. Com apenas poucas horas de duração, a bateria serve principalmente como uma ponte quando os laptops são movidos de um ponto a outro. Neste caso, a redução de consumo de energia é uma necessidade natural.

As electrônicas de equipamentos médicos também exigem alta eficiência em gerenciar o consumo de energia para monitorar/manter saúde dos pacientes ao longo prazo (marca-passos artificiais, por exemplo).

Todos os exemplos citados acima monstram a importância de reduzir o consumo de energia. No entanto, a concepção correta de um sistema eletrônico de baixo consumo de energia é um problema de vários níveis de complexidade e exigem estratégias sistemáticas na sua construção. As perdas de energia podem acontecer no alto nível devido ao software de aplicação ou no baixo nível por causa de processos de manufatura de transistores que apresentam alta currente de fuga. Assim como muitos aspectos de um projeto eletrônico, o problema de otimização de consumo de energia depende fortemente da capacidade dos projetistas em selecionar e utilizar as técnicas de redução de energia em todos os níveis de projeto.

## 1.1 Roadmap de Tecnologia de Projeto de Semicondutores

De acordo com o ITRS 2009<sup>2</sup>, a atual tecnologia de projeto semicondutores enfrenta dois conjuntos de desafios oriundos de duas diferentes complexidades — a complexidade de silício e a complexidade do sistema [26]. A primeira complexidade se refere aos impactos causados pelo encolhimento de processo de manufatura dos transistores, junto com o uso de novos materiais na arquitetura de interconexão de sistema.

A segunda refere-se ao crescente número de transistores em uma única pastilha de silício e a demanda do consumidor por equipamentos de maiores funcionalidades, menores custos e menor tempo de lançamento ao mercado.

Várias outras complexidades acontecem em heterogeneidade dos componentes durante a integração do sistema de SoC<sup>3</sup>. Especialmente para este caso, a especificação e validação de conceito tornam-se desafiador. Para lidar com essas duas complexidades,

<sup>&</sup>lt;sup>2</sup>International Technology Roadmap for Semicondutores, versão 2009

<sup>&</sup>lt;sup>3</sup>System on Chip

a tecnologia de projeto deve fornecer novas metodologia para otimizar o custo de projeto e novas ferramentas para melhorar o reuso dos blocos de propriedade intelectual.

A outra tendência clara dada pelo ITRS-2009 é sobre os desafios no gerenciamento de consumo de energia. Como a redução de tamanho de transistores, a tecnologia de projeto é obrigada a enfrentar vários novos cenários:

- produtos baseados em UMP<sup>4</sup> exigem cada vez mais capacidades de armazenamento e desempenho, com severas restrições em consumos de energia (tanto em estado de operação como em estado de 'stand-by').

- O aumento de densidade de potência agrava os efeitos térmicos e impacta a confiabilidade e o desempenho de projeto. A diminuição das tensões de alimentação agrava severamente a corrente de fuga e os efeitos de ruído. Estas tendências desafiam desde os recursos de interconnexão nos chips, as máquinas ATE <sup>5</sup> até os teste de burn-in. Especialmente para os sistemas que são alimentados pela alta tensão ou manufaturados em processos avançados (90nm, 65nm, 45nm), os projetos tendem a trabalhar numa temperatura elevada e rapidamente apresentarão vários mecanismos de falha em silício.

- O consumo de energia estática provocado pelas correntes de vazamento varia exponencialmente com os parâmetros de manufatura de transistores (largura de portas, espessura do óxido e a tensão limiar). Como consequência disso, análises de desempenho e a otimização de potência tornam-se desafiador.

## 1.2 Motivação

De acordo com as mensagens dadas pelo ITRS-2009, vimos que o custo de projeto é um fator fundamental que afeta, e afetarão a indústria de semicondutores nas próximas décadas. Este momento, a indústria de EDA<sup>6</sup> ainda falta ferramentas ou soluções viáveis que sejam capazes de balacear as restrições orçamentárias (em termos de tempo ou de custo) com o fluxo de projeto.

No entanto, a partir de dados de vários trabalhos relevantes de projetos SoC<sup>7</sup>, vimos que a tecnologia de redução de consumo de energia foi melhorada significativamente devido aos esforços e colaborações entre a indústria EDA, as empresas semicondutoras e a comunidade acadêmica. No contexto do fluxo de projeto, as técnicas de redução

<sup>&</sup>lt;sup>4</sup>Unidade de Micro Processamento

<sup>&</sup>lt;sup>5</sup>Equipamentos de Testes Automáticos

<sup>&</sup>lt;sup>6</sup>Electronic Design Automation

<sup>&</sup>lt;sup>7</sup>System on Chip

de energia demonstram diferentes capacidades em reduzir o consumo em distintos níveis de abstração. Infelizmente, várias informações interessantes dos projetos são omitidas pelas empresas sob acordos de confidencialidade ou proteção industrial. Tais informações incluem: arquitetura de baixo consumo de energia , representação única de intenção de consumo de energia, esforço de implementação ('front-end' / 'back-end') e os impactos de desempenho de área.

A adoção de qualquer técnica de redução de energia sempre está vinculada com objetivos especiais e provoca alguns impactos no projeto. Normalmente, a equipe de projeto indiretamente admite todos as possíveis inconveniências derivadas das técnicas. Apesar dos projetistas conheçam bem os impactos de forma qualitativa, as detalhes quantitativas ainda são incognitas ou apenas mantidas dentro do 'know-how' das empresas.

Neste trabalho, de acordo com resultados experimentais baseado num verdadeiro plataforma SoC<sup>8</sup>, tentamos quantificar os impactos derivados do uso de técnicas de redução de consumo de energia. Nós concentramos em relacionar o fator de redução de energia de cada técnica aos impactos em termo de área, desempenho, esforço de implementação e verificação.

Na ausência desse tipo de dados, que relacionam o esforço de engenharia com as metas de consumo de energia, incertezas e atrasos serão frequentes no cronograma de projeto.

Esperamos que este tipo de orientações possam ajudar/guiar os arquitetos de projeto em selecionar as técnicas adequadas para reduzir o consumo de energia dentro do alcance de orçamento e cronograma de projeto.

### 1.3 Publicação

Uma versão reduzida do presente trabalho, incluindo desde o capítulo 2 até o capítulo 6, será submetida para o First Workshop on Circuits and System Designs (WCAS 2011) em João Pessoa, Paraíba, Brasil.

## 1.4 Organização de Dissertação

A dissertação será apresentada da seguinte forma:

- Capítulo 1: Introdução

- Capítulor 2: Low Power Fundamentals and Techniques descreve as fontes de dissipação de energia em transistores CMOS seguido de alguns conceitos fundamen-

<sup>&</sup>lt;sup>8</sup>System on Chip

tais de análise de potência nas ferramentas de EDA <sup>9</sup>. Depois disso, fundamentos de algumas técnicas de redução de consumo de energia são apresentados.

- Capítulo 3: **Related Works** descreve alguns projetos relevantes de redução de consumo de energia e seus resultados.

- Capítulo 4: Low Power Design Flow apresenta as diferenças entre o fluxo de projeto ASIC convencional e o fluxo de projeto de redução de consumo de energia.

- Capítulo 5: Case Study Results apresenta um estudo de caso baseado numa plataforma SoC (Leon3) quando as técnicas de redução de consumo de energia são aplicadas. Descrevemos também as vantagens e desvantagens das técnicas utilizadas.

- Capítulo 6: Conclusão e Trabalhos Futuros. Concluimos a dissertação e mostramos possíveis trabalhos futuros.

<sup>&</sup>lt;sup>9</sup>Electronic Design Automation

## Capítulo 2

# Low Power Fundamentals and Techniques

Before we developing the fundamentals of low power techniques, we briefly discuss some mechanism of power consumption and several power related effects in CMOS circuits.

## 2.1 Power dissipation in CMOS technology

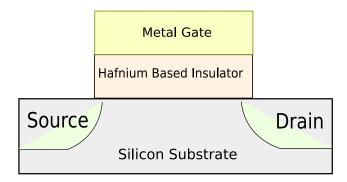

The traditional analysis approach considers a simple inverter as basic model to explain components of power consumptions. Just like in the Figure 2.1, the power dissipation happens when the inverter is in use and the total power can be decomposed into two classes: the static power and the dynamic power.

Roughly, the total power of an inverter gate can be described as the follower equation

$$P = P_{dynamic} + P_{static} (2.1.1)$$

and each one of these two components are described in the next two subsections. We also denote the dynamic power as  $P_{dynamic}$ , and the static as  $P_{static}$ .

### 2.1.1 Dynamic power dissipation

The dynamic power  $(P_{dynamic})$  is usually the dominant component<sup>1</sup> occurs only when the node voltage is switched. The model from Figure 2.1 is simplified as it assumes that all capacitance is connected at the output node. The output capacitance is divided into two components  $C_1$  and  $C_2$ . Assume first the input goes to **ground** (logic zero), then

$<sup>^{1}</sup>$ From 90 nm process forward, although, this picture suffers deep changes. Please consult section 2.1.2 for more details.

I switch : Charge/discharge current

$I_{internal}$ : Internal current  $I_{leakage}$ : Leakage current

Figura 2.1: Simplified Inverter Model

the  $C_1$  is connected to ground, and the  $C_2$  is to  $V_{dd}$  (note<sup>2</sup>). The charge of  $C_1$  changes from  $C_1V_{dd}$  to zero, as the NMOS transistor switches to GND. The charge of  $C_2$  changes from zero to  $C_2V_{dd}$  through  $V_{dd}$ . During the next phase, when the input voltage returns to low again,  $C_2$  is shorted through the PMOS transistor, and  $C_1$  is charged back to  $C_2V_{dd}$ . As a result, we take a charge of  $(C_1 + C_2)V_{dd}$  is taken from the power supply for a full switch cycle, or a total energy of  $(C_1 + C_2)V_{dd}^2$ . In a system whose frequency equals f Hz, we will get the power consumption value  $P = f(C_1 + C_2)V_{dd}^2$ . If we simplify the gate capacitance as  $C_{load} = C_1 + C_2$  using the miller effect, and introduce the switching probability for the input node as  $\alpha$ , we can express the dynamic power consumption of the CMOS inverter as:

$$P_{dynamic} = C_{load} V_{dd}^2 \alpha f (2.1.2)$$

Therefore, when a static CMOS gate is switched by an input signal with a nonzero rise or fall time, both NMOS and PMOS transistor will conduct simultaneously for a short period. During this interval, there will be a short-circuit current, flowing directly between  $V_{dd}$  and ground and not participating in charging or discharging of  $C_{load}$ . So, for the total component of the dynamic power, we should take into account the short-

$<sup>{}^{2}</sup>C_{1}$  and  $C_{2}$  are result from gate oxide capacitance( $C_{ox}$ ), gate junction capacitance( $C_{j}$ ) and the gate interconnect capacitance ( $C_{int}$ )

circuit effect. Hence the equation 2.1.2 should be corrected to:

$$P_{dynamic} = C_{load}V_{dd}^2\alpha f + P_{short}$$

(2.1.3)

where

$$P_{short} \approx V_{dd} I_{short} \frac{\tau_{in}}{4} 2f \approx V_{dd}^2 f \frac{C}{10}$$

(2.1.4)

The second term in equation 2.1.3 represents the short-circuit power. When the inverter's input is around  $\frac{V_{dd}}{2}$  during the turn-on and turn-off switching transients, both the PMOS and NMOS are on and a short circuit current  $I_{short}$  flows from  $V_{dd}$  to ground. The width of this short-circuit current pulse is about  $\frac{1}{4}$  of the input rise and fall time [17][23].

If we combine the equation 2.1.3 with Equation 2.1.4, we have:

$$P_{dynamic} = C_{load} V_{dd}^2 \alpha f k \tag{2.1.5}$$

Since the inverter is in the dynamic operation mode, the probability  $(\alpha)$  to have a short circuit in each switching transition is 100%. As the result, the dimensionless factor k becomes  $\alpha + 0.1 = 1.10$ , which can be lower bounded to 1 [17][23]. The dynamic power equation, therefore, can be expressed in a simplified form:

$$P_{dynamic} = C_{load} V_{dd}^2 \alpha f (2.1.6)$$

### 2.1.2 Static power dissipation

The static dissipation is the power consumed even a gate is not switching. When the transistors are nominally OFF, they leak small amount of current. Leakage effect include subthreshold conduction between the source and the drain, gate leakage from the gate terminal to the body, and junction leakage from source to body and drain to body. The subthreshold conduction is caused by thermal emission of carriers over the potential barrier set by the threshold voltage. The gate leakage is a quantum-mechanical effect caused by the tunneling through the thin gate dielectric. Junction leakage is caused by the current through the PN junction between the source/drain diffusion and the body terminal.

According to this description, the static power can be understood as the sum of the three types of dissipation and can be represented in the next equation [23]:

$$P_{static} = (I_{sub} + I_{gate} + I_{jun})V_{dd}$$

(2.1.7)

where the  $I_{sub}$  denotes the subthreshold leakage current, the  $I_{gate}$  denotes the gate leakage current and the  $I_{jun}$  denotes the junction leakage current. For each one of components, we present a brief description in next:

#### Subthreshold Leakage

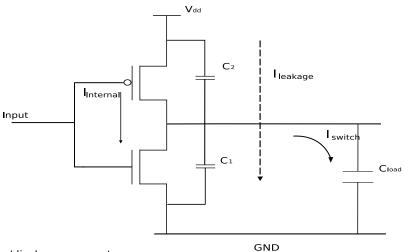

In an n-MOS transistor, the substrate is composed of p-type silicon, which has positively charged mobile holes as carriers, as show in Figure 2.2(a) and 2.2(b).

Figura 2.2: N-Type MOSFET in (a) Cut-Off Region (b) Linear Region

When a positive voltage is applied on the gate, an electrical field causes the holes to be repelled from the interface, creating a depletion region containing fixed negatively charged acceptor ions. A further increase in the gate voltage eventually causes electrons to appear at the interface, in what is called an inversion layer, or a channel (as show in Figure 2.2(b)).

The gate voltage at which the electron density at the interface is the same as the hole density in the neutral bulk material is called the threshold voltage. Practically speaking, the threshold voltage is the voltage at which there are sufficient electrons in the inversion layer to make a low resistance conducting path between the *MOSFET* source and drain.

If the gate voltage  $(V_{gs})$  is below the threshold voltage, as show in Figure 2.2(a), the transistor is turned-off (we say that the transistor is in the subthreshold region or weak-inversion region). Ideally no current should flow from the drain to the source of the transistor. However, there is a small current  $(I_{ds})$  that can be described by the next equation [23]:

$$I_{ds} = I_{off} \times 10^{\frac{V_{gs} + n(V_{ds} - V_{dd}) - k\gamma V_{sb}}{S}} \times (1 - e^{\frac{-V_{dS}}{v_T}})$$

(2.1.8)

where the  $I_{off}$  is the subthreshold current at  $V_{gs} = 0$  and  $V_{ds} = V_{dd}$ .  $V_{gs}$  is the voltage between the source and the gate terminal, while  $V_{ds}$  is the voltage between the drain and the source terminal.  $V_{sb}$  is the voltage between the source and the body terminal. The n is a process-dependent factor, affected by the depletion region characteristics and is typically ranging 1.3 - 1.7 for CMOS process. The  $v_T$  represents the thermal voltage and it equals to 26mV at the room temperature. The S represents the subthreshold slope, and indicates how much the gate voltage must drop to decrease the leakage current by an order of magnitude. A typical value for this is 100 mV/decade at the room temperature [23].

#### Gate Leakage

According to the quantum mechanics, the electron cloud surrounding an atom has a probabilistic spatial distribution. For gate oxide thinner than 15 - 20 Å, there is a nonzero probability that an electron in the gate will find itself on the wrong side of the oxide where it will get whisked away through the channel[23]. This effect of carriers crossing a thin barrier is called tunneling and results in leakage current through the gate.

Two physical mechanism for gate tunneling are called Fowler-Nordheim (FN) tunneling and direct tunneling. FN tunneling is most important at high voltage. Direct tunneling is most important at low voltage with thin oxide and is the dominant leakage component. The direct tunneling can be describes as [1]

$$I_{gate} = WA \times \left(\frac{V_{DD}}{t_{cor}}\right)^2 \times e^{-B\frac{t_{ox}}{V_{DD}}}$$

(2.1.9)

where the W represents the width of the gate,  $t_{ox}$  is the unit area of the gate oxide, while the A and B are experimental constant, depend on the manufacturing technology.

#### Junction Leakage

The PN junction between diffusion and the substrate or the well form diodes. The substrate and well are tied to GND or VDD to ensure these diodes do not become forward biased in normal operation. However, the reverse-biased diodes still conduct a small amount of current  $I_D$ , that can be described as:

$$I_D = I_S \times (e^{\frac{V_D}{v_T}} - 1) \tag{2.1.10}$$

where the  $I_D$  and  $I_S$  stand respectively for the diode current and diode reverse-biased saturation currents. The terms D and S are not related with the drain or source. The  $I_S$  depends on doping levels and on the area and perimeter of the diffusion region and  $V_D$  is the diode voltage. Normally this type of dissipation ranges from 0.1-0.01  $fA/\mu m^2$ , almost negligible compared with the other two mechanism of leakage[23].

In process with feature size above the 180nm, leakage was typically insignificant except in very low power applications. In 90nm and 65nm process, threshold voltage has reduced to the point that the subthreshold leakage reaches level of 1 - 10s of nA per transistor, which is significant when multiplied by million or billion transistors on a chip. In 45nm, the oxide thickness reduces to the point that the gate leakage becomes comparable to subthreshold leakage unless the HKMG dielectric are employed[23]. Overall, leakage has become an important design considerations in nanometer process.

#### High K Metal Gate (HKMG)

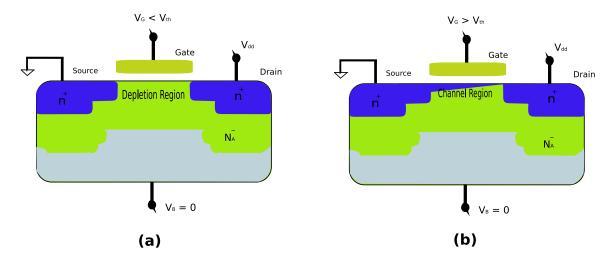

The HKMG is a new manufacturing approach<sup>3</sup> emerges to overcome the subthreshold leakage problem[6]. A different material for oxide isolation layer is chosen to design the dielectric layer. Different from the conventional CMOS isolation material (silicon dioxide based), the HKMG technology replace the isolation layer by a hafnium-based one, which presents a high dielectric constant k[8].

Silicon dioxide has been used as a gate oxide material for decades. As transistors have decreased in size, the thickness of the silicon dioxide gate dielectric has steadily decreased to increase the gate capacitance and thereby drive current and device performance. As the thickness scales below 2 nm, leakage current due to tunneling effect was increased drastically, which lead to larger power consumption and reduced device reliability. Replacing the silicon dioxide gate dielectric with a high-k material allows increased gate capacitance without the correspondent leakage effects[8].

The principle of high-K technology is based on modification of gate oxide capacitance of a MOSFET gate. Typically the insulator layer can be modeled as a parallel plate capacitor, just like Figure 2.3.

Figura 2.3: (a) High K Metal Gate (b) Oxide layer modeled as capacitor

If we ignore quantum mechanical and depletion effects from the silicon substrate and

<sup>&</sup>lt;sup>3</sup>Specially, begins with 45nm process

gate, the capacitance C of this parallel plate capacitor can be described by

$$C = \frac{K \times \varepsilon_0 \times A}{t} \tag{2.1.11}$$

where:

A: capacitor area

K: relative dielectric constant of the material (3.9 for silicon dioxide)

$\varepsilon_0$ : permittivity of free space

t: thickness of the capacitor oxide insulator

Since leakage limitation constrains further reduction of t, an alternative method to increase the gate capacitance is to modify the k by replacing silicon dioxide with a high-k material. In such a scenario, a thicker gate layer might be used which can reduce the leakage current flowing through the structure as well as improving the gate dielectric reliability. Based on this principle, semiconductor foundries now shrink gate equivalent oxide thickness at 32 nm from  $18\text{\AA}$  to just  $10\text{\AA}$  (1 nm) and, at the same time, gate leakage is reduced by 10 times[8]. From several IDM's<sup>4</sup> process specification manual, the usage of HKMG roughly offers a 40% reduction in power, and 20% increase in performance with  $V_{dd}$  at 1V[8].

The implementation of high-k gate dielectric is one of several strategies developed to allow further miniaturization of microelectronic components, colloquially referred to as extending Moore's Law.

#### 2.1.3 Power-Related Effects

As the technology node reduced, some power-related effects impact deeply on the design reliability. Next, we list same of them:

#### IR-Drop

This is a voltage reduction occured on the supply network  $(V_{dd})$  or ground (GND) of integrated circuits. The IR term comes from the Ohm's law, which states that current I flows through an effective resistance R, therefore, introduces a voltage drop as given by the equation V = IR.

Usually, designers assume the availability of an ideal power supply that can instantly deliver any amount of current to maintain the specific voltage throughout the chip. However, the combination of increasing current per-unit of area on the die and narrower metal line widths<sup>5</sup> causes localized voltage drops within the power grid, leading to decreases power supply voltage at transistors. These localized drops in the power

<sup>&</sup>lt;sup>4</sup>IDM stand for Integrated Device Manufacturer

<sup>&</sup>lt;sup>5</sup>which causes an increase in the power-grid resistance

supply voltage decrease the operating voltage of the chip, potentially causing timing and functional failures.

#### IR-Drop of Ground

This is a voltage increase that occurs on the ground network (GND). All the current that is sourced to the network combined with a finite resistance of the network leads to localized increase on the ground voltages around the chips. This increase in the ground voltage also decrease the operating voltage of the chip, resulting in the timing and functional failures.

The number of failures from poor power-grid network has become significant only recently, many designers still do not look at power distribution as a potential source of chip failures. Symptoms of IR-drop of VDD and GND could include the following:

- 1. Non-Functional chips: the total chip malfunction happens when the global IR drop of *VDD* or *GND* exceed the safe operation range. The failure resembles a logical functional failure or a manufacturing problem, although functional simulation indicates that the design is logically correct.

- 2. Intermittent or Data-dependent functional failures: this situation happens when we face with a great number of cells in close proximity switching simultaneously and causing local IR drop of *VDD* or *GND*. A higher power-grid resistance on that specific region of the chip can also provoke the same effect. In normal operation, this kind of "sensitization" might not occur, except when a specific data input activates the problem. As result, this effect appears on that part of chip.

- 3. Intermittent or Data-dependent timing failures: Just like the intermittent functional failure, some specific data inputs can cause IR drop of *VDD* or *GND* and induce a timing failure problem by changing the interconnection resistance or capacitance characteristics. In most cases, the whole chip speed will be slowed down, appearing to be *setup* or *hold* timing violations.

- 4. Timing library problem: traditionally, the timing library of a process are modeled by assuming certain region of supply IR drop in the design. This approach adds significant timing margins and makes performance estimation highly unpredictable. Chips can fail because the IR drop was actually higher, or they can operate much faster than the simulation results.

- 5. Over-designed power grid: too prevent possible IR drop effects, supply structure and interconnection routing are heavily designed and consume a significant area of chip.

#### Electromigration

It is used as a general term to describe failure mechanisms in the metal wires of a chip caused by the move of metal atoms in a wire because of high current stress. In such case, electrons collide with diffusion metal atoms and impel the atoms in the direction of electron flow. This collision produces a mass flux opposite to that of the current, and the divergence in this mass flux can result in damage to the conductor in form of void or killocks. Over a long period of time, the metal atom may move in the direction of the electron flow, causing two principal failure mechanism:

1. If enough atoms are moved, the wire effectively breaks and becomes an open circuit (Figure 2.4). In the long term, the interconnecting wires will breakdown, and in some specific cases, the design shows failure symptons at the post-manufacturing test stage.

Figura 2.4: Long term impact of electromigration effect

2. If enough atoms move to the same location, a short to an adjacent metal wire can be create. This phenomenon is commonly known as fusion.

Therefore, the electromigration is a long-term we arout mechanism of the chip interconnect wires. Its typical failure symptoms are primarily a change in either the timing or the functionality of a chip over time. In some case, the wires that provide unique connectivity in the circuit will cause a total function failure. Wires that are inherently redundant, such as a meshed power grid, exhibit symptoms of higher IR drop of VDD or GND after the failures damage the power grid section. In the case of shorts connections between wires on the chip, total functional failure occurs. Due to this, starting from the 130nm process, the power rail analysis methodologies have been wildly incorporated into the physical verification in order to validate the power network before the tape-out. Rails analysis should accurately highlight the IR-drop of VDD or GND and the electromigration problems, which could be caused by open circuits, missing vias/via arrays, high current densities, lack of power stripes and narrow widths of power routing. This technique is also suitable to identify long period reliability problems of chips under the influence of electromigration effects.

## 2.2 Power Analysis Model and Estimation Method

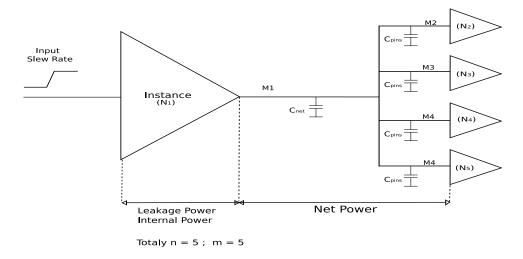

The preview sections (2.1.1 and 2.1.2) described the CMOS power dissipation sources of the semiconductor manufacturing process. In this section, we describe some fundamental concepts of power analysis modeling and estimation. The classical power estimation tools subdivided power consumption into three components: the internal power, the leakage power and the net power. Figure 2.5 shows a simplified power estimation model.

Figura 2.5: EDA tools power estimation model

Usually the power estimator returns an average power consumption as opposed to cycle-by-cycle power consumption. The classical estimators need switching information (input/output switching probability and pin/net toggle rates) to calculate the power. The follow equation shows how a generic power engine calculates the power dissipation:

$$P_{total} = \sum_{1}^{n} P_{instance} + \sum_{1}^{m} P_{net}$$

(2.2.1)

where,

$$\sum_{1}^{n} P_{instance} = \sum_{1}^{n} P_{leakage} + \sum_{1}^{n} P_{internal}$$

(2.2.2)

and

$$\sum_{1}^{m} P_{net} = \sum_{1}^{m} \frac{1}{2} \times C_{load} \times V_{dd}^{2} \times ToggleRate$$

(2.2.3)

We note that,

- $P_{leakage}$  is the leakage power in a cell, which is obtained from the technology library. Recent power analysis tools usually support both constant and state-dependent leakage power models.

- $P_{internal}$  is the internal power of the cell, which is obtained and calculated from the technology library.

- n is the number of cells in the design.

- $P_{net}$  is the net power consumption in the design (see section 2.2.3).

- m is the number of nets in the design.

In the next three sections some basic concepts related to each one of the above components will be explained.

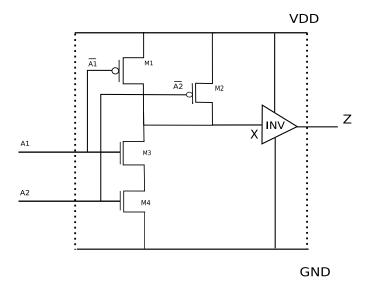

## 2.2.1 Internal Power Analysis

The internal power dissipation of a cell includes short circuit power and the switching power when charging or discharging the internal net capacitance. The values of the internal power could be calculated from the power look-up tables in the library. These tables are a function of the input slew rate (SR) and the output load capacitance  $C_{load}$ . Some libraries also have three-dimensional power tables which are function of the input slew, output load capacitance and a second output load capacitance.

Instead of one table, a cell can contain two tables to model the internal power at more advanced process technology: one table to rise transitions and another to fall transitions. Taking into account the path dependence, the internal cell power is determined as follow way:

$$P_{internal} = \sum_{per\ arc} (TR_{arc_{ij}} \times \Phi(S_i, C_j)) + \sum_{per\ pin} (TR_i \times \Phi(S_i))$$

(2.2.4)

Now, considering the Figure 2.6 as a simplified model for internal power estimation, we can analysis the equation 2.2.4:

Figura 2.6: Internal Power Model (2 Input AND)

- TR is the effective toggle rate of an arc or a pin. The effective toggle rate of  $arc_{ij}$  depends on the probability that the arc gets activated and on the toggle rate on the input  $pin_i$ . The probability that the arc gets activated is determined by the function of output  $pin_j$  and the probabilities of the other inputs pins. In our case, the  $arc_{ij}$  could the path from A1 to Z or A2 to Z. A1, in our case, represents the  $pin_1$ , and the A2 represents the  $pin_2$ .

- $\bullet$   $\Phi$  is the power calculated from a look-up table in the process technology file.

- $S_i$  is the slew rate of the  $input_i$  causing a toggle rate on  $output_j$ . In our case, the slew rates of input pins can be represented by  $S_1(A1)$  and  $S_2(A2)$ , causing toggle rate on Z ( $output_1$ ).

- $C_j$  is the load capacitance of  $output_j$ . In our case, it can be presented by  $C_1$ , which is the load capacitance at Z ( $output_1$ ).

- The total internal power of this gate, then, can be described as:

$$P_{internal} = Arc_{A1->Z} + Arc_{A2->Z} + Pin_{A1} + Pin_{A2}$$

(2.2.5)

where

$$Arc_{A1->Z} = TR_{A1->Z} \times \Phi(SlewRate_{A1}, C_{output_Z})$$

$Arc_{A2->Z} = TR_{A2->Z} \times \Phi(SlewRate_{A2}, C_{output_Z})$

$Pin_{A1} = TR_{A1} \times \Phi(S_{A1})$

$Pin_{A2} = TR_{A2} \times \Phi(S_{A2})$

### 2.2.2 Leakage Power Analysis

The leakage power dissipation component should be obtained from the technology library of the chosen manufacturing process (more specifically, from the logical synthesis libraries). In some technology, library vendors provide cells with different threshold voltages, enabling the possibility to perform some leakage power optimization techniques. For old process, it was usually modeled as a constant value, and in more advanced nodes, some cell leakage power is a function of the input state. making the leakage estimation more accurate. In this case, the leakage power for the specific cell is determined as follow equation:

$$P_{leakage} = \sum_{state=1}^{k} (P_{state\_leakage} \times Probability_{state})$$

(2.2.6)

where,

- K is the number of total possible states of the cell.

- $P_{state\_leakage}$  is the leakage of the cell in a specific state(logic Zero or One).

- $Probability_{state}$  is the probability that the cell stays in the actual state.

## 2.2.3 Net Power Analysis

The net power includes dissipation during net/pin capacitance charging and discharging process. The total power consumed by a determined net can be expressed as .

$$P_{net} = \frac{1}{2} \times C_{load} \times V_{dd}^2 \times TR \tag{2.2.7}$$

where,

$\bullet$   $C_{load}$  is the sum of parasitic capacitance from a net and it associated pins.

- $V_{dd}$  is the supply voltage, expressed usually in volts

- TR is the toggle rate associated with the net switching activity.

### 2.2.4 Power Estimation Methods

After introduced power analysis models from the preview sections, we present some power estimation methods. The two most common approaches for the power estimation are the vector-based and the propagation-based techniques. We describe both of them in following sections:

### **Vector-based Estimation**

The vector-driven method uses switching activity files (output of a discrete event simulator) to obtain the number of transitions associated to each net and I/O pin. Normally, the switching activity files are dumped in VCD<sup>6</sup>, SAIF<sup>7</sup> or TCF<sup>8</sup> formats. These files result from a good functional coverage simulation, and provide more accurate result when estimate power.

The power engine calculates the transition probability of each pin/net based on the activity information. After this step, the duty cycle of each net (which is responsible for state dependent internal/leakage power calculation) is also estimated. Finally, the power estimation is performed by the engine based on the previews sections (2.2.1, 2.2.2 and 2.2.3).

The most complicated step of estimation approach happens when one tries to produce a reliable input vector with good functional and power coverage. The vector-based approach is apply in the follow conditions:

- Gate-level simulation is possible at the full-chip level.

- Gate-level simulation provides sufficient functional coverage for the design.

- The switching activity vector include information that could cause highest power consumption.

$<sup>^6</sup>$ Value Change file format, was defined along with the Verilog HDL by the IEEE Standard 1364-1995 in 1995

<sup>&</sup>lt;sup>7</sup>Switching Activity Interchange Format

<sup>&</sup>lt;sup>8</sup>Toggle Count Format, from Cadence Design System TM

### Propagation-based Estimation

The propagation-based approach is vector-independent and provides coverage for all nets in a design. However, the accuracy depends on a good starting value, i.e, an initial information about the switching probabilities at the primary inputs of the design. Simple examples are clock, reset or enable inputs. To obtain an accurate prediction without information about the switching probabilities of these inputs is difficult and frequently results in inaccurate prediction and overestimated power consumption. We can divide the propagation method into several categories:

- Propagation through combinational cells: this is based on the library functions of each manufacturing process. The power engine get the previously defined combinational cell from the technology file and uses these functions to propagate the switching information through the synthesized netlist. The engine propagates duty cycle through combinational cell, at the same time, breaks combinational loops to estimate a precise result. The method is based upon internal heuristic of each power engine and activity information from other neighboring pins.

- Propagation through sequential cells: this is based on the activity of the pins like: inputs, set, reset or scan enable. However, most of these cells are in a sequential loop, like the state machine whose activity propagation mechanism is based on heuristic algorithms. A big drawback of the method is imprecise when the sequential cells from a loop structure, and the heuristic dimish the switching activity toward Zero.

- Propagation through macro cells<sup>9</sup>: the major component of power in macro cells is the internal power which is highly sensitive to the activity on reads and writes signals. A small change in activity on these two signals can cause a large change in the internal power numbers. Basically, the power estimation is based on process library as the case of combinational cells.

In general, this method is very useful in the early stages of the design, due to simplicity and speed. As long as the project approximates the sign-off step, the vector-based approach is highly recommended instead.

<sup>&</sup>lt;sup>9</sup>these ones can be a memory cell or a third-party IP

# 2.3 Low Power Techniques Fundamentals

After a brief description about CMOS power dissipation and estimation methods, now we will present several power reduction techniques used in this work, including their advantages and drawbacks.

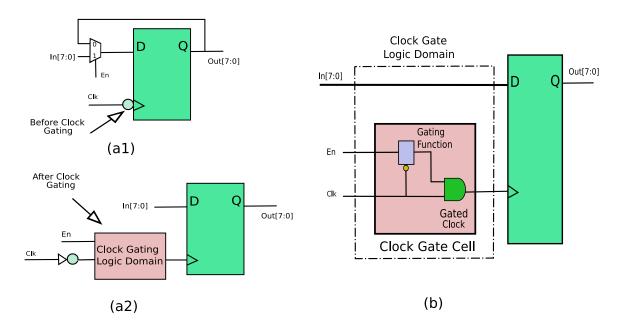

## 2.3.1 Clock Gating

The clock gating is a classical and powerful technique in optimizing dynamic dissipation. It is based on eliminating unnecessary clock toggle activities in the storage elements[5].

Any storage element<sup>10</sup> in the digital design is based on flip-flops. By analyzing the basic functionality of any flip-flop, we find that even though data is loaded into the design with very low frequency, the clock signal keeps the toggle behavior at every clock cycle.

Very often, the clock signal also drives a large capacitive load which makes clock signal a major source of dynamic dissipation. By inserting a special control signal (associated with a special gating logic) to control a group of flip-flops, one can eliminate unnecessary clock toggles and reduce the dynamic power effectively. We show the clock gating concept and implementation in Figure 2.7

Figura 2.7: Clock Gating concept

<sup>&</sup>lt;sup>10</sup>For example, registers, static rams, dynamic rams

Clock Gating can be implemented by inserting clock gating circuits into a sequential cell (Figure 2.7(a1)), alterating the enable signal to gate the clock pin of the flip-flop just like the 2.7(a2). As a result, the dynamic power dissipation could be reduced:

- The dynamic power is not dissipated during the idle period when the sequential circuit is turned-off by the gating function (see in Figure 2.7(b)).

- Dynamic power is saved if the enable signal is down. From the Figure 2.7(b), with the enable signal set to be in down state, the switching activity in clock gating cell is reduced to zero, remaining the leakage dissipation.

- With replacement of an enable circuit in the original design (Figure 2.7(a1)), the power dissipation at the input pin is reduced to net power, which is much lower than when the circuit was enabled.

### Possible Impacts, Requirements and Constraints

We understand how the clock gating could be used in reducing dynamic dissipation, it also brings some drawbacks and requirements to the implementation and DFT<sup>11</sup> structure. The impacts can happen in follower topics like: power, area, DFT, timing, PDK<sup>12</sup>, verification effort and back-end implementation.

#### Power Reduction

The clock gating features moderate dynamic power reduction and is a well-known technique to optimize clock network dissipation. However, it shows almost zero effect on leakage power. Since it just controls the switching activity of sequential cells, and cannot reduce the current leakage phenomenonae on gates which is basically process and temperature dependent. According to studies [10], the clock signal in digital design is responsible for 15%-45% of total consumptions. By applicating this technique, with the construction of activity pattern based clock tree, the total power can be reduced around 15%-20% [5].

### Timing and Functional Verification

The timing is not critical in a clock gating design, since the additional logic does not introduce significant delay. No extra effort is demanded on functional verification, since the clock gating insertion algorithm does not modify the logical functionality and

<sup>&</sup>lt;sup>11</sup>Design For Test

<sup>&</sup>lt;sup>12</sup>Process Design Kit

must be timing driven. Equivalence checking tools should be applied to warranty that the logical equivalence between the clock gating netlist and the  $RTL^{13}$  design.

### **Back-end Implementation**

Although the power aware placement and routing algorithm are well explored and studied by the EDA industry, most of the back-end implementation tools present wirelength overhead problem and cell overlaps after clock gating insertion. The correct (not necessary optimal) placement and routing algorithm for this technique must feature clock gating aware clock tree construction, non-overlap insertion and zero skew clock routing to further reduce power and clock skew [20]. Since the sequential logic's activity pattern plays an important role in a gated clock tree construction, several EDA tools propose technique for register clustering based on activity and transition patterns to optimize the clock network before the final placement and routing stage.

#### Area

Because several enable signal (more precisely, muxes) can be replaced with one clock-gate cell, so, this technique can result in area reduction. Therefore, a bad strategy of clock gating insertion (sometimes, after the placement stage) could increase the area and provokes routing congestion and wirelength overhead problem. In general, this technique does not show an expressive impact in final silicon area.

### Process Design Kit

The clock gating technique requires the integrated clock gating cells. Sometimes, the logical synthesizer must support the insertion algorithm, and in such case, standard cells are used to build customized clock gating logic. It is worth to remember that the clock gating aware DFT cells must be part of PDK to enable the circuit testability structure.

### Applicability in Macrocells

It is not possible to apply clock gating technique in reducing macroblock's power consumption. If the dominant power consumption of the design derives from macrocells, this technique will not show any significant result.

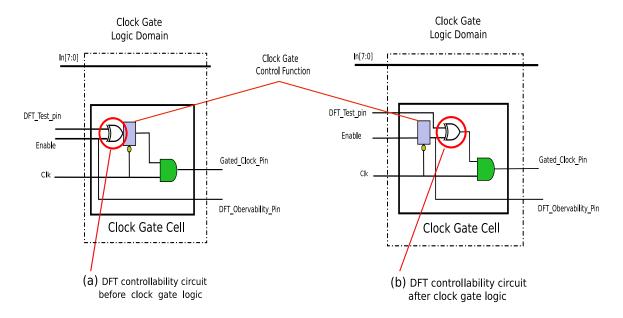

### Design For Test

The design team must pay a special attention on the DFT control logic while choosing the clock-gating style. The reliability of observability logic must be warrantied after the insertion of clock gating. As we know, any kind of DFT techniques require

<sup>&</sup>lt;sup>13</sup>Register Transfer Level

injection of a well known stimulus into DUT's<sup>14</sup> inputs. These stimulus can be applied by a simulator, an  $ATE^{15}$  machine or another DFT logic.

We refer the ability of one circuit to apply stimulis to DUT as *controllability*, while, the ability to evaluate the output response is called *observability*. Depending on the chosen circuit, the gated clock net can no longer be controlled by the DFT circuit and consequently, reducing the fault coverage rate of circuit. The worst of all, the clock gating control logic (drived by the enable signal) could no longer be observable.

Figura 2.8: Clock Gating cell with DFT feature

A common approach to correct this potential problem is to increment the controllability and observability logic with clock gating cells, just like in Figure 2.8.

With this extra logic inside the clock gating cells (in style 2.8(a) or in style 2.8(b)), the DFT tools can generate coverage vector and perform the fault coverage simulation of the clock gating circuit. Once the design is sampled out from the foundry, the ATE machines are able to detect manufacturing faults according to the clock gating aware test vectors.

## 2.3.2 Operand Isolation

Although the clock gating is very effective in reducing the dynamic power dissipation of a digital circuit, it can only save power on sequential elements and clock circuit.

<sup>&</sup>lt;sup>14</sup>Design Under Test

<sup>&</sup>lt;sup>15</sup>Automated Test Equipment

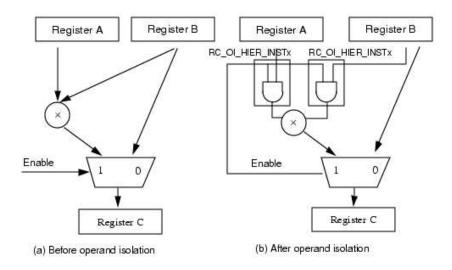

Whenever a module performs an operation whose result is not used by the downstream circuit (i.e combinational circuit), power is being consumed for an otherwise redundant computation. **Operand Isolation** is a dynamic power optimization technique to reduce power dissipation of datapath blocks by selectively blocking the propagation of the switching activity through the circuit[19][9]. We can show this technique by the example of Figure 2.9

Figura 2.9: Operand Isolation Concept

The idea of operand isolation is to identify redundant operations and, using special isolation circuitry, prevent switching activity from propagating into a module whenever it is about to perform a redundant operation. Therefore, the transition activity of the internal nodes of the module and, to a certain extent, its transitive fanout is reduced significantly, resulting in lower power consumption[19].

From the design of Figure 2.9(a), register C uses the results of the multiplier when the Enable signal is activated. When Enable is turned down, register C uses the results from the register B, but the multiplier continues its computation. Because the multiplier dissipates most of the power, the total amount of power wasted during idle is quite significant. The **Clock Gating** cannot be uses in this case, because the output of register B is always used by the multiplier.

**Operand Isolation** is a suitable solution in this case. It can shut-off (isolate) the functional unit (operand) when the results of the multiplier are not necessary. Figure 2.9(b), this technique inserts AND gate at the inputs of the multiplier and uses a extra enable logic to control the signal transitions. As a result, no dynamic power is dissipated when the result of the multiplier is not needed.

This is a pretty mature and automated technique in digital design. Normally,

after the lexical and syntactical analysis of input RTL design are performed, the logic synthesizer engine can identify some possible redundant computation blocks (such as adders and multipliers) and insert isolation logic.

### Possible Impacts, Requirements and Constrains

**Operand Isolation** brings some overhead and requirements in the implementation flow and silicon area. We continue our discussion according in follower topics: power, area, DFT, timing, PDK<sup>16</sup>, logic synthesis, verification effort and back-end implementation.

#### Power reduction

According to the recent research results[19], the operand isolation can reduce up to 30% of power consumption in designs which presents intensive control signal and redundant computation logic. For those cases which present intensive operation of state machines or sequential logic, this technique cannot achieve expressive results.

### Timing and Functional Verification Effort

There is major issues on timing and functional verification when using operand isolation circuits. The extra circuit does not add significant delays, after the insertion of isolation cells, the netlist can be verified by co-simulation and equivalence tools.

### Logic Synthesis

The logic synthesizer must feature operand isolation algorithm to detect redundant logic and automatize the isolation circuit insertion. In the early day of this technique, the isolation cells only were manually inserted after a long analysis by RTL designers, this procedure is error prone and extremely time consuming.

#### Area

According to several theorical and industrial results[9, 19], the operand isolation can slightly increase the final silicon area by adding several extra isolation cells. This penalty is worth if the power reduction is expressive. Normally this technique is suitable for the multimedia designs, which have massive redundant logic in the combinational logic and the memory cells are dominant factor in the final silicon area.

### Process Design Kit

Operand Isolation algorithm modify just the RTL design and inserting the isolation circuits during logic synthesis. No special requirements are required for the

<sup>&</sup>lt;sup>16</sup>Process Design Kit

PDK cells.

### Applicability in Macrocells

As the case of Clock Gating, the Operand Isolation cannot show any advantaged in optimizing macrocells' power consumption, since they are pre-designed with fixed architecture and power consumption.

### Design For Test

The post-manufacturing test structure can be easily implemented after the insertion of isolation logic, since the testability circuit just add observability and controllability circuits around the sequential cells whose logic functionality were not changed by the isolation algorithm.

### 2.3.3 Multiple Threshold Voltage

As described in the section 2.1.2, the leakage power is the power dissipated by the current leak in the transistor (subthreshold leakage, gate leakage, junction leakage). Leakage power is usually modeled in the library and characterized for several operation conditions (different temperature and supply voltages).

In the most advanced nodes <sup>17</sup> library specifies cell leakage power as a function of the input state which improve accuracy. In these cases, the leakage power is a function of pin switching activity.

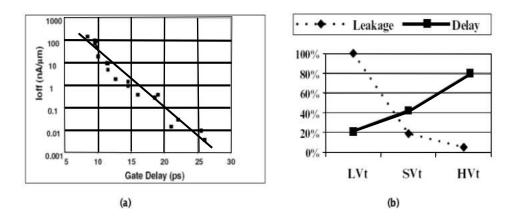

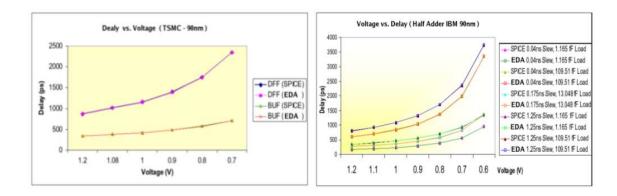

EDA<sup>18</sup> vendors have already automated the multiple  $V_{th}$  optimizaiion. One of big concerns in earlier days was about the timing impact associated with this approach. From Figure 2.10(a), we see the relationship between delay and leakage for a generic 90nm process.

From Figure 2.10(b), we can see some representative curves for leakage vs. delay for a multiple  $V_{th}$  library.

As explained earlier, subthreshold leakage depends exponentially on threshold voltage  $(V_{th})$ . While, the timing delays has a much weaker dependence on threshold voltage[23]. Many libraries vendors or process manufacture offer two or three versions of cells (low  $V_{th}$  cells, standard  $V_{th}$  cells and high  $V_{th}$  cells) which provide opportunities to make trade-offs between the leakage power and the performance during the physical design.

Since the leakage power is specified by the library as the function of input states, the switching activities of design becomes important for an accurate leakage power

<sup>&</sup>lt;sup>17</sup>specially at 90nm and below

<sup>&</sup>lt;sup>18</sup>Electronic Design Automation

Figura 2.10: (a) Current leakage x Timing Delay (b) Library, Leakage and Delay Graph optimization during the logical synthesis and the power optimization.

### Possible Impacts, Requirements and Constraints

Multiple  $V_{th}$  technique cannot reduce dynamic power, since the modifications in threshold voltage just reduces the current leak in subthreshold regions. The total power consumption is substantially reduced just when the design remains in standby mode. When multiple threshold voltage libraries are used, a larger leakage power savings result, but the performance degradation and area impact must be very carefully analyzed. The key point of this technique is how the design team will identify the most leak regions and critical path to achieve a good trade-off between the power and timing constraints.

## 2.3.4 Multiple Supply Voltage

Multiple supply voltage optimization is one of most aggressive power saving techniques. In today's industrial environment, several supply voltages are present in the design. In spite of this approach have received great attention of design teams, it comes with several drawbacks and impacts in the physical designs and the verification process.

From the CMOS power dissipation of section 2.1.1, the dynamic power consumption is proportional to factor the  $V_{dd}^2$ . Lowering  $V_{dd}$  value on some blocks help in reducing power significantly. Unfortunately, increases the propagation delay of the gates in the design.

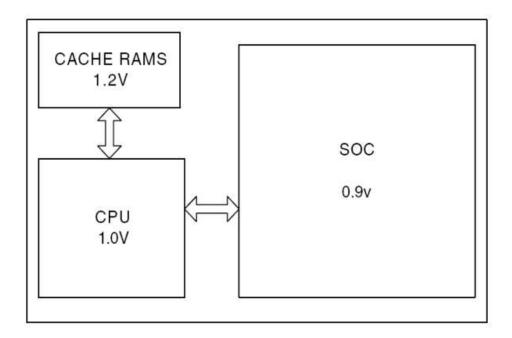

In order to detail the multiple Vdd approach in SoC platform, we consider a simple example in Figure 2.11.

This simple example contains 1 CPU unit (1.0V domain), 1 cache RAM memory (1.2V) and the entire peripheral hardware (BUS, I/O ports, external memory controller,

Figura 2.11: Multiple  $V_{dd}$  Example

timers) was supplied by 0.9V voltage domain.

The cache  $RAMs^{19}$  are supplied with highest voltage because they are on the critical timing path. The  $CPU^{20}$  is run at a second voltage level as it determines system performance, but can be run at slightly lower voltage than the cache and still have the overall CPU subsystem performance determined by the cache speed. The rest of the SoC can run at a lower voltage without impacting the overall system performance. Mixing blocks at different VDD supplies adds some complexity to the design, and not only need to add I/O pins to supply the different power rails, but also need a more complex power grid and level shifters on signals running between blocks.

By extending the idea of several supply levels, a more complex power strategies can be implemented. We can provide different voltages to our processor, for example, depending on its workload, or we can provide different voltages to a RAM - a low voltage to maintain memory contents when the memory is not being accessed, and a higher voltage to supports reads and writes. Several multiple voltage strategies can organized according to the following list:

• Static Voltage Scaling (SVS): different blocks or subsystems are given different, fixed supply voltages.

<sup>&</sup>lt;sup>19</sup>Ramdom access memory

<sup>&</sup>lt;sup>20</sup>Central processing unit

- Multi-level Voltage Scaling (MVS): an extension of the static voltage scaling case where a block or subsystem is switched between two or more voltage levels. Only a few, fixed, discrete levels are supported for different operating modes.

- Dynamic Voltage and Frequency Scaling (DVFS): an extension of MVS where a larger number of voltage levels are dynamically switched to follow changing workloads.

- Adaptive Voltage Scaling (AVS): an extension of DVFS where a control loop is used to adjust the voltage.

### Possible Impacts, Requirements and Constraints