### Técnicas e Arquitetura para Captura de Traços e Execução Especulativa

Este exemplar corresponde à redação final da Tese devidamente corrigida e defendida por João Paulo Porto e aprovada pela Banca Examinadora.

Campinas, 15 Fevereiro de 2011.

Prof. Dr. Guido Costa Souza de Araujo (Orientador)

Tese apresentada ao Instituto de Computação, UNICAMP, como requisito parcial para a obtenção do título de Doutor em Ciência da Computação.

# FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DO IMECC DA UNICAMP

Bibliotecária: Maria Fabiana Bezerra Müller – CRB8 / 6162

Porto, João Paulo

P838t Técnicas e arquitetura para captura de traços e execução especulativa/João Paulo Porto-- Campinas, [S.P.: s.n.], 2011.

Orientador: Guido Costa Souza de Araujo.

Tese (doutorado) - Universidade Estadual de Campinas, Instituto de Computação.

Otimização.

2.Processamento paralelo (Computadores).

3.Compiladores (Programas de computador).

I. Araujo, Guido Costa

Souza de. II. Universidade Estadual de Campinas. Instituto de

Computação. III. Título.

Título em inglês: Techniques and architecture for trace detection and speculative execution

Palavras-chave em inglês (Keywords): 1. Optimization. 2.Parallel processing (Electronic computers). 3.Compilers (Computer programs).

Área de concentração: Arquitetura de Computadores

Titulação: Doutor em Ciência da Computação

Banca examinadora: Prof. Dr. Guido Costa Souza de Araujo (IC – UNICAMP)

Prof. Dr. Philippe Olivier Alexandre Navaux (UFRGS)

Dr. Maurício Breternitz Jr (AMD)

Prof. Dr. Luis Eduardo Buzato (IC – UNICAMP)

Prof. Dr. Edson Borin (IC - UNICAMP)

Data da defesa: 15/02/2011

Programa de Pós-Graduação: Doutorado em Ciência da Computação

#### TERMO DE APROVAÇÃO

Tese Defendida e Aprovada em 15 de fevereiro de 2011, pela Banca examinadora composta pelos Professores Doutores:

| quido                     | Fray          |

|---------------------------|---------------|

| Prof. Dr. Guido Costa Sou | uza de Araújo |

Prof. Dr. Philippe Olivier Alexandre Navaux INF / UFRGS

Dr. Maurício Breternitz Junior Advanced Micro Devices

Prof. Dr. Luiz Eduardo Buzato IC / UNICAMP

Prof. Dr. Edson Borin

IC / UNICAMP

### Técnicas e Arquitetura para Captura de Traços e Execução Especulativa

#### João Paulo Porto<sup>1</sup>

Fevereiro de 2011

#### Banca Examinadora:

- Prof. Dr. Guido Costa Souza de Araujo (Orientador)

- Prof. Dr. Philippe Olivier Alexandre Navaux Instituto de Informática, Universidade Federal do Rio Grande do Sul (UFRGS)

- Dr. Maurício Breternitz Jr. Advanced Micro Devices, Austin, TX (AMD)

- Prof. Dr. Luiz Eduardo Buzato

Instituto de Computação, Universidade Estadual de Campinas (UNICAMP)

- Prof. Dr. Edson Borin Instituto de Computação, Universidade Estadual de Campinas (UNICAMP)

- Prof. Dr. Alexandro Baldassin (Suplente) Instituto de Geociências e Ciências Exatas, Universidade Estadual de São Paulo (UNESP)

- Prof. Dr. Sandro Rigo (Suplente)

Instituto de Computação, Universidade Estadual de Campinas (UNICAMP)

- Prof. Dr. Paulo Cesar Centoducatte (Suplente) Instituto de Computação, Universidade Estadual de Campinas (UNICAMP)

<sup>&</sup>lt;sup>1</sup>Suporte financeiro da CAPES, Intel Corporation e Microsoft Research

### Resumo

É sabido que o modelo de desenvolvimento de micro-processadores baseado na extração de *Instruction-Level Parallelism* (ILP) de código sequencial atingiu seu limite. Encontrar soluções escaláveis e eficientes que permitam a manutenção de inúmeras instruções em execução simultaneamente tem se mostrado um desafio maior que o imaginado.

Neste sentido, arquitetos e micro-arquitetos de computadores vêm buscando soluções alternativas para o desenvolvimento de novas arquiteturas. Dentre as soluções existentes, vêm ganhando força as baseadas na extração de *Thread-Level Parallelism* (TLP). Resumidamente, TLP é um tipo de paralelismo que tenta quebrar um programa sequencial em *tarefas* relativamente independentes entre si para executá-las em paralelo.

TLP pode ser extraído por hardware ou software. Idealmente, uma solução híbrida deve ser utilizada, com o software realizando a identificação das oportunidades de extração de TLP, e com o hardware provendo suporte para execução do código gerado. Com tal solução de compromisso, o hardware fica livre da necessidade de especular, e o software pode trabalhar com maiores garantias.

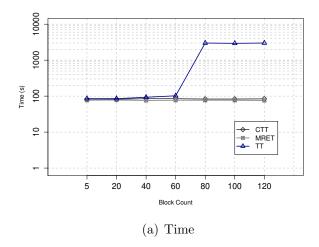

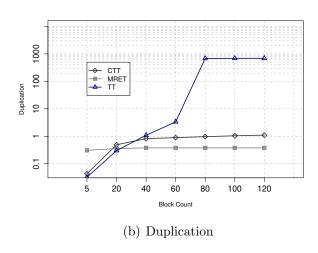

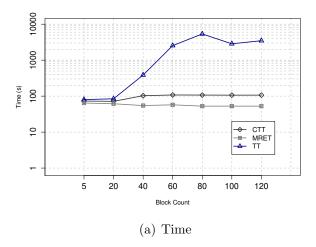

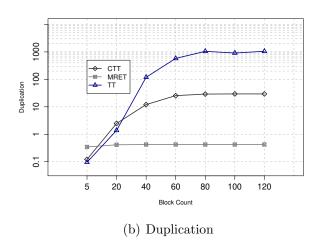

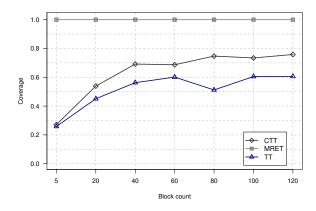

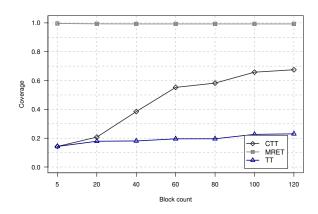

Nesta Tese, estudaram-se formas automáticas de paralelização e extração de TLP. Inicialmente, focou-se em traces dinâmicos de execução de programas sequenciais. Técnicas existentes (tais como MRET e Trace Trees) mostraram-se inapropriadas, de modo que desenvolveu-se uma nova técnica chamada  $Compact\ Trace\ Tree\ (CTT)$ , que mostrou-se mais rápida que  $Trace\ Trees$ .  $Trace\ Tree\ (TT)$  também apresentam grande nível de especialização de código ( $tail\ duplication$ ), característica ausente em MRET.

Além de CTT, esta Tese apresenta *Trace Execution Automata* (TEA), um autômato que representa *traces* de execução. Esta representação revelou, em nossos experimentos, quase 80% de economia de espaço quando comparada com a representação usual.

A seguir, o foco da Tese foi voltado para laços de execução e para paralelização estática de código sequencial através de *Decoupled Software Pipeline* (DSWP). Nosso primeiro resultado nesta direção, usando Java, mostrou claramente que sem nenhum suporte em *hardware*, a paralelização estática de programas poderia atingir um ganho de desempenho médio de 48% nas aplicações paralelizadas.

Finalmente, a Tese propõe um modelo de execução paralelo baseado em DSWP que

permite a consistência de dados entre as diversas *threads* de programas paralelizados. Apesar de não avaliar esta arquitetura completamente, os resultados iniciais são promissores. Além disso, o suporte necessário em *hardware* é simples e acomoda-se sobre o protocolo de coerência de *cache* existente, sem alterações sensíveis no processador.

### Abstract

The usual, *Insturction-Level Parallelism* (ILP)-oriented, microprocessor development model is known to have reached a hard-to-break limit. Finding scalable and efficient solutions that keep several instructions on-the-fly simultaneously has proven to be more difficult than imagined.

In this sense, computer architects and micro-architects have been seeking alternatives to develop new architectures. Among all, the TLP-based solutions are gaining strength. In short, TLP strives to break a sequential program into quasi-independent tasks in order to execute them in parallel.

TLP can be extracted either by hardware or software. Ideally, a hybrid solution would be employed, with the software being responsible to identifying TLP opportunities, and the hardware offering support for the parallel code execution. With such solution, the hardware is free from the heavy speculation burden, whilst the software can be parallelized with more warranties.

In this Thesis, automatic parallelization and TLP strategies were studied. The research first focused on dynamic execution traces. Existing techniques, such as MRET and  $Trace\ Trees$  proved unsuitable for our goals, which led us to develop a new trace identification technique called  $Compact\ Trace\ Trees$ , which showed to be faster than  $Trace\ Trees$ .  $Compact\ Trace\ Trees$  also present trace specialization, which MRET lacks.

Besides Compact Trace Trees, this Thesis presents a new trace representation called Trace Execution Automata, an automaton representing the execution traces. This technique revealed nearly 80% memory size savings when compared to the usual, code duplication representation.

Next, the Thesis' focus shifted to parallelizing loops statically. Our initial result in this direction, using Java and *without* any hardware support, clearly revealed that static parallelization of sequential programs could reach a 48% average speedup when compared to their sequential execution.

Finally, a new, *Decoupled Software Pipelining*-based execution model with automatic data coherence amongst parallelized programsthreads is proposed by the Thesis. Despite the lack of a full model evaluation, the initial results are promising. Differently from other

proposals, the hardware support necessary for this architecture is simple and builds upon the existing cache coherence protocol, without any modifications to this sensitive system component.

# Sumário

| Re           | esum  | 10                                                      | vi |

|--------------|-------|---------------------------------------------------------|----|

| $\mathbf{A}$ | bstra | net                                                     | ix |

| 1            | Intr  | rodução                                                 | 1  |

|              | 1.1   | Paralelismo em <i>Traces</i>                            | 2  |

|              |       | 1.1.1 Contribuições da Tese                             | 4  |

|              | 1.2   | Paralelismo em Laços Usando Decoupled Software Pipeline | 5  |

|              |       | 1.2.1 Técnicas Tradicionais de Paralelização de Laços   | 8  |

|              |       | 1.2.2 DSWP                                              | 8  |

|              |       | 1.2.3 Contribuições da Tese                             | 15 |

|              | 1.3   | Principais Contribuições                                | 16 |

|              | 1.4   | Publicações                                             | 16 |

|              | 1.5   | Organização desta Tese                                  | 17 |

| 2            | Tra   | balhos Relacionados                                     | 19 |

|              | 2.1   | <i>Traces</i>                                           | 19 |

|              | 2.2   | Thread-Level Speculation                                | 21 |

| 3            | Con   | npact Trace Trees in Dynamic Binary Translators         | 29 |

|              | 3.1   | Introduction                                            | 30 |

|              | 3.2   | Background on Trace Trees                               | 31 |

|              |       | 3.2.1 Sample Trace Tree Creation                        | 33 |

|              | 3.3   | Trace trees on DBT                                      | 34 |

|              |       | 3.3.1 Detecting Anchors                                 | 36 |

|              |       | 3.3.2 Indirect Branches                                 | 36 |

|              |       | 3.3.3 Trace Expansion                                   | 37 |

|              |       | 3.3.4 Code Duplication Due to Path Specialization       | 37 |

|              | 3.4   | Compact Trace Trees on DBT                              | 37 |

|              |       | 3.4.1 Compact Trace Tree Creation Example               | 39 |

|   | 3.5  | Experimental Results                                            | 39 |

|---|------|-----------------------------------------------------------------|----|

|   |      | 3.5.1 TT on DBT                                                 | 41 |

|   |      | 3.5.2 CTT on DBT                                                | 42 |

|   |      | 3.5.3 MRET, TT or CTT?                                          | 43 |

|   |      |                                                                 | 45 |

|   | 3.6  | Related and Previous Work                                       | 46 |

|   | 3.7  | Conclusions                                                     | 47 |

|   | 3.8  | Acknowledgments                                                 | 47 |

|   | Bibl | iography                                                        | 47 |

|   | _    |                                                                 |    |

| 4 |      |                                                                 | 51 |

|   | 4.1  | Introduction                                                    |    |

|   | 4.2  | Motivation                                                      |    |

|   | 4.3  |                                                                 | 57 |

|   |      |                                                                 | 58 |

|   |      |                                                                 | 59 |

|   | 4.4  | •                                                               | 61 |

|   |      |                                                                 | 63 |

|   |      | <b>₹</b>                                                        | 64 |

|   | 4.5  |                                                                 | 67 |

|   | 4.6  |                                                                 | 68 |

|   | Bibl | iography                                                        | 68 |

| 5 | Ext  | ending Decoupled Software Pipeline to Parallelize Java Programs | 71 |

|   | 5.1  |                                                                 | 72 |

|   |      | 5.1.1 Contributions                                             | 73 |

|   | 5.2  | Previous Work                                                   | 73 |

|   |      |                                                                 | 75 |

|   | 5.3  | v                                                               | 77 |

|   | 5.4  |                                                                 | 80 |

|   |      |                                                                 | 81 |

|   |      |                                                                 | 82 |

|   |      |                                                                 | 83 |

|   | 5.5  |                                                                 | 84 |

|   |      | •                                                               | 85 |

|   |      |                                                                 | 88 |

|   | 5.6  |                                                                 | 88 |

|   |      |                                                                 | 89 |

|   |      |                                                                 | 90 |

|                  |       | 5.6.3   | Derby Evaluation                                                | 91        |

|------------------|-------|---------|-----------------------------------------------------------------|-----------|

|                  |       | 5.6.4   | Mpegaudio Evaluation                                            | 93        |

|                  |       | 5.6.5   | Evaluating the Different Communication Queues Implementations . | 93        |

|                  | 5.7   | Conclu  | usions                                                          | 93        |

|                  | Bibl  | iograph | y                                                               | 94        |

| 6                | Cac   | he-Bas  | sed Cross-Iteration Coherence for Loop Parallelization          | 97        |

|                  | 6.1   | Introd  | luction                                                         | 98        |

|                  | 6.2   | Loop    | Parallelization and Execution                                   | 00        |

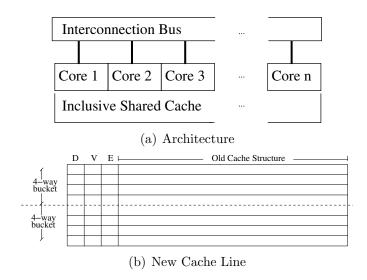

|                  | 6.3   | Archit  | secture                                                         | 02        |

|                  |       | 6.3.1   | The Iteration ID                                                | 02        |

|                  |       | 6.3.2   | The Coherence Tags                                              | 04        |

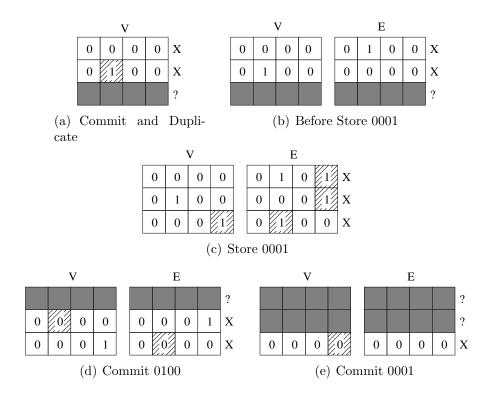

|                  |       | 6.3.3   | Committing and Squashing                                        | 07        |

|                  |       | 6.3.4   | On L1 Pressure                                                  | 08        |

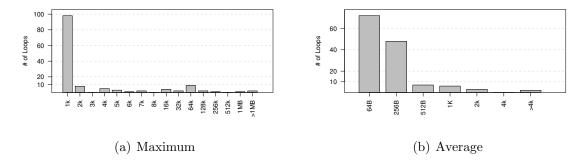

|                  | 6.4   | Exper   | imental Evaluation                                              | 08        |

|                  |       | 6.4.1   | Cache Size Requirements                                         | 08        |

|                  |       | 6.4.2   | Synchronization Overhead                                        | 10        |

|                  | 6.5   | Relate  | ed Work                                                         | 10        |

|                  | 6.6   | Conclu  | usions and Future Work                                          | 13        |

|                  | Bibl  | iograph | ny                                                              | 13        |

|                  | 6.A   | Exam    | ples                                                            | 16        |

|                  | 6.B   | Loop    | Detection and Selection                                         | 19        |

|                  | 6.C   | Proof   | of Correctness                                                  | 21        |

|                  |       | 6.C.1   | Lemma 1                                                         | 21        |

|                  |       | 6.C.2   | Write After Write (WAW)                                         | 21        |

|                  |       | 6.C.3   | Write After Read (WAR)                                          | 22        |

|                  |       | 6.C.4   | Read After Write (RAW)                                          | 24        |

| 7                | Con   | ısidera | ações Finais                                                    | 27        |

|                  | 7.1   | Traba   | lhos Futuros                                                    | 28        |

| Bi               | bliog | grafia  | 1:                                                              | 30        |

|                  |       |         |                                                                 |           |

| $\boldsymbol{H}$ | Pro   | va de ' | Corretude – Consistência e Versionamento de Dados 13            | <b>37</b> |

# Lista de Tabelas

| 1.1 | Resumo das características de MRET, TT e CTT                | 4   |

|-----|-------------------------------------------------------------|-----|

| 3.1 | Average coverage for all experiments                        | 41  |

| 3.2 | Total time on the framework (minutes)                       | 41  |

| 3.3 | Average duplication                                         | 42  |

| 3.4 | Total memory usage (in MB)                                  | 42  |

| 4.1 | Size Savings with TEA                                       | 62  |

| 4.2 | TEA Runtime Aspects – Replaying                             | 64  |

| 4.3 | TEA Runtime Aspects – Recording                             | 65  |

| 4.4 | TEA Overhead for Various Configurations                     | 66  |

| 5.1 | The Selected Benchmarks                                     | 84  |

| 5.2 | Size of the Pipeline Stages Compared to the Sequential Loop | 85  |

| 5.3 | Setup Configurations                                        | 88  |

| 6.1 | Synchronization Overhead in a Quad-Core Processor           | 111 |

# Lista de Figuras

| 1.1  | Exemplos de <i>Traces</i> de Execução                          | 3  |

|------|----------------------------------------------------------------|----|

| 1.2  | Antes da Transição 5 $\rightarrow$ 7                           | 6  |

| 1.3  | Após a Transição $5 \rightarrow 7$                             | 7  |

| 1.4  | Laço com Iterações Independentes e sua Paralelização com DOALL | 9  |

| 1.5  | Laço Paralelizado com DOACROSS                                 | 10 |

| 1.6  | Atualização de Elemento de Lista Ligada                        | 11 |

| 1.7  | Paralelização do Código da Figura 1.6                          | 12 |

| 1.8  | Bits Extra Utilizados para Consistência                        | 15 |

| 3.1  | Sample function                                                | 34 |

| 3.2  | Sample Trace Tree creation                                     | 35 |

| 3.3  | Sample Compact Trace Tree creation                             | 40 |

| 3.4  | 181.mcf – SPEC2000 int                                         | 43 |

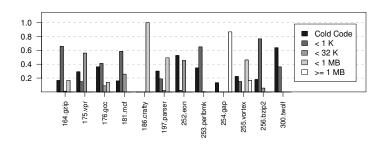

| 3.5  | 256.bzip2 – SPEC2000 int                                       | 44 |

| 3.6  | Interesting results                                            | 45 |

| 4.1  | Code Snippet and Resulting Trace                               | 54 |

| 4.2  | Optimization for Fig. 4.1                                      | 55 |

| 4.3  | (a) Sample code. (b) CFG for the sample code. (c) MRET traces  | 56 |

| 4.4  | (a) DFA for MRET traces. (b) TEA for whole program             | 57 |

| 5.1  | DOALL loop                                                     | 73 |

| 5.2  | Non-DOALL loops                                                | 74 |

| 5.3  | Examples for Definitions 5.3.1, 5.3.2 and 5.3.3                | 78 |

| 5.4  | Forward and Backward Communication Example                     | 79 |

| 5.5  | Sample Loop                                                    | 80 |

| 5.6  | A Sample 3-Stage Pipeline                                      | 81 |

| 5.7  | The funpipe Package Interface                                  | 81 |

| 5.8  | mpegaudio                                                      | 86 |

| 5.9  | compress                                                       | 87 |

| 5.10 | compress                                                       | 89 |

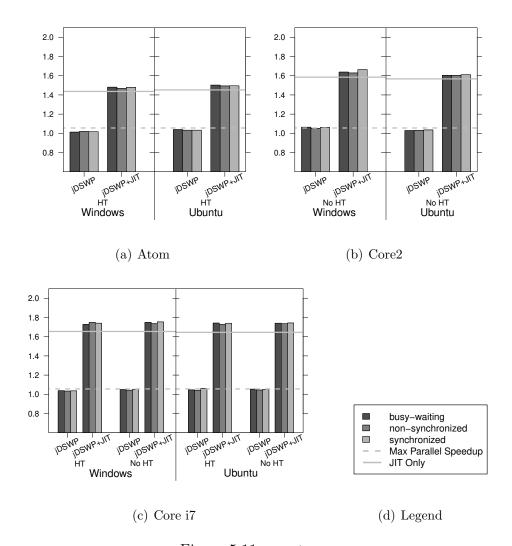

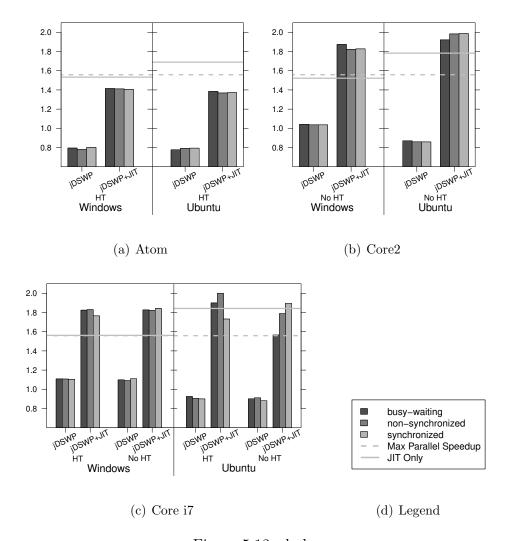

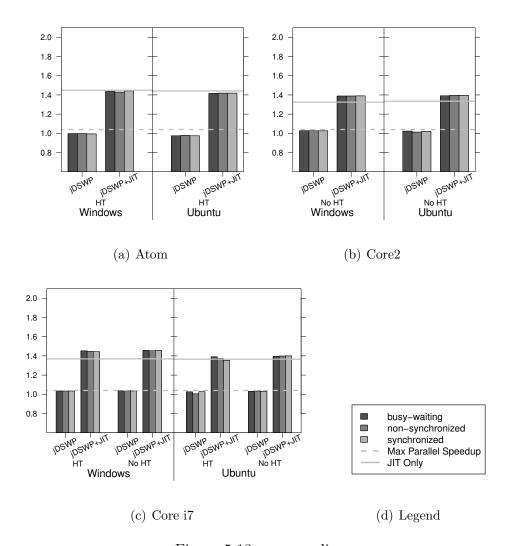

| 5.11 | crypto.rsa                                                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------|

| 5.12 | $derby \dots \dots$ |

| 5.13 | mpegaudio                                                                                                                 |

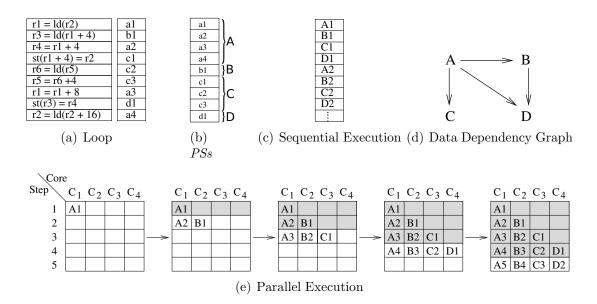

| 6.1  | A loop, its <i>PSs</i> and the pipelined execution                                                                        |

| 6.2  | Multicore System                                                                                                          |

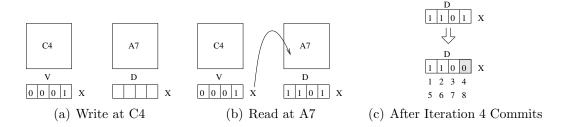

| 6.3  | Core 0's Written Data                                                                                                     |

| 6.4  | Keeping Track of Dependencies                                                                                             |

| 6.5  | Avoiding Duplicated Cache Lines                                                                                           |

| 6.6  | Cache Size Requirements                                                                                                   |

| 6.7  | Cache Size Requirements per Application                                                                                   |

| 6.8  | All possible cases                                                                                                        |

| 6.9  | Loop analysis and selection                                                                                               |

|      |                                                                                                                           |

# Lista de Algoritmos

| 3.2.1 Trace Tree Creation rules         |

|-----------------------------------------|

| 3.2.2 Trace Tree link rules             |

| 3.4.1 Compact Trace Tree Creation rules |

| 3.4.2 Compact Trace Tree link rules     |

| 4.3.1 Converting Traces to TEA          |

| 4.3.2 Using TEA to Record Traces        |

| 6.B.1Loop Detection Algorithm           |

# Lista de Acrônimos

| $\mathbf{AFD}$       | Autômatos Finitos Determinísticos                                               | . 51  |

|----------------------|---------------------------------------------------------------------------------|-------|

| AMAS                 | <b>-BT</b> Architectural and Micro-Architectural Support for Binary Translation | . 29  |

| $\mathbf{CFC}$       | Componente Fortemente Conexa                                                    | . 11  |

| $\mathbf{CFP}$       | Continual Flow Pipeline                                                         | 21    |

| $\mathbf{CMS}$       | Code Morphing Software                                                          | . 20  |

| $\mathbf{CPR}$       | Checkpoint Processing and Recovery                                              | . 21  |

| $\mathbf{CTT}$       | Compact Trace Tree                                                              | vii   |

| DSMT:                | x Distributed SMTx                                                              | . 14  |

| $\mathbf{DSWP}$      | Decoupled Software Pipeline                                                     | vii   |

| $\mathrm{E/S}$       | Entrada e Saída                                                                 | . 23  |

| $\mathbf{ECM}$       | Eliminação de Código Morto                                                      | . 20  |

| $\mathbf{ESC}$       | Eliminação de Subexpressões Comuns                                              | . 20  |

| $\operatorname{GDP}$ | Grafo de Dependências do Programa                                               | . 11  |

| $\mathbf{GFC}$       | Grafo de Fluxo de Controle                                                      | 2     |

| HTM                  | Hardware Transactional Memory                                                   | . 27  |

| ICMC                 | Inter-Core Memory Coherence                                                     | . 25  |

| $\operatorname{ILP}$ | Instruction-Level Parallelism                                                   | . vii |

| ISCA                 | International Symposium on Computer Architecture                                | 1     |

| JVM                  | Java Virtual Machine                                                            |       |

| $\mathbf{LEI}$       | Last Executed Iteration                                                         | . 19  |

| $\operatorname{LLP}$ | Loop-Level Parallelism                                                          | . 27  |

| LNCS                 | Lecture Notes in Computer Science                                               |       |

| $\mathbf{MDT}$       | Memory Disambiguation Table                                                     |       |

|                      | Most Frequently Executed Tail                                                   |       |

|                      | Most Recently Executed Tail                                                     |       |

| MRET                 | $^2$ Two-pass MRET                                                              |       |

| MSI                  | Modified - Shared - Invalid                                                     | . 18  |

| MSSP                 | Master/Slave Speculative Parallelization                                        |       |

| MSI                  | Modified - Shared - Invalid                                                     | . 18  |

| $\mathbf{MESI}$      | Modified - Exclusive - Shared - Invalid                                         | . 27  |

| MOSI                 | Modified - Owner - Shared - Invalid                      | 7  |

|----------------------|----------------------------------------------------------|----|

| $\mathbf{NET}$       | Next Executed Tail                                       | 2  |

| PS-DS                | <b>WP</b> Parallel Stage DSWP                            | 3  |

| $\mathbf{RAW}$       | Read After Write         2                               | 3  |

| SPAA                 | Symposium on Parallelism in Algorithms and Architectures | 7  |

| SMP                  | Symmetric MultiProcessors                                | 3  |

| Spec-D               | <b>SWP</b> Speculative DSWP                              | 1  |

| SVC                  | Speculative Versioning Cache                             | 3  |

| $\mathbf{SMT}$       | Symmetric Multi-Threading                                | 8  |

| $\mathbf{SMTx}$      | Software Multi-threaded Transactions                     | 4  |

| TEA                  | Trace Execution Automatavi                               | ii |

| $\operatorname{TLP}$ | Thread-Level Parallelism                                 | ii |

| TLS                  | Thread-Level Speculation                                 | 5  |

| TLDS                 | Thread-Level Data Speculation                            | 3  |

| TT                   | Trace Tree                                               | ii |

| $\mathbf{SMT}$       | Symmetric Multi-Thread                                   | 8  |

| UCP                  | Unidade Central de Processamento                         | 1  |

| $\mathbf{VLIW}$      | Very-Long Instruction Word                               | 7  |

| WAR                  | Write After Read                                         | 3  |

| WAW                  | Write After Write                                        | 3  |

| WiDGI                | ET Wisconsin Decoupled Grid Execution Tiles              | 8  |

### Capítulo 1

# Introdução

La Microarchitecture est Morte. Longue Vie à la Microarchitecture!.

A frase, título de um painel do *International Symposium on Computer Architecture* (ISCA) de 2010, resume, de maneira magistral, o presente momento para arquitetura e micro-arquitetura de computadores. A versão original (em francês *Le Roi est mort. Vive le Roi!* – O Rei morreu. Vivas ao Rei!) é utilizada quando da ascensão de um monarca, após o falecimento do monarca anterior, e denota a continuidade do governo.

É sabido que o desenvolvimento de processadores nos moldes empregados nas últimas décadas chegou ao ápice, e que novas técnicas serão necessárias para que novos *chips* sejam mais eficientes que seus predecessores, de modo que a *velha* micro-arquitetura morreu, e *novas* abordagens fazem-se necessárias.

Existem muitas proposta de novos modelos de execução (veja a Seção 2.2), bem como antigas idéias recicladas [19] para os novos tempos da micro-arquitetura. A existência de tal variedade de abordagens aponta claramente para um ponto de inflexão no desenvolvimento de processadores e, de certa forma, na maneira de se programar os novos chips.

Por um longo tempo, o foco no aumento de desempenho dos computadores foi a Unidade Central de Processamento (UCP). Manter mais de uma instrução em execução foi o subterfúgio mais utilizado pelos arquitetos de computadores, no início em processadores com *pipeline* em ordem [43] até os mais recentes processadores capazes de executar instruções fora de ordem [61]. Este modelo foi possível graças à evoluções micro-arquiteturais e avanços nos processos de fabricação que permitiram a manutenção da tendência histórica de dobrar a disponibilidade de transistores sem aumentar a área do *chip*, aumentando a frequência de operação destes transistores.

Entretanto, operar em altas frequências aumenta a dissipação de potência de um *chip*. Por exemplo, o processador Pentium ® IV (mono-núcleo) chegou a dissipar até 115W [29] (prescott @ 3.8 GHz). Assim, a Indústria adotou os processadores com múltiplos núcleos

como solução para os problemas enfrentados pelo modelo anterior.

Neste novo modelo, para aproveitar todo o potencial de processamento disponibilizado pelas UCP, é necessária a programação explícita em múltiplas linhas de execução (multi-thread programming). Apesar dos esforços para popularizar e simplificar a programação multi-threaded [14,53], a adoção deste novo modelo de programação tem sido lenta e mais difícil do que o originalmente imaginado.

Nas Seções seguintes resume-se os problemas de pesquisa encontrados e as contribuições feitas por esta Tese.

#### 1.1 Paralelismo em *Traces*

Traces são utilizados como forma de detectar regiões quentes em programas. Usualmente, estas regiões consistem de algumas poucas instruções que são responsáveis por grande parte do tempo de execução de programas. Além de pequenos, traces usualmente contém apenas os caminhos efetivamente exercitados durante a execução.

Por estas duas razões, *traces* são ótimos candidatos à otimização. Por serem usualmente pequenos, os algoritmos de fluxo de dados empregados por otimizadores executam rapidamente; por serem responsáveis por grande parte do tempo de execução, qualquer ganho oriundo da otimização tende a ser potencializado.

Antes, porém, de iniciar o estudo em oportunidades de paralelização em traces, estudaram-se técnicas de identificação dos mesmos. As técnicas Most Recently Executed Tail (MRET) [16] (também conhecido por Next Executed Tail (NET)) e TT [18], utilizadas durante a pesquisa, estão brevemente explicadas abaixo. Descrita abaixo também está a CTT [46], uma contribuição desta Tese. Veja a Seção 2.1 para outras técnicas.

Possivelmente a técnica mais conhecida para identificação de traces, MRET é também a mais simples e a que apresenta o menor custo em tempo de execução. Para identificar traces, MRET instrumenta as instruções (ou blocos básicos) do programa que são alvos de saltos para trás (i.e., saltos cujo alvo estão em instruções prévias no código do programa). MRET tende, desta forma, a instrumentar loop headers.

Assim que uma instrução é identificada como "quente" (*i.e.*, executa além de um limite determinado), todas as instruções executadas pelo programa devem ser marcadas até que (1) o programa execute uma instrução previamente marcada; ou (2) o número de instruções marcadas atinja um determinado limite. As instruções marcadas são consideradas um *trace* de execução.

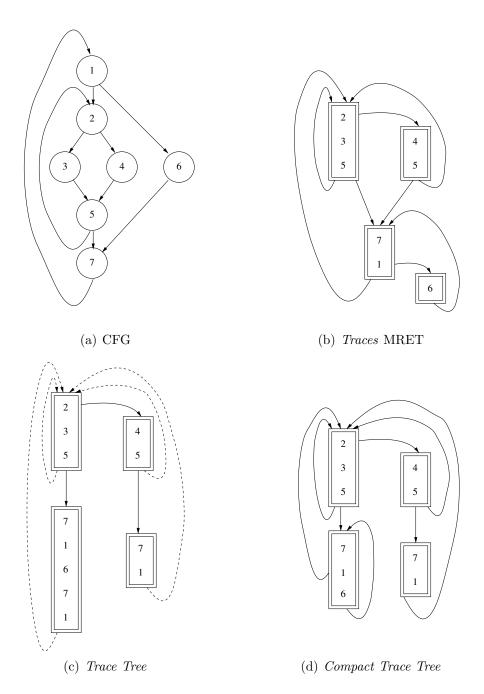

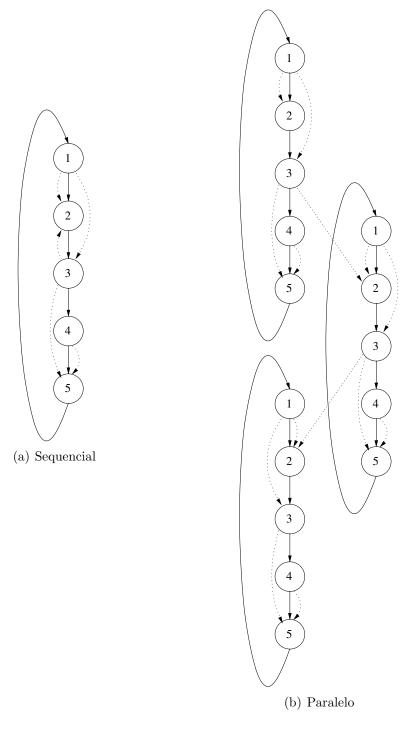

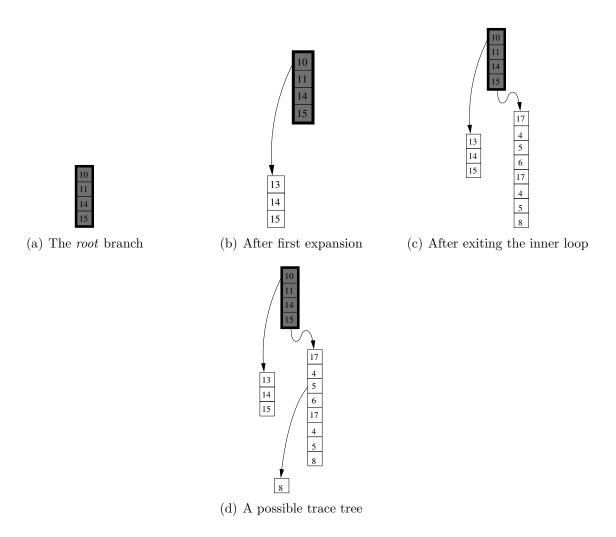

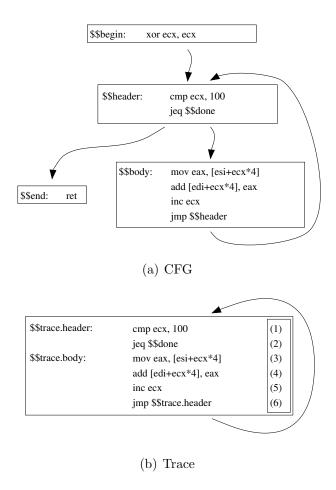

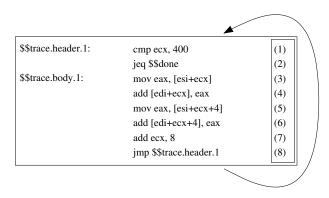

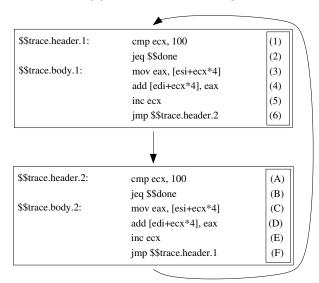

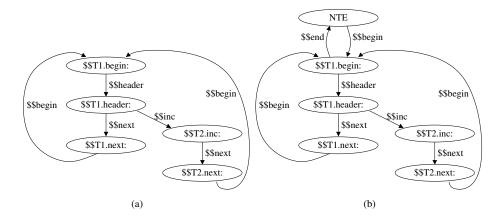

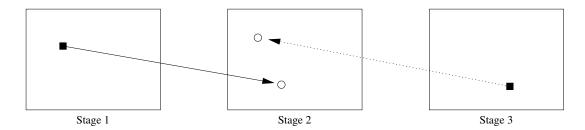

Por exemplo, o trace da Figura 1.1(b) representa os traces MRET decorrentes da execução do programa (com os retângulos representando sequências de instruções com uma única entrada e múltiplas saídas, i.e., super blocos), cujo Grafo de Fluxo de Controle (GFC) está representado na Figura 1.1(a). Repare que os traces representados são capazes

Figura 1.1: Exemplos de Traces de Execução

| Técnica | Especialização | Duplicação |

|---------|----------------|------------|

| MRET    | Baixa          | Mínima     |

| TT      | Altíssima      | Altíssima  |

| CTT     | Alta           | Média      |

Tabela 1.1: Resumo das características de MRET, TT e CTT

de capturar qualquer execução do programa.

Entretanto, MRET falha ao não ser capaz de identificar traces especializados da execução do programa. Tal especialização é desejável para potencializar as possibilidades de otimização. Por exemplo, note que não é possível identificar com clareza se todas as saídas do laço interno (aresta  $5 \to 7$  no GFC original) passam pela aresta  $1 \to 6$ . Os traces apenas indicam que tal aresta foi utilizada, não fornecendo informações adicionais (e.g., se a última iteração do laço interno a executar for  $2 \to 4 \to 5$ , então a aresta  $1 \to 6$  nunca será exercitada).

Gal et al. [18] propõem Trace Tree (TT). Diferentemente de MRET, TT identifica caminhos especializados da execução do programa. A forma de identificar instruções quentes em TT é idêntica a de MRET; a condição de parada de gravação de TT, contudo, é bem diferente.

TT marca as instruções executadas após a identificação de uma instrução quente até que o fluxo de execução do programa retorne à primeira instrução marcada. Assim, em TT as arestas de retorno (back edges) são implícitas, sendo por isso representada com arestas tracejadas nos traces da Figura 1.1(c), que ilustra uma possível TT para a execução do código na Figura 1.1(a).

Ao contrário de MRET, a TT representada não consegue capturar todos os fluxos de execução possíveis para o código original. Repare, em particular, que os ramos que representam o laço externo (super blocos  $\boxed{7,1,6,7,1}$  e  $\boxed{7,1}$ ) podem crescer ilimitadamente. Cientes destes problemas, os autores propõem heurísticas para limitar o crescimento da árvore. Entretanto, em nossos experimentos, as heurísticas propostas foram ineficientes.

#### 1.1.1 Contribuições da Tese

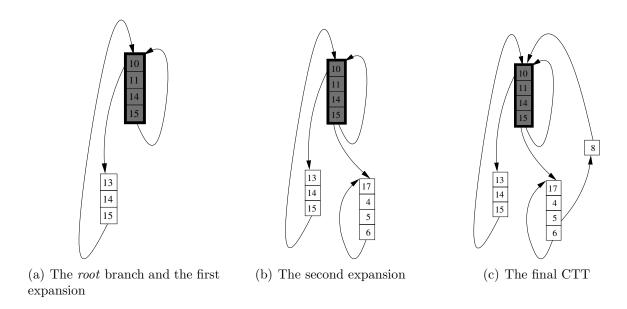

CTT (veja o Capítulo 3 ou [46]) surgiu como uma técnica intermediária entre MRET e TT. Nosso objetivo inicial era obter traces mais especializados que MRET e mais compactos que TT. Para identificar o término de um trace, CTT identifica saltos para instruções que iniciem um trace no caminho que vai da raiz do trace (i.e., o primeiro ramo identificado), até o trace sendo gravado. Isso permite que CTT identifique outros laços além do laço interno, permitindo uma representação mais compacta. A Tabela 1.1 resume as principais características de cada técnica.

A Figura 1.1(d) ilustra os *traces* que CTT gera. Note que a especialização de caminhos permite identificar instruções que nunca serão executadas dependendo do fluxo de execução do programa.

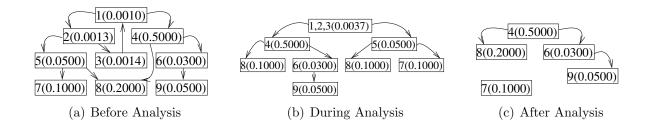

Outro resultado obtido por esta Tese foi o TEA (Capítulo 4 ou [45]), uma nova forma de representar traces que é independente da estratégia utilizada para identificá-los. TEA representa um trace t como um autômato. Para criar um TEA T a partir de um trace t existente, basta criar um estado  $E_i$  em T para cada instrução i de t, adicionando em T as transições  $E_i \xrightarrow{j} E_j$  para todos os pares de instruções (i, j) de t tal que exista uma aresta de fluxo de controle  $i \to j$ .

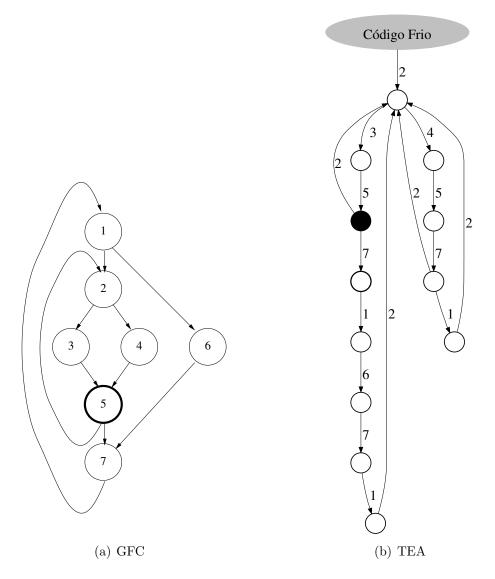

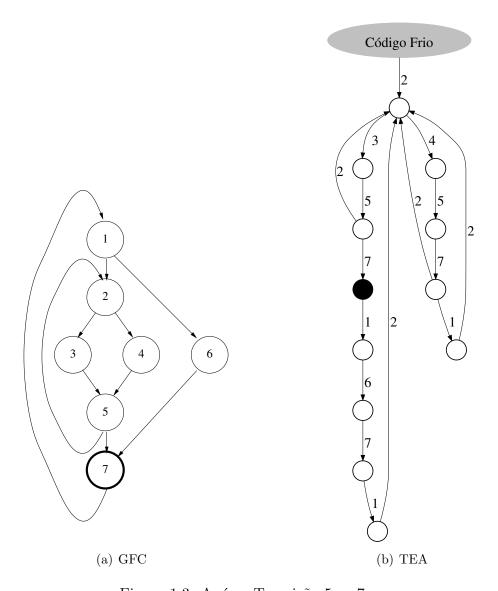

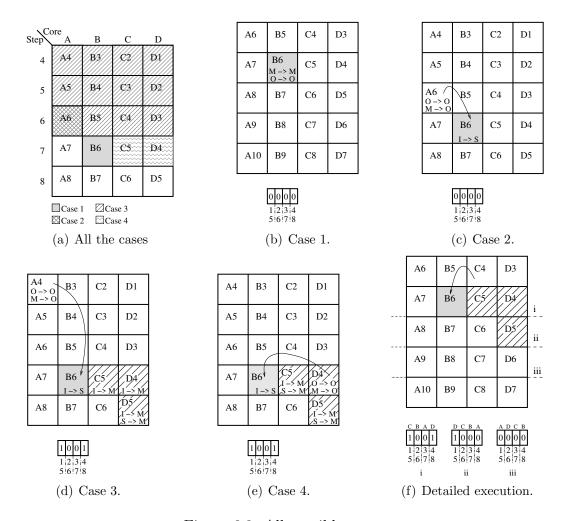

TEA não duplica código, executando as instruções originais do programa. As Figuras 1.2 e 1.3 ilustram a TT da Figura 1.1(c) representada por um TEA. Na Figura 1.2, o programa está prestes a fazer a transição  $5 \rightarrow 7$ , com o estado atual do autômato (e a instrução correspondente à 5) em destaque; a Figura 1.3 mostra o programa após a transição.

TEA pode ser atualizado dinamicamente para, por exemplo, indicar a detecção de um novo trace. Partindo de um autômato vazio (i.e., um TEA somente com o estado "Código Frio") é possível adicionar os traces detectados durante a execução de um programa. Com isso, TEA pode ser utilizada como representação única em um ambiente de otimização dinâmico.

O overhead em gerenciar a detecção, criação e otimização de traces exclusivamente em software em tempo de execução mostrou-se elevado demais (veja os Capítulos 4 e 3 para maiores detalhes) para que ganhos oriundos de otimização viessem a sobrepujá-lo. Assim, o foco do estudo mudou para otimização estática de laços.

# 1.2 Paralelismo em Laços Usando Decoupled Software Pipeline

A otimização estática de laços regulares é um problema resolvido (veja a Seção 5.2). Entretanto, a paralelização de laços não regulares continua sendo um problema em aberto. Existe ampla disponibilidade bibliográfica sobre *hardwares* especializados com suporte a paralelização oferecendo, entre outros, mecanismos que garantem a coerência entre as diversas linhas de execução do programa paralelo. Estas soluções são usualmente chamadas de *Thread-Level Speculation* (TLS).

TLS é uma área da arquitetura de computadores que utiliza algum tipo de especulação (de dados, de controle ou ambos) para aumentar o desempenho de aplicações. Como a execução ocorre de forma *especulativa*, mecanismos para recuperação de falhas são necessários para garantir a corretude da execução paralela.

Figura 1.2: Antes da Transição  $5 \to 7$

Figura 1.3: Após a Transição  $5 \to 7$

Em TLS esta Tese propõe um modelo de execução paralelo que, por sua regularidade, simplifica o suporte necessário para execução. Uma prova de corretude para tal modelo é apresentada no Apêndice A. Como o modelo de execução é baseado em DSWP, a Seção 1.2.2 descreve esta técnica. Por serem utilizadas para a explicação de DSWP, as técnicas tradicionais de paralelização DOALL e DOACROSS são ilustradas na próxima Seção.

#### 1.2.1 Técnicas Tradicionais de Paralelização de Laços

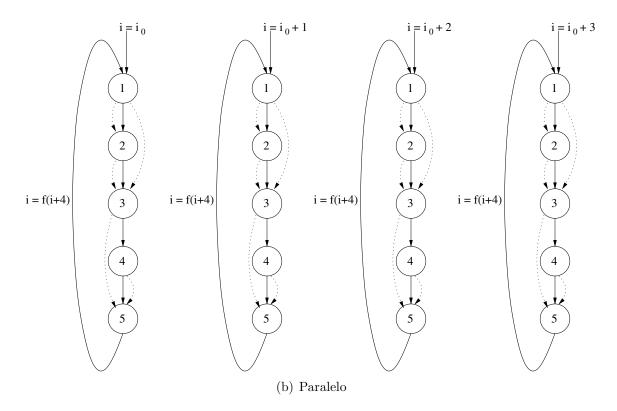

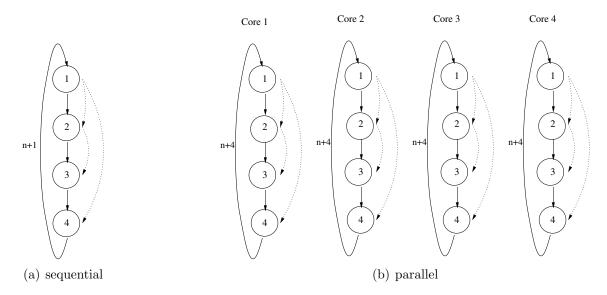

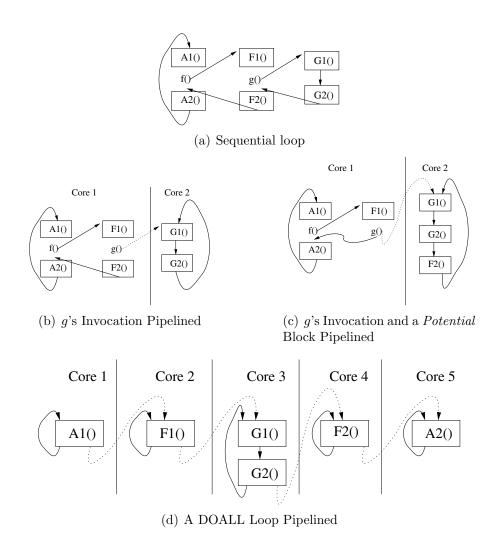

Tradicionalmente, as técnicas DOALL e DOACROSS são utilizadas para paralelizar laços estaticamente. Das duas, DOALL é a mais simples: laços paralelizados com esta técnica precisam que suas iterações sejam independentes entre si (*i.e.*, não pode haver dependências *loop carried*). A Figura 1.4(a) ilustra um laço que pode ser paralelizado empregando-se DOALL. As arestas sólidas são arestas de fluxo de controle, e as arestas pontilhadas representam dependências de dados.

DOALL é uma técnica escalável com o número de núcleos: o programa paralelo pode identificar, em tempo de execução, quantos núcleos estão disponíveis para execução do laço, criando um número ótimo de *threads*.

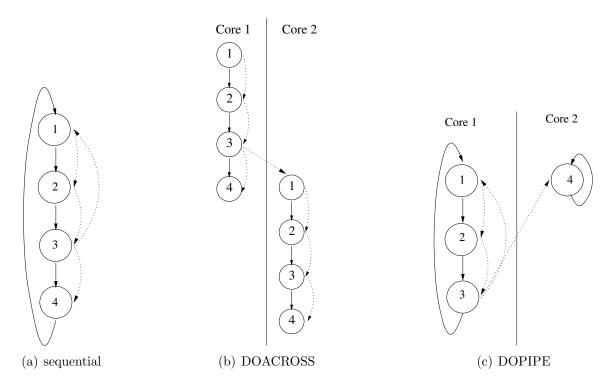

DOACROSS é ligeiramente mais geral que DOALL: dependências entre iterações são permitidas, sendo comunicadas em tempo de execução. A idéia básica por trás de DOACROSS é gerar todas as dependências de iterações futuras o mais cedo possível, iniciando as novas iterações conforme suas dependências são satisfeitas. A Figura 1.5 ilustra um laço que não pode ser paralelizado com DOALL: repare a dependência de dados  $3 \rightarrow 2$ . Esta única aresta faz com que o laço da Figura 1.5(a) não possa ser tratado por DOALL, enquanto a Figura 1.4(a) possa.

A Figura 1.5(b) ilustra a paralelização do laço apresentado na Figura 1.5(a). Diferentemente de DOALL, DOACROSS não é escalável com o número de núcleos: o código é gerado com um número pré-determinado de *threads* necessárias para sua execução. No exemplo da Figura, o número de *threads* assumido para paralelização é dois.

#### 1.2.2 DSWP

DSWP foi inicialmente proposto por Ottoni et al. [41]. Neste trabalho, os autores introduzem a nova técnica de TLS, descrevendo os algoritmos utilizados para geração de código paralelo e o mecanismo de comunicação inter-thread. Além disso, os autores apresentam uma extensa avaliação experimental da técnica, incluindo uma avaliação de tamanho e latência de várias filas de comunicação. A avaliação foi feita utilizando-se um simulador do processador Itanium(R) 2 [44] e o compilador IMPACT [4].

Figura 1.4: Laço com Iterações Independentes e sua Paralelização com DOALL.

Figura 1.5: Laço Paralelizado com DOACROSS.

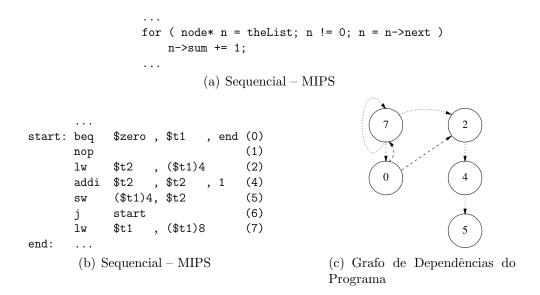

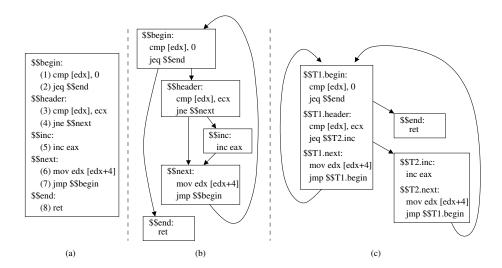

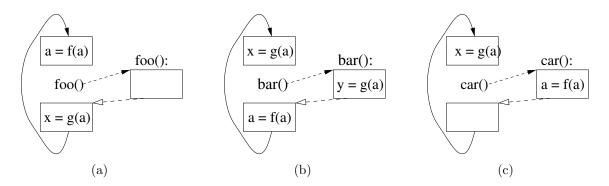

Figura 1.6: Atualização de Elemento de Lista Ligada

Como ilustração para DSWP, considere o laço apresentado na Figure 1.6(a), que percorre uma lista ligada somando 1 ao valor do campo sum. A Figura 1.6(b) mostra a codificação do laço em linguagem de montagem do processador MIPS já com os delay slots preenchidos. Os números entre parênteses indicam o ciclo em que as instruções entrariam no pipeline, e são usados para identificá-las nos exemplos.

O Grafo de Dependências do Programa (GDP), apresentado na Figura 1.6(c), representa dependências de dados com arestas pontilhadas e dependências de controle com arestas tracejadas. No GDP, vemos a existência de uma Componente Fortemente Conexa (CFC) contendo a instrução 7. Ele mostra também a existência de duas cadeias de dependências de dados: uma entre as instruções 2, 4 e 5, e outra entre as instruções 7 e 0. Há, ainda, dependências de controle entre as instruções 0 e 2 e 0 e 7.

O laço paralelizado utilizando-se DSWP é apresentado na Figura 1.7(a). Como é possível ver na Figura, DSWP gera dois estágios para o laço do exemplo, sendo o primeiro responsável por caminhar na lista ligada e, o segundo, por atualizar os elementos da lista. Note a existência de duas arestas entre o primeiro e o segundo estágio. Estas dependências serão honradas em tempo de execução com as filas de comunicação entre os núcleos. Vale ressaltar que as filas devem ser suficientemente rápidas para que a comunicação de dados não inviabilize a técnica.

O próximo trabalho baseado em DSWP foi publicado por Vachharajani et al. [64] e é chamado Speculative DSWP (Spec-DSWP). Os autores observaram que, apesar do bom desempenho de DSWP, havia ainda desempenho que poderia ser extraído utilizando-se especulação em dependências infrequentes que são removidas antes do compilador otimizar

Figura 1.7: Paralelização do Código da Figura 1.6

o código com DSWP. Nenhum suporte extra em *hardware* além da fila de comunicação é necessário para Spec-DSWP, de modo que o código gerado deve ser capaz de detectar e recuperar-se de falhas de especulação.

Continuando com o exemplo da lista ligada (Figura 1.6(b)), se a lista for suficientemente longa, a dependência de controle para a saída do laço ocorre infrequentemente. Desta forma, o compilador pode especulativamente remover a dependência,  $0 \to 2$ , conforme mostrado na Figura 1.7(b), de modo que a comunicação entre os estágios será, neste exemplo, diminuída. Obviamente, o compilador deverá inserir código de compensação devido à remoção da aresta de dependência.

O trabalho de Raman et al. [50] abandonou o suporte à especulação adicionado por [64] e utilizou outro subterfúgio para aumentar o desempenho de DSWP. Após o código paralelo ser gerado pelo compilador, a nova técnica, chamada Parallel Stage DSWP (PS-DSWP), aplica otimizações clássicas como DOALL [31] e DOACROSS [13] aos estágios gerados.

A Figura 1.7(c) mostra o resultado da aplicação da técnica de paralelização DOALL ao segundo estágio do programa paralelizado com DSWP. No exemplo, fazer esta otimização permite ao programa tolerar maiores latências no acesso à memória com o uso de uma thread extra. Note que a aresta de dependência de controle está presente.

Uma extensiva análise do desempenho de DSWP pode ser encontrada em [51]. Neste texto, os autores avaliam quais os fatores são possíveis gargalos para que DSWP gere código com o maior aumento de desempenho possível. Os autores avaliam diversas configurações de processadores (de dois até oito núcleos) e várias configurações distintas para a fila de comunicação. Eles introduzem uma nova variável nas análises: a banda disponível para o acesso à fila de comunicação. Os autores derivam expressões analíticas que podem ser utilizadas no momento da partição do programa em threads para determinar se o custo de comunicação é tolerável.

O trabalho de Huang et al. [28] é semelhante à união de [50] e [64], com a diferença que, neste novo trabalho, os autores aplicam outras técnicas de otimização aos estágios do pipeline de threads além de DOALL, a saber, LOCALWRITE [23] e SpecDOALL [52]. A avaliação experimental deste artigo foi feita, diferentemente dos anteriores, em um processador com oito núcleos comercial, logo, todo o suporte para as aplicações paralelizadas foi provido em software.

A união de Spec-DSWP e PS-DSWP é ilustrada na Figura 1.7(d). Note que o segundo estágio foi otimizado com DOALL e que a aresta de dependência de controle foi removida.

Todos os trabalhos envolvendo DSWP relacionados acima têm uma característica em comum: eles assumem a disponibilidade de informações completas sobre os acessos à memória realizados pelo código que será alvo da paralelização. Sem tal informação, o compilador não é capaz de particionar o código em estágios. Ainda pior, não há nenhum

suporte, tanto em hardware quando em software, para detecção de falhas na atualização da memória do programa.

Software Multi-threaded Transactions (SMTx), proposto por Raman et al. [49], executa cada estágio do laço paralelizado em um processo distinto, diferentemente das propostas anteriores, que utilizavam threads para executar os estágios. Em SMTx, cada iteração do laço original é uma transação (uma Tx), sendo cada estágio gerado na paralelização chamado de subTx. Há, ainda, dois outros estágios especiais cujas funções serão explicadas nos parágrafos seguintes. Para um exemplo da arquitetura proposta por SMTx, veja a Figura 1.7(e).

Inicialmente, todas as subTx possuem o mesmo mapeamento da memória virtual, sendo que as páginas estão protegidas contra escrita. No momento em que uma subTx s solicita uma escrita na página p, o sistema operacional cria uma nova página p' (cópia de p) para s. Assim, cada subTx executa isoladamente das outras. Caso o novo valor escrito seja necessário em uma subTx t diferente de s, SMTx propõe um sistema de comunicação de dependências entre subTx.

O código paralelo é também instrumentado de modo que todos os acessos à memória em todas as subTx sejam armazenados em um log, cujas entradas consistem de três campos: Operação (load ou store), Endereço e Valor.

Quando todas as subTxs de uma Tx terminam de executar, seus logs são combinados para formar um único log. Uma subTx especial chamada Try-Commit recebe este log e o processa. Tal processamento consiste em gravar o conteúdo do campo Valor em Endereço (no caso de uma entrada do tipo store no log) ou verificar se o valor presente na memória em Endereço é idêntico à Valor (loads). A lógica por trás deste processamento é que o log contém os acessos à memória da mesma forma que eles seriam executados pelo programa sequencial original. O resultado do processamento é informado a última subTx, chamada Commit.

Commit utiliza o resultado do processamento do log de uma Tx para identificar se execução paralela da iteração que gerou o log foi bem-sucedida ou não. O log de uma Tx bem-sucedida é executado por Commit (i.e., as entradas do tipo store no log são utilizadas para atualizar o conteúdo da memória) de modo a consolidar o estado do programa sequencial. Uma Tx mal-sucedida dispara a recuperação de falhas.

SMTx foi proposto e avaliado para ser utilizado em computadores com múltiplos processadores. Kim et al. [33] propõem Distributed SMTx (DSMTx), que é a generalização de SMTx para execução em clusters de computadores onde o acoplamento não seja tão forte. O custo de comunicação em tais ambientes é consideravelmente mais alto que em computadores multiprocessados, de modo que os autores avaliam formas de buferização de dados.

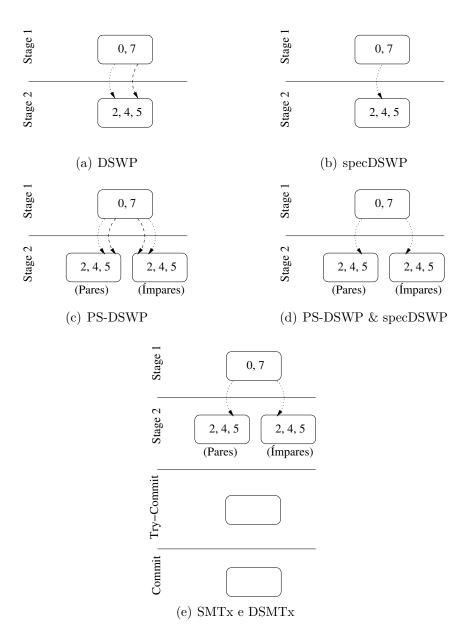

Figura 1.8: Bits Extra Utilizados para Consistência

#### 1.2.3 Contribuições da Tese

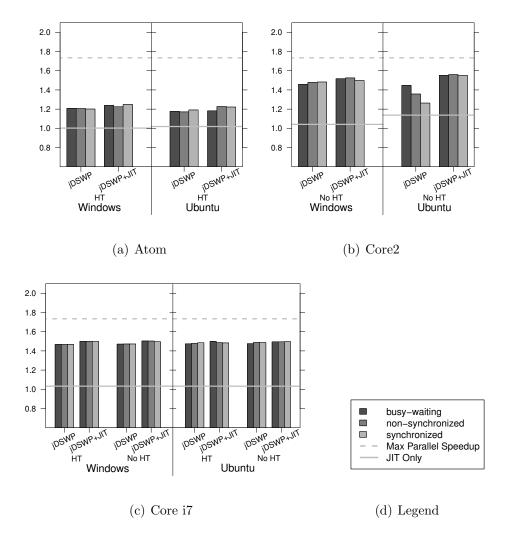

As contribuições desta Tese em DSWP (Capítulo 5) foram feitas usando Java em processadores de prateleira. A fila de comunicação, indisponível nos ambientes de teste, foi simulada em *software* usando diversas estratégias de sincronização. Contudo, os resultados mostraram que as diferentes estratégias não influenciam diretamente o desempenho da aplicação. Em média, o aumento no desempenho das aplicações chegou à 48%. Os problemas encontrados durante estes experimentos foram abordados no próximo trabalho.

Grande parte dos problemas oriundos da paralelização de código sequencial emergem de acessos à memória: a dificuldade de determinar, incontestavelmente, se duas instruções que acessam a memória endereçam posições distintas limita as possibilidades de otimização. Além disso, a dificuldade em determinar se um conflito ocorreu (bem como recuperar o estado do programa na eventualidade de um conflito) orientaram o estudo do Capítulo 6.

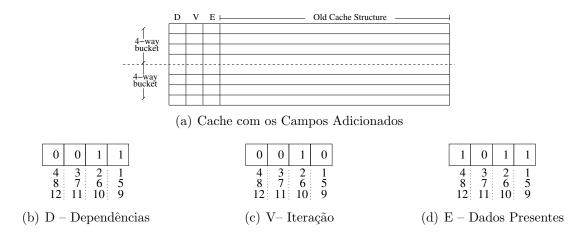

Como resultado, propõe-se ali um esquema de consistência de memória, baseado em versionamento automático de dados nas *caches* dos processadores, e construído sobre o protocolo de coerência de *cache* existente, sem alterações no mesmo. Alguns *bits* extras são adicionados à *cache*, conforme ilustrado na Figura 1.8(a).

Os bits extra compõem três tags, cada uma com uma função distinta, cooperando para manter a consistência em programas paralelizados (ou, ao menos, detectando violações da semântica do programa sequencial). A lógica para gerenciar estas tags foi cuidadosamente elaborada para ser simples e eficiente.

Na arquitetura proposta, cada iteração de laços paralelizados é representada univocamente por um único bit. Para evitar a necessidade de grandes campos na cache (e nas

mensagens de coerência), a arquitetura proposta limita a quantidade máxima de iterações ativas ao mesmo tempo. Além disso, utilizar um único bit simplifica a lógica necessária para o versionamento.

D é utilizado para manter as dependências de uma dada linha da cache. Na Figura 1.8(b) a existência de dois bits 1 indica que a linha l atrelada àquele campo é especulativa nas iterações correspondentes aos bits ligados. Quaisquer escritas a l nas iterações indicadas em D indica uma violação da semântica do programa sequencial.

V é utilizado para indicar a qual iteração a linha pertence. Se todos os bits deste campo forem zero, a linha atrelada a tag não é especulativa.

E é utilizado durante as operações do *commit* para evitar que a *cache* seja colocada em um estado inválido com múltiplas entradas para o mesmo endereço da memória. Colateralmente, E evita que a arquitetura proposta necessite de tráfego de rajada durante *commits*.

### 1.3 Principais Contribuições

De forma sucinta, as contribuições desta Tese são:

- Uma nova técnica de gravação de traces de execução de programas;

- Uma representação mais compacta para traces;

- Um algoritmo simples para paralelização de programas Java que, mesmo sem nenhum tipo de suporte específico da *Java Virtual Machine* (JVM), provê bons resultados;

- Uma arquitetura paralela com suporte à paralelização automática de laços sem a necessidade de *profiling*; e

- Uma prova de corretude para a arquitetura proposta sem a necessidade da criação de um protocolo de coerência específico.

### 1.4 Publicações

Durante a realização dos estudos desta Tese, foram publicados ou submetidos, em ordem cronológica, os seguintes trabalhos:

- J. P. Porto, Y. Wu, E. Borin e C. Wang. Compact Trace Trees in Dynamic Binary Optimization. Aplicação de patente no USPTO sob o número # 20100083236.

- J. P. Porto, G. Araujo, Y. Wu, E. Borin e C. Wang. Compact Trace Trees in Dynamic Binary Translators. Em *AMAS-BT 2009: 2<sup>nd</sup> Workshop on Architectural and MicroArchitectural Support for Binary Translation*. Junho de 2009. Austin, Texas, EUA.

- J. P. Porto, G. Araujo, E. Borin e Y. Wu. Trace Execution Automata in Dynamic Binary Translation. Em *AMAS-BT 2010: 3<sup>rd</sup> Workshop on Architectural and MicroArchitectural Support for Binary Translation*. Junho de 2010. St.-Malo, França.

- J. P. Porto, A. Oliveira, G. Araujo e M. Breternitz. Cache-Based Cross-Iteration Coherence for Loop Parallelization. Em *The 23<sup>rd</sup> ACM Symposium on Parallelism in Algorithms and Architectures*. Junho de 2011. San Jose, California, EUA. (Submetido)

- J. P. Porto e G. Araujo. Extending Decoupled Software Pipeline to Parallelize Java Programs. Em Software Practice and Experience. (Submetido)

### 1.5 Organização desta Tese

Antes de descrever a organização do texto, uma pequena nota ao leitor. Esta Tese, em concordância com as normas atuais que regem a pós-graduação da Universidade Estadual de Campinas, possui partes do texto escritas em língua estrangeira, correspondentes a artigos publicados ou submetidos a jornais científicos e conferências internacionais. Ainda de acordo com esta norma, o conteúdo desses textos reproduz fielmente aqueles dos artigos originais. Contudo, a formatação dos mesmos foi adequada para ficar compatível com o estilo do restante desse documento.

O Capítulo 2 lista trabalhos anteriores relacionados à esta Tese. Nele são detalhadas técnicas anteriores de TLS.

O Capítulo 3 inicia a coletânea com o primeiro artigo publicado durante a pesquisa deste trabalho. Nele, descreve-se uma nova técnica ara identificação de *traces*.

Durante os estudos sobre identificação de *traces*, desenvolvemos uma nova forma para representação dos mesmos, que é descrita no Capítulo 4.

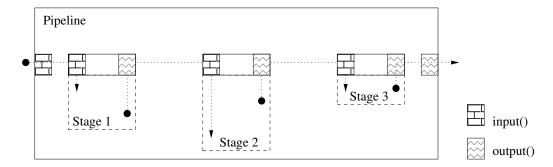

O Capítulo 5 apresenta uma extensão de DSWP para utilização em nível de códigofonte em Java. Nos experimentos realizados, nenhum suporte extra foi adicionado à JVM. O trabalho de paralelização, embora tenha sido feito manualmente, foi de extrema importância para o resultado final desta Tese por ter exposto os problemas intrínsecos à DSWP, em especial os problemas de *alias* de memória. As soluções para os problemas encontrados neste estudo foram úteis para a arquitetura descrita no Capítulo 6.

O Capítulo 6 apresenta a principal contribuição desta tese: uma arquitetura paralela com suporte à execução de código paralelizado utilizando estratégias baseadas no modelo *DOPIPE* [42] de paralelização como DSWP.

As conclusões da Tese são apresentadas no Capítulo 7, que também lista trabalhos futuros possíveis.

O Apêndice A apresenta uma prova de corretude para o mecanismo de coerência utilizado pela arquitetura proposta pelo Capítulo 6. Esta prova utiliza protocolo Modified-Shared-Invalid (MSI) de coerência de cache sem alterações.

# Capítulo 2

### Trabalhos Relacionados

Neste Capítulo, é feita uma revisão dos trabalhos anteriores em *Traces* (Seção 2.1) e em paralelização não-tradicional de laços usando TLS (Seção 2.2). As técnicas de paralelização tradicionais, utilizadas para paralelização de laços regulares, são descritas na Seção 5.2.

#### 2.1 Traces

Ao contrário de TLS, a literatura a respeito de *traces* não é tão extensa e, os trabalhos, não tão diversificados. Ainda assim, como uma importante parte deste trabalho, esta Seção dedica-se a listar alguns trabalhos relacionados detecção e usos de *traces*.

Cifuentes et al. [10] propõem Most Frequently Executed Tail (MFET). Nesta técnica, as arestas do GFC do programa são instrumentadas. MFET também instrumenta as instruções alvos de salto para trás. Quando uma instrução é identificada como "quente", MFET utiliza a informação sobre a frequência de execução das arestas para determinar o trace que deve ser formado.

Duesterwald *et al.* [16] propõem MRET. Assim como MFET, os inícios de *traces* são identificados em instruções que são alvo de saltos para trás. Entretanto, MRET segue o fluxo da execução do programa para determinar o *trace* a ser gravado. A idéia é evitar a custosa instrumentação em todas as arestas do GFC do programa original.

Last Executed Iteration (LEI) [26], proposto por Hiniker et al., procura identificar código quente mais significativo que MRET. Basicamente, a técnica utiliza um buffer com os últimos saltos executados pelo programa. Uma entrada repetida neste buffer indica a detecção de um loop header. Quando este loop header executar mais que um número determinado de vezes, LEI grava a execução do programa até que um ciclo seja formado, ou até que a execução do programa atinja um trace pré-existente.

Como MRET não é seletivo em relação ao caminho escolhido para gerar um trace,

Two-pass MRET (MRET<sup>2</sup>)<sup>2</sup> foi desenvolvida. Como o nome indica, ela é derivada de MRET. Seu funcionamento é bem simples: ao invés de gravar um trace assim que seu código se torna quente, MRET<sup>2</sup> grava um trace potencial, e programa continua a executar código normal. Quando um segundo trace for identificado, MRET<sup>2</sup> faz a intersecção de ambos os traces potenciais. Esta heurística tende a identificar caminhos mais significativos para execução do programa.

Há uma ampla literatura de ambientes de otimização de código baseados em traces. Por exemplo, Baraz et al. [6] introduz IA32-EL, um tradutor binário dinâmico que traduz código x86 para execução em sistemas Itanium (R). Este tradutor otimizante mostrou um desempenho superior à solução inicialmente empregada (i.e., uso de um núcleo de um processador 386 para execução nativa de código x86). Este ganho de desempenho somente foi possível pois IA32-EL identificava traces de execução, armazenando-os em uma trace cache para posterior otimização.

Dehnert et al. [15] descreve Code Morphing Software (CMS), a grande novidade da Transmeta em seus processadores: ao invés de manter a compatibilidade com x86 em hardware, uma camada de software (a CMS) foi utilizada. Desta forma, os engenheiros do processador se viram livres das idiossincrasias de x86. CMS também mantém os traces descobertos em uma trace cache, focando maior esforço de otimização nos traces mais executados.

Digital FX!32, proposto por Hookway [27], é um subsistema presente nos sistemas operacionais Windows NT 4.0 em sistemas Alpha para execução de aplicações x86 sem a necessidade de recompilação para a nova arquitetura. Diferentemente dos trabalhos anteriores, FX!32 inicialmente *interpretava* as aplicações, instrumentando o código executado. A otimização dos códigos mais executados era feita *offline*. As unidades de otimização eram *traces* de execução.

Gal et al. [17] propõem TraceMonkey, um compilador dinâmico para JavaScript que emprega TT para identificar código quente em aplicações Web. Compilar JavaScript para execução nativa é extremamente interessante, haja vista a quantidade de código JavaScript disponível que pode beneficiar-se direta e automaticamente da compilação.

Em comum, todos estes trabalhos não identificam oportunidades de paralelização de código em nível de *threads*, optimizando, contudo, o código com otimizações tradicionais, tais quais Eliminação de Subexpressões Comuns (ESC) e Eliminação de Código Morto (ECM) [1,39].

<sup>&</sup>lt;sup>2</sup>USPTO #20070079293

## 2.2 Thread-Level Speculation

Laços irregulares requerem técnicas mais poderosas de paralelização. Além da informação estática sobre o código, estas técnicas requerem informações sobre a execução dos programas. Usualmente, tais informações são obtidas com o emprego de instrumentação. Entretanto, outros meios podem ser utilizados, tal como anotação do código-fonte. A seguir, uma seleção de trabalhos anteriores em TLS.

- Akkary et al. [2]: Uma interessante abordagem em hardware para TLS, que quebra um programa sequencial em threads automaticamente. Para isso, o hardware procura agressivamente por laços e chamadas de função que são usados para delimitar o início de uma nova thread. Como estas são criadas antes dos valores de entrada (live-in) estarem prontos, os autores propõe um esquema de predição de valores. Eles também provêm e explicam o suporte para falhas de especulação.

- Checkpoint Processing and Recovery (CPR) [3] e, posteriormente, Continual Flow Pipeline (CFP) [57], introduzem micro-arquiteturas que são capazes de terminar (em inglês, retire) instruções fora da ordem original do programa. Para tanto, os autores introduzem novas estruturas nos processadores. Ambos os modelos baseiam a execução no processamento de checkpoints. Estas micro-arquiteturas, no entanto, apresentam elevado consumo de energia, inviabilizando-as. Hilton et al. [25], propõe o uso do modelo de execução de processamento de checkpoints em processadores in-order como forma de amenizar o custo de instruções de acesso à memória.

- Balakrishnam et al. [5]: os autores propõem a multiplexação de um programa pelo compilador e a demultiplexação pelo processador. Neste esquema, o compilador determina, estaticamente, a relação de dependência entre métodos e funções de um programa e expõe esta informação para o processador. Para executar o programa, o hardware executa as funções que tem todas as suas dependências satisfeitas. A medida que as funções terminam, novas dependências são satisfeitas e, assim, novas funções estão aptas para serem executadas.

- Bhowmik et al. [7]: Este trabalho descreve um compilador (baseado no compilador SUIF [66]) que faz a decomposição de um programa sequencial em threads. Para tanto, o compilador utiliza heurísticas e informações obtidas com instrumentação. A avaliação experimental do compilador foi feita com um simulador que executa traces de execução e, aparentemente, nenhum suporte especial em hardware foi necessário para execução do código paralelo.

- Bridges et al. [8] discorre sobre a necessidade de especulação para que técnicas automáticas de paralelização consigam efetivamente extrair paralelismo de aplicações irregulares. Após uma pequena revisão de DSWP os autores apresentam duas anotações de código que estendem a semântica de estruturas sequenciais de linguagens de programação tradicionais. A primeira anotação (@YBRANCH) indica saltos condicionais (i.e., ifs em linguagens de programação) não-determinísticos. Esta anotação indica ao compilador que o código protegido pela condição (i.e., o corpo do if) pode ser executado independente do resultado da condição. Esta anotação inclui também a probabilidade com que o corpo do if deve ser executado. A segunda anotação (@Commutative) é utilizada para anotar funções cuja ordem de invocação no programa paralelo não precise ser idêntica à ordem do programa sequencial (funções de alocação de memória são, em teoria, comutativas).

- Bulk [9, 62]: estes artigos descrevem uma maneira simples de verificar se um programa paralelizado viola a consistência sequencial durante a sua execução. Para detectar tais violações, os autores propõem um esquema baseado em assinaturas dos endereços de memória atualizados por cada uma das threads. Além das assinaturas, um esquema de checkpoint dos registradores é utilizado de modo a ser possível a restauração do estado correto da aplicação em resposta a detecção de conflitos. Nenhum suporte de software é proposto.

- Cintra et al. [11]: este trabalho propõe uma arquitetura escalável para TLS. Os autores criam seu próprio protocolo de coerência de cache para esta arquitetura. Além disso, as operações de commit e squash são potencialmente lentas: a primeira faz invalidação em rajada (burst-invalidate) de todos os dados quando do final de uma thread, enquanto a segunda força a sincronização dos processadores que executam a aplicação. Além disso, como os dados são invalidados ao término de uma thread, a cache do sistema ficará potencialmente fria.

- Collins et al. [12] propõe o uso de TLS para realização de pré-busca (pre-fetching) de loads "delinquentes". Um load é delinquente se é responsável por grande parte das faltas no acesso à cache (em inglês, cache miss). Em outras palavras, este load não é facilmente predito pelos mecanismos usuais de pré-busca. Para a avaliação, os autores implementaram um compilador que, identificando um load delinquente, emite código para a criação da thread responsável pela pré-busca dos dados. Algum suporte de hardware também é necessário. Assim, os autores utilizaram um simulador baseado em SMTSIM [63]. Os resultados mostram que eliminar os lo-ads delinquentes é equivalente ao aumento de desempenho obtido pela utilização de

memória penalidade de falha igual a zero (no original, zero-miss-penalty memories).

- Sohi et al. propõe um modelo de execução hierárquica, o Wisconsin Multiscalar [56]. Neste modelo, o fluxo dinâmico das instruções é partido em tarefas (tasks). Para isso, um hardware especializado prediz qual a próxima tarefa a ser executada e inicia sua execução em algum processador livre. Esta predição pode falhar, levando ao cancelamento de tarefas (task squashing) disparadas especulativamente. Neste modelo, a tarefa mais antiga (i.e., criada antes de todas as outras tarefas executando no sistema) é dita não especulativa e sempre termina. Neste contexto, Gopal et al. propõe Speculative Versioning Cache (SVC) [20], que é um tipo de cache versionada coerente. Organizado de maneira similar às caches em processadores Symmetric MultiProcessors (SMP), SVC detecta acessos à memória que violem a semântica do programa sequencial. SVC depende de um mecanismo centralizado que faz a busca em uma lista de dados sempre que há uma falha de leitura à cache ou um acerto de leitura (em inglês, cache hit) a um dado não especulativo.

- Hydra CMP: Hammond et al. [21] descreve o processador SMP Hydra, que é composto por quatro processadores MIPS. Além da cache privativa, Hydra provê também uma grande cache compartilhada por todos os processadores. Fazendo a interligação dos processadores com a cache compartilhada e com o restante do sistema (e.g., controlador de memória, controladores de Entrada e Saída (E/S) etc) existe um barramento largo o suficiente para acomodar um linha inteira de cache. Existe, ainda, um barramento mais estreito utilizado tanto para fazer atualizações no nível compartilhado da cache como para invalidar as cópias da linha sendo escrita nos outros processadores. A arquitetura Hydra também oferece suporte à TLS adicionando hardware especializados para tal, tanto nos núcleos como fora deles.

- Thread-Level Data Speculation (TLDS) é proposto por Steffan et al. [58] como um subterfúgio para aumentar a eficiência de TLS. Neste trabalho, os autores evitam anti-dependências (Write After Read (WAR) e Write After Write (WAW)) forçando os dados escritos especulativamente a residirem no primeiro nível da cache, o que limita a quantidade de dados escritos em modo especulativo. A detecção de conflitos Read After Write (RAW) é feita quando da escrita de um dado em modo especulativo simplesmente anexando (em inglês piggybacking) informações suficientes nas mensagens do protocolo de coerência. Um suporte para Hydra similar foi proposto por Hammond et al. [22] que adicionou a passagem (forwarding) automática de dados entre threads especulativas, além de algumas melhorias como a ausência de tráfego de rajada (burst traffic) ao término de threads especulativas. Apesar disso, o suporte

descrito para Hydra requer um sofisticado suporte em hardware.

- Johnson et al. [30] propõe um algoritmo para o particionamento de um programa sequencial em threads. O algoritmo proposto opera em nível de blocos básicos, utilizando informações estáticas e dinâmicas, estas obtidas com instrumentação, tentando maximizar a quantidade de paralelismo que é exposta ao hardware, que deve obrigatoriamente oferecer suporte à especulação, utilizando uma série de parâmetros tais quais o tamanho das threads geradas, o desbalanceamento de carga (no original, load imbalance) e a possibilidade de gerar cancelamentos por causa do escalonamento.

- Alchemist [67] é um ambiente de instrumentação que identifica dinamicamente candidatos a pré-cômputo. Por exemplo, um comando if que execute após um comando while e não dependa deste pode ser executado em paralelo com o mesmo. Apesar de identificar os candidatos ao pré-cômputo, Alchemist não faz a paralelização automaticamente, ficando a cargo do programador acatar ou não a sugestão do ambiente. Um estudo mais detalhado de pré-cômputo é feito em [32] por Kim et al.. Neste trabalho, os autores analisam diversos algoritmos em diversos compiladores. Este trabalho requer um suporte minimo do hardware para a criação das threads, e não requer nenhum suporte para consistência.

- Krishnan et al. [34,35] propõe neste artigo um sistema no qual o compilador é responsável por anotar o código binário com informações sobre o início e o fim de regiões as quais devem ser paralelizadas pelo hardware em tempo de execução. Diferentemente de grande parte dos trabalho que dependem de um compilador, neste os autores analisam o código binário, e não o código-fonte da aplicação, o que torna esta proposta uma alternativa para paralelização de código legado. O trabalho foca na paralelização de laços internos e o hardware é responsável por criar as threads para executar especulativamente iterações sucessivas de tais laços. As dependências de registradores são honradas pelo processador com o uso de um hardware específico chamado synchronizing scoreboard. As dependências dinâmicas são tratadas por uma tabela chamada Memory Disambiguation Table (MDT) que está localizada junto ao último nível da hierarquia de cache.

- Madrilles et al. propõe Anaphase [36] como outra solução para suporte à execução especulativa de threads. Este estudo focou no agrupamento de dois núcleos que podem operar de maneira independente ou cooperativa. Para o modo cooperativo, alguns bits são adicionados ao primeiro e ao segundo nível (que é compartilhado) da cache. Além deste suporte, o artigo introduz o módulo de coerência de memória entre

núcleos (*Inter-Core Memory Coherence* (ICMC)). Este módulo é responsável por garantir que as atualizações à memória ocorram da mesma forma como ocorreriam se o programa fosse executado sequencialmente. O conjunto de dois núcleos, uma memória *cache* compartilhada e um ICMC formam um *tile*. Neste artigo os autores apresentam uma estimativa da área necessária para implementar o sistema proposto.

- Marcuello et al. [37]: outra alternativa que depende unicamente do hardware para paralelizar programas sequenciais. Como a maioria dos estudos de TLS, este foca em laços, que não necessariamente são os laços internos de um programa. Como outras abordagens exclusivamente em hardware, este trabalho faz especulação do fluxo de controle para geração das threads, bem como para as dependências de dados. Aquelas são feitas baseadas na observação de que a maior parte das iterações tende a seguir o mesmo caminho dentro de um laço, enquanto estas são tratadas com o uso de uma tabela para predição de valores.

- Marcuello et al. [38]: Neste artigo, os autores apresentam uma alternativa para a criação de threads para especulação. Os resultados experimentais mostram que o sistema proposto (baseado em instrumentação) é mais eficiente que as heurísticas tradicionais, que usualmente criam threads para executar iterações, continuação de laços ou de subrotinas. Uma outra avaliação feita mostra que os preditores de valor não precisam de esquemas elaborados caso o número de threads a serem criadas não seja grande.

- Pinot [40]: os autores propõem uma arquitetura para execução especulativa de threads que conecta os núcleos do processador utilizando uma conexão em anel. Este design foi escolhido pela simplicidade de implementação da rede em anel, bem como pela alta velocidade que ela proporciona para a transferência de dados entre núcleos. Esta eficiência na transferência de dados entre núcleos adjacentes é útil neste modelo de execução, no qual cada thread cria um única outra thread para adiantar a computação que seria executada na sua continuação. Também é descrito um suporte em hardware para versionamento de memória como forma de aumentar o suporte a várias granularidades de TLP. Para criar as threads antes de serem necessárias o hardware faz predição de fluxo de controle. O hardware não é responsável por extrair as threads: um otimizador offline, com base em informações de instrumentação, delimita as threads no código do programa.

- Prvulovic et al. [47] analisa as ineficiências de arquiteturas com suporte a execução especulativa de threads e determinam que o custo de fazer commit, o esgotamento

de espaço para armazenar dados especulativos e o tráfego de coerência gerado pela especulação juntos dominam o custo de executar código especulativo. Para o primeiro gargalo é proposta uma solução que permite ao commit não escoar os dados especulativos para memória. Para o segundo gargalo (esgotamento de espaço para dados especulativos) é proposta uma solução que permite que uma região da memória principal seja utilizada como área de escape que pode ser redimensionada caso haja necessidade. Por fim, para contornar o excesso de mensagens de coerência devido à especulação, é proposta uma alteração no protocolo de coerência da cache que permita ao processador identificar linhas de cache que não precisam de coerência fina, diminuindo assim a quantidade de mensagens geradas pelo acesso a tais linhas.

- Compilador Mitosis (Quiñones et al.) [48]: quando da criação de uma thread, a maior parte das arquiteturas com suporte à TLS provê algum tipo de suporte em hardware para materialização dos valores iniciais dos registradores do processador que executará a nova thread. Neste artigo, os autores propõem que esta geração seja feita por p-slices uma ou mais instruções que efetivamente calculam o valor dos registradores vivos. Este código de prólogo pode facilmente negar os benefícios oriundos da paralelização. Para evitar que isso ocorra, os autores propõem heurísticas para otimizar as p-slices. O commit ocorre quando a thread não-especulativa atinge o início de uma thread especulativa. Neste ponto, o estado não especulativo é comparado com o estado predito e, caso sejam idênticos, a thread não-especulativa termina e a thread especulativa torna-se não-especulativa. Caso os estados sejam distintos, a thread especulativa e todas as threads por ela geradas são canceladas e a thread não especulativa continua a execução do programa, criando novas threads quando necessário.

- Raman et al. [49] propõe SMTx como forma viabilizar DSWP em processadores atuais. Os autores propõem o uso do sistema de memória virtual dos processadores atuais como forma de garantir que, no evento de uma falha de especulação, seja possível restaurar o estado correto do programa sequencial. Entretanto, esta estratégia ainda depende de informações de instrumentação para funcionar corretamente: cabe ao compilador identificar as dependências entre os estágios do pipeline.

- Renau et al. [54]: TLS surgiu como uma alternativa aos processadores superescalares. A existência de múltiplos núcleos em um mesmo processador possibilita que técnicas agressivas de otimização sejam empregadas para aumentar o desempenho de aplicações. Entretanto, todo o suporte necessário para execução correta de TLS era visto como algo que poderia consumir uma grande quantidade de energia

se implementado. Contrariando o esperado, os autores mostram que, com algumas otimizações em *software* e *hardware*, TLS pode ser eficiente em termos de consumo de energia. O estudo também aponta algumas ineficiências inerentes à estilos de projeto de sistemas com suporte à TLS para os arquitetos (e micro-arquitetos) de *hardware* evitem-los.

- Steffan et al. [59] faz uma proposta de hardware para TLS que diz ser escalável. O esquema proposto é um composto de processadores que estão interligados através de barramentos e de uma cache compartilhada. Apenas as iterações de laços são paralelizadas, de modo que a execução do código paralelo ocorre de forma semelhante à execução paralela de um laço DOALL, exceto que, neste caso, podem haver dependências entre as iterações, dependências estas que são honradas pelo hardware em tempo de execução. A coerência entre as iterações é mantida por um protocolo baseado em Modified Exclusive Shared Invalid (MESI), mas com extensões para o suporte à especulação. Contrariando o dito em [47], esta proposta necessita do tráfego de rajada para fazer commits e squashs, de modo que estas operações tendem a ser um fator limitante muito severo no desempenho geral do sistema.