| ESTE EXEMPLAR CORRESPONDE A REDAÇÃO FINAL DA  |

|-----------------------------------------------|

| TESE DEFENDIDA POR Danilo Morais              |

| Pagane E APROVADA                             |

| PELA COMISSÃO JULGADORA EM 28. 1. 02 1. 20 12 |

| ORIENTADOR                                    |

| ORIENTADOR                                    |

UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA MECÂNICA COMISSÃO DE PÓS-GRADUAÇÃO EM ENGENHARIA MECÂNICA

Danilo Morais Pagano

# Proposta de uma arquitetura de processamento de sinais utilizando FPGA

#### Danilo Morais Pagano

# Proposta de uma arquitetura de processamento de sinais utilizando FPGA

Dissertação apresentada ao Curso de Mestrado da Faculdade de Engenharia Mecânica da Universidade Estadual de Campinas, como requisito para a obtenção do título de Mestre em Engenharia Mecânica.

Área de Concentração: Mecânica dos Sólidos e Projetos Mecânicos

Orientador: Prof. Dr. Eurípedes Guilherme de Oliveira Nóbrega

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA E ARQUITETURA - BAE - UNICAMP

Pagano, Danilo Morais

P14p

Proposta de uma arquitetura de processamento de sinais utilizando FPGA / Danilo Morais Pagano – Campinas, SP: [s.n.], 2012.

Orientador: Eurípedes Guilherme de Oliveira Nóbrega.

Dissertação de Mestrado – Universidade Estadual de Campinas, Faculdade de Engenharia Mecânica.

1. Processamento de sinais - Tecnicas digitais.. 2. Fourier, Transformada de.. 3. FPGA. I. Nóbrega, Euripedes Guilherme de Oliveira. II. Universidade Estadual de Campinas. Faculdade de Engenharia Mecânica. III. Título.

Título em Inglês: Proposal to an architecture for signal

processing using FPGA

Palavras-Chave em Inglês: Digital signal processing; Fourier

Transform; FPGA.

Área de Concentração: Mecânica dos Sólidos e Projetos Mecâ-

nicos

Titulação: Mestre em Engenharia Mecânica

Banca Examinadora: Peter Jürgen Tatsch e Luis Otávio Sa-

raiva Ferreira.

Data da Defesa: 28/02/2012

Programa de Pós-Graduação: Engenharia Mecânica

# UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA MECÂNICA COMISSÃO DE PÓS-GRADUAÇÃO EM ENGENHARIA MECÂNICA DEPARTAMENTO DE MECÂNICA COMPUTACIONAL

### DISSERTAÇÃO DE MESTRADO

# Proposta de uma arquitetura de processamento de sinais utilizando FPGA

Autor: Danilo Morais Pagano

Orientador: Prof. Dr. Eurípedes Guilherme de Oliveira Nóbrega

A Banca Examinadora composta pelos membros abaixo aprovou esta Dissertação:

Prof. Dr. Eurípedes Guilherme de Oliveira Nóbrega, Presidente

Euri Lu Distin

Universidade Estadual de Campinas

Peter Singer Gola.

Prof. Dr. Peter Jürgen Tatsch

Universidade Estadual de Campinas

Prof. Dr. Luis Otávio Saraiva Ferreira Universidade Estadual de Campinas Aos meus pais, minhas irmãs, minha namorada e meus amigos.

#### **AGRADECIMENTOS**

Agradeço inicialmente a Deus por ter me guiado durante esta fase de minha vida, oferecendome forças para seguir em frente sem desistir.

Aos meus pais, Donizeti dos Santos Pagano e Rosimeiry P. de Morais Pagano pelo apoio e incentivo, sempre me fortalecendo e amparando nos momentos difíceis.

Às minhas irmãs, Lívia e Letícia, que sempre estiveram ao meu lado e me tiveram como um exemplo a ser seguido.

À minha namorada, Daiana Bueno, pela compreensão, paciência e apoio, contribuindo enormemente para a realização deste trabalho.

Ao meu orientador, Prof. Dr. Eurípedes Guilherme de Oliveira Nóbrega, que me aceitou como aluno de mestrado, acreditou e confiou no meu trabalho, conduzindo-me pelos melhores caminhos a serem seguidos.

A todos os professores que participaram desta minha caminhada, sempre dispostos a ajudar, transferindo o conhecimento e auxiliando na minha formação.

A todos os meus amigos pelo incentivo, auxílio e companheirismo, principalmente aos colegas do departamento que também contribuíram com ideias, palpites e discussões.

À Biosensor Ind. e Com. LTDA pelo apoio financeiro e pela confiança depositada no meu trabalho.

A grandeza não consiste em receber honras, mas em merecê-las. Aristóteles

#### **RESUMO**

Esta dissertação apresenta um sistema para processamento digital de sinais através de dispositivos de hardware reconfigurável. Uma implementação do algoritmo FFT foi adotada como meio para avaliar o desempenho da arquitetura proposta para o sistema. O processamento digital de sinais tradicionalmente tem um alto custo computacional, pois os algoritmos são implementados em software, o que pode não atender as restrições de tempo de aplicações reais. O objetivo principal deste trabalho é desenvolver uma arquitetura para adquirir os sinais através de módulos de aquisição de dados distribuídos em uma rede e processá-los usando um FPGA. Um microcontrolador da FreeScale Semiconductors® foi adotado como módulo de aquisição de dados, executando um sistema operacional de tempo real (RTOS) para garantir os requisitos temporais. Foi implementado o processador soft-core NIOS 2 da Altera® executando também um RTOS com recursos de comunicação em rede, incluindo um periférico escrito em VHDL para o processamento da FFT usando uma estrutura de *pipeline* baseada em estágios e comunicação direta ao barramento do processador. A versão em hardware do algoritmo obteve uma redução de até 2000 vezes no tempo de processamento da FFT comparado com a mesma versão implementada em software, alcançando um tempo de processamento de 3.9 microssegundos para sinais discretizados em 256 pontos, quando usado 100MHz de clock. A quantidade de pontos pode ser facilmente aumentada alterando-se apenas o núcleo do periférico desenvolvido, e os resultados permitem adotar a arquitetura proposta para aplicações em tempo real de processamento digital de sinais.

Palavras-Chave: Processamento de sinais - Tecnicas digitais.; Fourier, Transformada de.; FPGA.

**ABSTRACT**

This work presents a digital signal processing system based on reconfigurable hardware. Im-

plementation of the FFT algorithm is used as a mean to assess the adopted configuration per-

formance. Digital signal processing algorithms are in general software implemented, incurring

high computational cost, which may not attend the real-time constraints of real applications. The

main objective of this work is to develop an FPGA based architecture to process signals acqui-

red through a distributed network of data acquisition modules. A microcontroller from FreeScale

Semiconductors® was adopted as data acquisition module, running a real-time operating system

(RTOS) to guarantee timing requirements. The soft-core processor NIOS 2 from Altera<sup>®</sup>, also run-

ning an RTOS with network communication capabilities, was implemented including a peripheral

module written in VHDL for the computation of the FFT, which uses a pipeline-based stage struc-

ture and directly communicates with the processor bus. The hardware version of the algorithm

achieved a reduction up to 2000 times in the FFT processing time compared to the same version

implemented in software, reaching a processing time of 3.9 microseconds for 256 points sampled

signals when using 100MHz of clock. The number of points can be easily increased just changing

the core of the developed peripheral module, and the results permit to expect adequate real-time

application of digital signal processing adopting the proposed configuration.

**Keywords**: Digital signal processing; Fourier Transform; FPGA.

viii

## LISTA DE FIGURAS

| 1.1  | Processador NIOS 2 no reconhecimento de folhas                                            | 3  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Processador NIOS 2 no reconhecimento de pessoas.                                          | 4  |

| 1.3  | Projeto de <i>hardware</i> do filtro digital de imagens                                   | 5  |

| 1.4  | Projeto de <i>hardware</i> do leitor de cartões                                           | 6  |

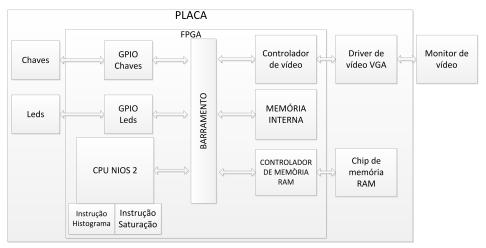

| 1.5  | Diagrama de blocos do processador com instruções personalizadas                           | 7  |

| 1.6  | Processador multi-núcleos desenvolvido.                                                   | 7  |

| 1.7  | Projeto de <i>hardware</i> do sistema de aquisição de dados                               | 8  |

| 1.8  | Projeto de <i>hardware</i> simplificado do sistema de reconhecimento da fala              | 9  |

| 1.9  | Diagrama de blocos simplificado do processador                                            | 10 |

| 2.1  | Histórico do surgimento e utilização de tecnologias de construção de circuitos integra-   |    |

|      | dos. A parte branca indica que apesar da tecnologia estar disponível, ela ainda não tinha |    |

|      | sido recebida com entusiasmo pelos profissionais do setor.                                | 14 |

| 2.2  | Estrutura interna de um FPGA                                                              | 17 |

| 2.3  | Níveis de abstração em linguagens de descrição de <i>hardware</i>                         | 19 |

| 2.4  | Exemplo de projeto em VHDL                                                                | 20 |

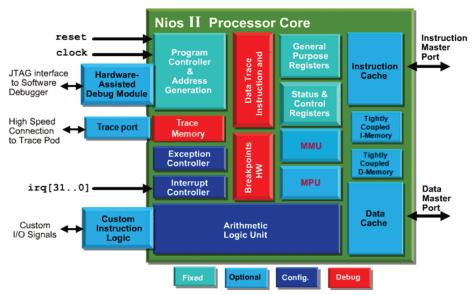

| 2.5  | Estrutura interna do soft-core NIOS2.                                                     | 24 |

| 2.6  | Barramento Avalon <i>Memory Map</i> e seus módulos internos                               | 26 |

| 2.7  | Comando de leitura e de escrita de dados em uma interface Avalon MM                       | 26 |

| 2.8  | Transmissão de dados através da interface Avalon ST                                       | 27 |

| 2.9  | Kit de desenvolvimento NEEK                                                               | 28 |

| 2.10 | Periféricos do kit de desenvolvimento NEEK                                                | 29 |

| 2.11 | Microcontrolador MCF51CN128                                                               | 30 |

| 2.12 | Kit de desenvolvimento TOWER.                                                             | 31 |

| 2.13 | Conceitos básicos de um sistema operacional                                               | 34 |

| 2.14 | Componentes do núcleo e componentes adicionais do MQX                                     | 36 |

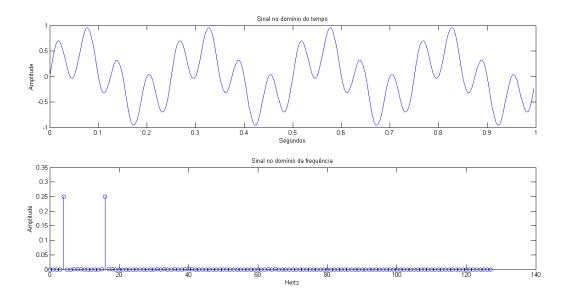

| 2.15 | Sinal representado no domínio do tempo e no domínio da frequência                         | 41 |

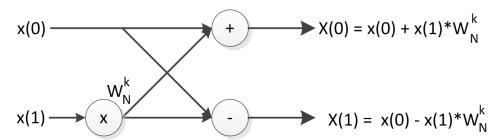

| 2 16 | Operação horboleta                                                                        | 44 |

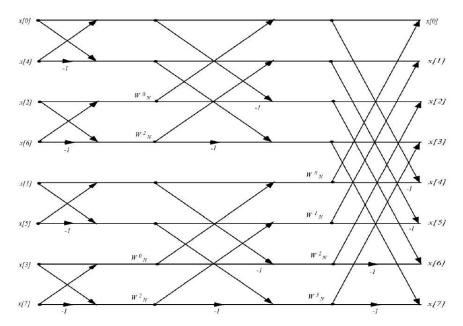

| 2.17 | Etapas do algoritmo FFT DIT                                                       | 45 |

|------|-----------------------------------------------------------------------------------|----|

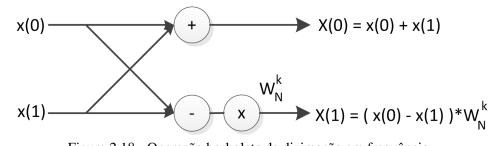

| 2.18 | Operação borboleta da dizimação em frequência                                     | 47 |

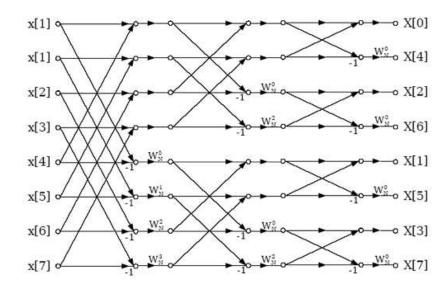

| 2.19 | Etapas do algoritmo FFT DIF para um sinal de 8 pontos                             | 47 |

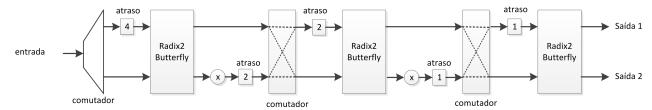

| 2.20 | Exemplo do algoritmo R2MDC com 8 pontos                                           | 49 |

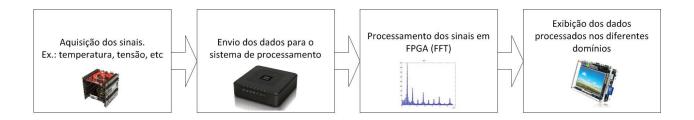

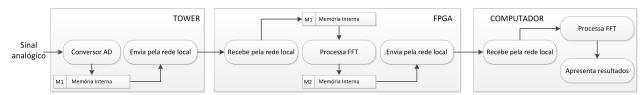

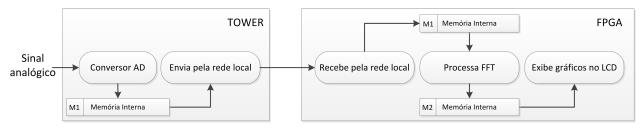

| 3.1  | Funcionamento do sistema: da aquisição à visualização.                            | 52 |

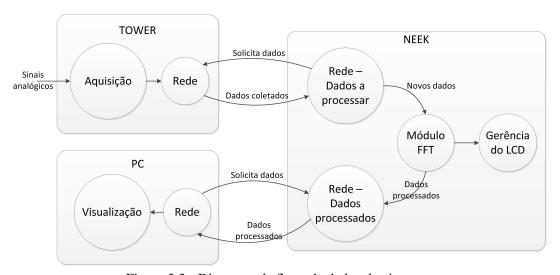

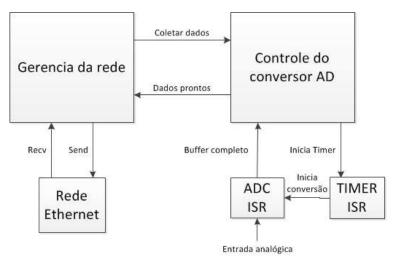

| 3.2  | Estrutura do sistema de aquisição em rede                                         | 52 |

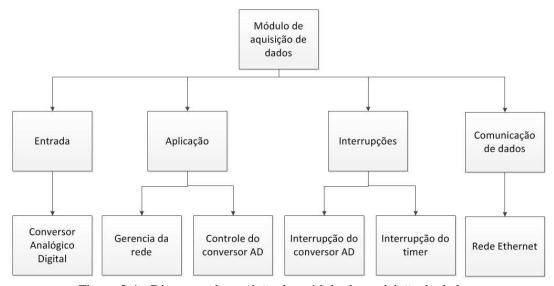

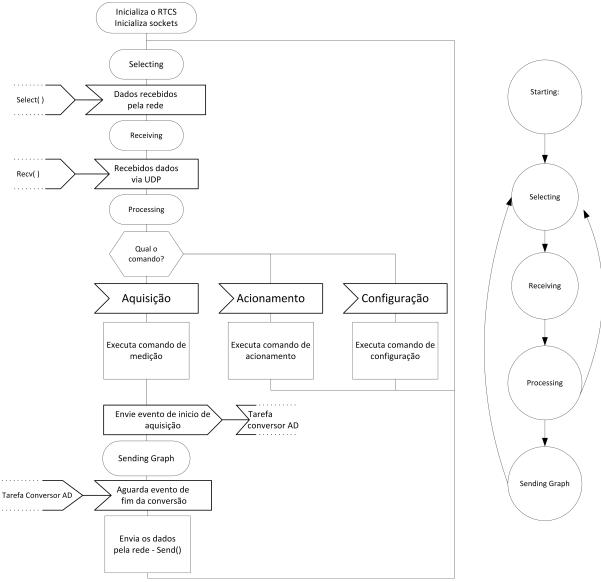

| 3.3  | Diagrama de fluxo de dados do sistema.                                            | 53 |

| 3.4  | Diagrama de partição do módulo de aquisição de dados                              | 54 |

| 3.5  | Diagrama de interação do módulo de aquisição de dados                             | 55 |

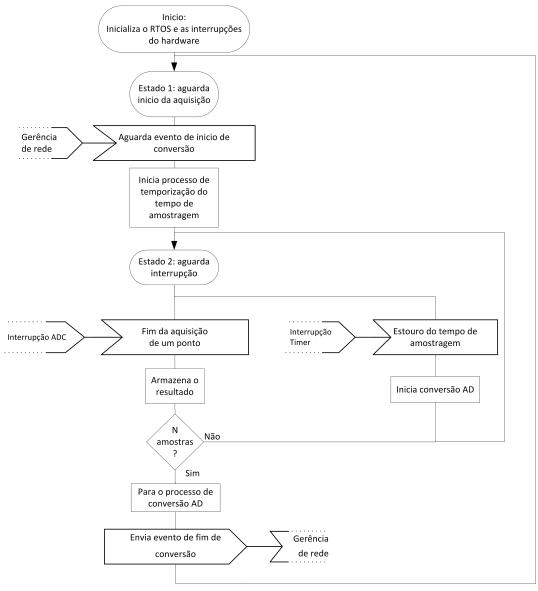

| 3.6  | Diagrama de estados SDL da tarefa de controle do conversor AD                     | 56 |

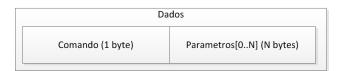

| 3.7  | Formato do comando enviado do NEEK para o TOWER                                   | 57 |

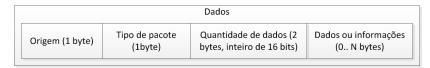

| 3.8  | Formato da resposta enviada do TOWER ao NEEK.                                     | 57 |

| 3.9  | Diagrama de estados SDL da tarefa de monitoramento da rede e diagrama de estados  |    |

|      | simplificados                                                                     | 58 |

| 3.10 | Diagrama de sequência do módulo de aquisição de dados                             | 59 |

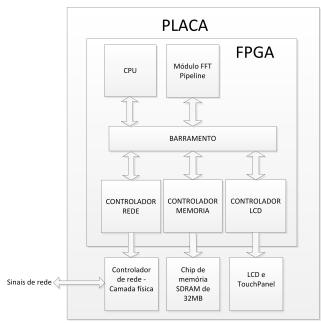

| 3.11 | Placa do NEEK com o processador desenvolvido e os periféricos externos ao FPGA de |    |

|      | forma simplificada                                                                | 60 |

| 3.12 | Organização do <i>software</i> desenvolvido                                       | 61 |

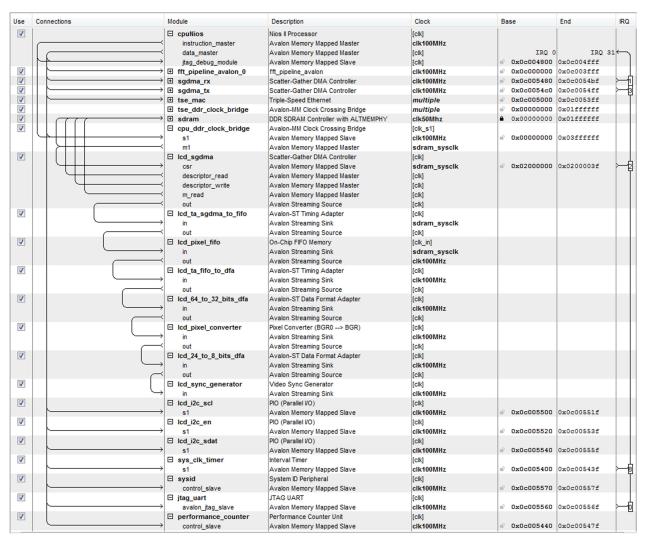

| 3.13 | Janela do SoPC Builder com o processador construído                               | 62 |

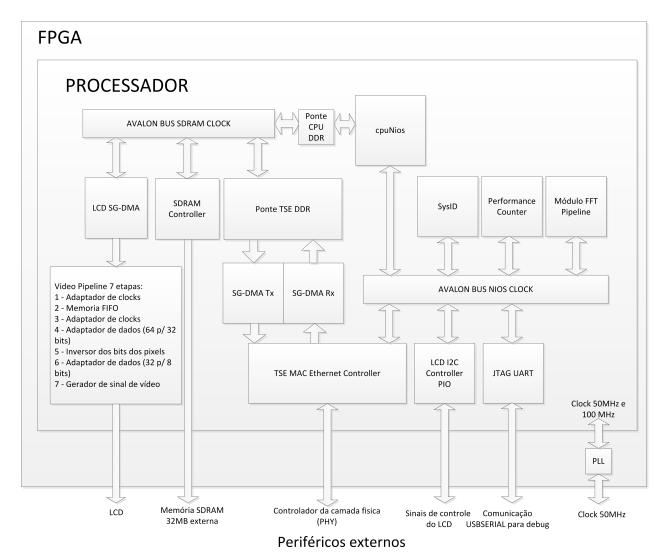

| 3.14 | Diagrama de blocos do processador desenvolvido                                    | 63 |

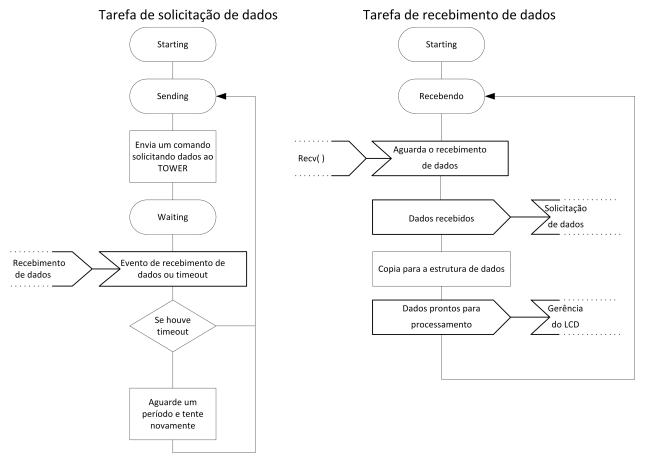

| 3.15 | Tarefas do módulo de comunicação                                                  | 66 |

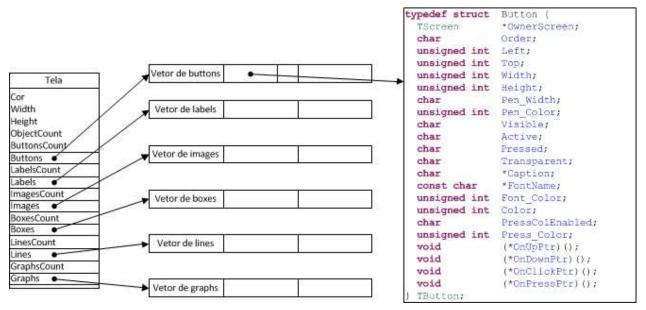

| 3.16 | Estrutura de dados da tela e de um botão.                                         | 67 |

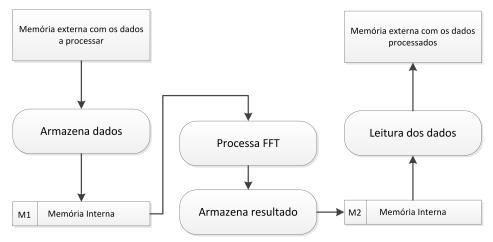

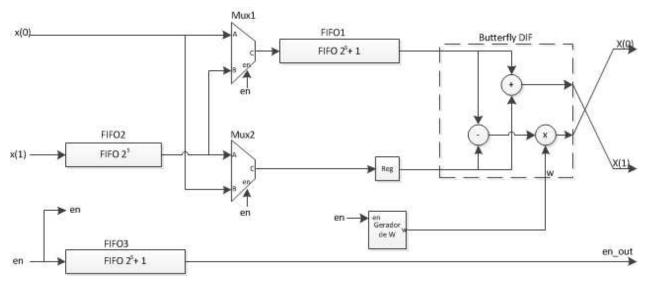

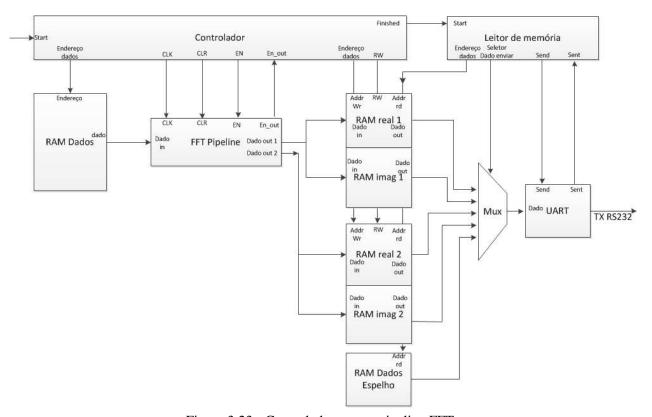

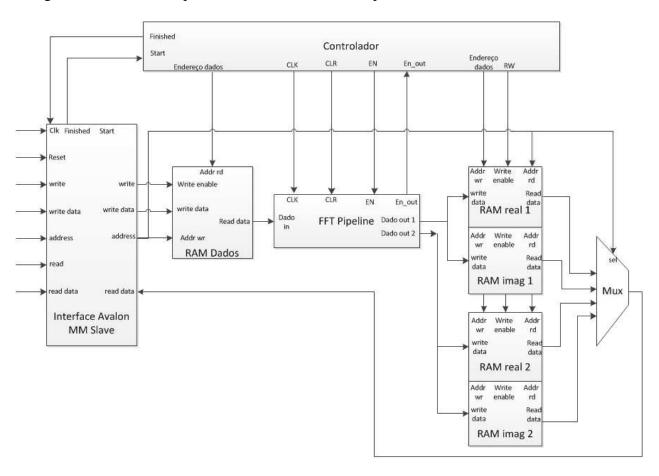

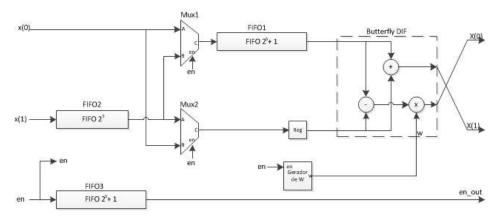

| 3.17 | Diagrama do fluxo de dados no módulo em desenvolvimento.                          | 70 |

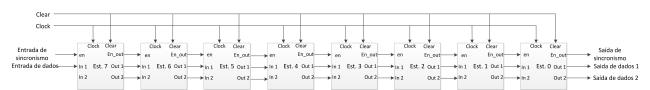

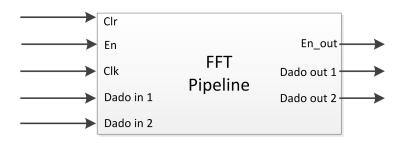

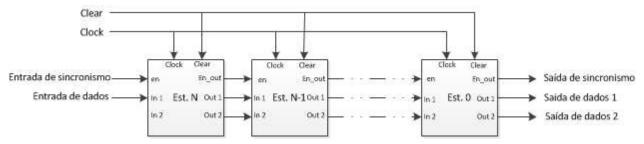

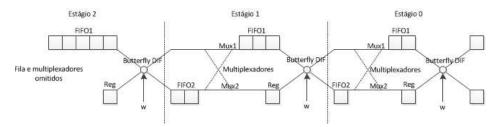

| 3.18 | Fluxo de dados em um pipeline de 8 estágios                                       | 70 |

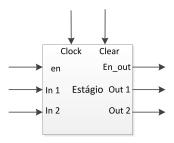

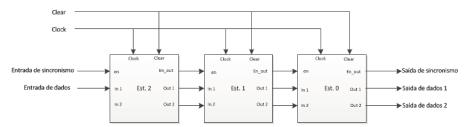

| 3.19 | Entradas e saídas de um estágio                                                   | 71 |

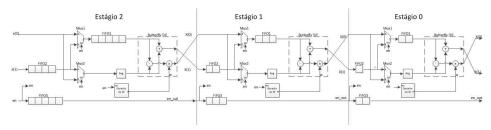

| 3.20 | Detalhamento da estrutura interna de um estágio                                   | 71 |

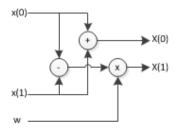

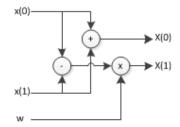

| 3.21 | Operação borboleta no algoritmo DIF                                               | 73 |

| 3.22 | Sinais de entrada e saída do pipeline.                                            | 73 |

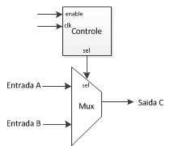

| 3.23 | Controlador para o pipeline FFT                                                   | 74 |

| 3.24 | Controlador para o pipeline FFT                                                   | 77 |

| 3.25 | Tela de configuração dos sinais do periférico desenvolvido                        | 79 |

|      | X                                                                                 |    |

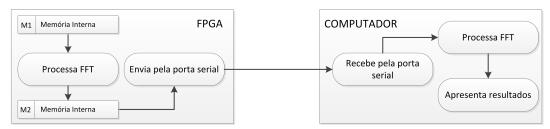

| 4.1          | Diagrama de fluxo de dados do teste realizado na primeira situação                        | 82  |

|--------------|-------------------------------------------------------------------------------------------|-----|

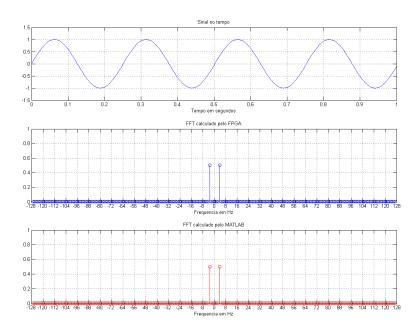

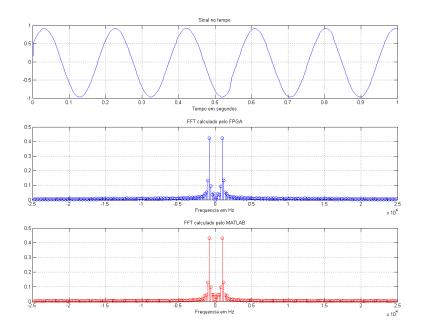

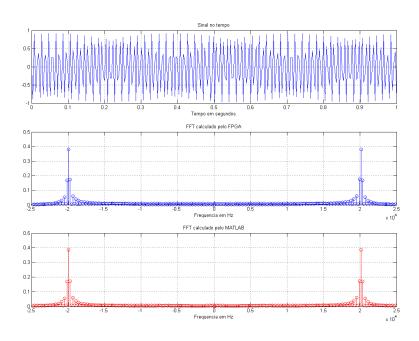

| 4.2          | Sinal original de 4Hz, FFT calculada pelo FPGA e FFT calculada pelo Matlab <sup>®</sup>   | 83  |

| 4.3          | Sinal original de 32Hz, FFT calculada pelo FPGA e FFT calculada pelo Matlab <sup>®</sup>  | 83  |

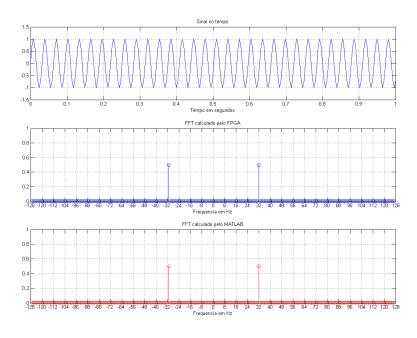

| 4.4          | Sinal original de 64Hz, FFT calculada pelo FPGA e FFT calculada pelo Matlab <sup>®</sup>  | 84  |

| 4.5          | Diagrama de fluxo de dados do teste realizado na segunda situação                         | 85  |

| 4.6          | Sinal original em forma de senoide, FFT calculada pelo FPGA e FFT calculada pelo          |     |

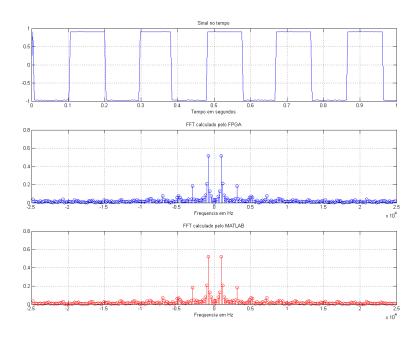

|              | $Matlab^{	ext{	iny $\mathbb{R}$}}.$                                                       | 85  |

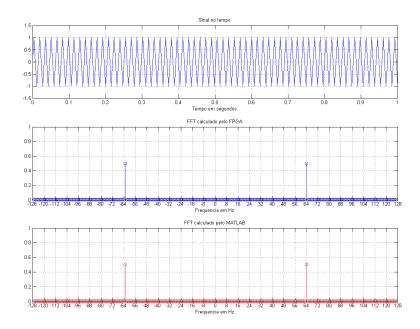

| 4.7          | Sinal original de onda quadrada de 10Khz, FFT calculada pelo FPGA e FFT calculada         |     |

|              | pelo Matlab <sup>®</sup>                                                                  | 86  |

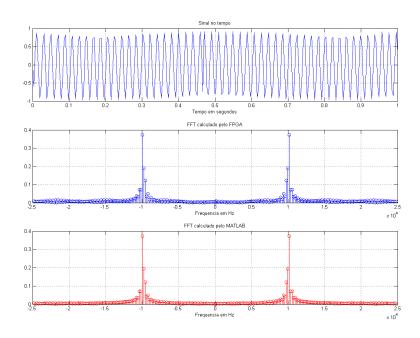

| 4.8          | Sinal original de senoide de 10KHz, FFT calculada pelo FPGA e FFT calculada pelo          |     |

|              | Matlab®                                                                                   | 86  |

| 4.9          | Sinal original de senoide de 20KHz, FFT calculada pelo FPGA e FFT calculada pelo          |     |

|              | $Matlab^{\circledR}$                                                                      | 87  |

| 4.10         | Diagrama de fluxo de dados do teste realizado na terceira situação                        | 87  |

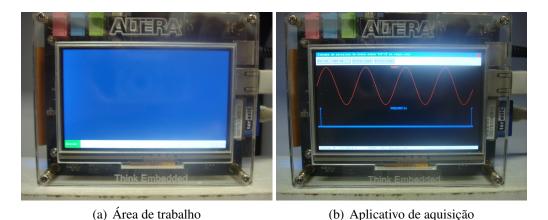

| 4.11         | À esquerda, tela da área de trabalho com o atalho para as demais telas. À direita, a tela |     |

|              | do aplicativo de aquisição de dados.                                                      | 88  |

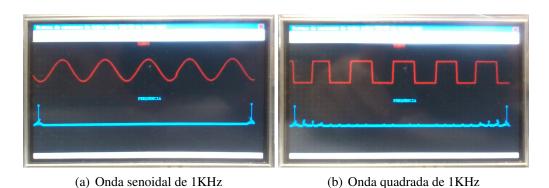

| 4.12         | Diferentes espectros de frequências para diferentes formas de onda, ambas com             |     |

|              | frequência de 1KHz                                                                        | 88  |

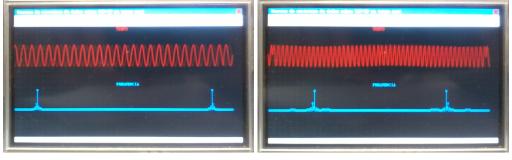

| 4.13         | Foto do NEEK com sinal senoidal de 5KHz e de 10KHz                                        | 89  |

| <b>A.</b> 1  | Configuração genérica do <i>pipeline</i>                                                  | .03 |

| A.2          | Pipeline com todos os sinais envolvidos                                                   | .04 |

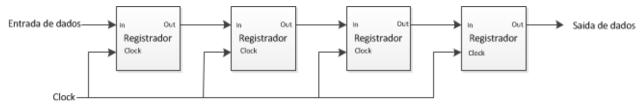

| A.3          | Estrutura de uma fila de dados                                                            | .05 |

| A.4          | Estrutura do multiplexador auto-controlado                                                | .05 |

| A.5          | Operação borboleta DIF                                                                    | .05 |

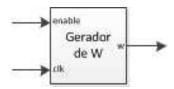

| A.6          | Entradas e saídas do gerador de fatores                                                   | .06 |

| A.7          | Elementos de um estágio                                                                   | .06 |

| A.8          | Sequência simplificada do <i>pipeline</i>                                                 | .07 |

| A.9          | Sequência detalhada do <i>pipeline</i>                                                    | .08 |

| A.10         | Simplificação para facilitar a simulação                                                  | .08 |

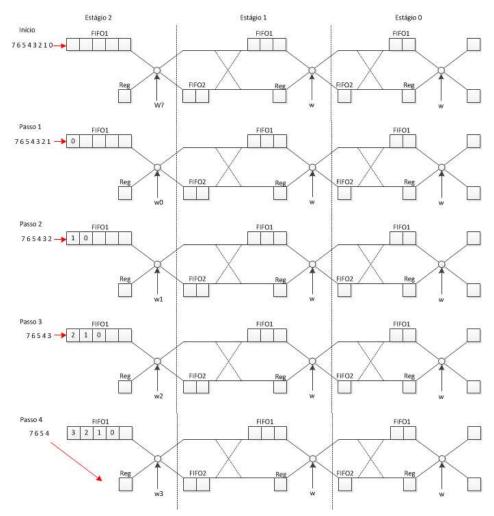

| <b>A</b> .11 | Passos 0 a 4 a simulação                                                                  | .09 |

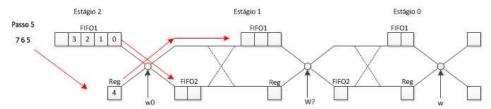

| A 12         | Passo 5 da simulação                                                                      | 10  |

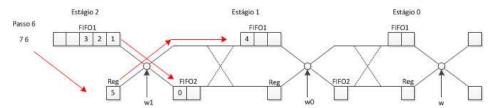

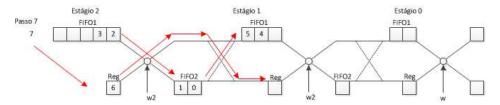

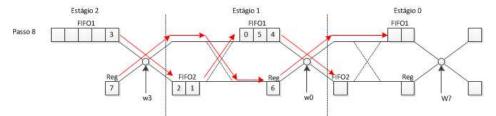

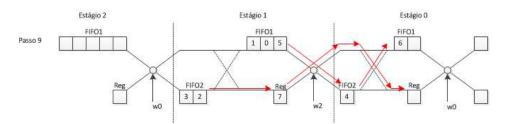

| A.13 Passo 6 da simulação.  |    |     |    |      | •   |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 110 |

|-----------------------------|----|-----|----|------|-----|-----|------|-----|----|---|----|---|--|--|--|--|------|--|--|-----|

| A.14 Passo 7 da simulação.  |    |     |    |      |     |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 110 |

| A.15 Passo 8 da simulação.  |    |     |    |      |     |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 111 |

| A.16 Passo 9 da simulação.  |    |     |    |      |     |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 111 |

| A.17 Passo 10 da simulação. |    |     |    |      |     |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 112 |

| A.18 Passo 11 da simulação. |    |     |    |      |     |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 112 |

| A.19 Passo 12 da simulação. |    |     |    |      | •   |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 112 |

| A.20 Passo 13 da simulação. |    |     |    |      | •   |     |      |     |    |   |    |   |  |  |  |  |      |  |  | 113 |

| A.21 Relação dos passos com | ає | exe | cu | ıção | o d | o a | ılgo | rit | mo | Σ | IF | • |  |  |  |  | <br> |  |  | 113 |

## LISTA DE TABELAS

| 2.1 | Principais diferenças entre as versões do processador NIOS 2                         | 23  |

|-----|--------------------------------------------------------------------------------------|-----|

| 2.2 | Tabela de ordenação <i>bit</i> -reverso                                              | 45  |

| 4.1 | Tempos médios do processamento a 100MHz                                              | 89  |

| 4.2 | Utilização dos elementos lógicos do FPGA                                             | 90  |

| 4.3 | Utilização de elementos lógicos pelos principais periféricos do processador          | 90  |

| D.1 | Comparação dos resultados para executar 1 multiplicação, em milissegundos e por pul- |     |

|     | sos de <i>clock</i>                                                                  | 129 |

| D.2 | Tempos de execução do algoritmo FFT para 256 pontos em ponto flutuante               | 129 |

#### LISTA DE ABREVIATURAS E SIGLAS

#### **Abreviaturas**

art. artigo

cap. capítulo

comb. combinacional

mux. multiplexador

reg. registrador

sec. seção

#### **Siglas**

ADC Conversor Analógico-Digital

API Application Programming Interface

ASIC Application Specific Integrated Circuit

CI Circuito Integrado

CPLD Complex Programmable Logic Device

DFT Discrete Fourier Transform

DIF Decimation In Frequency

DIT Decimation in Time

DMA Direct Memory Access

DMC Departamento de Mecânica Computacional

DSP Digital Signal Processing

DRAM Dynamic Random Access Memory

EL Elementos lógicos

FEM Faculdade de Engenharia Mecânica

FFT Fast Fourier Transform

FIFO First In First Out

FPGA Field Programmable Gate Array

Gbps Giga bits por segundo

HAL Hardware Abstraction Layer

LCD Liquid Crystal Display

LE Logic Elements

LUT Look Up Table

MAC Midia Access Controller

MIPS Milhões de Instruções Por Segundo

MM Memory Map

NEEK NIOS 2 Embedded Evaluation Kit

PLD Programmable Logic Device

PLL Phased Locked Loop

$R2^2SDC$  Radix $2^2$  single-path delay commutator

R2MDC Radix-2 multipath delay commutator

R2SDC Radix-2 single-path delay feedback

R4MDC Radix-4 multipath delay commutator

R4SDC Radix-4 single-path delay commutator

R4SDF Radix-4 single-path delay feedback

RAM Random Access Memory

RISC Reduced Instruction Set Computer

RTCS Real Time Communication Suite

RTOS Real-Time Operating System

RTL Register Transfer Level

SDL Specification and Description Language

SDRAM Synchronous Dynamic Random Access Memory

SGDMA Scatter-Gather Direct Memory Access

SoPC System On a Programmable Chip

SPLD Simple Programmable Logic Device

SRAM Static Random Access Memory

SSRAM Synchronous Static Random Access Memory

ST Stream

TCP Transmission Control Protocol

TOWER TWR-MCF51CN128

TSE Triple Speed Ethernet

UART Universal asynchronous receiver/transmitter

UDP User Datagram Protocol

ULA Unidade Lógica Aritmética

UNICAMP Universidade Estadual de Campinas

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Intergraded Circuit

## SUMÁRIO

| 1 | INT | RODUÇ   | ÂO                                              | 1  |

|---|-----|---------|-------------------------------------------------|----|

|   | 1.1 | Trabal  | hos relacionados                                | 2  |

|   | 1.2 | Objeti  | vo                                              | 9  |

|   | 1.3 | Organi  | ização do trabalho                              | 10 |

| 2 | Fun | DAMEN   | NTOS                                            | 13 |

|   | 2.1 | Introdu | ução ao FPGA                                    | 13 |

|   |     | 2.1.1   | Linguagens para programação de FPGAs            | 18 |

|   |     | 2.1.2   | Fluxo de projeto para FPGA                      | 21 |

|   | 2.2 | Micro   | processadores em <i>hardware</i> reconfigurável | 22 |

|   |     | 2.2.1   | Processador Soft-core NIOS 2 e SoPC Builder     | 23 |

|   |     | 2.2.2   | Kits de desenvolvimento                         | 28 |

|   | 2.3 | Micro   | controlador <i>Coldfire</i> FreeScale®          | 29 |

|   |     | 2.3.1   | O microcontrolador MCF51CN128                   | 29 |

|   |     | 2.3.2   | Kits de desenvolvimento                         | 30 |

|   | 2.4 | Sistem  | nas operacionais de tempo real                  | 31 |

|   |     | 2.4.1   | Características principais                      | 32 |

|   |     | 2.4.2   | RTOS uC/OS2                                     | 34 |

|   |     | 2.4.3   | RTOS MQX                                        | 35 |

|   | 2.5 | Repres  | sentação numérica de ponto fixo                 | 36 |

|   |     | 2.5.1   | Números racionais positivos                     | 37 |

|   |     | 2.5.2   | Complemento de 2 em números binários            | 38 |

|   |     | 2.5.3   | Números racionais sinalizados                   | 38 |

|   |     | 2.5.4   | Regras básicas para aritmética em ponto fixo    | 38 |

|   | 2.6 | Proces  | ssamento espectral de sinais                    | 40 |

|   |     | 2.6.1   | Transformada Fourier Discreta                   | 41 |

|   |     | 2.6.2   | Transformada Fourier Rápida                     | 42 |

|   |     | 2.6.3   | Dizimação no tempo                              | 43 |

|            |       | 2.6.4   | Dizimação na frequência                                     | 46  |

|------------|-------|---------|-------------------------------------------------------------|-----|

|            |       | 2.6.5   | Algoritmos seriais para a FFT                               | 48  |

| 3          | DES   | ENVOL   | VIMENTO DA ARQUITETURA                                      | 51  |

|            | 3.1   | Visão   | geral do sistema                                            | 51  |

|            |       | 3.1.1   | Aquisição de dados                                          | 54  |

|            |       | 3.1.2   | Processamento de sinais usando FPGA                         | 59  |

|            | 3.2   | Algori  | tmo FFT em FPGA                                             | 68  |

|            |       | 3.2.1   | O fluxo de dados                                            | 69  |

|            |       | 3.2.2   | O controlador do fluxo de dados                             | 74  |

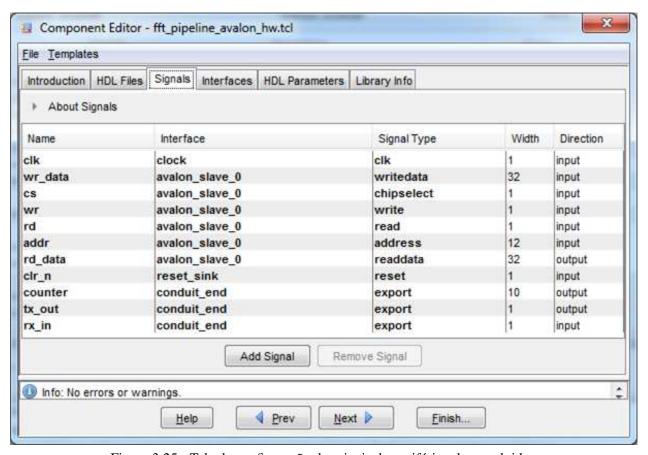

|            |       | 3.2.3   | Implementação do módulo personalizado para o cálculo da FFT | 76  |

|            |       | 3.2.4   | Integração do módulo implementado com o NIOS 2              | 79  |

| 4          | RES   | ULTAD   | os                                                          | 81  |

|            | 4.1   | Testes  | realizados e seus resultados                                | 81  |

|            |       | 4.1.1   | Situação 1                                                  | 81  |

|            |       | 4.1.2   | Situação 2                                                  | 84  |

|            |       | 4.1.3   | Situação 3                                                  | 87  |

|            | 4.2   | Tempo   | o de execução                                               | 89  |

|            | 4.3   | Utiliza | ação de elementos lógicos                                   | 90  |

| 5          | Con   | NCLUSÕ  | DES E PERSPECTIVAS                                          | 91  |

|            | 5.1   | Perspe  | ectivas                                                     | 93  |

| Rı         | EFER! | ÊNCIAS  | \$                                                          | 95  |

| <b>A</b> l | PÊND: | ICE A - | FUNCIONAMENTO DO ALGORITMO FFT                              | .03 |

|            | A.1   | Simula  | ação para oito pontos                                       | 07  |

| Αı         | PÊND' | ICE B - | Códigos VHDL                                                | 15  |

|            | B.1   |         |                                                             |     |

|            | B.2   |         | tador                                                       |     |

|            | B.3   |         | rador                                                       |     |

|            |       | _       |                                                             | 17  |

|            | D.T   | 111()   |                                                             |     |

| B.5                                                                 | Butterfly DIF                                                | 118 |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|--------------------------------------------------------------|-----|--|--|--|--|--|--|--|--|--|

| B.6                                                                 | Estágio                                                      | 119 |  |  |  |  |  |  |  |  |  |

| B.7                                                                 | Pipeline                                                     | 120 |  |  |  |  |  |  |  |  |  |

| APÊNDICE C - ESTRUTURA DE DADOS DO MÓDULO DE GERENCIAMENTO DE TELAS |                                                              |     |  |  |  |  |  |  |  |  |  |

| APÊNDIO                                                             | CE D - DESEMPENHO DE UMA MULTIPLICAÇÃO NO PROCESSADOR NIOS 2 |     |  |  |  |  |  |  |  |  |  |

| E SEU EF                                                            | FEITO NA FFT EM SOFTWARE                                     | 129 |  |  |  |  |  |  |  |  |  |

#### 1 Introdução

Nas últimas décadas, as constantes mudanças e avanços na tecnologia têm transformado a forma de projetar circuitos digitais. A presença dos *chips* reconfiguráveis faz com que algoritmos complexos possam ser embarcados e que a prototipagem aconteça em tempo reduzido, além de poder ter o seu comportamento alterado rapidamente. A existência atual de *hardware* reprogramável de grande capacidade permite que algoritmos de alta complexidade computacional possam ser implementados de forma concorrente, em oposição à regra de uma instrução por vez por processador, conhecida como "gargalo" de Von Neumann (SEBESTA, 2002).

A proposta deste trabalho é atuar no processamento de sinais, desenvolvendo uma arquitetura que possa ser utilizada com facilidade para a implementação concorrente dos respectivos algoritmos. Sinais estão presentes em muitas situações do dia-a-dia do ser humano. De acordo com Mello (2011), um sinal pode ser definido como uma função que carrega uma informação. Um exemplo é a comunicação por sinal de voz, onde há o sinal gerado pelo trato vocal e o sinal recebido pelo sistema auditivo. Apesar do sinal ser transmitido, a forma como ele é processado é inerente ao receptor. O processamento de sinais lida com a representação, transformação e manipulação dos sinais e da informação que eles contêm. Até a década de 60, a tecnologia para processamento de sinais era basicamente analógica. A evolução de computadores e microprocessadores juntamente com diversos desenvolvimentos teóricos causou um grande crescimento na tecnologia digital, surgindo o processamento digital de sinais (PDS). Um aspecto fundamental do processamento digital de sinais é que ele é baseado no processamento de sequências de amostras. Para tanto, o sinal contínuo no tempo é convertido numa sequência de amostras, ou seja, convertido em um sinal discreto no tempo. Após o processamento digital, a sequência de saída pode ser convertida de volta a um sinal contínuo no tempo.

Para realizar o processamento de um sinal podem ser usadas diversas ferramentas: um computador pessoal, um microcontrolador, um FPGA (*Field Programmable Gate Array*), dentre outros. A proposta deste trabalho é utilizar um FPGA para processar dados. Foi desenvolvido um sistema de aquisição de dados distribuído em uma rede local, onde diversos dispositivos realizam a aquisição de um sinal e o transmitem pela rede para um dispositivo central (um FPGA) que o processa e exibe o resultado numa tela de LCD (*Liquid Crystal Display*).

#### 1.1 Trabalhos relacionados

Existem diversos trabalhos que utilizam processadores *soft-core* embarcados em FPGA combinados com módulos personalizados para otimizar o processamento. Esses projetos geralmente buscam a execução em tempo real, ou seja, dentro de um tempo determinado. Para tanto, são propostas arquiteturas que permitem que o processador fique livre do processamento computacional mais complexo, através da criação de rotinas concorrentes diretamente em *hardware*. Estas rotinas geralmente se transformam ou em instruções personalizadas diretamente no núcleo do processador ou em periféricos acoplados ao barramento interno do processador. As duas implementações otimizam o processo e aumentam o desempenho do sistema. Ao utilizar instruções personalizadas, é necessário escrever um programa em linguagem C e ocupar o processador com esta tarefa. Utilizar periféricos é uma solução que pode desocupar consideravelmente o processador, deixando-o livre para executar outras funções, permitindo otimizações mais eficazes diretamente em *hardware*.

As implementações utilizando esta metodologia de projeto, que inclui projeto de *hardware* em FPGA e utilizam processadores *soft-core* executando um determinado algoritmo, têm levado a resultados de alto desempenho em termos de tempo de execução. A flexibilidade presente nesta metodologia permite criar aplicações para diversas áreas do conhecimento, como por exemplo, controle robótico, processamento de sinais, processamento de imagens e inteligência artificial. Geralmente implementações em *hardware* são melhores que implementações em *software* em termos de tempo de processamento e consumo de energia. Alguns trabalhos relacionados com esta metodologia serão apresentados nos próximos parágrafos.

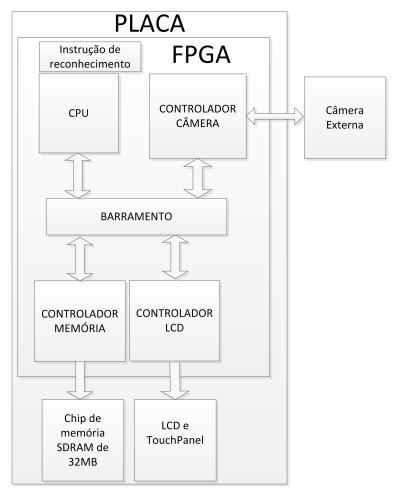

O processamento de imagens digitais é um assunto que se estende à ciência da computação, teoria da informação, geometria e outras aplicações. Liao et al. (2010) propõem um sistema de reconhecimento de folhas de plantas utilizando um projeto misto de *software* e *hardware*, onde utiliza instruções personalizadas diretamente no núcleo do processador para acelerar o tempo de execução. Neste trabalho foi adicionada uma instrução de comparação personalizada para realizar a identificação das folhas, resultando em redução no tempo de processamento em até 7 vezes. A Figura 1.1 apresenta um diagrama de blocos simplificado do processador.

Figura 1.1 - Processador NIOS 2 no reconhecimento de folhas. Fonte: Adaptado de Liao et al. (2010).

Reconhecimento e rastreamento de pessoas em imagens é uma tarefa complexa. Um método de reconhecimento foi proposto por Mayya et al. (2010), que utiliza um processador NIOS 2 e instruções personalizadas para acelerar o reconhecimento das pessoas. O algoritmo foi desenvolvido em linguagem C, e foi executado pelo processador que utilizou variáveis de ponto fixo em *software*. Obteve-se uma taxa de quatro quadros por segundo. Ao invés de utilizar uma câmera para capturar as imagens, foi utilizada uma memória *Flash* com as imagens e vídeos previamente armazenados. A Figura 1.2 apresenta o processador desenvolvido.

Figura 1.2 - Processador NIOS 2 no reconhecimento de pessoas. Fonte: Adaptado de Mayya et al. (2010).

A execução de filtros digitais de sinais é uma tarefa complexa e pode consumir um alto tempo na execução. No trabalho de Boudabous et al. (2005), o foco está na aceleração do algoritmo do filtro digital de distância direcional aplicado na remoção de ruídos em imagens. Foi realizada a comparação entre a execução do algoritmo puramente em *software* e uma segunda versão composta de um programa para movimentar os dados e instruções personalizadas para acelerar a execução do algoritmo, utilizando o processador NIOS 2 da Altera<sup>®</sup>. Obteve-se uma redução de aproximadamente 20 mil vezes no tempo de execução e todos os 288 multiplicadores em *hardware* presentes no FPGA foram utilizados.

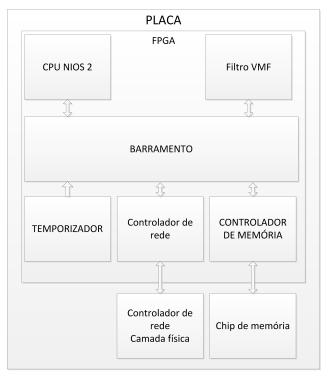

Uma implementação parecida com a anterior, proposta pelo mesmo autor, é o filtro digital por vetor de medianas, apresentada em Boudabous et al. (2007). A contribuição deste trabalho está na implementação do algoritmo em um módulo periférico ao processador, utilizado para realizar os cálculos. O módulo proposto foi criado utilizando uma linguagem de descrição de circuitos. Nele foram instanciados 36 vezes o componente de cálculo da norma entre dois pixels, um componente que realiza o acúmulo destes resultados e por fim um componente que minimiza a norma calculada. Esta complexidade computacional foi removida do processador, que agora deve enviar os dados para o periférico e realizar a leitura do resultado. Com isto, 96% dos multiplicadores presentes no FPGA foram utilizados, gerando uma redução de aproximadamente 48 vezes na execução do

algoritmo. A Figura 1.3 apresenta o processador desenvolvido.

Figura 1.3 - Projeto de *hardware* do filtro digital de imagens. Fonte: Adaptado de Boudabous et al. (2007).

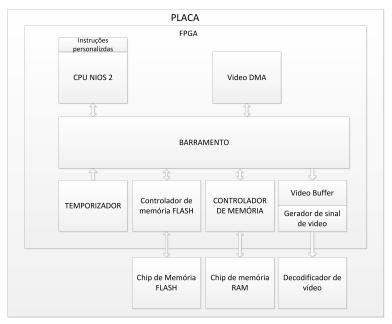

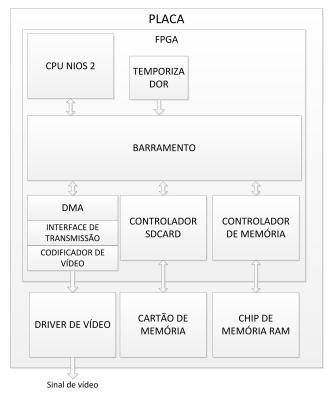

Além de processamento de imagens, outras aplicações para um sistema composto por um FPGA foram avaliadas. Todas elas possuem um processador e implementações em *hardware* para realizar otimizações de processamento. Yang et al. (2011) apresentam uma implementação de um leitor de imagens de um cartão de memória com saída para um sinal de vídeo. Trata-se de um projeto em que o foco está na leitura dos dados do cartão implementado em linguagem C. Porém foi preciso desenvolver o *hardware* no FPGA que faz o acesso e o processamento dos dados contidos no cartão. A Figura 1.4 apresenta o processador desenvolvido.

Figura 1.4 - Projeto de *hardware* do leitor de cartões. Fonte: Adaptado de Yang et al. (2011).

Ramakrishna et al. (2011) sugerem a utilização de instruções personalizadas para realizar o cálculo do histograma e da saturação de uma imagem. É feita uma comparação do algoritmo sem e com o uso de instruções personalizadas no processador NIOS 2. Observa-se um ganho no tempo de execução ao utilizar instruções personalizadas. A Figura 1.5 apresenta a estrutura interna do processador desenvolvido.

Figura 1.5 - Diagrama de blocos do processador com instruções personalizadas. Fonte: Adaptado de Ramakrishna et al. (2011).

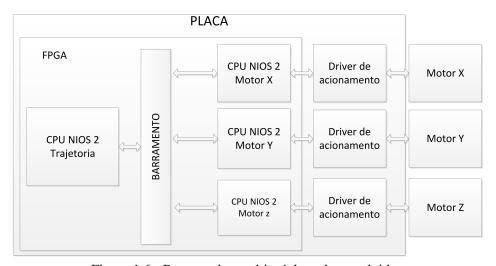

A Lógica nebulosa tem sido muito utilizada para resolver problemas de controle. A implementação de lógica nebulosa em FPGA tem a vantagem de ser flexível e de execução rápida. Kung et al. (2009) implementam um processador com quatro núcleos NIOS 2 para controlar uma mesa XYZ (3 graus de liberdade). Um dos núcleos calcula a trajetória do movimento, enquanto os demais controlam os motores. Cada núcleo de controle dos motores recebe o comando de posicionamento do núcleo principal e realiza o controle da posição utilizando lógica nebulosa. Portanto, o funcionamento paralelo dos quatro núcleos aumentam o poder computacional do sistema. A Figura 1.6 mostra o processador de forma simplificada.

Figura 1.6 - Processador multi-núcleos desenvolvido. Fonte: Adaptado de Kung et al. (2009).

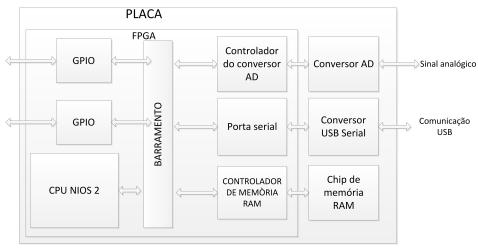

Sistemas de aquisição de dados utilizam placas de aquisição de dados ou microprocessadores para controlar a aquisição, armazenamento e transmissão dos dados. Wei e Guidong (2010) apresentam alguns pontos fracos destes sistemas e propõem o uso de um FPGA para realizar em *hardware* o controle da aquisição e o uso do processador NIOS 2 para realizar o ajuste do sinal antes de enviá-lo para um computador através da porta USB. O projeto é flexível, com ênfase na portabilidade e facilidade de configuração do conversor analógico-digital externo ao FPGA. A Figura 1.7 mostra este processador.

Figura 1.7 - Projeto de *hardware* do sistema de aquisição de dados. Fonte: Adaptado de Wei e Guidong (2010).

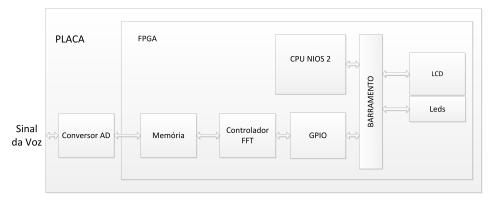

O reconhecimento da fala pode ser utilizado em inúmeras aplicações. Reconhecer uma palavra envolve uma sequência de processamentos, que podem ser otimizados através do uso de um FPGA. Zhang et al. (2011) apresentam uma proposta de sistema embarcado em um FPGA para reconhecimento da fala. O projeto foi dividido em 2 partes: uma utiliza o *hardware* para aplicar o algoritmo da transformada rápida de Fourier externo a um processador NIOS 2 e a outra aplica os demais processos matemáticos para realizar o reconhecimento. Obteve-se um ganho de 17 vezes no tempo de reconhecimento. A Figura 1.8 apresenta o diagrama de blocos simplificado do sistema.

Figura 1.8 - Projeto de *hardware* simplificado do sistema de reconhecimento da fala. Fonte: Adaptado de Zhang et al. (2011).

#### 1.2 Objetivo

O principal objetivo deste trabalho foi desenvolver uma arquitetura para adquirir e processar sinais digitais usando um FPGA como módulo central, e módulos de conversão analógico-digital distribuídos em uma rede local. Os resultados obtidos no processamento poderão ser transmitidos para um sistema de arquivamento e monitoramento remoto por operadores, além de possibilitar a operação do sistema de processamento diretamente sobre o FPGA. Neste caso, existe a necessidade de uma interface homem-máquina para apresentação dos dados processados e para controle da aquisição remota dos sinais. Deste modo, a unidade central representada pelo FPGA necessitou de inteligência embarcada, por isso foi utilizado um microcontrolador de boa capacidade de processamento para as funções de comunicação. Deve-se ressaltar que este microcontrolador foi projetado em linguagem de descrição de circuitos e sintetizado no FPGA. Porém, como não é o foco do sistema, adotou-se a princípio uma propriedade intelectual do fabricante do FPGA.

Deste modo, pode-se dividir o trabalho realizado em três partes principais:

- módulo de aquisição de dados;

- módulo de processamento digital de sinais;

- interface homem-máquina.

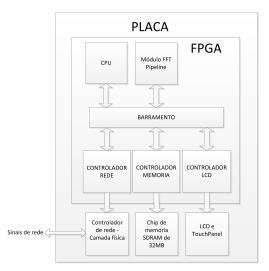

Para tanto, foi necessário projetar e implementar uma arquitetura no processador que permita executar todas as funções necessárias. O diagrama de blocos da Figura 3.11 apresenta um esquema

simplificado, onde pode-se visualizar o processador que foi projetado.

Figura 1.9 - Diagrama de blocos simplificado do processador.

Com o propósito de concentrar os esforços e prover uma metodologia de teste do sistema a desenvolvido foi adotada uma ferramenta de processamento digital de sinais que possa explorar os recursos disponíveis no sistema, a transformada rápida de Fourier.

#### 1.3 Organização do trabalho

O capítulo 1 apresenta uma introdução ao trabalho realizado, onde comenta-se a respeito de trabalhos relacionados que utilizam processadores *soft-core* e módulos em *hardware* para otimizar o processamento em FPGA. Estes trabalhos vão de sistemas de aquisição de dados a processamento de imagens.

O capítulo 2 apresenta os fundamentos utilizados no trabalho. São apresentados os dispositivos programáveis, sua composição e utilização; o microprocessador *soft-core* NIOS 2 e seu barramento; os sistemas operacionais de tempo real; a representação numérica de ponto fixo e sua aritmética; e os algoritmos da transformada rápida de Fourier.

O capítulo 3 aborda o desenvolvimento do projeto. Primeiro é apresentada uma visão geral da arquitetura. Depois é apresentado o módulo de aquisição de dados detalhadamente. Finalmente é apresentado o algoritmo implementado em *hardware* para transformada de Fourier e sua integração

ao processador NIOS 2.

O capitulo 4 expõe os resultados obtidos nos experimentos comparando a implementação dos algoritmos puramente em *software* e utilizando o módulo FFT desenvolvido em *hardware*. É levantada a discussão sobre a utilização de elementos lógicos no FPGA.

O capítulo 5 apresenta as conclusões obtidas pelos experimentos e aponta futuros trabalhos a serem desenvolvidos.

O apêndice A apresenta uma simulação passo a passo do algoritmo proposto para o cálculo da FFT.

#### **2 FUNDAMENTOS**

Este capítulo aborda os conhecimentos necessários para a realização do projeto proposto. Na primeira seção será abordado o funcionamento dos FPGAs, as linguagens de descrição de *hardware* existentes, o fluxo de um projeto em FPGA, o uso de processadores *soft-core* e a ferramenta de desenvolvimento utilizada. Na segunda seção será apresentado o microcontrolador MCF51CN128 da FreeScale Semiconductors que foi utilizado neste projeto, abordando suas características técnicas, seus periféricos e o uso do sistema operacional de tempo real MQX, além da ferramenta de desenvolvimento. Na terceira seção será apresentada a representação numérica em ponto fixo, utilizada nos cálculos implementados no FPGA. Por fim, será apresentada a transformada de Fourier discreta e suas variações de implementação através da transformada rápida com dizimação no tempo e na frequência.

#### 2.1 Introdução ao FPGA

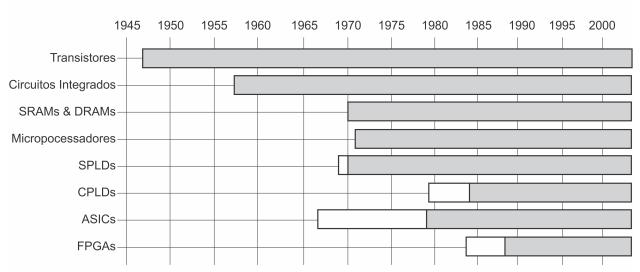

Antes da criação dos FPGAs, as tecnologias disponíveis para desenvolvimento de circuitos eram os transistores, circuitos integrados (memórias, registradores, e outros), microprocessadores, SPLDs (*Simple Programmable Logic Device*), CPLDs (*Complex Programmable Logic Device*) e ASICs (*Application Specific Integrated Circuits*). A Figura 2.1 mostra as datas aproximadas do surgimento destas tecnologias. Por exemplo, embora o primeiro FPGA tenha surgido por volta de 1984, os projetistas de *hardwares* só começaram a utilizar esta tecnologia no início de 1990 (MAXFIELD, 2004).

Após a invenção dos transistores, os circuitos digitais tornaram-se cada vez mais complexos. O número de transistores utilizados nos circuitos digitais aumentava rapidamente. Portanto, surgiu a necessidade de reduzir a eletrônica envolvida e desta forma surgiu o circuito integrado (CI). A cada novo CI lançado, a complexidade dos projetos aumentava exponencialmente, possibilitando o desenvolvimento de aplicações que até então eram difíceis de serem implementadas (MAXFIELD, 2004).

Figura 2.1 - Histórico do surgimento e utilização de tecnologias de construção de circuitos integrados. A parte branca indica que apesar da tecnologia estar disponível, ela ainda não tinha sido recebida com entusiasmo pelos profissionais do setor.

Fonte: (MAXFIELD, 2004)

No final de 1960 e início de 1970 surgiram novas tecnologias na área de circuitos integrados digitais, o que impulsionou o seu processo de expansão. Em 1970 foi anunciada a primeira DRAM (*Dynamic Random Access Memory*). A memória RAM dinâmica é formada por pares de transistores e capacitores que consomem pouco espaço no silício. O atributo dinâmico é utilizado porque o capacitor perde a informação ao longo do tempo, de modo que cada célula da DRAM deve ser periodicamente atualizada para manter a informação armazenada. A memória SRAM (*Static Random Access Memory*) difere da memória DRAM porque uma vez que a informação foi carregada para dentro da célula SRAM os dados permanecerão inalterados, a menos que seja especificamente alterado ou a energia elétrica seja removida do sistema (MAXFIELD, 2004; MOREIRA, 2009).

Ainda na década de 70 surgiu o projeto de um microprocessador que incorporava as funções de uma unidade de processamento central em um único circuito integrado. Os microprocessadores substituíram milhões de transistores o que diminuiu o tamanho dos dispositivos. Eles são utilizados principalmente para processamentos complexos e dentre algumas aplicações estão presentes nos computadores e aparelhos eletrônicos. As tecnologias SRAM e de microprocessadores são largamente utilizadas na maioria dos FPGAs (MAXFIELD, 2004; MOREIRA, 2009).

Os dispositivos lógicos programáveis (*Programmable Logic Devices*, *PLDs*) foram os primeiros circuitos integrados cuja arquitetura interna (determinada pelo fabricante) foi projetada de

tal forma que podia ser configurado ou programado em campo, no local de trabalho do desenvolvedor. O termo PLD pode ser atribuído a duas subcategorias: os SPLDs e os CPLDs. Os SPLDs referem-se aos primeiros PLDs fabricados, os quais originalmente continham um número modesto de unidades lógicas equivalentes e eram bastante simples. Os CPLDs são dispositivos que contêm uma determinada quantidade de funções SPLD que compartilham uma matriz de interconexões programáveis. Se comparado aos FPGAs, esses dispositivos contêm um número relativamente limitado de unidades lógicas que podem ser utilizadas para implementar funções menores e menos complexas (MAXFIELD, 2004; MOREIRA, 2009).

Durante todo este processo, existia ainda a fabricação de *chips* dedicados para uma aplicação, chamados de ASIC. Esses dispositivos podem conter centenas de milhares de unidades lógicas, e podem ser otimizados em termos de desempenho e de área ocupada. Em geral, o ASIC é concebido e construído para fim industrial e produção em larga escala. Portanto, as opções disponíveis para a construção de circuitos integrados eram ou a utilização de PLDs, altamente configuráveis, mas sem suporte a funcionalidades complexas, ou a utilização de ASICs para aplicações específicas (MAXFIELD, 2004; MOREIRA, 2009).

Em meados de 1985, uma companhia chamada Xilinx® introduziu a ideia de combinar o controle de usuário e o *time-to-market* do PLD com a densidade e os benefícios de arranjo de unidades lógicas. Isto gerou uma nova classe de circuito integrado chamado de FPGA. As FPGAs ocupam o meio-termo entre PLDs e ASICs, porque suas funcionalidades podem ser personalizadas na "programação em campo"como acontece com os PLDs, e além disso, podem conter milhares de unidades lógicas utilizadas para a execução de funcionalidades extensas e complexas que anteriormente só poderiam ser realizadas utilizando ASIC. O custo de um projeto em FPGA é menor do que o de um projeto em ASIC, apesar de componentes ASICs serem mais baratos quando utilizados na produção de larga escala. Ao mesmo tempo, implementar mudanças no projeto é mais fácil em FPGA e o tempo necessário para a especificação, desenvolvimento e implementação até a finalização do projeto é menor (MAXFIELD, 2004; MOREIRA, 2009).

Os FPGAs são circuitos integrados digitais que contêm blocos configuráveis de lógica com interconexões programáveis entre eles. Os projetistas podem configurar esses dispositivos de maneira que executem diferentes tarefas. A parte do nome FPGA referenciada como *Field Programmable* menciona o fato de que sua programação acontece "em campo", ou seja, no local do usuário, diferentemente de dispositivos cuja programação é feita apenas pelo fabricante. Isto significa que

os FPGAs podem tanto ser configurados no laboratório como podem ser modificados depois de já estarem em seus locais definitivos de operação. O termo *Gate Array* está relacionado ao conceito de arranjo de unidades lógicas. As unidades lógicas são componentes padrão formados por transistores que podem ser configurados independentemente e interconectados a partir de uma matriz de trilhas condutoras e chaves programáveis (MAXFIELD, 2004; ALTERA, 2011p).

Durante o início da década de 1990, o tamanho e a sofisticação dos FPGAs começaram a aumentar. O grande mercado eram os consumidores das áreas de telecomunicação e redes, as quais envolviam o processamento de grandes blocos de dados. Mais tarde, no final da década de 1990, a utilização de FPGA em indústria automotiva e em aplicações industriais passou a ter um grande crescimento. No início do ano 2000, já se encontrava disponível FPGAs de alto desempenho contendo milhares de unidades lógicas. Algumas das características destes dispositivos são a possibilidade de incorporar os núcleos de microprocessadores embarcados, além dos pinos de alta velocidade para serem usados como entradas e saídas. O resultado é que atualmente os FPGAs podem ser utilizados para implementar praticamente qualquer circuito digital, incluindo *software* e dispositivos de comunicação como rádio, radar, processamento de imagem e outras aplicações de processamento digital de sinais (MAXFIELD, 2004; ALTERA, 2011p).

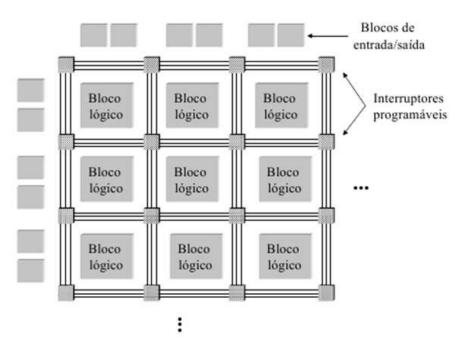

Atualmente, os FPGAs são compostos por memória SRAM embarcada configurável (pode ser reprogramada quantas vezes for necessário) para realizar as conexões, blocos de entrada e saída de dados e blocos lógicos. Sendo mais específico, um FPGA contém componentes lógicos programáveis, chamados de elementos lógicos (LEs) e uma hierarquia de interconexões reconfiguráveis que permitem que os elementos lógicos possam estar fisicamente conectados. Um FPGA que utiliza células SRAM deve ser reprogramado toda vez que é ligado, pois o dispositivo FPGA é composto de uma memória volátil que perde as conexões ao ser desligada. Pode-se configurar LEs para executar funções complexas de combinações, ou portas lógicas meramente simples como AND e XOR. Na maioria dos FPGAs, os blocos lógicos também incluem elementos de memória, que podem ser simples *flip-flops* ou blocos completos de memória (MAXFIELD, 2004; ALTERA, 2011p).

Os blocos lógicos programáveis, presentes nos FPGAs, podem ser vistos como componentes que podem ser configurados independentemente. Atualmente, o bloco lógico programável é composto de vários recursos que podem implementar diversas funções aritméticas e lógicas. Estes recursos variam de acordo com o fabricante do FPGA, mas de maneira geral incluem LUTs (*Lookup Table*), registradores que podem atuar como *flip-flops*, memórias, multiplicadores e acumulado-

res programáveis. Cada FPGA é formado por um grande número de blocos lógicos programáveis interconectados através de uma matriz de trilhas condutoras e chaves programáveis baseados em SRAM. Para especificar a funcionalidade de cada bloco lógico programável, assim como seletivamente fechar as chaves da matriz de interconexão, é necessário gerar um arquivo binário que indique as configurações do FPGA. Esse arquivo binário é gerado a partir de ferramentas de *software* seguindo um determinado fluxo de projeto. A hierarquia de chaves programáveis em conjunto com os blocos lógicos programáveis permite que o sistema possa ser interconectado de acordo com a necessidade do projetista. A Figura 2.2 apresenta os blocos lógicos, as chaves de interconexão física interna e os blocos de entrada e saída de dados. (SKLIAROVA; FERRARI, 2003; ALTERA, 2011p; MAXFIELD, 2004)

Figura 2.2 - Estrutura interna de um FPGA. Fonte: (SKLIAROVA; FERRARI, 2003)

### 2.1.1 Linguagens para programação de FPGAs

Existem diversas maneiras de desenvolvimento e implementação de projeto de circuitos para FPGA. Os métodos tradicionais de fazer a programação de um FPGA incluem o uso de linguagem esquemática ou linguagem de descrição de *hardware*. A linguagem utilizada descreve as funções lógicas a serem sintetizadas no FPGA.

A linguagem esquemática apresenta diretamente as conexões e os elementos digitais que serão utilizados no processo, enquanto que as linguagens de descrição descrevem o funcionamento do *hardware* independente dos recursos digitais que serão utilizados. Logo, para utilizar este método de programação, é preciso ter em mente todo o *hardware* que deverá ser projetado (MOREIRA, 2009).

Normalmente utilizam-se linguagens de alto nível para descrever o funcionamento de um circuito através de um arquivo de texto ao invés de uma descrição gráfica no nível de lógica digital. As linguagens de descrição de *hardware* são utilizadas para descrever uma representação funcional e comportamental do circuito através de notação adequada e padronizada que independe do fabricante de *hardware* (MOREIRA, 2009).

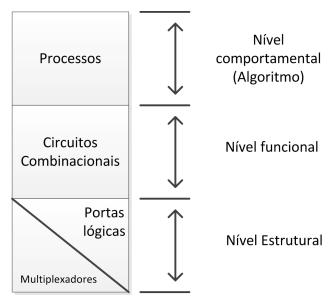

As linguagens de descrição de *hardware*, HDL(*Hardware Description Language*) são bastante versáteis, por isso é importante entender de que maneira essa linguagem pode ser utilizada como parte do fluxo de projeto de um circuito digital. As funcionalidades de um circuito digital podem ser representadas em três diferentes níveis de abstração e a linguagem pode oferecer suporte a esses níveis de abstração, como mostrado na Figura 2.3. O nível mais alto de abstração é o comportamental, que permite descrever o comportamento do circuito através de laços e processos. Neste nível de abstração também é possível compor equações através de multiplicações e somas. O próximo nível de abstração possibilita descrever o funcionamento do circuito em termos de lógica combinacional (por exemplo, *if, then, else*) e booleana. Este nível de abstração também engloba a representação do circuito no nível de registros de transferências (RTL, *Register Transfer Level*), que consiste basicamente em uma representação por registradores interligados por lógica combinacional. O nível mais baixo de abstração de um HDL é o estrutural, que consiste em uma representação direta do circuito através de portas lógicas (CARDOSO; ARANTES, 2007; MAXFIELD, 2004).

A principal motivação para a utilização de linguagens de descrição de hardware é que estas

Figura 2.3 - Níveis de abstração em linguagens de descrição de *hardware*. Fonte: Adaptado de Cardoso e Arantes (2007)

são linguagens padronizadas independentemente do fornecedor de *hardware* ou da tecnologia empregada, portanto é portátil e reutilizável. Uma vez que o código foi escrito, ele pode ser utilizado para implementar um circuito em um dispositivo programável ou pode ser utilizado no processo de fabricação de um *chip*. Atualmente, muitos *chips* comerciais são projetados utilizando essa abordagem (PEDRONI, 2004).

#### **VHDL**

Em 1980 o Departamento de Defesa dos Estados Unidos iniciou um programa para documentar o comportamento de ASICs que compunham os equipamentos vendidos às Forças Armadas americanas e desenvolveu uma linguagem para descrever o *hardware* de um *chip*. Isto quer dizer que a linguagem foi desenvolvida para substituir os complexos manuais que descreviam o funcionamento dos ASICs. Esta linguagem foi chamada de HDL (*Hardware Description Language*) e posteriormente de VHDL (VHSIC *Hardware Description Language*, onde VHSIC significa *Very High Speed Intergraded Circuit*). Ela foi certificada como um padrão IEEE em 1987 e vem recebendo revisões desde então (ALTERA, 2011n; ALTERA, 2011f).

De acordo com Mentor (1991), um projeto desenvolvido utilizando VHDL é composto de:

- Entidades (*Entities*)

- Arquiteturas (*Architecture*)

- Configurações (Configuration)

- Bibliotecas (*Packages*)

A entidade é responsável pela descrição das portas de entrada e saída dos circuitos, que servem para formalizar uma comunicação com outros circuitos. A arquitetura é responsável por descrever o comportamento dos circuitos, ou seja, o algoritmo utilizado para desempenhar sua funcionalidade. As arquiteturas podem possuir estruturas concorrentes e estruturas sequenciais que são descritas como um algoritmo. As estruturas do código são sempre concorrentes (paralelas), sendo que a lógica de conexão das mesmas especificam o comportamento final do circuito (PERRY, 2002).

Na Figura 2.4, como exemplo, temos um projeto completo, executando uma operação lógica conjuntiva entre os sinais de entrada. Observe que na declaração da entidade, denominada de "PORTA AND", encontra-se a especificação dos sinais e sua direção, entrada ou saída. Na declaração da arquitetura, denominada "comportamento", está o comportamento da entidade, a qual realiza a lógica e atribui o resultado no sinal de saída. A figura apresenta ainda o *hardware* gerado a partir do código VHDL (MENTOR, 1991).

```

ENTITY PORTA_AND IS

PORT (

A, B: IN STD_LOGIC;

C: OUT STD_LOGIC

)

END PORTA_AND;

ARCHITECTURE comportamento OF PORTA_AND IS

BEGIN

C <= A AND B

END comportamento;

```

Figura 2.4 - Exemplo de projeto em VHDL.

# 2.1.2 Fluxo de projeto para FPGA

A mudança em desenvolver um projeto com base no esquema digital para o desenvolvimento com base no HDL trouxe melhorias significativas. Essa mudança permitiu aos desenvolvedores implementar os módulos em um padrão comportamental que era independente da tecnologia. No entanto, haviam muitos aspectos no projeto digital com o uso do HDL que poderiam ser melhorados. A fim de aperfeiçoar o desenvolvimento de projeto em circuitos integrados houve um esforço por parte da comunidade acadêmica e da indústria para definir um fluxo principal de projeto. O fluxo tradicional de projeto de circuitos para FPGA pode ser dividido em quatro fases distintas: especificação, verificação, implementação e depuração do sistema. É importante salientar que pode haver variação na especificação de cada fase do fluxo de projeto de acordo com o fabricante da FPGA (CARDOSO; ARANTES, 2007; MAXFIELD, 2004).

Na fase de especificação, o circuito é descrito através de uma linguagem de descrição. Através desta descrição, o *software* fornecido pelo fabricante do FPGA irá criar as conexões internas, resultando na lógica descrita. Nesta fase deve-se atentar ao modo de descrever os circuitos, pois apesar das linguagens oferecerem diversos recursos, nem todos podem ser sintetizados (convertidos em um circuito lógico) (CARDOSO; ARANTES, 2007).

Na fase de verificação, o programa escrito em linguagem de descrição de *hardware* é simulado através de ferramentas oferecidas pelo fabricante. O simulador é um *software* que confirma as funcionalidades de um circuito. Quando um projeto utiliza uma linguagem padronizada, por exemplo VHDL, há garantias de que o projeto pode ser reutilizado. Se um fornecedor de FPGA alterar suas bibliotecas, apenas é necessário fazer a compilação da fase de síntese. Depois de completar a fase de síntese é necessário verificar se o circuito projetado está trabalhando conforme o esperado. Esse é o objetivo da fase de verificação. No caso do simulador encontrar algum problema, o projeto deve voltar para a etapa de especificação. O projetista deverá corrigir a descrição do *hardware* e executar a etapa de verificação. Estimativas indicam que os projetistas utilizem 50% do tempo de desenvolvimento nas fases de especificação e verificação até que o projeto funcione como o esperado. Após o projeto funcionar apropriadamente, inicia-se a fase de implementação (CARDOSO; ARANTES, 2007; MAXFIELD, 2004).

Nesta fase, o circuito descrito é compilado e sintetizado no FPGA. Ela é realizada necessa-

riamente com o uso do ambiente de programação do fabricante do FPGA. Esta fase compreende as etapas de tradução, posicionamento e roteamento, analisador de tempo e *download* do código para o FPGA. Durante a tradução, o *software* analisa o código e gera os elementos de *hardware* necessários para criar o circuito dentro do FPGA. Feito isto, o *software* parte para a etapa de posicionamento destes elementos e roteamento dos sinais existentes entre eles. Então, através de restrições criadas pelo usuário (ou utilizando as configurações padrão), parte para a análise do tempo de propagação dos sinais. Enfim, cabe ao usuário fazer o *download* dos dados gerados pelo *software* para o FPGA (CARDOSO; ARANTES, 2007; ALTERA, 2011e).

Ao fazer o *download* do código para o FPGA, dá-se início à fase de depuração. Nessa fase, é preciso verificar se o projeto está funcionando no dispositivo real conforme havia sido planejado. Encontrar problemas nessa fase significa que a especificação do projeto para o dispositivo em uso não foi realizada de maneira apropriada ou que alguns aspectos dos sinais, cuja origem ou destino sejam o dispositivo, não foram considerados. Desta forma, deve-se coletar os dados do problema e corrigir a modelagem do projeto voltando a fase de especificação.

#### 2.2 Microprocessadores em *hardware* reconfigurável

Os FPGAs tem sido amplamente empregados para a criação de circuitos digitais específicos. Contudo, existem outros recursos que podem ser aproveitados, como por exemplo, o uso de microprocessadores totalmente escritos em linguagem de descrição de *hardware*. Estes têm a vantagem de permitir que seja criado um processador com *hardware* totalmente dedicado à aplicação com a vantagem de utilizar circuitos adicionais criados pelo próprio usuário. Isto abre portas para que o sistema tenha um módulo em hardware, que agregado a um processador pode permitir que este execute funções complexas de forma muito mais rápida.

# 2.2.1 Processador Soft-core NIOS 2 e SoPC Builder

O processador *soft-core* NIOS 2 (ALTERA, 2011k) é um processador escrito totalmente em linguagem de descrição de *hardware*, por isto é chamado de *soft-core* ou seja, o núcleo do processador pode ser alterado. Trata-se de um núcleo que possui arquitetura *Harvard* RISC de 32-bits. Foi desenvolvido internamente pela Altera® e pode ser personalizado de acordo com a necessidade, sendo possível alterar desde suas configurações até suas instruções aritméticas. Sua única limitação é a quantidade de elementos lógicos presentes no FPGA em uso, visto que ele é livre de *royalties*.

Existem três versões disponíveis: econômico, padrão e rápido. A Tabela 2.1 apresenta as principais diferenças entre elas.

Tabela 2.1 - Principais diferenças entre as versões do processador NIOS 2.

| Item                         | Econômico  | Padrão      | Rápido      |  |

|------------------------------|------------|-------------|-------------|--|

| Performance a 100MHz         | 15 MIPS    | 64 MIPS     | 113 MIPS    |  |

| Elementos lógicos consumidos | 600 a 700  | 1200 a 1400 | 1400 a 1800 |  |

| Multiplicador em hardware    | Não possui | 3 ciclos    | 1 ciclo     |  |

É possível adicionar lógica personalizada diretamente na unidade lógica aritmética (ULA) do processador; veja na Figura 2.5 o bloco de *Custom Instructions*. Assim, pode-se desenvolver suas próprias instruções, como instruções de ponto flutuante.

Figura 2.5 - Estrutura interna do soft-core NIOS2. Fonte: (ALTERA, 2011k)

Para desenvolver projetos com FPGAs da Altera<sup>®</sup>, utiliza-se o *software* Quartus 2 IDE. Tratase de uma ferramenta para compilação, síntese e análise de projetos escritos em linguagem de descrição de *hardware* ou diagramas esquemáticos, fornecida gratuitamente. Para desenvolver o processador NIOS 2, utiliza-se o *software* SoPC *Builder* (*System on a Programmable Chip*), uma extensão do Quartus 2 IDE. Ele inclui além do núcleo processador NIOS 2, diversos periféricos (ALTERA, 2011c). No processo de desenvolvimento, os periféricos desejados são instanciados no SoPC *Builder*, montando o processador de acordo com sua necessidade. Feito isto, segue-se para a etapa de instanciar o processador desenvolvido pelo SoPC *Builder* dentro do projeto em desenvolvimento no Quartus 2 IDE, utilizando qualquer uma das linguagens aceitas pelo ambiente de desenvolvimento. O projeto deve ser compilado para enfim ser sintetizado no FPGA (ALTERA, 2011l).

Com o circuito sintetizado no FPGA, deve-se desenvolver o *software* que será executado pelo processador. Isso é realizado utilizando o NIOS 2 IDE *Eclipse* e a linguagem C ou C++ para criar o código, contando-se com o apoio de sistemas operacionais de tempo real e bibliotecas de acesso ao *hardware* (HAL, *Hardware Abstraction Layer*).

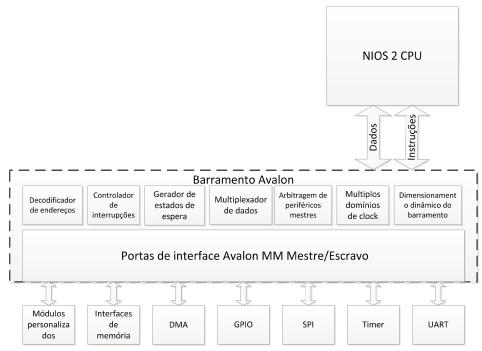

#### Barramento Avalon e Periféricos

Como pode ser visto na Figura 2.6, todas as conexões entre o processador e um periférico são realizadas através do sistema de interconexão, chamado *System Interconnect Fabric Avalon Bus*. Existem dois tipos diferentes de barramentos de dados disponíveis (*Memory Map e Stream*), variando na forma de conexão e manipulação dos dados. Além dos barramentos de dados e suas interfaces, ainda existem as interfaces de *reset*, *clock*, interrupção e sinais externos ao sistema. A interface de interrupção envia uma requisição de interrupção ao processador. A interface de sinais externos, chamada de *Conduit*, tem o objetivo de enviar ou receber sinais externos ao sistema, como por exemplo os sinais de uma comunicação de dados. O funcionamento de cada interface está descrito no manual de especificação do barramento Avalon (ALTERA, 2011a).

De acordo com a especificação deste barramento (ALTERA, 2011a), o tipo *Memory Map* (MM) é baseado em endereços de memória. Toda conexão de um periférico ao barramento MM é realizada através de uma interface MM. Esta interface pode ser de 2 tipos: mestre ou escravo. A interface mestre acessa a interface escrava através do barramento. A interface escrava sempre possui um endereço base e um endereço final, que engloba todos os seus registradores internos. Estes registradores internos podem ser endereços de pequenas memórias internas ao módulo, registradores de controle, de estado, ou qualquer outro registrador que possa ser acessado através de um endereço. A Figura 2.6 apresenta o barramento Avalon MM com seus módulos internos e diversos periféricos do tipo MM, tanto mestres quanto escravos.

Figura 2.6 - Barramento Avalon *Memory Map* e seus módulos internos. Fonte: Adaptado de Altera (2011a)

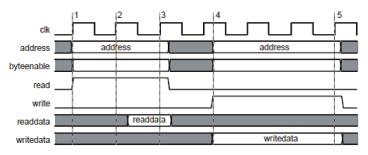

Existem vários sinais envolvidos em uma transação de dados entre uma interface mestre e uma interface escrava. A Figura 2.7 apresenta alguns destes sinais e suas formas de onda durante um comando de leitura e um comando de escrita de dados.

Figura 2.7 - Comando de leitura e de escrita de dados em uma interface Avalon MM. Fonte: (ALTERA, 2011a)

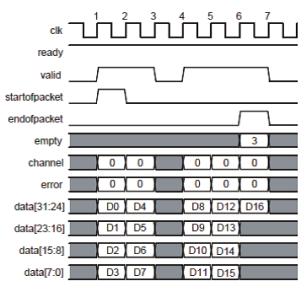

O barramento de fluxo de dados, chamado de *Stream*, tem o objetivo de trocar dados em alta velocidade através de uma interface mais simples. Esta interface pode ser de dois tipos: geradora de dados (*Source*) ou receptora de dados (*Sink*). A interface geradora de dados sempre está conectada a uma interface receptora de dados. Existem diversos periféricos que utilizam esta interface para

transmitir dados de forma mais rápida e sem ocupar o processador para tal tarefa, como os módulos de acesso direto à memória (DMA). A Figura 2.8 apresenta alguns dos sinais envolvidos numa transmissão de dados com a interface *Stream* (ALTERA, 2011a).

Figura 2.8 - Transmissão de dados através da interface Avalon ST. Fonte: (ALTERA, 2011a)

O SoPC *Builder* possui uma variedade de periféricos que podem ser adicionados ao sistema em construção. Dentre eles os mais comumente utilizados são: temporizador, memórias *On-Chip*, memórias FIFO, medidor de desempenho, acesso direto à memória (DMA), controladores de memória (SDRAM, SRAM, FLASH), processador NIOS2, controlador de rede *ethernet*, comunicação serial síncrona e assíncrona, pinos de entrada e saída de uso geral. Cada um destes módulos existentes possui além de sua descrição em *hardware* e importação ao SoPC *Builder*, um modelo no ambiente de programação em C/C++. Neste ambiente é necessário, através de instruções para o processador, configurar e utilizar estes módulos. É preciso conhecer detalhadamente cada periférico utilizado no sistema em criação, para que no momento do desenvolvimento do *software*, ele seja corretamente utilizado (ALTERA, 2011).

#### 2.2.2 Kits de desenvolvimento

A elaboração de todo o projeto foi realizado sobre uma placa de desenvolvimento completa para FPGA, denominada Altera NIOS II *Embedded Evaluation Kit* (NEEK) *Cyclone* III *Edition* (conforme a Figura 2.9), que inclui ferramentas de desenvolvimento de *hardware* e *software*, documentação, acessórios e periféricos necessários para criar sistemas embarcados (ALTERA, 2011h; ALTERA, 2011i).

Figura 2.9 - Kit de desenvolvimento NEEK. Fonte: (ALTERA, 2011h)

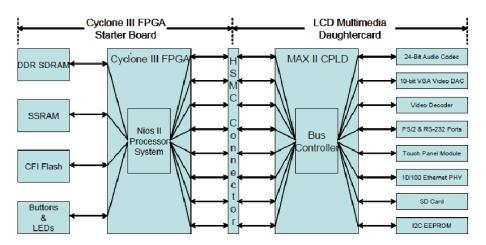

A placa de desenvolvimento inclui um FPGA Altera *Cyclone* III EP3C25F324 préconfigurado com um projeto de *hardware* armazenado na memoria *flash*, assim como várias demonstrações armazenadas no cartão de memória. Toda vez que o sistema é ligado, o *hardware* armazenado na memória *flash* é gravado no FPGA através de um CPLD dedicado a esta função. Após esta gravação, um programa seletor de aplicações é executado sob este *hardware* recém-gravado, permitindo que seja executado um projeto armazenado no cartão de memória. Pode-se criar uma aplicação e armazená-la no cartão de memória, ou utilizar as ferramentas de desenvolvimento para gravar o projeto diretamente no FPGA utilizando um cabo USB. A Figura 2.10 apresenta a estruturação do NEEK, que possui duas placas principais (*Cyclone* III FPGA *Starter Board* e LCD *Multimedia Daughtercard*), onde cada uma delas possui uma variedade de periféricos (ALTERA, 2011h; ALTERA, 2011i).

Figura 2.10 - Periféricos do kit de desenvolvimento NEEK. Fonte: (ALTERA, 2011i)

Visto a parte do dispositivo de *hardware* utilizado, se faz necessário apresentar as ferramentas de *software* que realizam a comunicação e também o projeto de construção do processador que irá processar o algoritmo proposto:

- Quartus 10.1 SP1: utilizado no desenvolvimento dos códigos em VHDL para a descrição e síntese do *hardware*. Também foi utilizada uma extensão chamada SoPC *Builder* que realiza a montagem e a configuração do processador NIOS 2 e seus periféricos. (ALTERA, 2011)

- NIOS 2 IDE 10.1 SP1: ambiente de programação em C/C++, utilizado para criar o *software* que será executado pelo processador NIOS 2, desenvolvido no Quartus 10.1.

# 2.3 Microcontrolador Coldfire FreeScale®

#### 2.3.1 O microcontrolador MCF51CN128

O MCF51CN128 é um microcontrolador de 32 *bits*, núcleo *ColdFire* V1 da Freescale<sup>®</sup>, de baixo custo e consumo, barramento de até 50.33MHz, com 128 KB de memória *flash*, 24KB de memória RAM, um conversor analógico-digital (ADC), que suporta diversos tipos de comunicação,

entre eles a *ethernet*. Ele possui 70 pinos que podem ser utilizados como entrada ou saída. A Figura 2.11 apresenta uma das versões do microcontrolador. (FREESCALE, 2011b)

Figura 2.11 - Microcontrolador MCF51CN128.

O seu conversor analógico-digital possui 12 canais multiplexados, ou seja, apenas um pode ser lido no mesmo instante de tempo. Possui 12 *bits* de resolução e pode chegar a até 2.5 microssegundos de tempo de conversão quando em configurações mais simples. Suporta o modo de conversão contínua, onde realiza conversões em sequência, uma após outra, sem necessidade de um disparo. Também possui a funcionalidade de comparação em *hardware*, o que permite criar um nível de disparo para conversões, o que pode garantir que o primeiro ponto de um sinal seja capturado sempre com o mesmo valor inicial, como em aplicações que requerem sincronismo. A tensão de referência para as conversões é a própria alimentação do microcontrolador, que pode ir de 1.8 V a 3.6 V. O resultado da conversão é sempre proporcional ao valor aplicado, tendo a alimentação como limite. (FREESCALE, 2011b)

#### 2.3.2 Kits de desenvolvimento

A FreeScale<sup>®</sup> oferece uma ferramenta de desenvolvimento para este microcontrolador, o módulo TOWER (TWR-MCF51CN128). Trata-se de um conjunto de placas que quando montados se assemelham a uma torre. É um kit de desenvolvimento modular, onde o usuário pode substituir as placas e montar outras configurações com os módulos existentes. A Figura 2.12 apresenta o TOWER. Existem dezenas de módulos desenvolvidos tanto pelo fabricante do microcontrolador

quanto por terceiros. Estes módulos vão de placas com diferentes microcontroladores a placas com sensores e dispositivos de comunicação. Neste projeto foram utilizados o módulo processador MCF51CN e o módulo de comunicação serial com rede *ethernet*.

Figura 2.12 - Kit de desenvolvimento TOWER.

## 2.4 Sistemas operacionais de tempo real

Projetar aplicações para sistemas embarcados é sempre um desafio. Uma maneira de diminuir a complexidade da aplicação é a utilização de um projeto orientado a tarefas, dividindo o projeto em pequenas tarefas mais simples de serem gerenciadas. Cada tarefa é então responsável por uma parte da aplicação. Com isto, algumas tarefas têm mais prioridade sobre outras, ou seja, possuem requisitos de tempo real para responderem mais rapidamente e corretamente (IAR, 2012).

De acordo com Shaw (2003), um sistema operacional tempo-real (RTOS, *Real Time Operating Systems*) é um programa que agenda a realização de tarefas de maneira temporal, atribuindo prioridades a estas tarefas, gerenciando os recursos do sistema e fornecendo uma base sólida para

o desenvolvimento do código de uma aplicação. Essas aplicações vão de simples brinquedos até sistemas complexos quanto a navegação de uma aeronave.

Então, se uma aplicação utiliza um sistema operacional de tempo real, já estão presentes características que priorizam tarefas em relação a outras. Além disto, existem recursos em um sistema operacional que garantem sincronismo e comunicação entre as tarefas. Ao usar um sistema operacional de tempo real, fica garantido que tarefas críticas com relação ao tempo são executadas dentro de suas restrições (IAR, 2012).

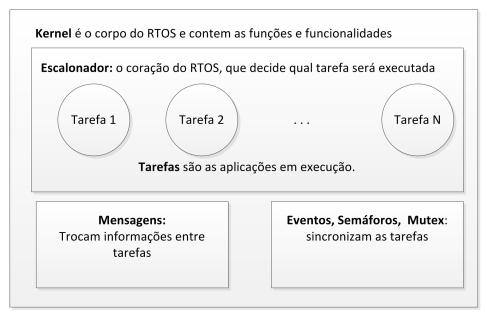

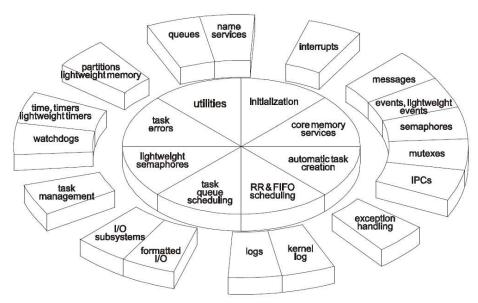

## 2.4.1 Características principais

O núcleo de um RTOS é conhecido como *kernel*. Existem funções chamadas de API (*Application Programming Interface*) que acessam o *kernel* para criar tarefas e recursos do RTOS. O *kernel* também contém um escalonador. O escalonador é responsável por executar as tarefas de acordo com o tipo de escalonamento. A grande diferença entre os tipos de escalonamento é como eles distribuem o tempo do processador, ou seja, a execução do programa, entre as várias tarefas que o escalonador está gerenciando. O tipo mais popular de escalonamento é o preemptivo, baseado em prioridade. Um escalonador preemptivo baseado em prioridade suporta escalonamento tanto preemptivo quanto não preemptivo. Em uma situação preemptiva, uma tarefa de maior prioridade imediatamente interrompe uma tarefa em execução com prioridade menor (IAR, 2012).

A maior parte dos *kernels* utiliza um sistema de temporização por interrupção de geralmente 10ms, a qual é chamada de *tick*. Sem um sistema de *ticks* em um RTOS, o escalonamento simples ainda é possível, porém os serviços baseados no tempo não estão disponíveis. O sistema de *ticks* pode ser implementado com um dos temporizadores em *hardware* implementados no microcontrolador em questão (IAR, 2012).

Uma tarefa é como uma função que tem sua própria pilha (chamadas de funções, variáveis, etc) e um conjunto de dados de controle (*Task Control Block*), que armazenam informações sobre o estado da tarefa (em execução, em espera, etc). Ao contrário da maioria das funções, uma tarefa quase sempre é um laço de repetição infinito, ou seja, uma vez criada, a execução nunca deixará o laço. Uma tarefa que está pronta para ser executada está em um estado de PRONTA (*READY*), ou,

ela pode estar suspensa, esperando algo acontecer antes de entrar no estado de PRONTA. Este estado é chamado de estado de ESPERA (*WAITING*). Cada RTOS pode dar um nome a estes estados, e podem existir outros como executando, terminado, completo (IAR, 2012).

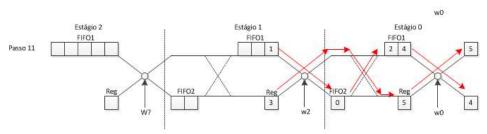

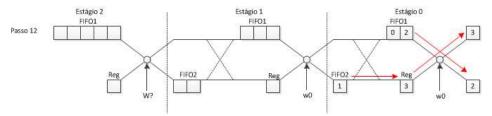

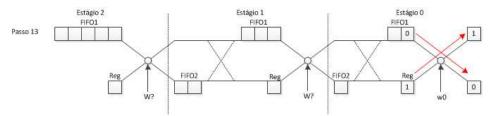

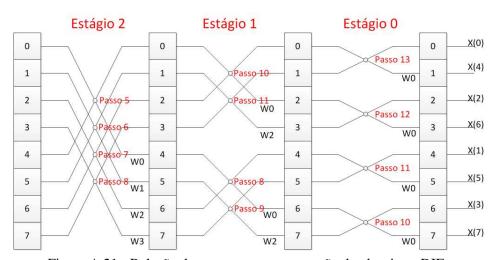

Como dito, existem dois tipos principais de escalonadores. Em um escalonador orientado a eventos (algoritmo de escalonamento com prioridade controlada), cada tarefa possui uma prioridade e a tarefa com a maior prioridade é executada. A ordem de execução depende somente desta prioridade. A regra neste caso é: o escalonador ativa a tarefa que possui a maior prioridade da lista de tarefas prontas para serem executadas (IAR, 2012).