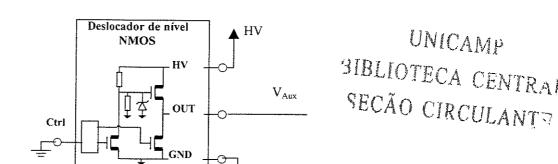

UNICAMI BIBLIOTECA CENTRAL SEÇÃO CIRCULANT

# Universidade Estadual de Campinas

# FACULDADE DE ENGENHARIA ELÉTRICA E DE COMPUTAÇÃO

# DEPARTAMENTO DE MICROELETRÔNICA

# INTEGRAÇÃO INTELIGENTE DE POTÊNCIA BASEADA EM TRANSISTORES NMOS

Saulo Finco

Este exemplar corresponde a redação final da tese defendida por <u>SAULO FINCO</u>

e e prosesda colla Comissão

Julgada em <u>16</u>

06 2000 Sillmon Mueno de Fre

Orientador: Prof. Dr. Wilmar Bueno de Moraes

DEMIC - FEEC - UNICAMP

Co-Orientadores: Prof. Dr. Frank Herman Behrens

Prof. Dra. Maria Inês Silva de Castro Simas

## Comissão Julgadora:

Prof. Dr. Wilmar Bueno de Moraes - FEEC/UNICAMP

Prof. Dr. Peter Jünger Tatsch - FEEC/UNICAMP

Prof. Dr. Carlos Ignácio Zamitti Mammana - Fundação CTI

Prof. Dr. Renato Ribas - UFRGS

Prof. Dr. Nicolau Jannuzzi - Fundação CTI

Prof. Dr. Alberto Martins Jorge - FEEC/UNICAMP

Dissertação apresentada como parte integrante dos requisitos necessários para a obtenção do Título de Doutor em Engenharia Elétrica, na área de concentração ELETRÔNICA, MICROELETRÔNICA E OPTOELETRÔNICA, à Comissão Julgadora da Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas.

Campinas, 16 de Junho de 2000

ONICABE

CM-00153703-0

## FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

F492i

Finco, Saulo

Integração inteligente de potência baseada em transistores NMOS / Saulo Finco.--Campinas, SP: [s.n.], 2000.

Orientador: Wilmar Bueno de Moraes. Co-orientadores: Frank Herman Behrens, Maria Inês Silva de Castro Simas.

Tese (doutorado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Circuitos integrados. 2. Transistores de potência.

3. Eletrônica de potência. 4. Microeletrônica. 5. Sistemas eletrônicos analógicos. I. Moraes, Wilmar Bueno de. II. Behrens, Frank Herman. III. Castro Simas, Maria Inês de IV. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. V. Título.

# UNICAMP SIBLIOTECA CENTRAI SEÇÃO CIRCULANTE

#### Resumo

Este trabalho está relacionado com importantes progressos no projeto de Circuitos Integrados Inteligentes de Potência usando agregados, fundamentados em uma única célula básica contendo transistores NMOS. Tais agregados estão associados de forma matricial adequada para implementar funções genéricas requeridas pelos circuitos de controle de potência. Esta técnica permite o projeto de novos CIs semidedicados de baixo custo, proporcionando uma nova estratégia de configuração de ICs que permite uma fácil implementação industrial em direção à integração Inteligente de Potência utilizando tecnologias CMOS convencionais digital/analógica, sem nenhuma etapa adicional de processo. A mesma técnica pode também ser aplicada a tecnologias complexas e sofisticadas dedicadas à integração de Circuitos Inteligentes de Potência (Smart Power Technologies), para a prototipagem rápida ou produção em escala industrial destes circuitos. No cenário mundial, um grande esforço têm sido realizados para compatibilizar a integração inteligente de potência com processos CMOS convencionais de baixo custo. Os resultados apresentados comprovam a potencialidade da técnica desenvolvida neste trabalho em muitos nichos de aplicação.

#### **Abstract**

This work is related to important improvements in Smart Power design using arrays based on a unique NMOS cell type. These arrays are arranged in matrices that can implement generic functions required by power control blocks, thus enabling low cost semicustom designs. This new IC configuration strategy has an easy industrial implementation towards Smart Power using standard digital/analog CMOS technologies, without any additional processing steps. The same method can also be applied to sophisticated Smart Power technologies, for fast prototyping or even for industrial production. A huge worldwide effort is being carried out to find solutions that may render Smart Power circuits compatible with low cost CMOS technologies. The results show potentialities of these techniques for many niche of applications.

### Agradecimentos

Sou grato a um grande número de colaboradores e instituições que no transcorrer do desenvolvimento deste trabalho contribuíram com maior ou menor intensidade para a sua realização, através de um simples comentário ou questionando-me com uma visão crítica mais profunda, ou, de outra forma, simplesmente tendo paciência e amizade. Não sendo possível agradecer a todos nominalmente ao menos gostaria de explicitamente agradecer:

À Fundação Centro Tecnológico para Informática — CTI, que abrigou este trabalho dentro de seus projetos institucionais, propiciando suporte de inestimável valor, em termos materiais, laboratoriais, através de convênios internacionais, pelas participações em congressos internacionais, pelo patrocínio do Projeto Multiusuário Brasileiro — PMU, entre outras ações. Particularmente agradeço o Prof. Dr. Carlos I. Z. Mammana, presidente da Fundação CTI, por ter proposto a semente deste trabalho e pelo apoio demonstrado em todas as fases importantes.

À coordenação do Programa de Cooperação Internacional Institucional entre o CNPq (Brasil)/ICCTI (Portugal) permitindo o intercâmbio entre pesquisadores da Fundação CTI, Campinas, Brasil, e do Instituto de Telecomunicações - IT do Instituto Superior Técnico – IST, Lisboa, Portugal. Ao suporte dado pelo programa PMU - Fapesp.

Aos meus orientadores Prof. Dr. Wilmar Bueno de Moraes, da FEEC-DEMIC-UNICAMP, à Prof. Dra. Maria Inês Castro Simas, do IT-IST, e ao Prof. Dr. Frank H. Behrens da PUCCAMP, que em momento algum mediram esforços pessoais para a concretização deste trabalho. Recordo-me que seus incentivos, críticas, sugestões e ensinamentos sempre foram colocados de forma tranqüila e prazerosa.

Ao Dr. Pierre Rossel, Dr. Georges Charitat e Dr. Nicolas Nolhier, companheiros de trabalho do LAAS/CNRS-França, pelas discussões iniciais deste trabalho. Ao Prof. Dr. Carlos A. dos Reis da UNICAMP pela aplicação experimental deste trabalho em seus desenvolvimentos técnicos.

Aos companheiros de trabalho pelas valorosas contribuições durante a redação e composição deste trabalho: Pedro N. M. Santos, António Pedro A. Casimiro e Paulo Tavares, pesquisadores do Instituto de Telecomunicações do Instituto Superior Técnico; Carlos de Oliveira, Pimentel, Márcio, Wellington, Cleomar, Susete, Marinalva, Elaine e Mariana, da Fundação CTI. Ao amigo João Costa Freire e família pela compreensão e apoio.

À minha querida esposa, ao meu filho e pela paciência, compreensão e muito carinho...

Aos meus queridos pais por terem sustentado meus estudos ao longo de minha vida.

Ao nosso Deus Criador e Mantenedor, pela vida, saúde e cuidados que teve para comigo durante as inúmeras jornadas estendidas de trabalho. Muito obrigado!

# Índice

| Capítulo 1 - Introdução ger | AI |

|-----------------------------|----|

|-----------------------------|----|

| 1.1 INTRODUÇAO                                                                 |               |

|--------------------------------------------------------------------------------|---------------|

| 1.2 MOTIVAÇÃO                                                                  |               |

| 1.3 Objetivos                                                                  |               |

| 1.4 Organização                                                                |               |

| 1.5 Referências                                                                |               |

|                                                                                | *********     |

|                                                                                |               |

| CAPÍTULO 2 - A INTEGRAÇÃO DE POTÊNCIA, TECNOLOGIAS E APLICAÇÕES                |               |

| 2.1 Introdução                                                                 | 15            |

| 2.2 CONCEITOS BÁSICOS                                                          | 17            |

| 2.3 TECNOLOGIAS DEDICADAS À INTEGRAÇÃO DE POTÊNCIA                             | 10            |

| 2.3.1 Tecnologias MOS                                                          | 10            |

| 2.3.1.1 Circuitos Integrados Inteligentes de Potência                          | 19            |

| 2.3.1.2 Circuitos Integrados de Alta Tensão                                    | ± 0           |

| 2.3.2 Tecnologias BiCMOS                                                       | 22            |

| 2.3.3 Tópicos sobre Isolamento                                                 | 72            |

| 2.3.3.1 Auto-isolamento                                                        | 72            |

| 2.3.3.2 Isolamento por Junções Verticais                                       | ~~~~~~~<br>^A |

| 2.3.3.3 Isolamento por Dielétrico                                              | 25            |

| 2.4 DESCRIÇÃO DE ALGUNS PROCESSOS COMERCIAIS                                   |               |

| DEDICADOS À INTEGRAÇÃO DE POTÊNCIA                                             | 27            |

| 2.4.1 BCD V, Tecnologia da SGS-THOMSON                                         | 26            |

| 2.4.2 SmartMOS, Tecnologia TMOS da Motorola                                    | 30            |

| 2.4.3 BCD5, Tecnologia da MICREL                                               | 32            |

| 2.4.4 TrenchFETs, Tecnologia da TEMIC                                          | 32            |

| 2.4.5 Considerações sobre as Novas Tecnologias em Desenvolvimento              | 33            |

| 2.5 INTEGRAÇÃO INTELIGENTE DE POTÊNCIA.                                        | 34            |

| 2.5.1 Controle da Potência                                                     | 34            |

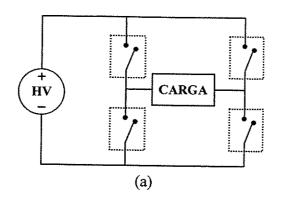

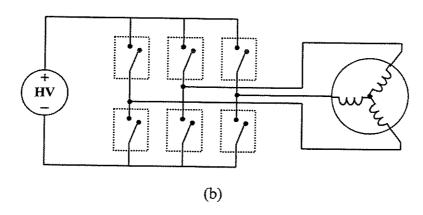

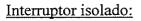

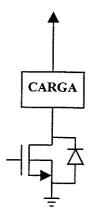

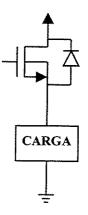

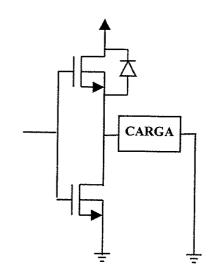

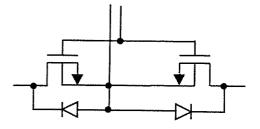

| 2.5.1.1 Topologias de Carga e de Interruptor                                   | 34            |

| 2.5.1.2 Concretização dos Interruptores                                        | 3.8           |

| 2.5.1.3 Circuitos de Acionamento e suas Topologias                             | 40            |

| 2.5.2 Circuitos de Controle de Proteção                                        | 41            |

| 2.6 DESAFIOS PARA INOVAÇÃO                                                     | 41            |

| 2.6.1 Evolução dos Dispositivos de Potência nas Tecnologias CMOS Convencionais | 44            |

| 2.6.2 Dispositivos Laterais NMOS                                               | 47            |

| 2.6.2.1 Descrição Detalhada                                                    | 48            |

| 2.6.2.2. Modelamento dos Dispositivos Laterais                                 | 49            |

| 2.6.3 Alguns Resultados Experimentais Preliminares                             | 49            |

| 2.6.4. Alguns Resultados Experimentais                                         | 51            |

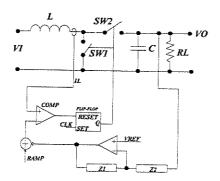

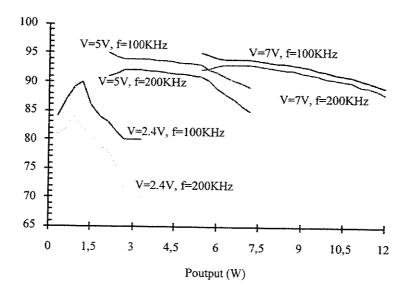

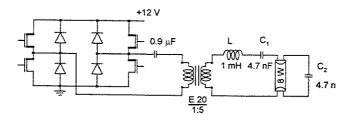

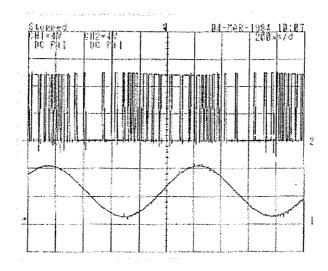

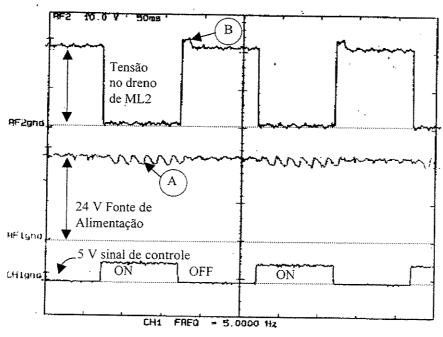

| 2.6.4.1 Regulador DC-DC tipo Ampliador (Boost)                                 | 51            |

| 2.6.4.2 Reator Eletrônico para Lâmpada Fluorescente                            | 53            |

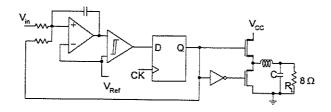

| 2.6.4.3 Amplificador Sigma-Delta                                               | 54            |

| 2.7 CONCLUSÕES                                                                 | 55            |

| 2.8 Referências                                                                | 56            |

|                                                                                |               |

## CAPÍTULO 3 - CIRCUITOS PARA O CONTROLE DE POTÊNCIA BASEADOS EM TRANSISTORES NMOS

| 3.1 Introdução                                                           | 6            |

|--------------------------------------------------------------------------|--------------|

| 3.2 CIRCUITOS PARA O CONTROLE DE POTÊNCIA                                | 63           |

| 3.2.1 Circuitos de Retificação, Retenção, Limitação e Regulação          | 64           |

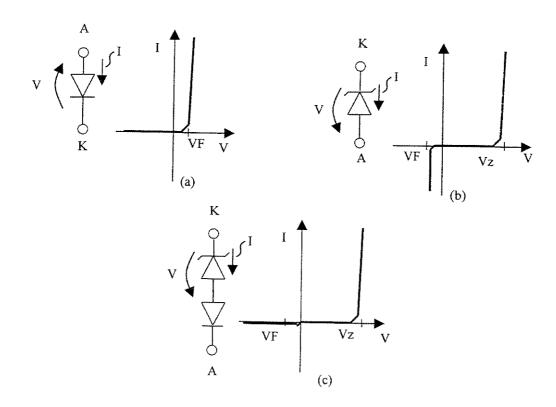

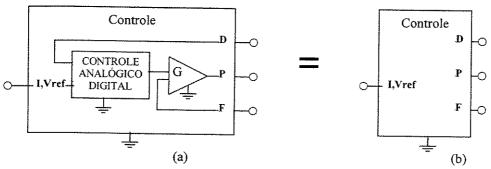

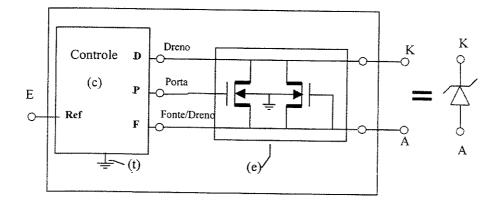

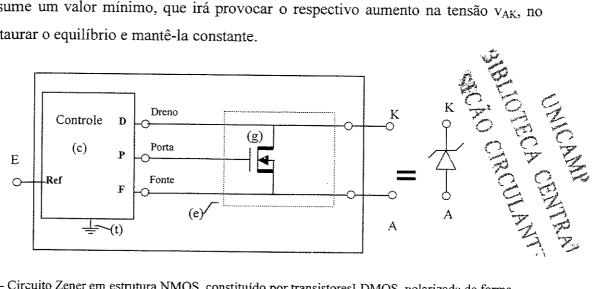

| 3.2.1.1 Circuitos Zener Baseados Unicamente em Transistores NMOS         | 60           |

| 3.2.1.2 Circuitos Retificadores Baseados Unicamente em Transistores NMOS | 6            |

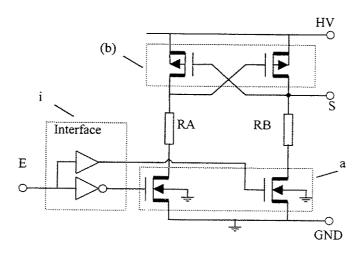

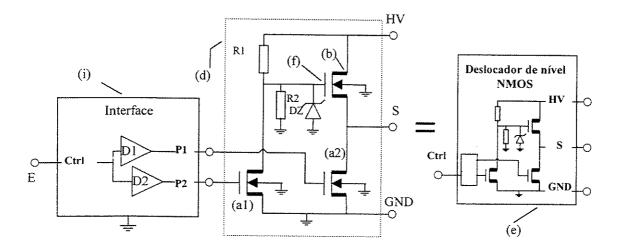

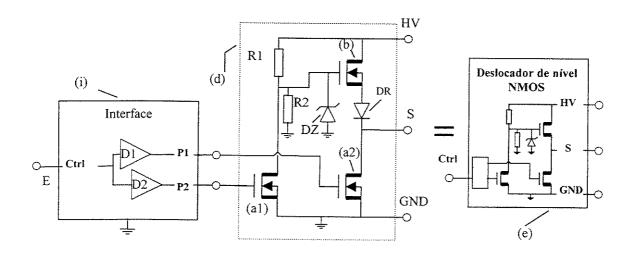

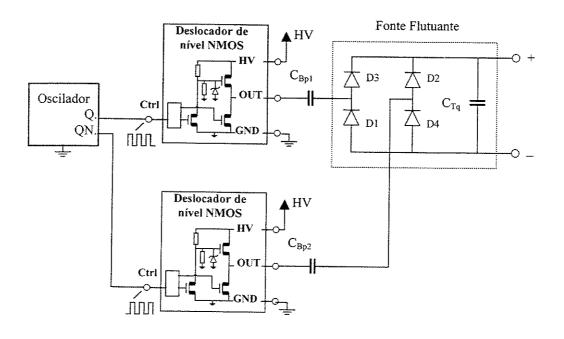

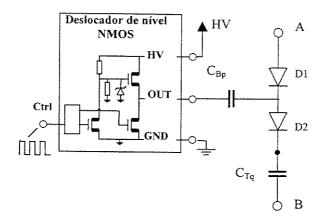

| 3.2.2 Circuitos de Deslocamento de Nível Baseados em Transistores NMOS   |              |

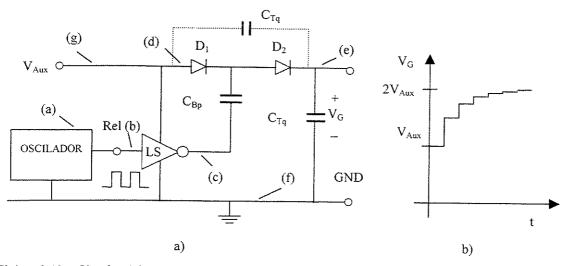

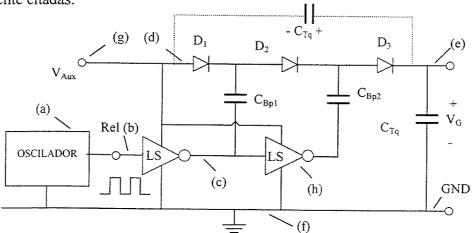

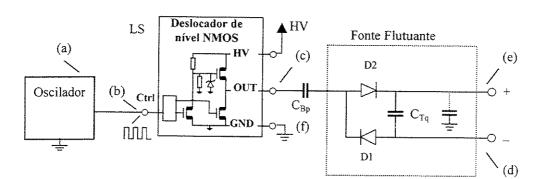

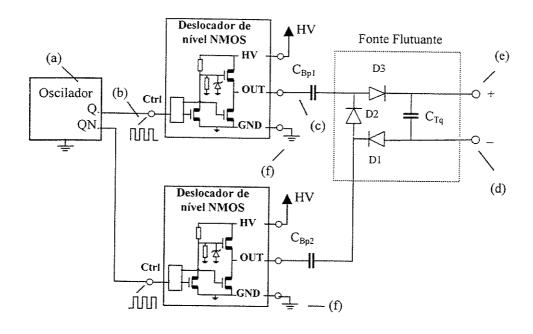

| 3.2.3.1 Circuitos de Bombeamento de Cargas Capacitivos (Charge Pump)     | 74           |

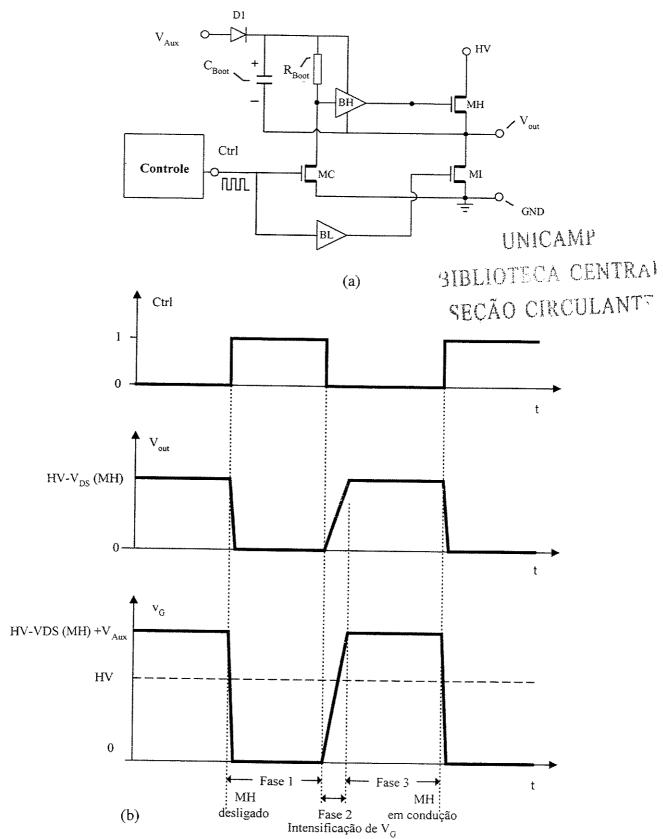

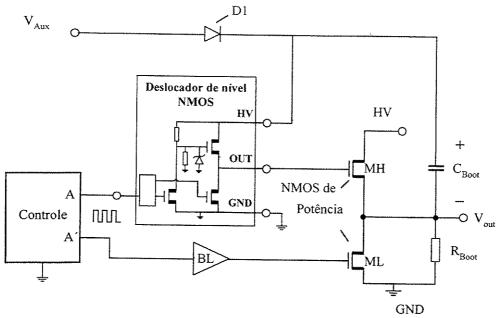

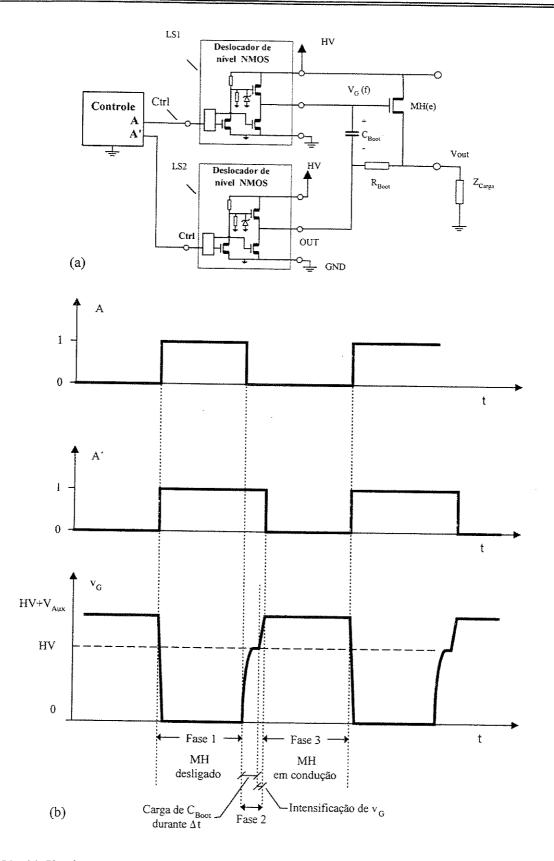

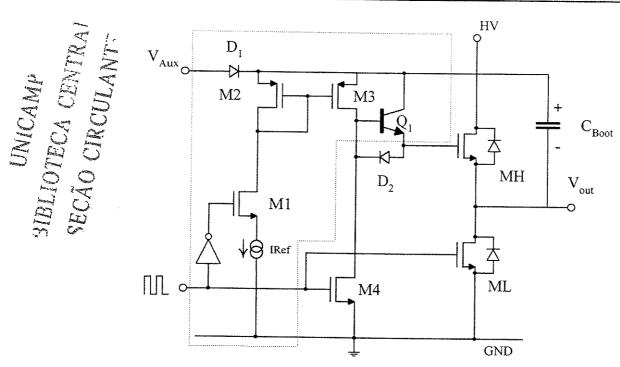

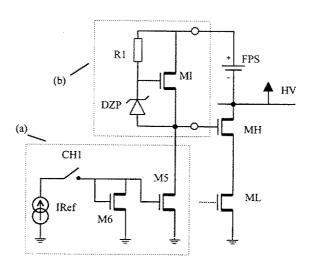

| 3.2.3.2 Circuitos de Intensificação de Excitação (Bootstrap)             | <i>7</i> 9   |

| 3.2.4 Fontes de Corrente Baseadas Unicamente em Transistores NMOS        | 85           |

| 3.3 IMPLEMENTAÇÃO FÍSICA DE CIRCUITOS NMOS PARA APLICAÇÃO EM CIIP        | 8            |

| 3.3.1 Especificações Gerais da Arquitetura de uma Matriz Semidedicada    |              |

| para Aplicações em Potência.                                             | 90           |

| 3.3.1.1 Pré-requisitos:                                                  | 91           |

| 3.3.1.2 Restrições:                                                      | 9            |

| 3.3.1.3 Características Desejadas                                        | 92           |

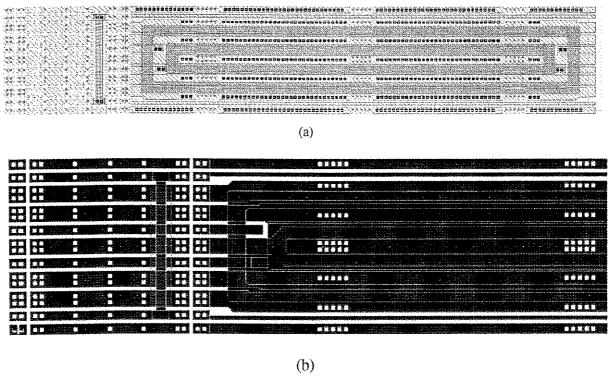

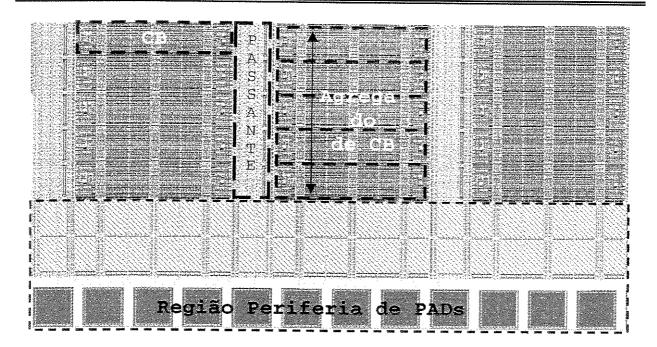

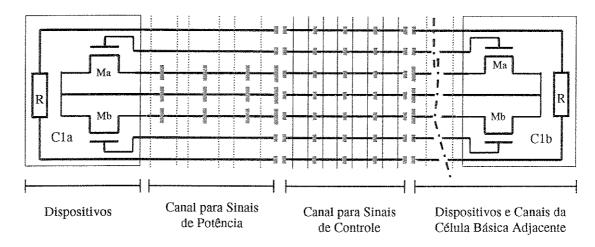

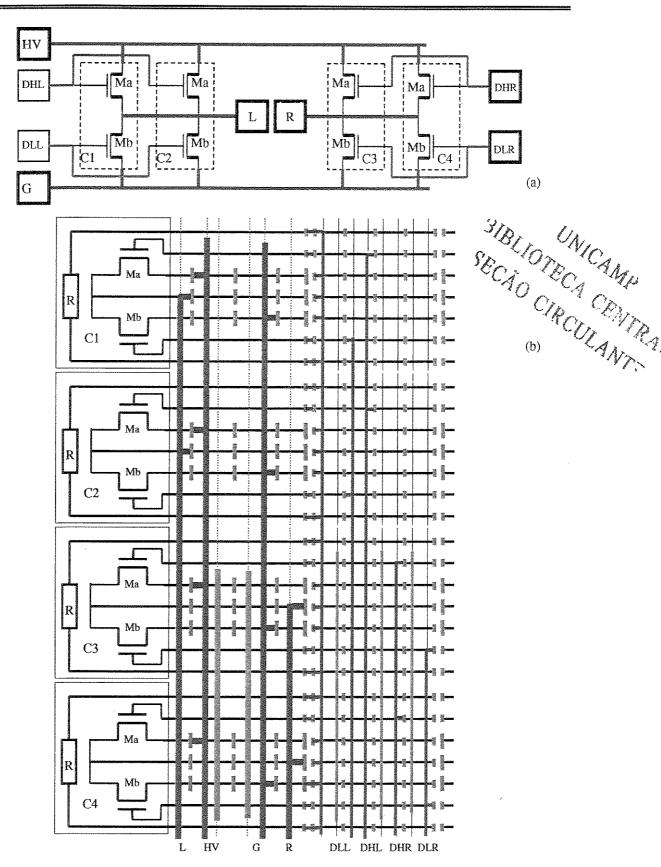

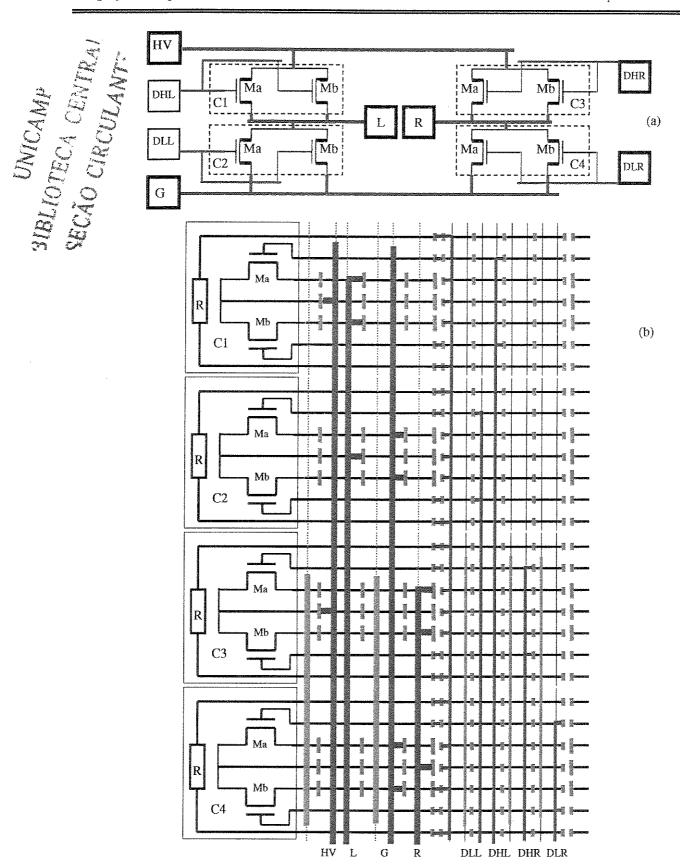

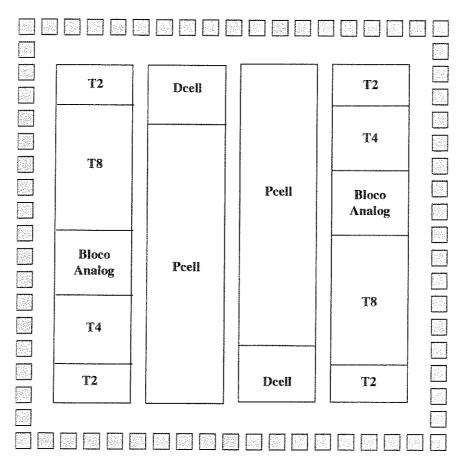

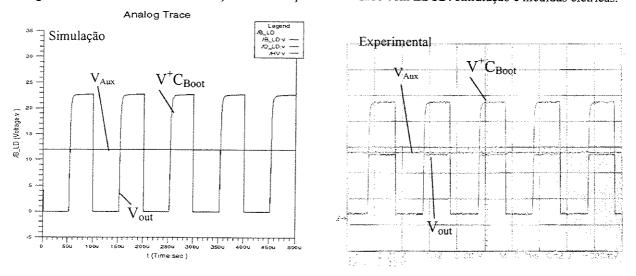

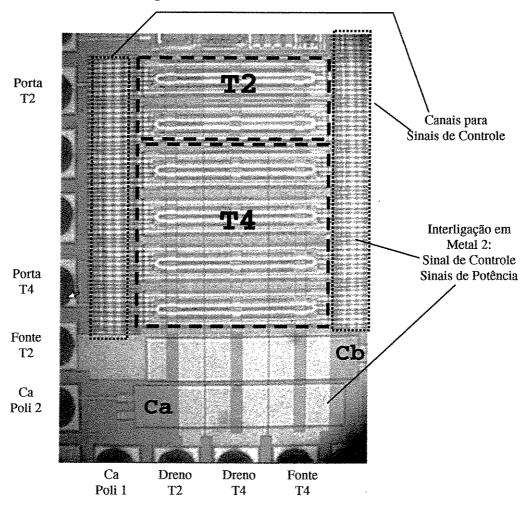

| 3.3.2 Arquitetura da Planta da Célula Básica de Comutação                | 93           |

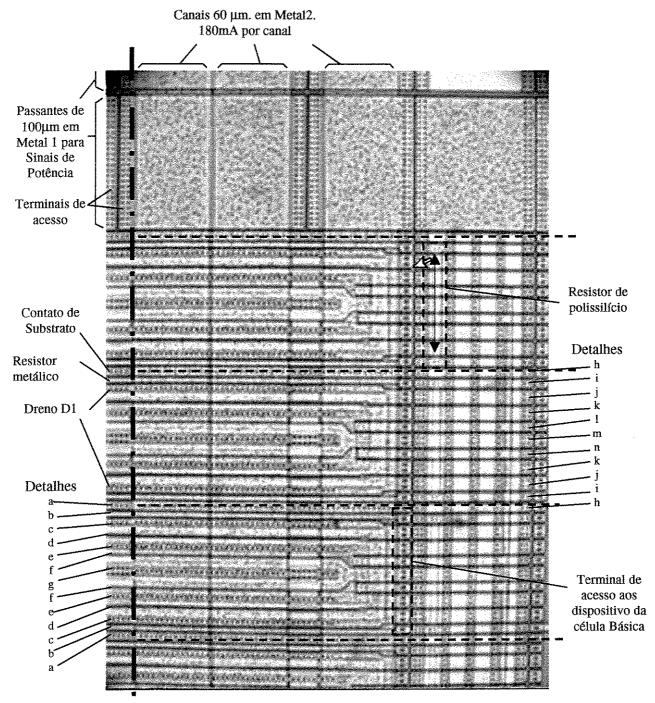

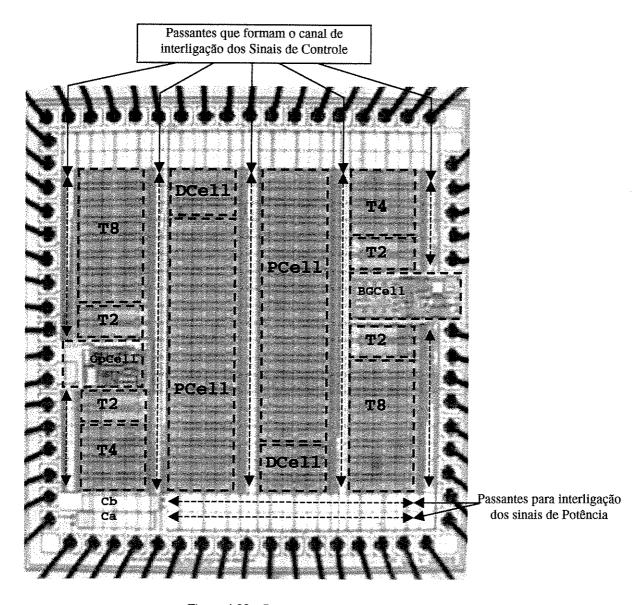

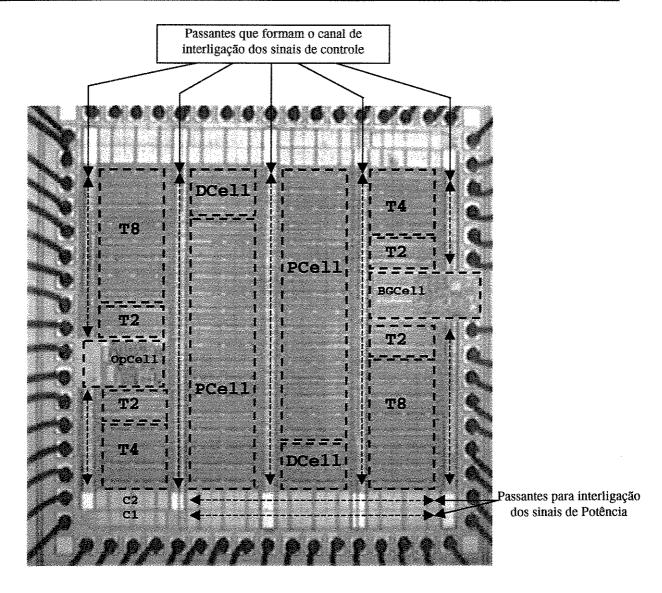

| 3.3.3 Arquitetura da Matriz de Células Básicas                           | 98           |

| 3.3.4 Considerações sobre o Desenho das Máscaras                         | 99           |

| 3.3.4.1 Exemplos de Roteirização de Ligações                             | 100          |

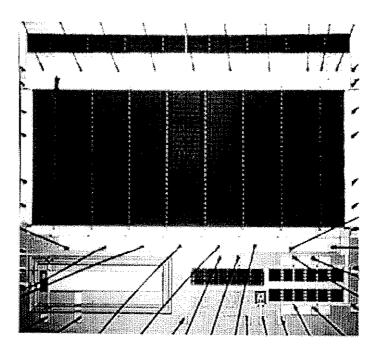

| 3.3.4.2 Planta Final                                                     | 106          |

| 3.4 CONCLUSÃO                                                            |              |

| 3.3 REFERÊNCIAS                                                          | 109          |

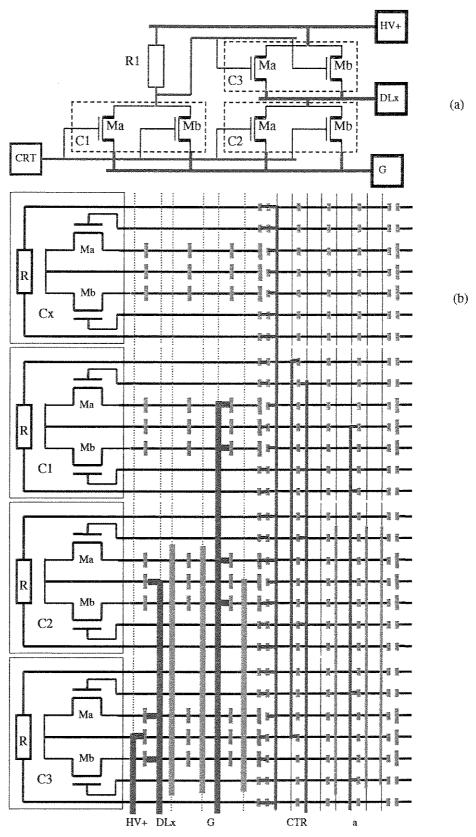

| 4.1 INTRODUÇÃO                                                           | د 112<br>112 |

| 4.2 CIRCUITOS PARA O CONTROLE DE POTÊNCIA                                | 116          |

| 4.2.1 Circuitos de Retificação, Retenção, Limitação e Regulação          | 116          |

| 4.2.1.1 Circuitos Zener                                                  | 120          |

| 4.2.1.2 Circuitos Retificadores                                          | 121          |

| 4.2.1.3 Associação Série de Circuitos Zener com Retificador              | 122          |

| 4.2.2 Circuitos de Deslocamento de Nível                                 | 123          |

| 4.2.3 Circuitos de Excitação                                             | 124          |

| 4.2.3.1 Circuitos de Bombeamento de Cargas                               | 124          |

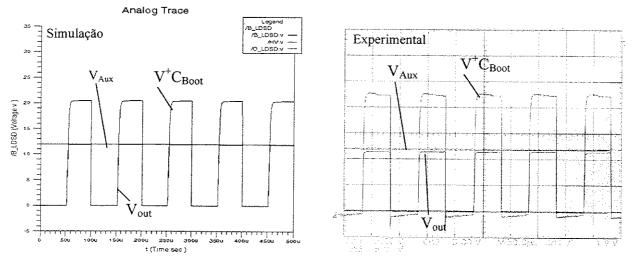

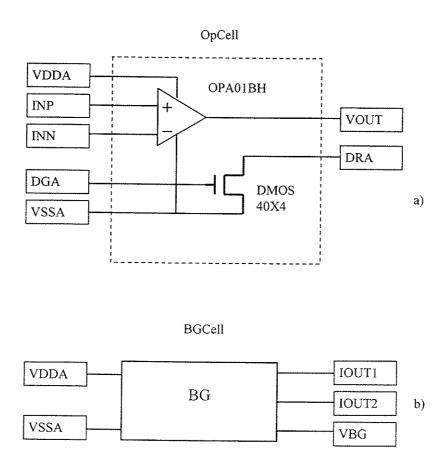

| 4.2.3.2 Circuitos de Intensificação de Excitação                         | 126          |

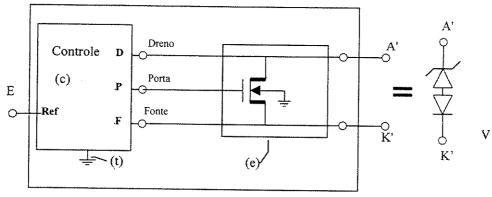

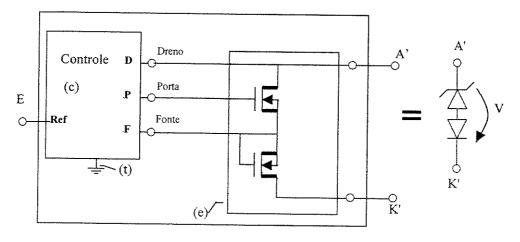

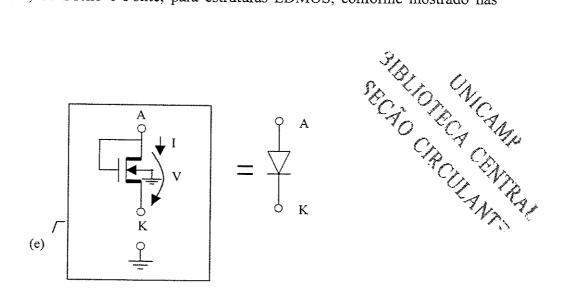

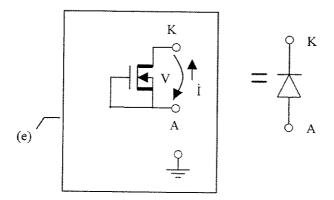

| BASEADAS EM ESTRUTURAS LDSD E LDMOS                                      | 100          |

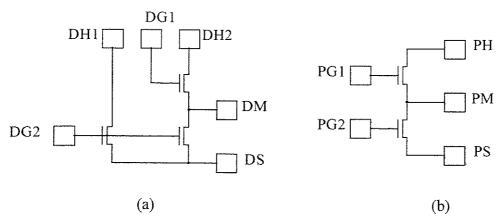

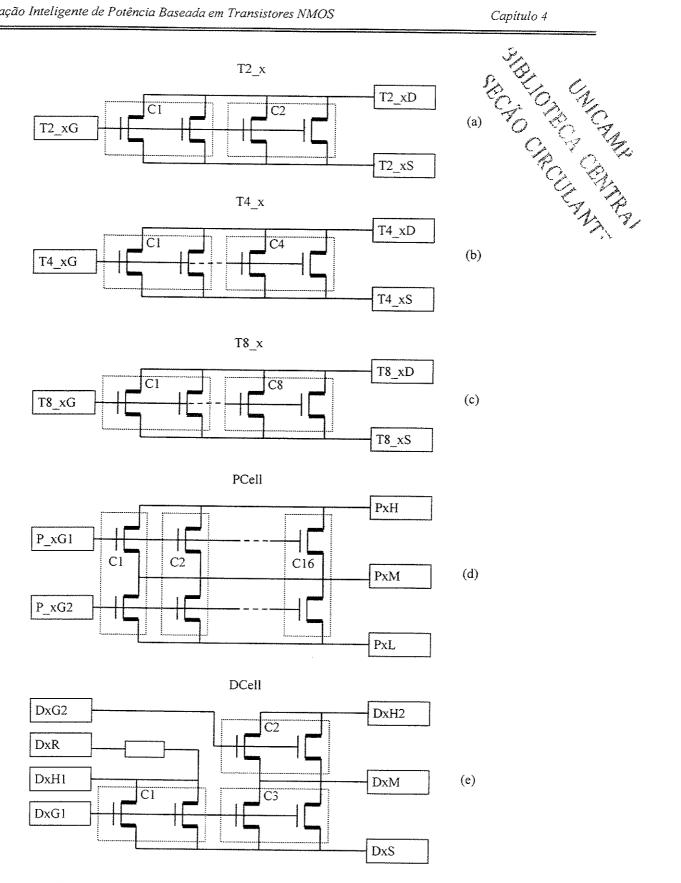

| 4.3.1 Esquema Elétrico das Células de Potência                           |              |

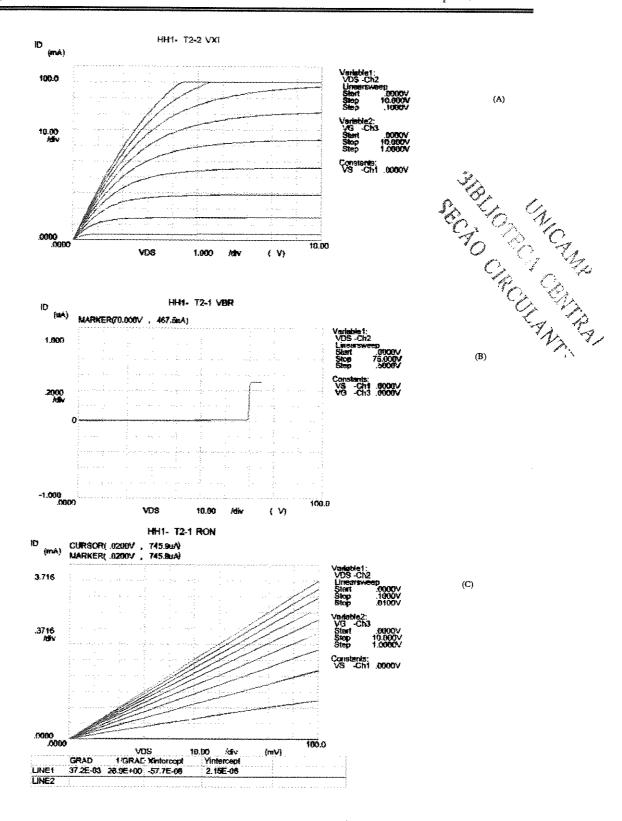

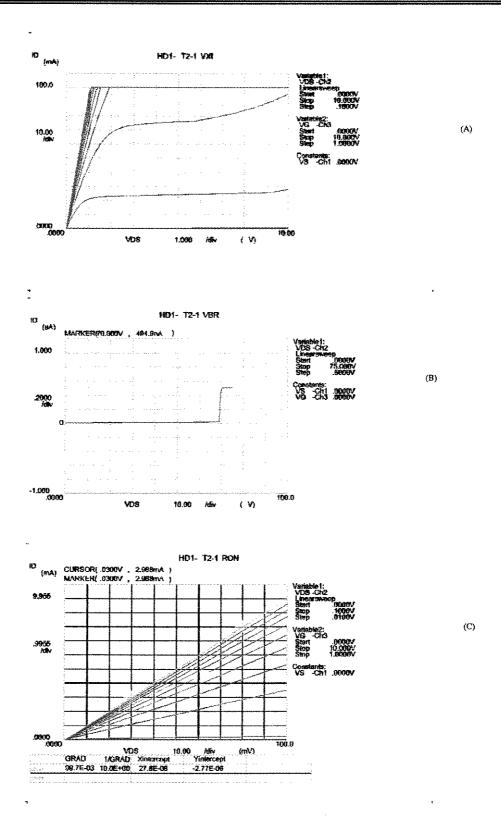

| 4.3.2 Características Elétricas das Células de Potência                  | 127          |

| 4.3.3 Planta das Células de Potência, dos Agregados e das Matrizes       | 131<br>125   |

| 4.4 EXEMPLOS DE CIRCUITOS DE APLICAÇÃO                                   | 140          |

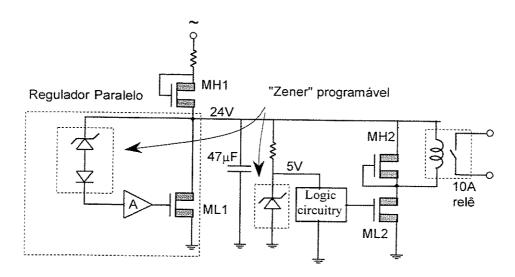

| 4.4.1 Fonte de alimentação 24V DC                                        | 140<br>141   |

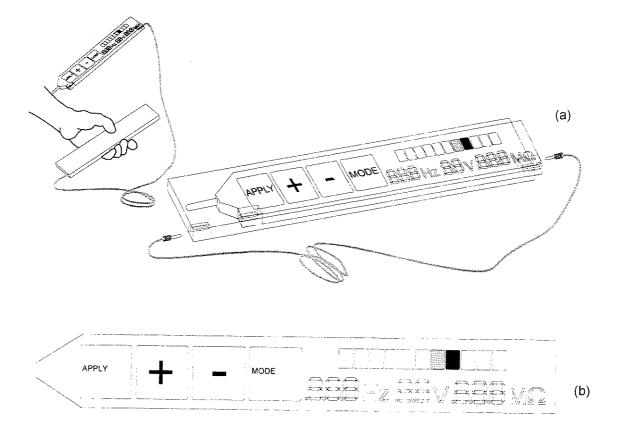

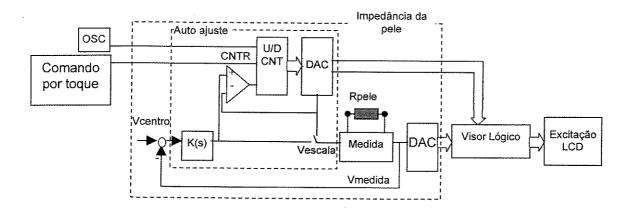

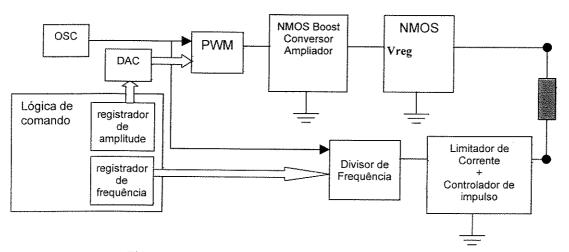

| 4.4.2 Micro-sistema para Estimulação Terapêutica                         | 141<br>142   |

| 4.4.3 Sistema para Indústria Automotiva                                  | 143<br>140   |

| 4.5 CONCLUSÕES                                                           | 140<br>150   |

| 4.6 Referências                                                          | 150          |

|                                                                          | 132          |

| Capítulo 5 - Conclusão Geral                                             |              |

| 5.1 Recapitulação                                                        | 155          |

| 5.2 TEMAS PARA DESENVOLVIMENTO FUTURO                                    | 157          |

| 5.3 HISTÓRICO SOBRE OS PRINCIPAIS TRABALHOS PUBLICADOS                   | 159          |

|                                                                          |              |

1

# Introdução Geral

Onde se apresenta de forma concisa o contexto, a motivação, os objetivos e a forma da organização e apresentação deste trabalho.

# Capítulo 1

# Introdução Geral

| 1.1 Introdução  | 3 |

|-----------------|---|

| 1.2 MOTIVAÇÃO   |   |

| 1.3 Objetivos   |   |

| 1.4 Organização |   |

| 1.5 REFERÊNCIAS | 9 |

### 1.1 Introdução

A atual tendência de evolução no sentido do desenvolvimento de micro-sistemas, i.e., de CIs que realizam as funções de um sistema em um único circuito monolítico, conduz à integração de circuitos de controle analógicos, digitais e dispositivos de comutação, em uma única pastilha, com capacidade de controlar a potência fornecida a uma determinada carga. Este tipo de CIs é conhecido na literatura técnica anglo-saxônica como circuito monolítico *Smart Power* [1.1] e também freqüentemente será denominado no âmbito deste trabalho como Circuitos Integrados Inteligentes de Potência ou simplesmente CIIP. Fatores como a diminuição das dimensões do encapsulamento e número de pinos de ligação ao exterior, das interferências eletromagnéticas [1.1] [1.2], volume, e fundamentalmente o custo global do sistema com melhoria da funcionalidade [1.3], têm motivado o desenvolvimento destes CIs.

Há um grande número de sistemas eletrônicos que requerem o desenvolvimento de Circuitos Integrados de Aplicação Específica - ASICs. A escolha entre o tipo de ASIC semipersonalizado ou totalmente personalizado para realizar uma determinada função é condicionada pelo compromisso entre custo, tempo de desenvolvimento e desempenho pretendido. O tempo e o custo de desenvolvimento de um ASIC totalmente personalizado é superior ao de um ASIC semipersonalizado mas, em contrapartida, os circuitos assim produzidos podem atingir maior desempenho com menor área de silício e menor custo de produção em grandes volumes de utilização [1.4].

Os ASICs semipersonalizados configuráveis por máscaras, dedicados à integração de sistemas inteligentes de potência, são freqüentemente utilizados em aplicações em que o volume de produção é pequeno [1.5] e/ou em que o tempo de prototipagem ou desenvolvimento deve ser reduzido, ou ainda, para a validação final do projeto do CI. Estes ASICs são uma alternativa de construção de sistemas integrados em substituição aos sistemas híbridos que contêm CIs e componentes de potência discretos, ou atuam como uma via otimizada para o desenvolvimento de um ASIC totalmente personalizado. No mercado já existem estes tipos de componentes configuráveis por máscara há mais de 10 anos, em que os dispositivos dedicados ao processamento de potência são essencialmente transistores LDMOS [1.6].

Desde 1986 têm sido apresentadas algumas tecnologias LSI que combinam transistores Bipolares/CMOS/LDMOS [1.7]. As propriedades do transistor de potência LDMOS permitindo o suporte de tensões elevadas no corte e a possibilidade de integração monolítica de múltiplas células de comutação controladas por circuitos Bipolares ou CMOS, foram as principais condicionantes técnicas motivadoras do avanço do uso da tecnologia de *smart power* no mercado. Porém, os custos deste processo, que exige etapas adicionais às necessárias para a fabricação de circuitos puramente analógico/digitais Bipolares, ou CMOS, o consumo de área e a complexidade dos projetos, inicialmente apresentaram-se como um entrave ao avanço daquela tecnologia no mercado de CIs devido ao aumento dos custos da ordem de 1,5 a 10 vezes [1.5], [1.9], até o início da década de 90, quando comparado com a concretização do sistema com componentes discretos ou com os equivalentes eletromecânicos. Este panorama é antagônico ao panorama previsto para os fins dos anos 90 e início da próxima década, segundo o qual, os sistemas eletrônicos otimizados em custo e desempenho conteriam CIIP.

Também é cada vez mais evidente que a prototipagem rápida será uma necessidade no desenvolvimento de um CIIP da mesma forma como ocorre em toda a indústria eletrônica de ASICs hoje em dia. A dificuldade no acesso às tecnologias para potência, principalmente devido ao seu alto custo e ao longo ciclo de projeto desde a especificação até à obtenção de protótipos, levam os projetistas de CIIP a terem dificuldade em testar suas idéias rapidamente, mesmo com um desempenho não otimizado. Considerando que esta fase de verificação da consistência do projeto é uma atividade importante no desenvolvimento de um CIIP, a disponibilidade de um serviço de prototipagem rápida deste circuito traz aos projetistas a possibilidade de uma primeira avaliação da possibilidade de integração de suas idéias antes de iniciar um trabalho de refinamento e otimização do projeto.

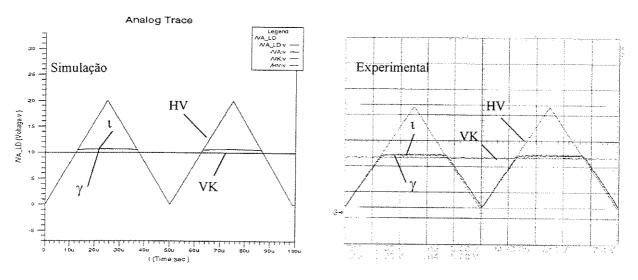

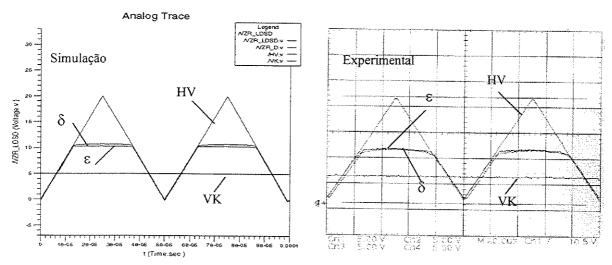

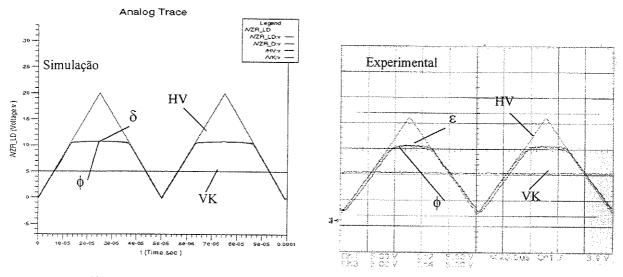

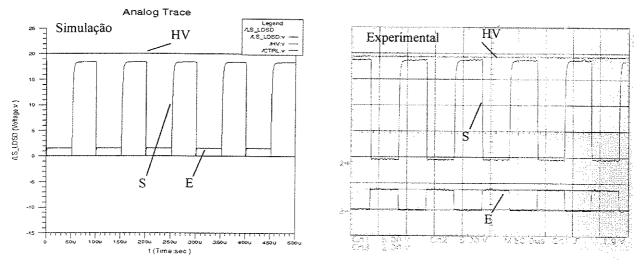

Este trabalho baseia-se nos resultados de simulação e resultados experimentais obtidos de estruturas NMOS, que suportam alta tensão (HV), que são totalmente compatíveis com a tecnologia CMOS digital e que realizam funções similares às funções dos transistores LDMOS construídos em tecnologias combinadas no que se refere ao suporte de correntes na condução e de tensões no corte, de tempos de comutação [1.9]. Este trabalho visa alcançar aplicações de sistemas inteligentes de potência que operem em gamas de tensões até 50V e de corrente até 2A.

### 1.2 Motivação

As características específicas das topologias de conversão de potência, regulação e amplificação tornam possível pensar em um arranjo básico de células de comutação de potência e de funções elementares pré-difundidas, que podem ser configuradas de acordo com os requisitos de cada aplicação com o objetivo de obter uma solução versátil, compatível com a produção de poucas unidades, redução de custos e do ciclo de projeto, usando técnicas semelhantes às utilizadas em circuitos configuráveis tais como os *Field-Programmed Gate Arrays* (FPGAs) e *Mask-Programmed Gate Arrays* (MPGAs).

Tecnicamente a tecnologia CMOS não é, atualmente, a mais adequada para a fabricação de circuitos monolíticos inteligentes de potência, mas fatalmente irá drenar a maior parte das aplicações de baixa/média potência. A integração destes sistemas em tecnologia CMOS é, assim, um desafio atual e exigirá dos engenheiros e projetistas de sistemas o desenvolvimento de novas técnicas e de novas topologias passíveis de adaptarem esta tecnologia às funcionalidades específicas exigidas pelos CIIP [1.8].

A principal motivação deste trabalho foi a de introduzir a capacidade de configuração por máscara em circuitos integrados de potência compatíveis com processos CMOS convencionais. Em conformidade com esta motivação, surgiu a necessidade de gerar padrões que possam ser associados de forma repetitiva e otimizada e que possibilitem a concretização de todas as funções exigidas pelos CIIP através da configuração pós-fabrico de um circuito integrado pré-definido. Esta preocupação visa uma rentável utilização da área de silício ao mesmo tempo que disponibiliza uma metodologia de prototipagem rápida e válida para um grande número de tecnologias possíveis de ser utilizadas no seu fabrico.

Parte desta dissertação pode ser considerada como um estudo de viabilidade de uma alternativa para a integração de sistemas inteligentes de potência configuráveis baseado numa tecnologia puramente CMOS, seguindo assim a tendência de migração dos sistemas eletrônicos para esta tecnologia, pressionados pelos baixos custos de produção em larga escala. Esta solução torna exequível o conceito de prototipagem de CIIP, acima apresentado.

Tipicamente existem dois caminhos para o desenvolvimento de Circuitos Integrados Inteligentes de Potência [1.5]. O primeiro trata de desenvolver uma tecnologia capaz de concretizar uma família de dispositivos de potência e agregar a estes circuitos de alta densidade e baixa tensão para realizar as funções de controle. O segundo consiste em compatibilizar a fabricação de dispositivos de potência com um processo dedicado a uma elevada escala de integração já existente. Ambos os caminhos exigem um elevado custo de desenvolvimento de processo, caracterização, etc. Neste trabalho propõe-se uma solução que se aplica a ambos os caminhos, porém com a vantagem de exigir um reduzido esforço de desenvolvimento de processos de fabricação.

### 1.3 Objetivos

Resultados experimentais, acumulados ao longo dos últimos anos de trabalho, demonstraram que a utilização dos transistores NMOS que suportam alta tensão e que são capazes de controlar potências médias, disponíveis em processos CMOS convencionais, associados a resistores, capacitores e indutores, integrados ou não, são suficientes para realizar um grande número de circuitos que são tipicamente utilizados em aplicações que recorrem a CIIP (*Smart Power*) [1.10] e [1.11]. Tais resultados fundamentaram este trabalho, cujo objetivo é apresentar um conjunto de circuitos básicos exigidos pelos CIIP. Esta estratégia utiliza somente o transistor NMOS e elementos passivos disponíveis em processos compatíveis com a tecnologia CMOS, dispensando o uso de outros dispositivos de alta tensão como os transistores PMOS, Bipolares PNP, Bipolares NPN ou diodo retificador e diodo Zener .Tem-se assim por principal objetivo apresentar uma nova família de circuitos baseados em transistores NMOS de alta tensão (NMOS-HV) para realizar as principais funções requeridas pelos circuitos de acionamento e de controle existentes nos CIIP. O conjunto de circuitos aqui apresentado é composto por seis circuitos:

- 1) emuladores de diodo retificador

- emuladores de diodo Zener

- 3) deslocadores de nível (*Level shifter*)

- 4) bombas de carga capacitiva (*charge-pump*)

- 5) intensificadores de tensão (bootstrap)

- 6) fonte de corrente flutuante

Também são apresentadas possíveis topologias dos dispositivos de potência dos CIIP compatíveis com a tecnologia CMOS escolhida para demonstrar a viabilidade da abordagem proposta.

Tem-se como um segundo objetivo a geração de uma proposta de arquitetura celular adequada à construção de uma matriz capaz de concretizar a família de circuitos e topologias propostas. Para veículo experimental deste estudo foram projetadas duas células básicas dedicadas ao controle de potência, uma concretizada em tecnologia puramente CMOS e a outra numa tecnologia combinada CMOS/LDMOS, ambas compatíveis com os circuitos de controle CMOS. Uma análise destas duas células permitirá ao leitor avaliar o desempenho, as potencialidades e versatilidade dos mesmos e sobre as vantagens e desvantagens das topologias de circuito testadas.

A especificação da arquitetura da matriz e do agregado pré-difundido, originada na associação destas matrizes, deve atender a dois requisitos fundamentais definidos pelos resultados obtidos em trabalhos anteriores [1.12] e dos quais este é uma continuação:

- 1. ser totalmente compatível com o processo CMOS digital convencional contendo pelo menos dois níveis de interligação em metal;

- 2. ser configurável apenas através do último nível de metal, adequando-se à atual infra-estrutura de processo e respectivas ferramentas de *software* para projetos de CIs semipersonalizados desenvolvidos pela Fundação Centro Tecnológico para Informática.

Tem-se como último objetivo, não menos importante que os anteriores, a construção experimental de alguns exemplos de aplicação com potencial interesse comercial que são técnica e economicamente viáveis em tecnologia CMOS convencional, em contraste com a inviabilidade econômica de se construírem em uma tecnologia dedicada.

### 1.4 Organização

Este trabalho está dividido em 5 Capítulos. No início de cada capítulo é apresentado o índice relativo ao mesmo, e na seqüência, a descrição do seu propósito. Cada capítulo possui uma conclusão individual do trabalho desenvolvido. As referências e as figuras estão organizadas por capítulo sendo listadas no final de cada um e referidas ao longo do texto. Na introdução do Capítulo 1, o contexto deste trabalho é apresentado em tópicos que têm relação direta com este trabalho, tais como os Circuitos Integrados Inteligentes de Potência - CIIPs, Circuitos Integrados de Aplicação Específica - *ASICs*, os *ASICs* semipersonalizados programáveis por máscaras, dedicados à integração inteligente de potência, perspectivados para a prototipagem rápida. No

tópico seguinte foi à procura de compatibilização desses *ASICs* com processo CMOS convencional, investigando soluções tanto para os circuitos como para a arquitetura da planta das matrizes que devem realizar os circuitos propostos, considerando as restrições impostas pelo processamento final disponibilizado para a realização do mesmo.

Na primeira parte do Capítulo 2 são apresentados uma revisão das tecnologias e principais processos que foram desenvolvidos para serem utilizados na construção dos CIIP presentes no mercado. Na segunda parte é relatado o desenvolvimento e a evolução de nossas pesquisas na busca de compatibilizar a integração de dispositivos de potência em tecnologias CMOS convencionais, único processo tecnológico disponível na época para realizar integração inteligente de potência e que está alinhada com a atual tendência de simplicidade e baixo custo na construção dos CIIP. Na parte final do capítulo são apresentados alguns dos circuitos que motivaram a persistência na continuação deste trabalho superando as dificuldades impostas pelas variadas restrições técnicas.

Na primeira parte do Capítulo 3 são apresentados os principais circuitos que dão sustentação à proposta de construir circuitos dedicados ao controle de potência baseados unicamente em transistores NMOS, dispensando o uso de tecnologias complexas para um grande conjunto de aplicações nos diversos segmentos da eletrônica. Na segunda parte são apresentadas e descritas duas arquiteturas de planta de células básicas que permitem a formação de matrizes de transistores e agregados capazes de realizar os circuitos dedicados ao controle da potência descritos na primeira parte do Capítulo 3.

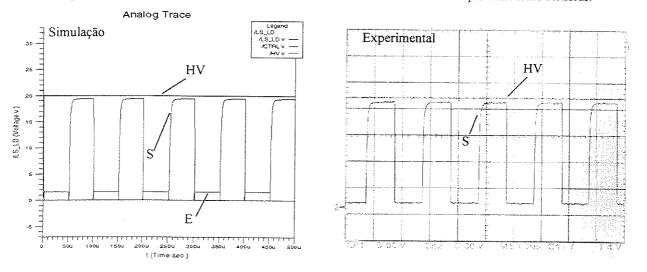

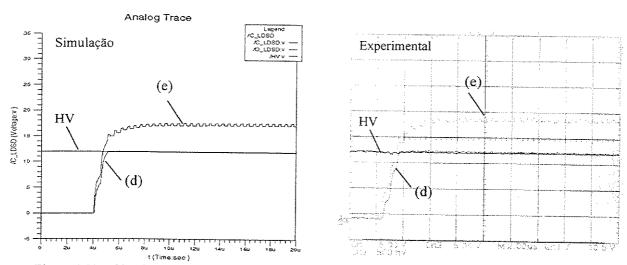

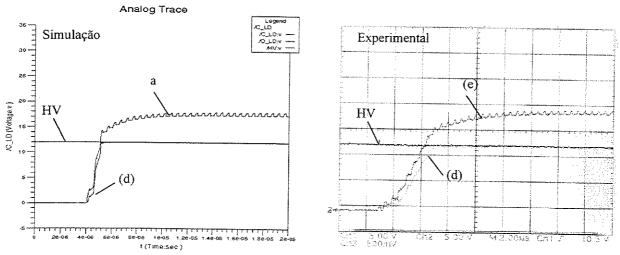

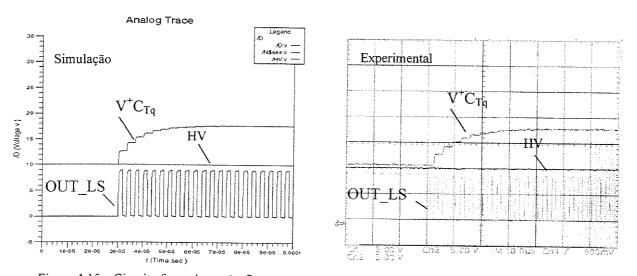

O Capítulo 4 apresenta os principais resultados de simulação elétrica, os resultados experimentais dos circuitos, bem como as respectivas fotos, para as estruturas construídas que foram apresentadas no Capítulo 3. Na última parte são também apresentados alguns exemplos de aplicações recorrendo aos CIIP construídos. São ilustrações do interesse e do desempenho da solução adotada. No Capítulo 5 é apresentada uma conclusão geral dos resultados obtidos e trabalhos futuros são propostos no âmbito da continuação desta pesquisa.

#### 1.5 Referências

- [1.1] B.J. Baliga, "An Overview of Smart Power Technology", IEEE Trans. on Electronic Devices, Vol. 38, n.7, pp. 1568-1575, Julho, 1991.

- [1.2] M.I. Castro Simas, "Intelligent Power Devices", II Workshop IBERCHIP, 1995.

- [1.3] D. Pryce, EDN, pg. 67, Março, 1987.

- [1.4] J.P. Huber, M.W. Rosneck, "Successful ASIC Design the First Time Through", Van Nostrand Reinhold, 1991.

- [1.5] "Smart Power Markets and Applications", Electronic Trend Publications, Saratoga, CA 1988.

- [1.6] A.P. Ramsey, in VLSI System Design IEEE, Vol 9, N° 5, pg. 36-41, Maio, 1998

- [1.7] C. Cini, "Smart Power Processes for LSI Circuits", SGS-THOMSON Application Note AN446/0392.

- [1.8] B.J. Baliga, "Power ICs in the Saddle", in Power Electronics in Action, Gadi Kaplan Editor, IEEE SPECTRUM, pp. 34-49, Julho 1995.

- [1.9] "Smart Power ICs Technologies and Applications", Springer Editor, pg. 53,1997.

- [1.10] S. Finco, J. Guilherme, F. Behrens, M. I. Castro Simas and M. Lança, "Pushing standard CMOS Technologies into Smart Power Conversion and Amplification", Journal of Circuits, Systems and Computers, vol. 5, no. 3, pp. 455-463, © World Scientific Publishing Company, 1995.

- [1.11] H. Ballan, M. Declercq, "High Voltage Devices and Circuits in Standard CMOS Technologies", Kluwer Academic Publishers, Dordrecht, The Netherlands, 1999.

- [1.12] F.H. Behrens, S. Finco, R.P. Ribas, F. Chavez, L.A. Razera, "Matriz Gate Array CMOS Avançada Configurável por um Único Nível de Metal", Anais do I Workshop Iberchip, pp. 259-270, Cartagena de Indias, Colômbia, Fevereiro, 1995.

UNICAMP 3IBLIOTECA CENTRAL SEÇÃO CIRCULANT?

2

# A Integração de Potência, Tecnologias e Aplicações

Onde se disserta sobre o estado da arte das tecnologias usadas na integração de potência, revendo primeiramente, os principais aspectos tecnológicos dos processos dedicados à integração de potência em geral e aos circuitos integrados inteligentes de potência em particular, com a apresentação das tecnologias usadas pelos fabricantes: Micrel, Motorola, Temic, SGST. São também referidos as tecnologias CMOS convencionais e os resultados obtidos, quando se visam aplicações de conversão e amplificação de potência.

# Capítulo 2

## A Integração de Potência, Tecnologias e Aplicações

| 2.1 INTRODUÇÃO                                                                 | 12        |

|--------------------------------------------------------------------------------|-----------|

| Z.Z CONCEITOS BASICOS                                                          |           |

| 2.3 TECNOLOGIAS DEDICADAS A INTEGRAÇÃO DE POTÊNCIA                             | 17        |

| 2.3.1 Technologias WOS                                                         | 1 77      |

| 2.3.1.1 Circuitos integrados Inteligentes de Potência                          | 10        |

| 2.3.1.2 Circuitos integrados de Alta Tensão                                    | 10        |

| 2.3.2 Tecnologias BiCMOS                                                       | 19        |

| 2.5.5 Topicos sobre isolamento                                                 | 22        |

| 2.3.3.1 Auto-isolamento                                                        |           |

| 2.3.3.2 Isolamento por Junções Verticais                                       | 24        |

| 2.3.3.1 Isolamento por Dieletrico                                              | 25        |

| 2.4 DESCRIÇÃO DE ALGUNS PROCESSOS COMFRCIAIS DEDICADOS À INTECDAÇÃO DE DOTÉMO. | 27        |

| 2.4.1 BCD V, Technologia da SGS-THOMSON                                        | 20        |

| 2.4.2 Sittat tivicos, Technología TMOS da Motorola                             | 20        |

| 2.4.3 DCD3, Technologia da Mickel.                                             | 22        |

| 2.4.4 Helichreis, rechologia da leivilo                                        | 22        |

| 2.4.3 Considerações sobre as Novas Tecnologias em Desenvolvimento              | 22        |

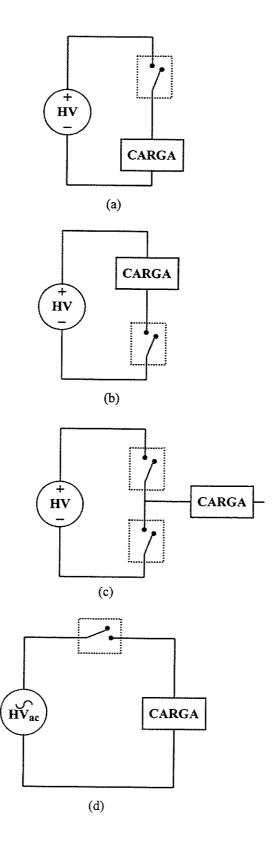

| 2.3 INTEGRAÇÃO INTELIGÊNTE DE POTENCIA                                         | 21        |

| 2.3.1 Controle da Potencia                                                     | 2.4       |

| 2.3.1.1 Topologias de Carga e de Interruptor                                   | 24        |

| 2.3.1.2 Concretização dos intermintores                                        | 20        |

| 2.3.1.3 Circuitos de Acionamento e suas Tonologias                             | 40        |

| 2.5.2 Circuitos de Connoie de Molecao                                          | 41        |

| 2.0 DESAFIOS PARA INOVAÇÃO                                                     | 41        |

| 2.0.1 Evolução dos Dispositivos de Potencia nas Tecnologias CMOS Convencionais | 4.4       |

| 2.6.2 Dispositivos Laterais NMOS                                               | 47        |

| 2.6.2.1 Descrição Detainada                                                    | 10        |

| 2.0.2.2. Wodelamento dos Dispositivos Laterais                                 | 40        |

| 2.6.3 Alguns Resultados Experimentais Preliminares                             | 40        |

| 2.0.4. Alguns Resultados Experimentais                                         | 51        |

| 2.0.4.1 Regulador DC-DC tipo Ampliador (Boost)                                 | £ 1       |

| 2.0.4.2 Reator Eletronico para Lampada Fluorescente                            | 50        |

| 2.0.4.5 Ampinicator Sigma-Della                                                | E 4       |

| Z./ CONCEUSUES                                                                 | 55        |

| 2.8 Referências                                                                | .55<br>56 |

|                                                                                | 20        |

### 2.1 Introdução

Nas duas últimas décadas assistiu-se a um grande progresso tecnológico, que foi marcado pelo desenvolvimento da Microeletrônica. A sigla VLSI surgiu com muita ênfase em todo o meio industrial e educacional. A associação de complexidade e velocidade encontrou aplicação imediata para sistemas VLSI no processamento digital complexo, sofisticado e de alto desempenho, atingindo rapidamente o estado da arte. Porém, isto é um fato somente quando o alvo é o processamento de sinais e controle. Quando os objetivos são os circuitos integrados de potência - CIP, (PICs - Power Integrated Circuits) [2.1], ainda há um longo caminho a percorrer para atingir o mesmo grau de desenvolvimento. Na verdade, as condições que, nos anos 80, permitiram a contratação de um grande número de pessoas no projeto e especificação de circuitos VLSI, no que se refere aos CIP, ainda esta em fase embrionária. Podemos referir, nomeadamente, as bibliotecas de células e ferramentas automáticas de projeto e teste, que tornam possível o ciclo de prototipagem rápida, e que permitem o acesso a tecnologias de baixo custo e fácil interface com os fabricantes de circuitos integrados. O completo preenchimento destes requisitos é condição essencial para a eficaz interação entre os projetistas de circuitos e as tecnologias disponibilizadas pelos fabricantes, para além do ambiente relativamente restrito da indústria de semicondutores. Este progresso vai ainda permitir a recorrência a estas soluções em um vasto campo de aplicações.

Importantes avanços podem ser observados nos circuitos integrados de potência, pois a sua importância econômica é já inquestionável. Soluções monolíticas dedicadas à conversão e amplificação de potência são altamente desejáveis, não somente pelo fato de reduzir interfaces e conseqüentemente seu volume, peso e interferências eletromagnéticas, mas também pelo fato de aumentar o rendimento, com uma melhoria significativa do desempenho e da confiabilidade de todo o sistema, tornando-se cada vez mais importante, permitindo a concretização de fontes de alimentação compactas, de conversores e de amplificadores de potência compatíveis com a impressionante redução de custo e volume alcançada no processamento de sinal [2.2]. Um grande número de aplicações que recorrerão a soluções monolíticas é previsível, visto que a potência que os CIP podem entregar à carga pode ser de dezenas, centenas ou até mesmo um milhar de Watt [2.1]. Deste modo, muitas abordagens estão sendo investigadas buscando novas estratégias para reduzir os custos dos circuitos integrados de potência. Relativamente aos CIP, dois tipos de

circuitos podem ser encontrados no mercado: os Circuitos Integrados Inteligentes de Potência - CIIP e os Circuitos Integrados de Alta Tensão (HVICs - High Voltage Integrated Circuits).

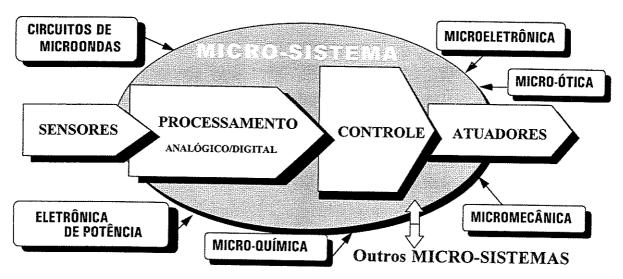

Considerando as conquistas das tecnologias até este momento, espera-se que num futuro próximo, não somente a microeletrônica e a integração de potência mas também a mecânica [2.3], a óptica [2.4] e a química [2.5], venham a concorrer para uma nova era na qual os microsistemas [2.6] serão o âmago de uma grande quantidade de produtos. Os micro-sistemas, como representados na Figura 2.1, integram microprocessadores, circuitos integrados de potência, micromáquinas, sensores químicos, circuitos de microondas e conexões ópticas, usando novos métodos de interligação, tais como pastilha sobre pastilha, pastilha dentro de pastilha [2.6] e camada enterrada de metal [2.7].

Figura 2.1 - Diagrama de Blocos de um micro-sistema que utiliza um amplo espectro de tecnologias.

Os circuitos integrados inteligentes de potência são considerados, segundo B. J. Baliga, como a chave para a segunda revolução da eletrônica [2.8], assim como os transistores MOS foram os componentes eletrônicos fundamentais da primeira. A inteligência atribuída aos dispositivos de potência, quer dos circuitos integrados inteligentes de potência, quer dos circuitos integrados de alta tensão, advém da capacidade de realizar funções lógicas e de memorização, permitindo a implementação de funções de proteção e de funções complexas de controle e de interfaceamento com microprocessadores.

O impacto dos circuitos integrados de potência, com ênfase especial nos dispositivos de potência, sobre os recentes avanços na indústria automotiva e aeroespacial, equipamentos médicos, de telecomunicação e muitos outros, e a expectativa da grande redução de custo para aplicações destas soluções monolíticas em muitos produtos de consumo, tais como aparelhos elétricos, ar condicionado e sistemas de iluminação, máquinas e ferramentas, controles programáveis e robótica, justificam o súbito aumento de interesse desta área e a reflexão que será apresentada neste capítulo.

Embora o Silício reúna a maioria dos requisitos para concretização dos CIP, novas estruturas de heterojunções estão sendo estudadas e testadas, tais como: o Arsenieto de Gálio, cuja elevada mobilidade dos elétrons permite realizar dispositivos que suportam alta tensão, operando a uma elevada velocidade de comutação [2.9]; o Silício-Germânio, que pode ser produzido com um baixo custo, além de suportar altas tensões e operar a uma elevada velocidade de comutação [2.6]; o Carbeto de Silício, que possui a capacidade de suportar uma temperatura de operação muito superior à do Silício, sendo estes dispositivos úteis para aplicação em controle de motores e na indústria automotiva e aeronáutica [2.10]; o Diamante, que oferece o melhor isolamento entre os dispositivos de potência e o circuito de controle [2.6]. Porém, todas estas soluções ainda não estão tecnologicamente resolvidas e estão em fase de aprimoramento com a evolução dos processos de fabricação. Deste modo, somente as tecnologias sobre Silício serão consideradas neste trabalho.

Neste capítulo, também, será feita uma breve consideração sobre a realização de circuitos integrados de potência e as estratégias usadas para aumentar o isolamento entre os dispositivos de potência e os circuitos que operam em baixa tensão. As principais funções requeridas para o desempenho inteligente dos dispositivos de potência também serão referidas. Finalmente, uma nova abordagem para aumentar a capacidade de uma tecnologia CMOS convencional para suportar aplicações de potência é apresentada, bem como as perspectivas de inovação quando usadas em aplicações de baixa ou média potência. Resultados simples porém diversificados, obtidos experimentalmente, ilustram a parte final deste capítulo, nomeadamente topologias de conversão e amplificação, concretizadas utilizando células otimizadas, que confirmam a viabilidade desta proposta, sendo os resultados obtidos nos circuitos preliminares responsáveis pelo desenvolvimento mais aprofundado, relatado nesta dissertação.

#### 2.2 Conceitos Básicos

Os Circuitos Integrados Inteligentes de Potência [2.8] [2.11] são definidos como circuitos integrados de potência, que atuam como interface entre o controle analógico/digital e a carga de potência e são projetados para controlar médias tensões (muitas dezenas de Volt) e níveis de corrente relativamente elevados (alguns Ampere). Estas exigências de mercado motivaram o desenvolvimento de tecnologias sofisticadas e muito dispendiosas, destinadas a integrar na mesma pastilha dispositivos de potência com o seu controle, proteção, memórias e circuitos de amostragem, diagnóstico de falhas e monitoramento de processos. Os CIIP são projetados para realizar funções complexas de comutação a altas freqüências, promovendo assim grandes progressos nesta área e induzindo os fabricantes de semicondutores a entrarem no mercado de circuitos integrados de potência de aplicação específica, tanto para baixa, como para média potência, nomeadamente nas áreas da indústria automotiva, robótica, telecomunicação móvel, equipamentos médicos e áreas que exigem elevada confiabilidade e compactação.

Circuitos Integrados de Alta Tensão (HVIC) [2.12] são circuitos integrados de potência, que suportam elevadas tensões (centenas de Volt), no corte, para aplicações que exigem uma corrente relativamente baixa (menor que um Ampere e tipicamente dezenas de mA), tais como os circuitos de acionamento de mostradores eletroluminescentes de plasma. Nestes circuitos, usualmente, muitos dispositivos de potência são colocados dentro da mesma pastilha com seus respectivos circuitos de acionamento e controle e outros circuitos que operam em baixa tensão. Os isolamentos para alta tensão e a necessidade inerente de interligações exigem técnicas especiais que evoluíram a partir da invenção da técnica de RESURF (REDUced SURface Field), que será referida a seguir. Os Circuitos Integrados de Alta Tensão representam uma solução atraente para um grande número de aplicações, nomeadamente para painéis planos eletroluminescentes, circuitos para telecomunicações, reatores eletrônicos e automação industriais.

Em paralelo com estas soluções monolíticas, existem associações de componentes discretos montados em placas de circuito impresso e de circuitos híbridos sob o mesmo encapsulamento, que permitem a construção dos chamados módulos inteligentes de potência [2.13], utilizados em aplicações que requerem simultaneamente alta tensão e elevadas correntes como no caso dos veículos elétricos, alguns circuitos para telecomunicações, alguns reatores eletrônicos, automação industrial, controle de motores, tração e linhas de transmissão de alta tensão. De fato, soluções

monolíticas para estas aplicações são proibitivas em função das dimensões da pastilha requerida, considerando as tecnologias disponíveis na atualidade.

### 2.3 Tecnologias Dedicadas à Integração de Potência

Tanto os transistores bipolares de potência discretos, como os MOSFETs de potência e posteriormente suas estruturas derivadas, tais como os IGBTs e os tiristores MOS, têm sido usados para realizar os dispositivos inteligentes de potência.

A seguir, versões das tecnologias utilizadas serão revisadas, considerando suas principais contribuições na implementação de circuitos integrados de alta tensão e circuitos integrados inteligentes de potência, considerando especialmente as técnicas desenvolvidas para aumentar a tensão de ruptura.

### 2.3.1 Tecnologias MOS

Recentemente as estruturas MOS apresentaram grandes melhorias na capacidade de suportar tensão e de transportar corrente. O progresso conseguido tem aberto um grande leque de aplicações para esta tecnologia, que no início se julgava essencialmente eficaz para a concretização de circuitos que operam em baixa tensão, baixa corrente e com maior ou menor complexidade de integração (LSI e VLSI). A maioria dessas inovações baseia-se na técnica da dupla difusão para a realização de dispositivos com comprimento de canal reduzido, tal estrutura de dispositivo denominando-se DMOS (double Diffusion MOS). A incorporação de uma região de deriva ou deslocamento (drift region) fracamente dopada entre a região ativa do canal e a região de dreno permitiu obter dispositivos que suportam no corte elevadas tensões sem a ocorrência da ruptura. Além do mais, para reduzir a área de silício relacionada com essa técnica, foi feita a estrutura vertical. Os terminais de dreno e fonte estão posicionados em lados opostos da pastilha semicondutora.

A maturidade das tecnologias MOS permite a produção de dispositivos de potência que apresentam características interessantes, tais como: elevada impedância de entrada, reduzidas perdas de comutação, coeficiente de temperatura negativo, eficácia de comutação inerente à condução baseada em portadores majoritários e a possibilidade de integração com circuitos de

controle complexos realizados com tecnologia CMOS, integrando funções analógicas e digitais na mesma pastilha. A combinação simultânea dessas características dá origem a dispositivos de elevado desempenho [2.14].

## 2.3.1.1 Circuitos Integrados Inteligentes de Potência

Um circuito integrado inteligente de potência é essencialmente constituído por um ou vários dispositivos de potência, associados na mesma pastilha a circuitos de elevada densidade, que operam em baixa tensão, para obter uma melhoria da sua funcionalidade.

A disponibilidade de dispositivos MOS de potência realizados em Silício, tais como o transistor MOS vertical com dupla difusão, o transistor VDMOS e sua implementação lateral o transistor LDMOS tornaram viáveis e atraentes os circuitos integrados inteligentes de potência em muitas aplicações desenvolvidas pela Philips e pela Siemens, entre outros [2.15], [2.16] e [2.17]. Porém, como a principal preocupação é a redução do custo [2.18] para aplicações de média potência, a redução das dimensões da pastilha foi alcançada usando o conceito de modulação da condutividade, através da injeção de portadores [2.19] implementada no IGBT (*Insulated Gate Bipolar Transistor* também chamado de *COMFET*, pela RCA; *GEMFET*, pela Motorola; e *IGT*, pela GE e Philips), e o seu transistor lateral derivado, o transistor lateral com porta isolada LIGT (*Lateral Insulated Gate Transistor*), foi fabricado pela Philips utilizando a tecnologia CMOS [2.20].

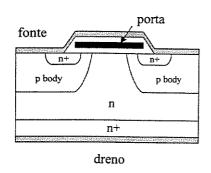

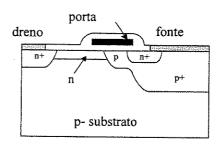

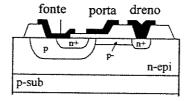

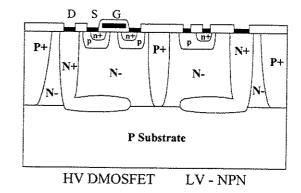

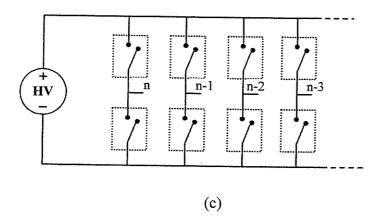

Os dispositivos inteligentes de potência são projetados usando uma estratégia especial para otimizar a capacidade dos dispositivos de potência no que diz respeito à sua tensão de ruptura e resistência de condução, tanto usando um dispositivo com fluxo de corrente na vertical, mostrado na Figura 2.2, através do crescimento de uma camada epitaxial sobre um substrato com elevada concentração de impurezas, como utilizando um fluxo de corrente lateral, recorrendo ao conceito de semicondutor com baixa concentração de impurezas (LDD - Lightly Doped Drain) [2.21], Figura 2.3, ou ainda utilizando placas de campo e/ou técnicas de deslocamento de porta em relação ao dreno [2.22].

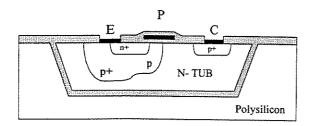

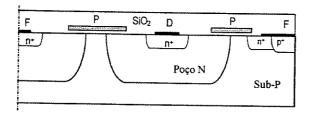

Outra solução de estrutura de dispositivo lateral, usando o conceito de redução do campo superficial, REduced SURface Field (RESURF) [2.23], permite que dispositivos laterais possam

suportar no corte elevadas tensões com uma capacidade de corrente razoável. Este efeito ocorre em estruturas que contêm uma fina camada de crescimento epitaxial, com uma forte concentração de impurezas sobre um substrato com baixa concentração de impurezas. A Figura 2.4 mostra um exemplo do corte lateral desta estrutura.

Figura 2.2 – Corte transversal de um dispositivo com fluxo de corrente na vertical.

Figura 2.3 - Corte transversal de um dispositivo com fluxo de corrente lateral.

UNICAMP SIBLIOTECA CENTRAL SEÇÃO CIRCULANTE

Figura 2.4 – Corte transversal de um dispositivo que utiliza o conceito de redução do campo superficial (*RESURF*).

Para os diversos tipos de dispositivos acima referidos, existem diferentes soluções para integrar os circuitos de controle que operam em baixa tensão, com o isolamento necessário. Na Seção 2.3.3, Tópicos sobre Isolamento, será apresentada uma revisão das técnicas utilizadas.

## 2.3.1.2 Circuitos Integrados de Alta Tensão

Dispositivos discretos de alta tensão têm sido fabricados recorrendo a estruturas caracterizadas por um fluxo de corrente vertical, através da região de deriva, com baixa concentração de portadores minoritários. Deste modo, para isolar estes dispositivos, é necessário realizar difusões profundas que são inadequadas para serem fabricadas em processos dedicados à construção de circuitos integrados de baixa tensão. Em contraste com os processos para construção dos dispositivos inteligentes de potência, onde ambas as estruturas, vertical ou horizontal, podem ser encontradas, os dispositivos de alta tensão, como não precisam suportar correntes muito elevadas,

são baseados no fluxo de corrente horizontal e os maiores esforços incidiram no desenvolvimento de técnicas que permitam a estas estruturas laterais suportar alta tensão.

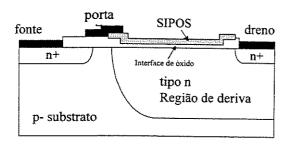

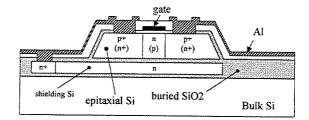

Numerosas técnicas têm sido estudadas com o objetivo de atingir a tensão de ruptura próxima da tensão ideal de uma junção plana [2.14], [2.22] e [2.23]. Uma das primeiras tentativas foi a utilização do Silício Policristalino Semi-Isolante (Semi Insulating Polycrystalline Silicon - SIPOS) para a camada de passivação, mostrado na Figura 2.5 [2.24] e [2.25], para reduzir os efeitos de campo na superfície e aumentar a tensão de ruptura. Porém, esta solução é suscetível de provocar contaminação de superfície, dando origem à existência de elevadas correntes de fuga, e de reduzir a imunidade do dispositivo à dV/dt [2.26]. Outras soluções derivadas desta técnica foram desenvolvidas para resolver os problemas de contaminação e da corrente de fuga [2.27]. Melhorias posteriores foram obtidas usando placas de campo e camadas semi-resistivas [2.28]. Estas técnicas podem ser aplicadas tanto para os dispositivos da tecnologia MOS como para os da tecnologia Bipolar.

O uso de substratos de elevada resistividade com uma camada de crescimento epitaxial relativamente fina elimina o efeito de ruptura na superfície devido ao efeito chamado RESURF anteriormente referido [2.23]. Esta técnica, quando aplicada a dispositivos de alta tensão, como no caso dos transistores MOS com injeção de portadores por efeito de Schottky, (Schottky Injection MOS-gated Transistor - SINFET) [2.29], conduz a soluções viáveis para processos de HVIC, compatíveis com a tecnologia CMOS, Figura 2.6 [2.30]. Porém, a tensão de ruptura é de difícil previsão quando a técnica de RESURF é utilizada, devido ao fato de requerer um controle preciso da concentração de impurezas na camada de crescimento epitaxial, quando as tolerâncias dos parâmetros de processo são frequentemente maiores que a precisão requerida para otimizar a tensão de ruptura. Além disto, os dispositivos que utilizam a técnica de RESURF apresentam uma elevada resistência de condução devido à fina camada de crescimento epitaxial utilizada na sua fabricação, como mostrado na Figura 2.4. Com o objetivo de melhorar a resistência de condução destes dispositivos, mantendo elevadas tensões de ruptura, outras técnicas têm sido propostas que utilizam uma região de deriva, cuja concentração de impurezas é otimizada de forma a satisfazer a condição do efeito RESURF: em uma delas, através do implante de uma região de deriva [2.31]; outra utiliza múltiplas camadas de deriva resistivas [2.32].

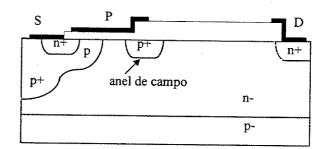

Foi também proposta [2.33] e otimizada [2.34] a utilização de anéis de campo flutuantes entre o canal e o dreno do transistor LDMOS, como mostrado na Figura 2.7. A vantagem desta técnica reside no fato da concentração de impurezas e a espessura da camada de crescimento epitaxial não serem parâmetros cruciais no projeto; porém, a tensão de ruptura é uma função da concentração de impurezas do anel e a implementação deste exige por vezes uma máscara adicional no processo [2.34].

A G K G A

Contato Schotiky p+ • WW•

p

n-

Figura 2.5 - Corte transversal de um transistor NMOS de alta tensão usando camada SIPOS

Figura 2.6 - Corte transversal de uma estrutura SINFET

Figura 2. 7 - Corte transversal de um transistor LDMOS que utiliza anéis de campo flutuantes

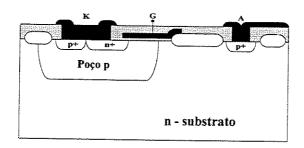

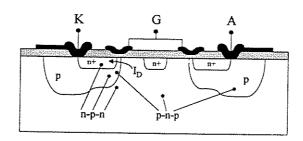

Muitas outras tentativas de novas estruturas foram desenvolvidas e testadas [2.35], e merecem posterior atenção com o objetivo de torná-las facilmente compatíveis com circuitos de controle CMOS. Algumas das mais interessantes, devido ao elevado potencial no que diz respeito ao suporte de correntes e tensões elevadas com uma baixa resistência de condução, são as estruturas: LIGT, Figura 2.8, que podem ser incorporadas em um CIP, juntamente com circuitos de controle CMOS [2.20], mas apresenta a desvantagem da degradação da velocidade de comutação quando comparado com o transistor LDMOS; MICFET ("Minority Carrier Injection Field Effect Transistor") [2.36], que permite alcançar uma baixa resistência de condução com reduzida penalidade no tempo de passagem ao corte do dispositivo de potência; uma outra estrutura que merece destaque é o TRIMOS, um TRIAC com porta isolada, Figura 2.9 [2.37], que derivou do transistor de alta tensão LDMOS e opera com ambas as polaridades da fonte de tensão,

apresentando dois modos de operação, um dos quais regenerativo, característica que é altamente desejável quando é requerido o suporte de uma corrente muito elevada.

Figura 2.8 - Estrutura do transistor LIGT

Figura 2.9 - Estrutura TRIMOS baseada em dois transistores LDMOS com um dreno comum.

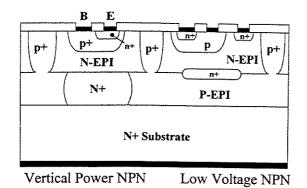

## 2.3.2 Tecnologias BiCMOS

Durante a década de 80, a tecnologia BiCMOS evoluiu dos esforços iniciais da tecnologia BiMOS [2.38], [2.39] e [2.40] para uma tecnologia madura e viável, tornando-se uma opção para a integração monolítica de aplicações que requerem tanto circuitos anaiógicos, como digitais. Com o advento dos transistores bipolares controlados por portas MOS, novos CIP foram desenvolvidos. Tanto os circuitos integrados inteligentes de potência, como os circuitos de alta tensão *HVICs*, beneficiando-se da capacidade de corrente do transistor bipolar e suporte de elevada tensão, conjuntamente com alta impedância de entrada proporcionada pelo transistor MOS, que simplifica os seus circuitos de controle.

Estes dispositivos bipolares controlados por portas MOS, que incluem o IGBT (Insulated Gate Bipolar Transistor) [2.19], os tiristores de porta MOS (MOS-SCR, MOS-GTO, TRIMOS, etc.), o MCT (MOS-Controlled Thyristor) [2.35], e o MTO (MOS Turn-Off thyristor) [2.14], foram primeiramente desenvolvidos para dispositivos discretos que suportam múltiplos kiloampere e kilovolt. Porém, esforços adicionais estão permitindo expandir as suas aplicações para realizar

CIP robustos, de baixo custo, tanto para os dispositivos com estrutura vertical como para os de estrutura horizontal.

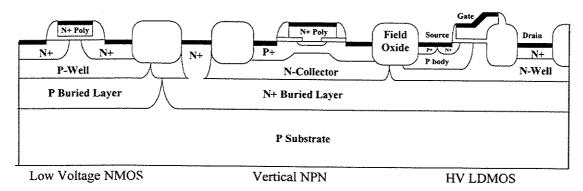

Avanços recentes [2.41] abriram o caminho para a fabricação de dispositivos bipolares de alta tensão e elevado desempenho, através da incorporação de camadas de crescimento epitaxiais e enterradas, que são totalmente compatíveis com as demais etapas de processos para fabricação dos circuitos de controle, operando em baixa tensão, Figura 2.10 [2.42].

Fig. 2.10 - Corte transversal de uma estrutura BiCMOS.

### 2.3.3 Tópicos sobre Isolamento

A maior dificuldade no desenvolvimento de circuitos integrados inteligentes de potência - CIP é a proteção eletricamente eficaz do circuito que opera em baixa tensão, relativamente à alta tensão aplicada nos dispositivos de potência. As técnicas de isolamento usualmente utilizadas nos CIP são baseadas em soluções tecnológicas altamente complexas e dispendiosas. Essas técnicas podem ser divididas em três tipos diferentes: auto-isolamento, isolamento por junção e isolamento por dielétrico.

#### 2.3.3.1 Auto-isolamento

Esta técnica [2.43] é baseada na polarização inversa das junções obtidas através de uma junção profunda, ou poço, com uma fraca concentração de impurezas, difundido em uma camada de crescimento epitaxial, sendo o circuito de controle implementado por dispositivos laterais construídos dentro do poço. Tal técnica pode ser aplicada tanto a estruturas verticais, como a horizontais. No primeiro caso, um poço-P com uma fraca concentração de impurezas é difundido dentro de uma camada de crescimento epitaxial-N de deriva, crescida sobre substrato-N de forte

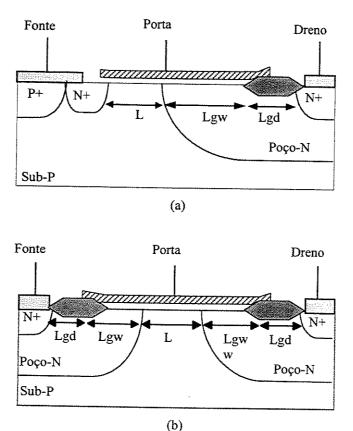

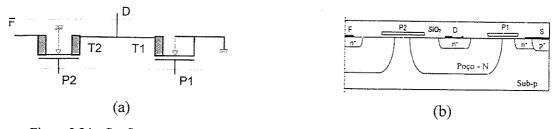

concentração de impurezas, mostrado na Figura 2.11. Também é mostrado como os dispositivos CMOS de alta tensão são construídos, munindo os drenos dos dispositivos CMOS de baixa tensão de uma região de deriva "resurfed". Observa-se que esta solução tecnológica é limitada à realização de interruptores eletrônicos isolados (high side) e, também, que o substrato do transistor PMOS não pode ser isolado eletricamente do dreno dos transistores de potência. Para uma estrutura lateral, um poço-N de fraca concentração de impurezas é difundido em um substrato P, mostrado na Figura 2.12, com a função de criar uma região de deriva em direção ao dreno. Também deve ser lembrado que a estrutura lateral deve ser projetada com uma geometria anelar, cujo dreno é completamente circundado pelas regiões de porta e fonte do transistor. Isto limita a tecnologia a dispositivos de alta tensão no estágio de saída configurados como fonte comum.

Figura 2.11 – Corte transversal de uma estrutura vertical auto-isolada.

Figura 2.12 - Corte transversal de uma estrutura horizontal auto-isolada.

A técnica chamada de auto-isolamento apresenta excelente resultado de isolamento estático. Porém as capacitâncias associadas a esta técnica não permitem um isolamento dinâmico muito eficiente. De fato, os transitórios de tensão em camadas de crescimento epitaxial ou no substrato podem induzir fluxos de corrente suficientemente elevados na região do poço, que por sua vez podem gerar níveis de tensão que polarizem diretamente as junções de dreno e fonte, produzindo uma condução intempestiva (*latch-up*).

## 2.3.3.2 Isolamento por Junções Verticais

Esta técnica [2.43] utiliza a capacidade de isolamento de junções inversamente polarizadas, obtidas por regiões de fraca concentração de impurezas numa camada dupla de crescimento epitaxial. As ilhas de elevada concentração de impurezas conferem o isolamento necessário aos circuitos que operam em baixa tensão. Esta técnica também pode ser aplicada tanto a estruturas verticais como a estruturas horizontais. Nas estruturas verticais, utilizam-se "paredes" verticais, para permitir o fluxo de corrente na vertical, sendo utilizada como contato uma região n<sup>+</sup> de

elevada concentração de impurezas difundida na interface superior da camada epitaxial p de suave concentração, mostrado na Figura 2.13. Adicionalmente, camadas enterradas do tipo n são utilizadas para reduzir a resistência de condução e aumentar o ganho do transistor pnp lateral.

Esta solução tecnológica é limitada à existência de um único transistor de potência ou a uma matriz de transistores com dreno comum, quando na implementação de circuitos integrados inteligentes de potência. Para a estrutura lateral, uma camada espessa de crescimento epitaxial é otimizada para a construção de transistores de baixa tensão e de elevado desempenho, como mostrado na Figura 2.14.

Figura 2.13 - Corte transversal de uma estrutura vertical utilizando a técnica de isolamento por junção.

Figura 2.14 - Corte transversal de uma estrutura horizontal utilizando a técnica de isolamento por junção.

Estas tecnologias são complexas e normalmente utilizam mais de 12 máscaras de processo, porém, ainda assim, não é possível evitar o desencadeamento de condução intempestiva (*latch-up*) quando o dispositivo é exposto a variações de tensão muito rápidas. Uma solução derivada desta tecnologia, que apenas utiliza 9 máscaras, foi desenvolvida baseada no efeito denominado de "poço flutuante" [2.44], que apresenta uma maior eficácia tanto em regime estático de operação do dispositivo, como em regime dinâmico, se for convenientemente protegido por um circuito periférico de atenuação.

### 2.3.3.3 Isolamento por Dielétrico

Esta técnica tem atraído a atenção dos fabricantes [2.45], principalmente dos fabricantes dos *HVICs*, como sendo uma alternativa ao isolamento por junção pn. Nesta técnica, o efeito *latch-up* é inexistente e os efeitos capacitivos parasitas são pequenos. Têm a vantagem inerente de suportar de elevadas tensões, baixa taxa de geração de corrente térmica, alta confiabilidade, alta

densidade de empacotamento eletrônico e uma grande flexibilidade de projeto. Um dos primeiros esforços para implementar esta técnica usou ilhas de cristal de silício sobre um substrato policristalino separados por uma fina camada de SiO<sub>2</sub> [2.43], Figura 2.15, tendo-se conseguido a completa inexistência de corrente de fuga, quando inversamente polarizado e é reduzida a possibilidade de ocorrência de condução intempestiva. Porém a matéria prima é de custo muito elevado, devido ao fato de utilizar um substrato espesso de silício policristalino para obter resistência mecânica compatível com o processo, o que também origina uma baixa condutividade térmica.

Adicionalmente, esta técnica requer um procedimento de corrosão profunda e polimento da face inferior da lâmina, exigindo a utilização de precauções não convencionais para evitar a flexão da lâmina durante as etapas de processamento realizado em elevadas temperaturas, durante o processo de fabricação do dispositivo. Deste modo, a técnica de isolamento por dielétrico - DI é limitada em sua capacidade de dissipar potência sobre a pastilha, restringindo-se o seu uso a aplicações de baixa potência ou que exijam características superiores de isolamento, tais como as que são requeridas em circuitos integrados de alta tensão usados em telecomunicações.

Muitos trabalhos têm sido desenvolvidos com o objetivo de criar novos processos que permitem implementar a técnica de isolamento por dielétrico [2.12]. Por exemplo, um destes processos usa o Silício-Sobre-Safira (SOS - Silicon on Saphire), que oferece vantagem quando a robustez à radiação é requerida e utiliza a tão bem caracterizada tecnologia CMOS.

O desenvolvimento de processos que realizam a colagem de Silício diretamente sobre o Silício (SDB - Silicon Direct Bonding) permite a produção de lâminas de Silício sobre Isolante (SOI - Silicon on Isulator) [2.46], [2.47] e a geração de lâminas de Silício Sobre Isolante Sobre Silício (SOIS - Silicon on Insulator on Silicon) [2.48], os quais oferecem muitas vantagens para a construção de circuitos integrados de alta tensão isolados por dielétrico. Esta técnica apresenta uma maior qualidade, quando comparado com o SOS e tanto a espessura do Silício como a do dielétrico podem ter um grande leque de opções relativamente à espessura desejada, e concomitantemente, esta técnica exige menor número de etapas no processo de fabricação e menos equipamentos adicionais.

Uma outra tecnologia de *SOI* que permite obter um elevado grau de isolamento, mesmo em presença de transitórios abruptos, utiliza a implantação de oxigênio (SIMOX) [2.49]. O corte de uma destas estruturas é exemplificado na Figura 2.16, para formar camadas duplas de isolante enterradas [2.50].

Figura. 2.15 - Corte transversal de um PIC usando isolamento por dielétrico convencional.

Figura. 2.16 – Corte transversal de um MOSFET usando a técnica de isolamento por dielétrico SIMOX.

# 2.4 Descrição de Alguns Processos Comerciais Dedicados à Integração de Potência

A tecnologia que agrega às tecnologias de construção dos dispositivos Bipolares, CMOS e DMOS, é conhecida na literatura como tecnologia BCDMOS. Diversos fabricantes [2.51] oferecem diferentes variações de tecnologias que integram dispositivos Bipolares, lógica de controle CMOS e dispositivos de potência DMOS (BCDMOS). As tecnologias BCDMOS podem ser caracterizadas genericamente como sendo orientadas para processos Bipolares ou para processos CMOS. A tecnologia orientada para processos Bipolares caracteriza-se por conter regiões isoladas formadas por crescimento epitaxial enterradas, e a orientada para processos CMOS é caracterizada por conter regiões de difusão de poço como base para os dispositivos verticais Bipolares.

As primeiras são mais adequadas para aplicações que requerem interfaces com tensões mais elevadas, i.e. superiores a 20V, e que operam a altas freqüências, utilizando um pequeno número de portas lógicas, tipicamente inferior a 200. As segundas são tipicamente mais adequadas para aplicações que exigem um processamento lógico relativamente complexo, i.e. acima de 1000 portas lógicas equivalentes ou para dispositivos com tensão de operação inferior a 12V. Geralmente os processos destas tecnologias têm seus limites de operação em torno de 20V.

A principal distinção provém da técnica de construção utilizada para cada tecnologia. Nas tecnologias que utilizam isolamento por junção conseguem-se maiores tensões de ruptura das junções quando ambas possuem uma mais baixa concentração de impurezas; já nas tecnologias

que recorrem à soldagem de lâminas, a ruptura ocorre no isolamento por óxido, para tensões tão mais elevadas quanto mais eficaz for o isolamento. Processos que utilizam a técnica de isolamento por junção são as de mais baixo custo. Quando um dos lados da junção p-n obtida por difusão apresenta baixa concentração de impurezas, resulta que a região de depleção irá estender-se a distâncias consideráveis dentro da região de difusão de baixa concentração. Este resultado determina espaçamentos significativamente grandes (dezenas de µm) entre distintas junções que permitem a construção dos dispositivos DMOS neste tipo de tecnologia BCDMOS. Este grande espaçamento requerido pelos dispositivos DMOS pode ser parcialmente resolvido pela utilização da tecnologia de isolamento por dielétrico, onde a região que deve suportar altas tensões não é obtida a partir da difusão de um poço. Infelizmente esta solução requer um processo mais sofisticado e de elevado custo. São raros os processos comerciais ou os dispositivos semicondutores inteligentes que utilizam a técnica de isolamento por dielétrico para aplicações de alta tensão.

Nos sub-itens desta seção serão apresentadas sumariamente algumas das tecnologias utilizadas por alguns dos principais fabricantes de dispositivos semicondutores de potência.

## 2.4.1 BCD V, Tecnologia da SGS-THOMSON [2.52]

A SGS THOMSON foi a pioneira a produzir a tecnologia BCDMOS. Em meados dos anos oitenta, foi proposta a conjugação da tecnologia do transistor DMOS com a tecnologia Bipolar convencional, que utiliza o isolamento por junções verticais. Como resultado, obtiveram produtes que reúnem os benefícios dos circuitos Bipolares de alta precisão, com a alta densidade dos circuitos lógicos CMOS e a alta eficiência do estágio de potência construído com transistores DMOS. O fato de todos os contatos dos dispositivos estarem no topo da lâmina permitiu a integração totalmente isolada do transistor de potência DMOS e de qualquer outro tipo de estágio de potência, incluindo as configurações em ponte.

Devido à baixa dissipação de potência dos transistores DMOS, a existência da tecnologia BCD trouxe a possibilidade de montagem de circuitos integrados de potência em encapsulamento de baixo custo tipo DIP e SO. Adicionalmente, a redução de dissipação e possibilidade de construção de circuitos CMOS de alta densidade resultou na possibilidade de integração de funções altamente complexas. Através dos anos, a tecnologia original BCD da SGS THOMSON

tem evoluído para uma litografia mais fina, encolhendo de 4 para 2,5 micra, posteriormente para 1,0 e agora 0,6 µm. Em paralelo, a tecnologia tem se tornado mais flexível, adicionando mais recentemente novas capacidades tal como a de incluir memória não volátil ao processo original Bipolar/CMOS/DMOS [2.52].

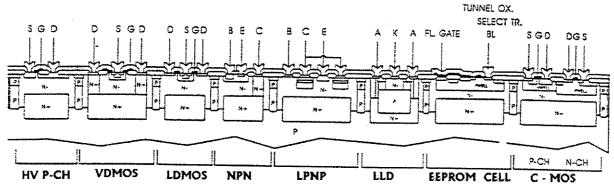

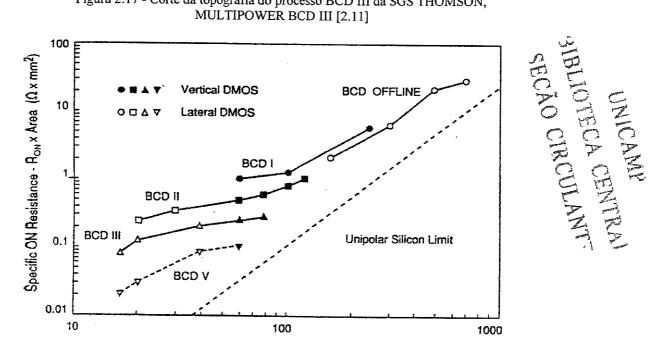

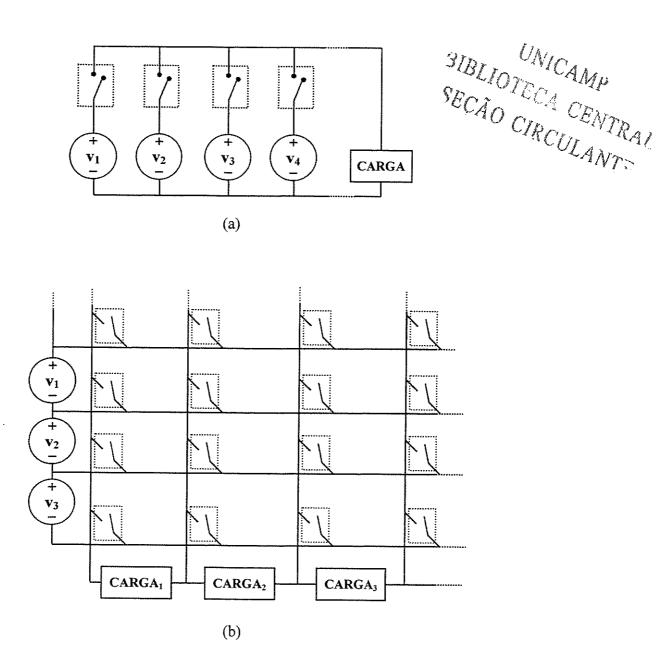

A Figura 2.17 mostra um corte da topografia do processo BCD III da SGS THOMSON apresentado por A. Andreini et al. em sua contribuição ao livro da referência [2.11]. A tecnologia BCD5/CD5 é uma evolução da BCD III de 1,2  $\mu m$ , porém com uma litografia de 0,6  $\mu m$  e com a capacidade adicional de integrar memória flash na realização dos CIIP. A Figura 2.18 apresenta um gráfico da evolução do processo BCD desenvolvido pela SGS THOMSON [2.11].

Figura 2.17 - Corte da topografia do processo BCD III da SGS THOMSON, MULTIPOWER BCD III [2.11]

Figura 2.18 - Gráfico da evolução do processo BCD desenvolvido pela SGS THOMSON [2.11]

## 2.4.2 SmartMOS, Tecnologia TMOS da Motorola [2.53]

A família TMOS de transistores MOS de potência, desenvolvida pela Motorola, é formada por uma matriz de canais verticais difundidos, baseada num processo parametrizado para as especificações de V<sub>BR</sub> e R<sub>ON</sub> do dispositivo desejado. Esta tecnologia tem como característica propiciar a realização de dispositivos em uma larga escala de valores tensão e corrente com baixos valores da resistência de canal durante o estado de condução, R<sub>DS(on)</sub>.

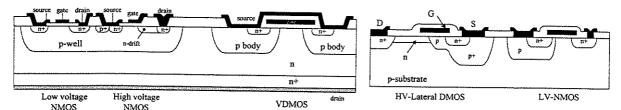

Os transistores MOS TMOS de potência da Motorola são o último passo de uma progressão evolucionária, que começou com o transistor MOS de pequenos sinais em 1973, sendo posteriormente substituído pelo Transistor lateral MOS da dupla difusão (LDMOS) e pelo transistor MOS vertical V-groove (VDMOS).

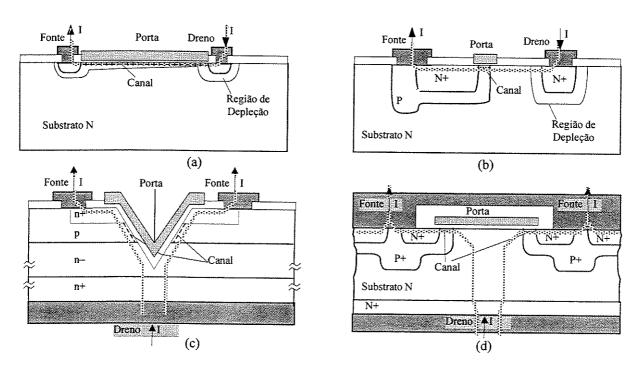

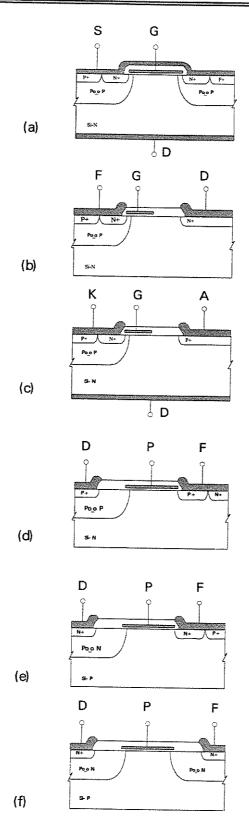

O transistor MOS, canal N, para pequenos sinais era construído num substrato tipo P com baixa concentração de impurezas, no qual eram difundidas duas regiões N<sup>+</sup> com alta concentração de impurezas, como mostrado na Figura 2.19 (a). As regiões N<sup>+</sup> atuam como dreno e fonte, separadas pelo canal do transistor, o qual era definido pelo processo litográfico. Esta configuração resultou em canais de longo comprimento, baixa capacidade de corrente, baixa tensão inversa de ruptura e um alto valor de R<sub>DS(on)</sub>.

Duas grandes mudanças na estrutura do transistor de pequenos sinais MOS foram responsáveis pela evolução deste para os dispositivos de potência MOS. A primeira consistiu no uso da técnica de auto-alinhamento do canal, associada à técnica de difusão dupla para obter transistores com canais curtos, o que permitiu uma alta densidade de canal, resultando uma alta capacidade de corrente e baixo R<sub>DS(ON)</sub>. A segunda foi a incorporação de uma região de baixa concentração de impurezas entre o dreno e fonte formadas por uma difusão N-, conferindo ao dispositivo a propriedade de suportar elevadas tensões inversas no corte.

Estas alterações resultaram no transistor MOS, cuja estrutura é mostrada na Figura 2.19 (b). Todos os terminais do dispositivo estão localizados no topo da superfície da pastilha. A maior desvantagem desta configuração é a ineficiência do uso da área de silício, particularmente na área da região de deriva existente entre o canal e o ponto de contato de dreno.

O próximo passo no processo evolucionário é uma estrutura vertical, na qual o contato de dreno está na parte de baixo da pastilha, depois o crescimento da densidade do canal de empacotamento. O conceito inicial usa um transistor de potência V-groove MOS passando pela difusão dupla da região N<sup>+</sup> e P<sup>-</sup>. Figura 2.19 (c). A solicitação da densidade do empacotamento adequado, uso eficiente do silício e baixa tensão inversa de ruptura são obtidas nesta configuração. Entretanto, para esta estrutura vertical, o processo consistente e o resultado obtido justificam claramente um elevado custo de pastilha.

O passo seguinte dado na evolução deste processo foi a criação de uma estrutura vertical de potência TMOS como mostrado na Figura 2.19 (d), similar à da Figura 2.19 (b), exceto que o contato de dreno é localizado também na parte de baixo da pastilha. A estrutura da porta é feita com polissilício localizado entre duas camadas de óxido (óxido de porta e óxido grosso ou de isolamento), permitindo que o metal do contato de fonte cubra toda a área ativa do dispositivo. Esta configuração com duas camadas de contato elétrico, a de dreno e a de fonte, localizadas em lados opostos da pastilha, apresenta uma melhor densidade de empacotamento e mantém as vantagens do processo do LDMOS plano, resultando num processo de alto rendimento, com baixo valor de R<sub>DS(on)</sub> e adequado para produzir dispositivos com uma larga gama de tensões.

Figura 2.19 – (a) MOS lateral convencional; (b) DMOS lateral de baixo Ron; (c)V-groove NMOS, (d) TMOS.

# 2.4.3 BCD5, Tecnologia da MICREL [2.54]

A MICREL é proprietária de uma tecnologia BCDMOS dedicada à realização de ASICs para aplicações em CIIP. Esta tecnologia é divulgada pela MICREL com o nome de BCD5, permitindo a combinação de dispositivos de alta velocidade e baixa tensão para a construção de circuitos digitais e analógicos com dispositivos DMOS de alta tensão, 100 V, utilizados tipicamente como circuito de excitação para interruptores de potência. Os dispositivos presentes nesta tecnologia são: DMOS alta tensão, PMOS FETs alta tensão, NPN alta tensão, diodo Schottky, diodo Zener, resistores e capacitores e transistores MOS tipo p e n para lógica transistores JFET. A tecnologia BCD5 é uma das tecnologias vocacionadas para a construção de dispositivos bipolares, utiliza a técnica de isolamento por junção e apresenta-se capaz de oferecer um processo tecnológico que resolve grande parte dos problemas de alta tensão e alta velocidade, a um preço muito competitivo no mercado para a fabricação de ASICs.

# 2.4.4 TrenchFETs, Tecnologia da TEMIC [2.55]

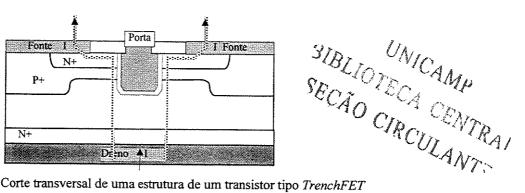

No primeiro semestre de 1999 a Siliconix, pertencente ao grupo da TEMIC Semiconductor, anunciou que havia superado todos os recordes da baixa resistência de condução para transistores encapsulados em cápsulas tipo elevado-volume. Esta tecnologia é apresentada pelo fabricante como sendo a tecnologia de potência mais avançada disponível no mercado atual. Este feito foi atribuído à tecnologia utilizada na construção do dispositivo de potência, que permite a construção da célula elementar compacta gerando um dispositivo de potência ultra denso. A tecnologia caracteriza-se principalmente pelo fato da porta do transistor ser construída dentro de uma "trincheira" cavada no silício, semelhante às utilizadas nas atuais tecnologias para a fabricação de memórias de alta densidade. Devido a esta característica, a Siliconix registrou o nome proprietário *TrenchFET* que caracteriza a tecnologia utilizada na construção deste dispositivo de potência. Um corte transversal ilustrando esta tecnologia é apresentado na Figura 2.20.

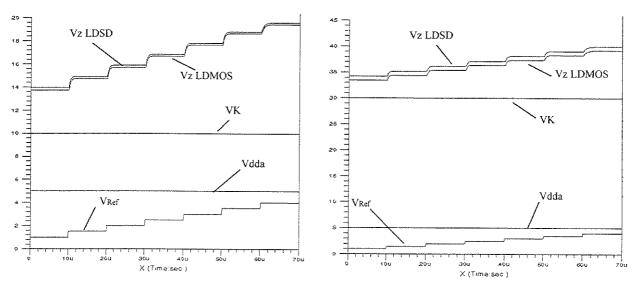

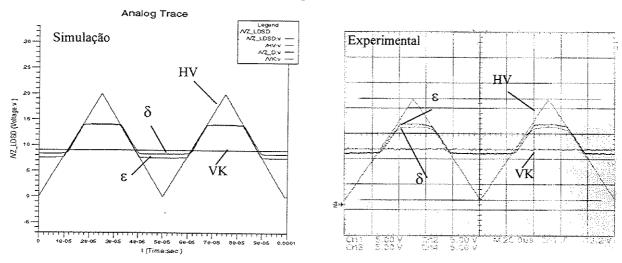

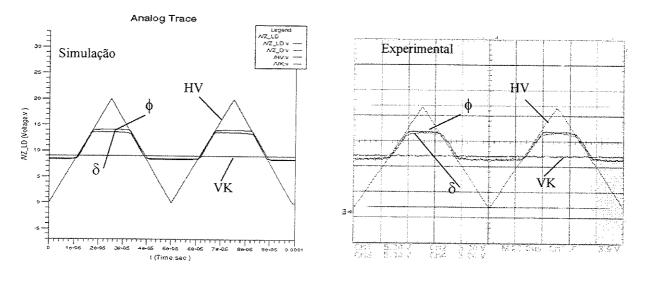

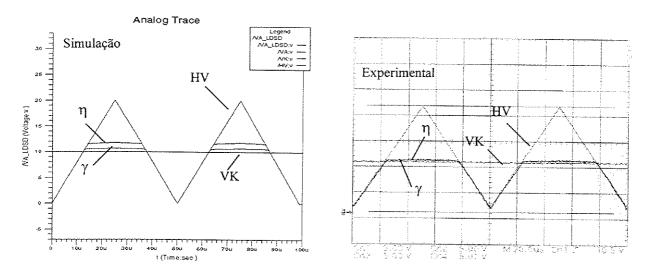

Outras melhorias importantes destacadas pelo fabricante são a redução significativa das capacitâncias parasitas quando comparado com as outras tecnologias e a capacidade da junção em operar a temperaturas de até 175°C. A faixa de tensão de operação dos dispositivos oferecidos no mercado varia de 12 a 80 V. Estes sucessos permitiram à Siliconix colocar no mercado