## Universidade Estadual de Campinas Faculdade de Engenharia Elétrica e de Computação Departamento de Semicondutores, Instrumentos e Fotônica

# "PROJETO DE UM CIRCUITO INTEGRADO DEDICADO À SIMULAÇÃO DE CIRCUITOS ULSI"

Autoria: Eliane França Orientador: Prof.Dr. Furio Damiani

Banca Examinadora:

Furio Damiani – FEEC/UNICAMP

José Carlos Pereira – EESC/USP(São Carlos)

Norian Marranghello – DCC/UNESP(São José do Rio Preto)

José Raimundo Oliveira – FEEC/UNICAMP

Marconi Kohm Madrid - FEEC/UNICAMP

Tese apresentada à FEEC/UNICAMP, como parte dos requisitos exigidos para obtenção do título de Doutor em Engenharia Elétrica, Área de Eletrônica e Comunicações

Campinas, Dezembro de 1999

| - ACA          |

|----------------|

| UNIDADE_BC_    |

| N. CHAMADA:    |

| TUNICAMP       |

| E 8446         |

| V. Es.         |

| TOMBO 80/41125 |

| PROC 278/00    |

|                |

| PRECO QB 11,00 |

| DATA           |

| N. CPD         |

CM-00142036-2

## FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

F844p

França, Eliane

Projeto de um circuito integrado dedicado à simulação de circuitos ULSI / Eliane França.--Campinas, SP: [s.n.], 1999.

Orientador: Furio Damiani.

Tese (doutorado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Arquitetura de computador. 2. Microprogramação. 3. Microprocessadores. 4. Aritmética de vírgula flutuante. I. Damiani, Furio. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

**G Senhor com sabedoria fundou a Terra; preparou os céus com inteligência.**Provérbios, 4-19

## Agradecimentos

A Deus, por ter-me permitido perseverar no caminho do conhecimento.

Aos meus pais, Lia e Dorvil e à minha irmã Dalva, pelo apoio, incentivo e dedicação que permitiram concentrar minhas atenções neste trabalho.

Ao Prof. Dr. Furio Damiani pela sua amizade e orientação.

Ao Prof. Dr. José Raimundo Oliveira pela sua disponibilidade, atenção e valiosas informações técnicas.

Ao Prof. Dr. Peter Jürgen Tatsch pelo apoio e amizade.

À minha amiga Raquel, secretária do DSIF, pela presteza, bom humor e eficiência no atendimento às solicitações de alunos e professores do Departamento.

À Dirce, Charles, Francisca e Sueli, pela amizade, confiança e companheirismo que sempre me dedicaram.

Ao CNPq e à Coordenadoria de Pós-Graduação, pela concessão da bolsa de estudos em parte do período do desenvolvimento do projeto.

#### Resumo

O objetivo deste trabalho é o desenvolvimento de um microprocessador dedicado para a simulação de circuitos ULSI – *Ultra Large Scale Integration*, ou seja, circuitos integrados de larga escala de integração. Ele faz parte de um arranjo de processadores proposto para um sistema de simulação por *hardware*, denominado ABACUS, desenvolvido no DSIF/FEEC/UNICAMP.

Dentro do ABACUS este microprocessador, denominado MPH – *Model Processing Hardware* (processador de modelos) é a célula unitária de um arranjo de microprocessadores.

A arquitetura do MPH é formada pelos seguintes blocos: registros de entrada e saída, memória para armazenamento do programa de descrição do modelo – UMA; memória para dados e resultados da simulação – MEL; controle microprogramado e Unidade Aritmética e Lógica em ponto flutuante para 32 bits.

Por apresentar uma arquitetura microprogramada, encontra aplicabilidade em outros sistemas dedicados tais como: satélite para previsão do tempo, robótica, redes neurais, *hardware* evolutivo, etc.

O projeto foi descrito em linguagem VHDL – VHSIC – (Very High Speed Integrated Circuits) Hardware Description Language e simulado em ambiente Mentor Graphics.

## **Abstract**

The aim of this work is the development of a custom microprocessor to simulate ULSI – Ultra Large Scale Integration circuits. It is part of an array of processors proposed as a system for circuit simulation by Hardware, named ABACUS.

Inside the ABACUS, the microprocessor, named MPH – Model Processing Hardware (model processor), is the basic cell of the microprocessor array.

The architecture of the MPH is composed by: input and output registers, memory to store the program of description model – UMA; a memory for the storage of simulation data and results – MEL; microprogramed control and Arithmethic and Logic Unit in 32 bits floating point.

As its architecture is microprogrammed, it can be employed in other custom systems like: time prevision satellite, robotics, neural networks, evolvable hardware and so on.

The design has been described in VHDL language – VHSIC Hardware Description Language and simulated in Mentor Graphics environment.

## Índice

## Introdução

## Capítulo I

| I.1 – Introdução                                               | 1  |

|----------------------------------------------------------------|----|

| I.2 - Fundamentos e Objetivos                                  | 1  |

| I.3 – Arquitetura do Sistema ABACUS                            | 2  |

| I.4 - Arquitetura do Microprocessador - MPH                    | 5  |

| I.5 - Ferramentas utilizadas para o desenvolvimento do projeto | 7  |

| I.6 – Comentários                                              | 7  |

| Capítulo II                                                    |    |

| II.1 – Introdução                                              | 1  |

| II.2 - Processamentos Computacionais                           | 1  |

| II.3 - Fundamentos sobre arquiteturas computacionais           | 2  |

| II.4 –Entrada e Saída                                          | 3  |

| II.5 - Unidade Central de Processamento                        | 3  |

| II.5.1 – Unidade de Controle                                   | 3  |

| II.5.1.1 – Microprogramação                                    | 5  |

| II.5.2 – Fluxo de Dados                                        | 9  |

| II.5.2.1- Unidade Lógica e Aritmética – ULA                    | 9  |

| II.5.2.1-1 - Representações Numéricas Binárias                 |    |

| de Números Inteiros Positivos e Negativos                      | 10 |

| II.5.2.1-2 - Operações Aritméticas em Ponto Fixo               | 11 |

| II.5.2.1-2.1 - Soma e Subtração em Ponto Fixo                  | 11 |

| II.5.2.1-2.2 - Multiplicação em Ponto Fixo                     | 16 |

| II.5.2.1-2.3 - Divisão em Ponto Fixo                           | 19 |

| II.5.2.1-3 - Padrão IEEE e Aritmética em Ponto Flutuante       | 21 |

| II.5.2.1-3.1 - Formatos Básicos                                | 22 |

| II.5.2.1-3.2 - Propriedades da representação numérica          |    |

| segundo o Padrão ANSI/IEEE 754                                 | 23 |

| II.5.2.1-3.3 - Formatos Numéricos                              | 23 |

| II.5.2.1-3.4 - Arredondamentos numéricos                                 | 24 |

|--------------------------------------------------------------------------|----|

| II.5.2.1-3.5 – Exceções                                                  | 25 |

| II.5.2.1-3.6 - Resumo do Formato                                         | 26 |

| II.5.2.1-3.7 - Considerações numéricas do projeto                        | 26 |

| II.5.2.1-4 - Operações Aritméticas em ponto flutuante                    | 26 |

| II.5.2.1-4.1 - Soma e Subtração em Ponto Flutuante                       | 27 |

| II.5.2.1-4.1-1 - Operação Efetiva                                        | 27 |

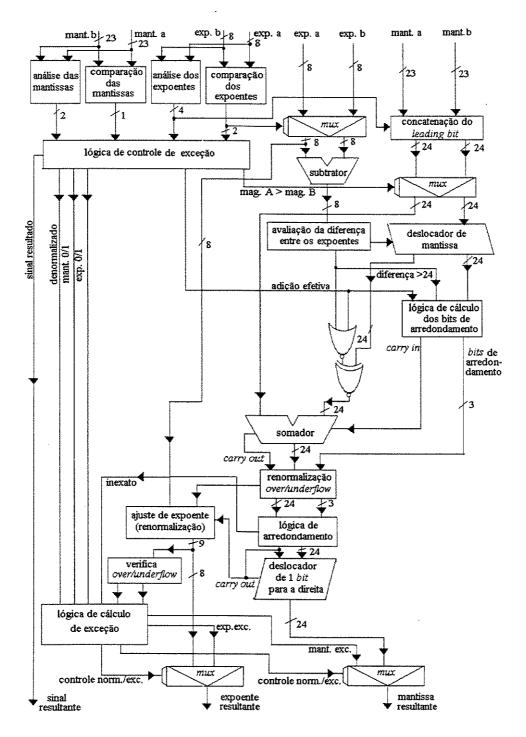

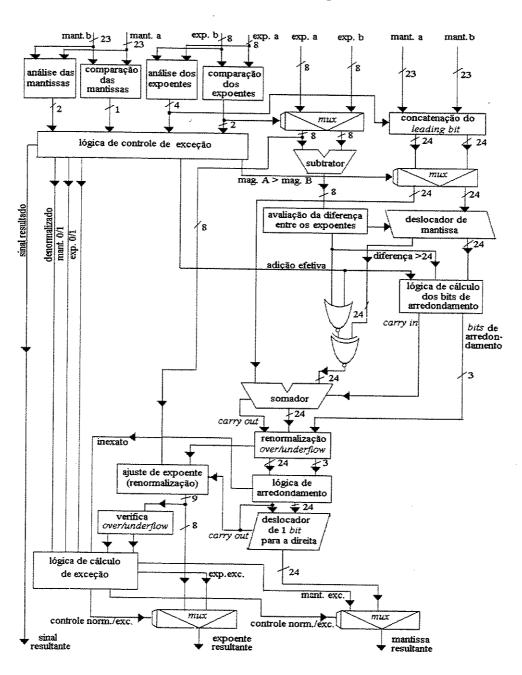

| II.5.2.1-4.1-2 - Arquitetura do Somador/Subtrator em Ponto Flutuante     | 27 |

| II.5.2.1-4.1-2.1 - Análise de Mantissas e Expoentes                      | 30 |

| II.5.2.1-4.1-2.2 - Comparação de Mantissas e Expoentes                   | 30 |

| II.5.2.1-4.1-2.3 - Lógica para Controle de Exceção                       | 30 |

| II.5.2.1-4.1-2.4- Multiplexação para Mantissas e Expoentes               | 31 |

| II.5.2.1-4.1-2.5 - Subtração e Avaliação de Expoentes                    | 31 |

| II.5.2.1-4.1-2.6 - Deslocamento de Mantissa                              | 31 |

| II.5.2.1-4.1-2.7 - Lógica de Cálculo dos Bits de Arredondamento          | 31 |

| II.5.2.1-4.1-2.8 - Soma de Mantissas                                     | 32 |

| II.5.2.1-4.1-2.9 - Renormalização de Mantissa                            |    |

| por causa de Overflow ou Underflow                                       | 32 |

| II.5.2.1-4.1-2.10 - Lógica de Arredondamento da Mantissa                 | 33 |

| II.5.2.1-4.1-2.11 - Deslocamento de 1 bit para a direita                 | 33 |

| II.5.2.1-4.1-2.12 - Renormalização de expoente (ajuste)                  | 33 |

| II.5.2.1-4.1-2.13 - Verificação de Overflow/Underflow do Expoente        | 34 |

| II.5.2.1-4.1-2.14 - Lógica para Cálculo de Exceção                       | 34 |

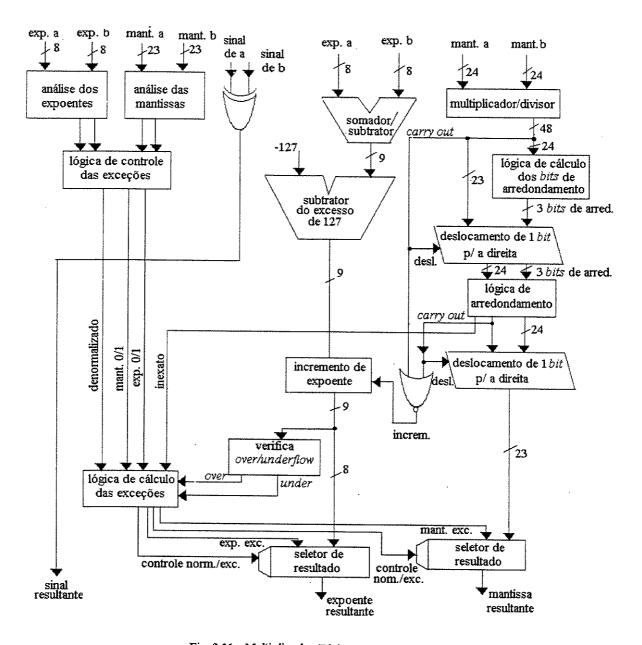

| II.5.2.1-4.2 - Multiplicação e Divisão em Ponto Flutuante                | 34 |

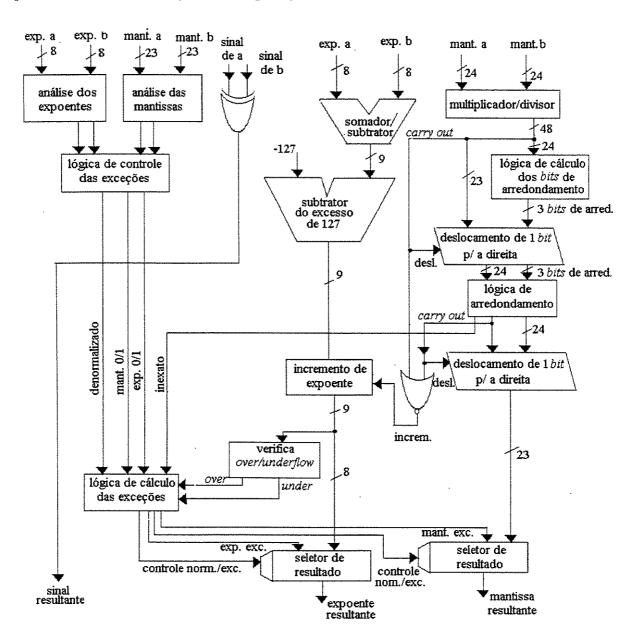

| II.5.2.1-4.2-1 - Arquitetura do Multiplicador/Divisor em Ponto Flutuante | 34 |

| II.5.2.1-4.2-1.1 - Análise de Mantissas e Expoentes                      | 36 |

| II.5.2.1-4.2-1.2 - Lógica de controle de exceção                         | 36 |

| II.5.2.1-4.2-1.3 - Lógica para obtenção do sinal resultado               | 36 |

| II.5.2.1-4.2-1.4 – Soma/Subtração de expoentes                           | 37 |

| II.5.2.1-4.2-1.5 - Subtração do excesso de 127                           | 37 |

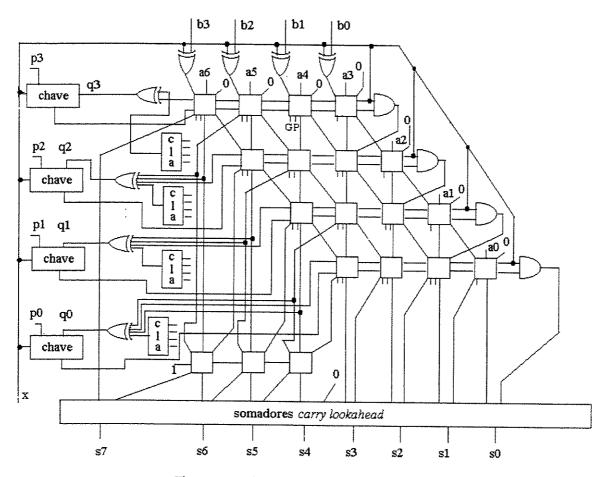

| II.5.2.1-4.2-1.6 - Multiplicação / Divisão de mantissas                  | 37 |

| II.5.2.1-4.2-1.7 - Lógica de cálculo dos bits de arredondamento          |    |

| da mantissa                                                              | 38 |

| II.5.2.1-4.2-1.8 - Lógica de Arredondamento da mantissa                  | 38 |

| II.5.2.1-4.2-1.9 - Deslocamentos de 1 bit para a direita                 | 38 |

| II.5.2.1-4.2-1.10 - Incremento de expoente                     | 38 |

|----------------------------------------------------------------|----|

| II.5.2.1-4.2-1.11 - Verificação de underflow e overflow        | 38 |

| II.5.2.2 – Registradores                                       | 39 |

| II.5.2.2-1 – Tipos de Endereçamento                            | 40 |

| II.6 – Memórias                                                | 41 |

| II.7 – Comentários                                             | 45 |

|                                                                |    |

| Capítulo III                                                   |    |

| III.1 – Introdução                                             | 1  |

| III.2 – Considerações gerais sobre o microprocessador proposto | 1  |

| III.3 – Arquitetura do MPH                                     | 2  |

| III.3.1 -Filas de Entrada/Saída                                | 3  |

| III.3.2 – Unidade de Controle                                  | 4  |

| III.3.2.1 - Registro de Instrução -IR - Instruction Register   | 5  |

| III.3.2.2 - Decodificador do Código de Operação (opcode)       | 5  |

| III.3.2.3 - Mmux - Multiplexador de Endereços para a           |    |

| Memória de Controle                                            | 5  |

| III.3.2.4 - Registro de Endereço da Microinstrução             | 6  |

| III.3.2.5 - Unidade de Modelos Armazenados - UMA               | 6  |

| III.3.2.6 - Registro da Palavra de Controle                    | 7  |

| III.4 - Campos da Palavra de Controle                          | 8  |

| III.5 - Decodificação da Microinstrução                        | 9  |

| III.6 – Registradores de Uso Comum                             | 9  |

| III.7 – Memória de Escrita e Leitura                           | 10 |

| III.8 – Repertório de Instruções previstas para o              |    |

| microprocessador                                               | 12 |

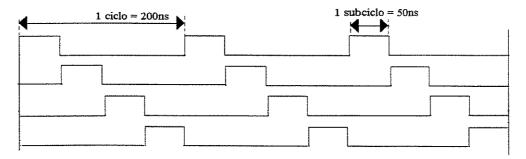

| III.8.1 - Base de Tempo para Execução das                      |    |

| Microinstruções                                                | 15 |

| III.8.2 - Algumas Instruções Descritas em Termos de            |    |

| Microinstruções                                                | 15 |

| III.9 – Modelos                                                | 16 |

| III.9.1 - Programa para o Cálculo da Corrente no Resistor      | 17 |

| III.9.2 - Programa para o Cálculo da Tensão no Resistor        | 18 |

| III.10 - ULA - Unidade Lógica e Aritmética em Ponto Flutuante  | 19 |

| III.10.1 - Registradores internos à UnidadeAritmética e Lógica | 20 |

| III.10.2 - Somador/Subtrator em Ponto Flutuante                 | 20 |

|-----------------------------------------------------------------|----|

| III.10.3 - Mutiplicador/Divisor em Ponto Flutuante              | 21 |

| III.10.4 - Funções Trigonométricas                              | 23 |

| III.11 - Comprovação de resultados                              | 24 |

| III.12 - Pinagem do Microprocessador                            | 25 |

| III.13 - Comentários                                            | 25 |

| Capítulo IV                                                     |    |

| IV.1 – Introdução                                               | 1  |

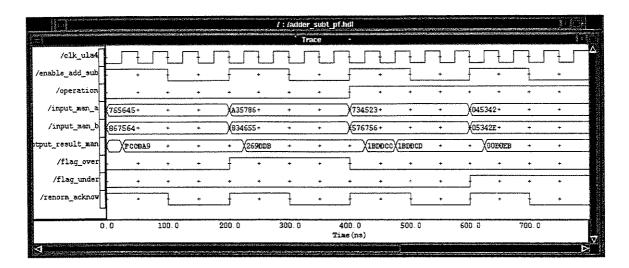

| IV.2 – Somador/Subtrator em Ponto Flutuante                     | 2  |

| IV.3 - Multiplicador/Divisor em Ponto Flutuante                 | 3  |

| IV.4 – Unidade de Controle Microprogramada                      | 7  |

| IV.5 – Tabelas Trigonométricas                                  | 9  |

| IV.6 – Comentários                                              | 11 |

| Capítulo V                                                      |    |

| V.1 - Introdução                                                | 1  |

| V.2 - Resultados da Unidade Aritmética e Lógica                 |    |

| em ponto flutuante                                              | 1  |

| V.2.1 - Somador/subtrator em ponto fixo                         | 1  |

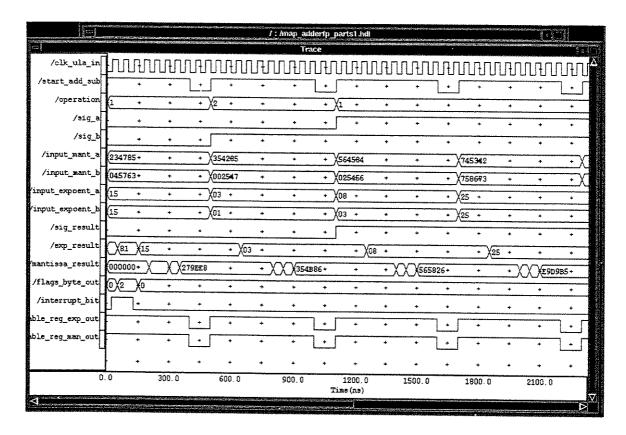

| V.2.2 - Somador/subtrator em ponto flutuante                    | 2  |

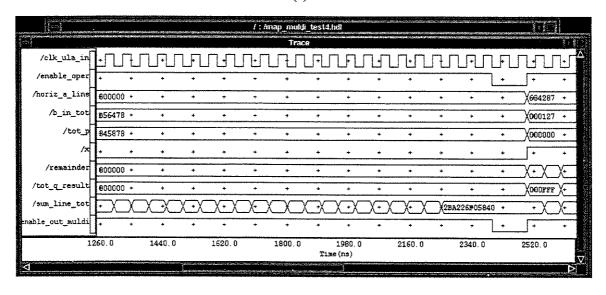

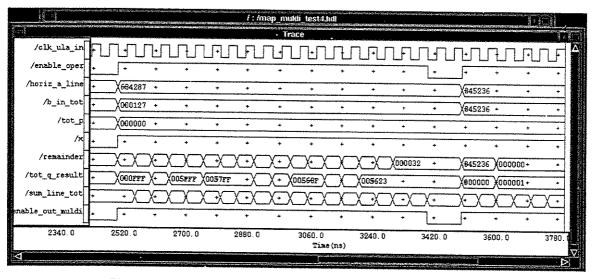

| V.2.3 – Multiplicador/divisor em ponto fixo                     | 4  |

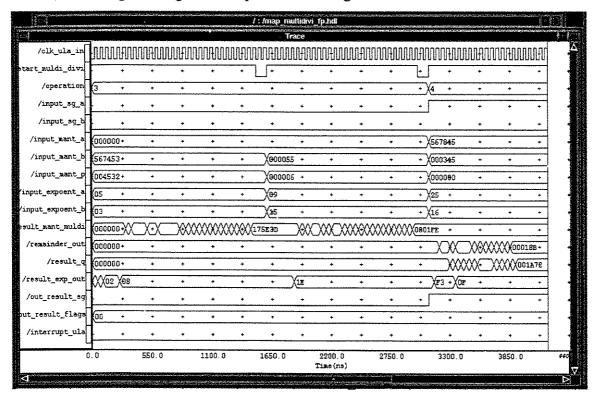

| V.2.4 - Multiplicador/divisor em ponto flutuante                | 6  |

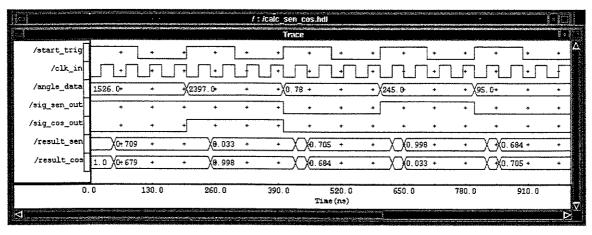

| V.3 – Resultados das funções trigonométricas                    | 8  |

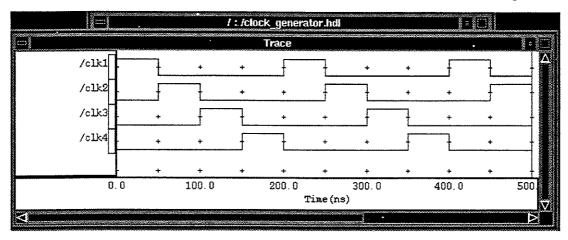

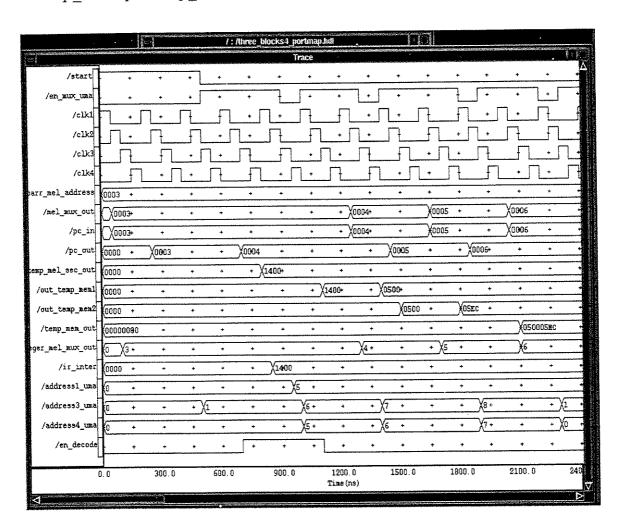

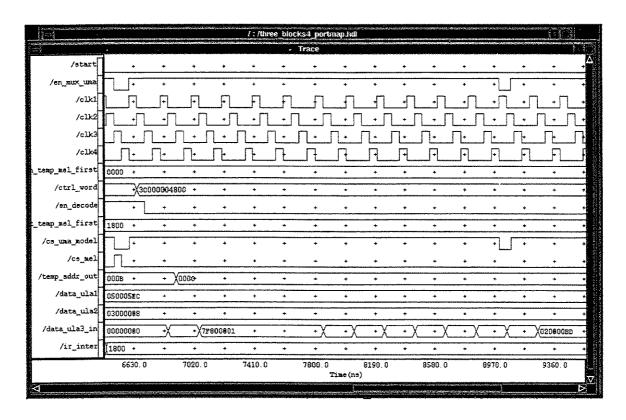

| V.4 – Resultados da Unidade de Controle                         | 9  |

| V.4.1 - Processamento de Instruções                             | 10 |

| V.5 – Processadores comercialmente disponíveis                  | 13 |

| V.6 – Análise dos resultados aritméticos obtidos para as quatro |    |

| operações fundamentais                                          | 15 |

| V.7 - Comentários sobre o desempenho do MPH                     | 15 |

| V.8 – Sugestões para trabalhos posteriores                      | 16 |

| V.9 – Conclusão                                                 | 16 |

## Introdução

O universo de ferramentas dedicadas utilizadas para auxiliar na concepção de projetos eletrônicos, CAD (Computer Aided Design), se constitui, nos dias de hoje, num aliado indispensável dos projetistas de circuitos integrados nas diversas etapas de projeto desde o desenvolvimento da arquitetura propriamente dita até a implementação da mesma, dada a alta complexidade das estruturas atualmente propostas.

O objetivo principal, em se gerar novas ferramentas, é buscar redução no tempo e custo de concepção de circuitos, através da automação de várias etapas da elaboração dos mesmos e também se adaptar às necessidades do mercado atual onde os circuitos tem apresentado a cada dia, um crescimento no grau de complexidade. Atualmente projetos que apresentam arquiteturas da ordem de milhões de componentes, como é o caso dos circuitos ULSI (Ultra Large Scale Integration), tornam inviável o uso de ferramentas utilizadas para desenvolvimento e simulações de estruturas de pequeno porte.

Em geral, as ferramentas de CAD usadas para simulação trabalham com a representação do comportamento do circuito integrado (CI). Com esta finalidade vários níveis de abstração podem ser considerados.

No nível mais elevado, com menor índice de detalhes, o modelamento se restringe à arquitetura do sistema, ou seja, a interação de grandes blocos ou subsistemas.

Em nível mais baixo, ou melhor, vislumbrando sua arquitetura mais intrínseca, o comportamento do circuito é tratado a partir do modelo de seus componentes elétricos: transistores, resistores, capacitores, etc. O particionamento do circuito se torna em uma estratégia importante na redução da complexidade para o tratamento de estruturas de grande porte.

Embora não exista uma classificação rígida para os simuladores de circuitos existentes, eles podem ser agrupados de acordo com os níveis de abstração adequados à modelagem dos circuitos analisados. Para os circuitos digitais temos a considerar cinco grupos [4]:

- simuladores a nível de arquitetura permitem a descrição funcional em alto nível dos grandes blocos funcionais que compõem o circuito as saídas são funções da entrada e dos estados internos.

- simuladores a nível de registradores o tratamento dos sistemas se dá a partir de modelos de blocos discretos mais detalhados como, por exemplo, unidades lógicas funcionais, tais como, contadores e registradores de deslocamento.

- simuladores a nível de lógica a descrição dos circuitos se dá a partir de portas lógicas elementares, tais como: portas NE (NAND), NOU (NOR), etc. Os níveis lógicos (0, 1, etc) são utilizados para análise das respostas do circuito em função do tempo, para sinais aplicados às entradas.

- simuladores a nível de temporização utilizam modelos simplificados de transistores para a avaliação de sinais de um circuito e técnicas de simulação lógica para a propagação dos valores dos sinais.

- simuladores a nível de circuitos que prevêem o desempenho do circuito a partir da utilização de dispositivos eletrônicos simulados, cujos parâmetros são obtidos por medidas em laboratório sobre dispositivos fabricados pelo mesmo processo a ser utilizado na integração do circuito.

Estas várias formas de tratamento da simulação devem portanto buscar a melhor adequação ao modelamento do circuito em análise.

É importante ressaltar que a discussão dada acima trata fundamentalmente de simulações de circuitos lógicos. Tradicionalmente faz-se uma divisão entre o procedimento para os circuitos lógicos e analógicos. Para os circuitos analógicos o procedimento de simulação se dá a partir de resolução de equações algébrico-diferenciais utilizando métodos implícitos de integração numérica, método de Newton para a solução de sistemas lineares esparsos. Por outro lado os circuitos digitais têm suas simulações fundamentadas no escalonamento de eventos (transições de estados).

Um fator relevante na observação de diferenças entre as simulações lógicas e analógicas é que as primeiras trabalham com um nível de abstração bastante elevado onde os transistores podem até serem tratados como simples chaves enquanto que os analógicos exigem um maior grau de definição do comportamento físico dos componentes envolvidos. O saldo resultante destas diferenças se observa na falta de detalhes do comportamento do circuitos lógicos ao longo do tempo em oposição ao tempo de execução da simulação de um circuito analógico.

As presentes pesquisas realizadas na área, inclusive neste trabalho, buscam simplicidade e rapidez nas simulações para circuitos lógicos aliada à riqueza de detalhes dos simuladores analógicos.

O procedimento encontrado para se aliar eficiência com detalhes de representação está na utilização de técnicas adaptativas, aplicadas nos simuladores híbridos, onde partes relevantes do circuito são resolvidas através de técnicas de simulação analógica enquanto parte significativa pode permanecer dormente durante parte da simulação, como por exemplo ocorre nos circuitos digitais em tecnologia MOS. Para se conhecer o que é

realmente relevante são utilizadas técnicas de escalonamento de eventos utilizada em simuladores lógicos.

Os simuladores híbridos correspondem ao estado da arte no ramo da simulação de circuitos e necessitam de um *hardware* onde diversas estruturas interajam paralelamente.

O propósito do trabalho aqui exposto é o desenvolvimento de um microprocessador dedicado à simulação de circuitos para a implementação de parte do algorítmo *ABACUS* (hArdware BAsed CircUit Simulator), proposto em trabalhos de pesquisa realizados na Faculdade de Engenharia Elétrica [1-4], na tese de Doutorado de Norian Marranghello [5] e na dissertação de Mestrado de Wilfredo Machaca Luque [6], ambas sob a orientação do Prof. Dr. Furio Damiani.

O ABACUS apresenta uma nova metodologia voltada à simulação de circuitos, onde se pretende tirar o maior proveito do casamento das mais eficientes variações arquiteturais com modernas técnicas de simulação; buscando a viabilização da simulação elétrica de circuitos ULSI constituída por milhões de componentes.

O microprocessador que aqui será apresentado é dedicado para o uso nesta ideologia proposta, recebe o nome do MPH (Model Processing Hardware) e se configura como a célula-mãe do sistema ABACUS de simulação, dado que o mesmo se fundamenta basicamente no uso de um arranjo de processadores, mapeados e configurados convenientemente para o projeto a ser simulado. Cada componente do circuito é representado no sistema por um destes processadores.

Uma característica peculiar desta proposta é que a simulação de qualquer componente do circuito a ser simulado, se processe por *hardware*, buscando assim significativa redução no tempo de processamento de circuitos ULSI.

Embora o circuito aqui desenvolvido tenha sido inicialmente proposto para o sistema acima mencionado veremos, durante o transcorrer da descrição do trabalho, que a sua utilização não se restringe somente a esta arquitetura, mas apresenta larga versatilidade de aplicações.

A dissertação desta tese segue a seguinte disposição:

- Capítulo I Apresentação do projeto Descrição sintetizada dos fundamentos do sistema de processamento e a apresentação funcional de cada bloco do conjunto previsto para operar o algoritmo proposto pelo ABACUS.

- Capítulo II Fundamentos Teóricos do Projeto Abordagens teóricas das técnicas necessárias para o desenvolvimento dos vários blocos formadores do microprocessador MPH.

- Capítulo III Desenvolvimento do Projeto Desenvolvimento do projeto propriamente dito com a escolha de arquiteturas adequadas, tomadas a partir do conhecimento das técnicas conhecidas no capítulo anterior.

- Capítulo IV Descrições VHDL e simulações dos blocos pertencentes à arquitetura do MPH Utilização da linguagem VHDL (VHSIC (Very High Speed Integrated Circuits) Hardware Description Language) na descrição e apresentação dos resultados dos circuitos formadores do MPH, simulados em ambiente Mentor Graphics.

- Capítulo V Análise dos resultados das simulações, conclusões e sugestões para trabalhos posteriores

- Referências Bibliográficas

## Capítulo I

## Apresentação do Projeto

#### I.1 - Introdução

Este projeto é parte integrante do desenvolvimento de uma nova metodologia para o processo de simulação de circuitos. Pretende-se criar uma estrutura de simulação fundamentada em processamento por *hardware* visando simplificar as simulações que geralmente se fundamentam na resolução de programas, onde se utilizam enormes sistemas de equações algébrico-diferenciais não lineares resultantes dos circuitos ULSI (Ultra Large Scale Integration).

A filosofia proposta é substituir as citadas equações por reduzidas expressões comportamentais de circuitos onde a simulação ocorra fazendo uso de um arranjo de microprocessadores sujeitos a um mapeamento pré definido.

Este trabalho versa portanto sobre o projeto deste microprocessador dedicado para o emprego no arranjo, parte integrante da arquitetura prevista para o simulador *ABACUS* (hArdware BAsed CircUit Simulator) [1]-[5], denominação dada ao sistema de simulação. O algoritmo foi desenvolvido por Norian Marranghello em sua tese de doutorado no DSIF/FEE/UNICAMP [5] e será abordado no transcorrer deste capítulo.

O sistema inicialmente previsto para simulações de circuitos busca a exploração do paralelismo dos arranjos computacionais de uma forma mais ampla, através da redução do tempo de simulação.

Este capítulo apresenta a proposta do sistema de simulação de uma forma ampla, com o objetivo de trazer ao leitor o conhecimento sobre a finalidade do microprocessador aqui desenvolvido que corresponde ao processo MPH (Model Processing Hardware), como será definido a seguir.

#### I.2 - Fundamentos e Objetivos

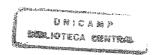

O simulador de circuitos *ABACUS* é baseado em *hardware* e projetado com a finalidade de executar simulações de circuitos VLSI e ULSI em alta velocidade, em um nível de detalhes comparável aos simuladores convencionais de bom desempenho. Seu diagrama de blocos pode ser visto na figura 1.1.

#### I.3 - Arquitetura do Sistema ABACUS

A arquitetura do sistema ABACUS prevê que o usuário mapeie circuitos ULSI, simule circuitos menores, visando uma redução na complexidade do circuito total. Estas simulações parciais, em um estágio final, devem ser utilizadas para o cálculo do resultado total.

O algorítmo de simulação pode ser representado através de cinco processos principais, quatro dos quais (HCP, HIP, HOP, AMP) rodariam no computador hospedeiro, ou seja, o detentor do mapeamento do circuito total e das diversas partições do circuito, e o quinto rodaria em cada MPH.

Vejamos a função de cada um destes processos [5]:

Fig. 1.1 - Arquitetura do "ABACUS"

Processo HIP (Host Input Process)

Processa os dados de entrada fornecidos pelo usuário, organizando-os para o tratamento pelos demais processos do simulador:

- 1 Lê o arquivo de entrada

- 2 Identifica os elementos do circuito

- 3 Identifica as análises a serem feitas

- 4 Monta a base de dados do circuito

- 5 Monta o grafo de interconexões do circuito

- 6 Verifica o número de MPHs disponíveis no arranjo

- 7 Particiona o circuito em subcircuitos (se necessário), de acordo com o número de MPHs disponíveis e mantem os componentes fortemente conectados no mesmo sub-circuito sempre que possível

- 8 Prepara cada (sub) circuito para simulação e transfere-o ao processo AMP (avisa o processo AMP a respeito disto)

- 9 Finaliza o processo HIP e sinaliza o processo HCP

#### Processo HCP (Host Control Process)

Este processo encerra a operação do ambiente de simulação e ativa e desativa cada um dos demais processos do computador hospedeiro, sempre que necessário. Tem também a função de controlar a operação do sistema de simulação, não no sentido de sincronização dos demais processos mas como um gerente assíncrono dos mesmos.

As etapas de processamento desta unidade podem ser então resumidas como se segue:

- 1 Inicia o processo de simulação

- 2 Inicia o processo HIP

- 3 Inicia o processo HOP

- 4 Termina quando todos os processos estiverem concluídos

#### Processo HOP (Host Output Process)

Este processo realiza a função inversa do HIP, ou seja, a partir das soluções geradas pelo simulador e da base de dados organizada pelo processo HIP, fornece as respostas solicitadas pelo usuário. Suas funções podem ser resumidas como a seguir:

- 1 Recebe a base de dados do HIP e formata-a para a saída

- 2 Recebe os resultados da simulação do processo AMP e formata-os para a saída

- 3 Quando os processos HIP e AMP sinalizarem o término de funcionamento, transfere os resultados finais formatados para a saída especificada pelo usuário

- 4 Encerra o processo HOP e avisa o fato ao HCP

#### Processo AMP (Array Manager Process)

Tem como objetivo controlar o funcionamento do arranjo de processadores, ou seja, controla a operação do arranjo fundamentado nos dados que cada processador do arranjo fornece-lhe. Etapas deste processo:

- 1 Verifica o número de MPHs disponível no arranjo, armazena-o e informa seu valor quando requisitado

- 2 Recebe um circuito do processo HIP

- 3 Mapeia o circuito nos processadores do arranjo

- 4 Estabelece o estado inicial do arranjo

- 5 Inicia o contador com o número de elementos do circuito mapeado

- 6 Incrementa e decrementa o contador, conforme o estado de convergência dos processadores do arranjo, até zerar o contador

- 7 Busca as soluções no arranjo

- 8 Transmite as soluções ao processo HOP

- 9 Repete os passos 2 a 8 até que todo o circuito seja simulado

- 10 Encerra o processo AMP, avisando os processos HCP e HOP

#### Processo MPH (Model Processing Hardware-element)

Executa efetivamente a simulação do circuito, com base nos dados a ele fornecidos pelo processo AMP. Suas etapas podem ser assim descritas:

- 1 Espera os dados do processo AMP

- 2 Identifica o elemento a ser simulado

- 3 Configura a ULA de acordo com o elemento

- 4 Busca os dados de entrada da memória do hospedeiro

- 5 Executa os passos:

- 5.1 Busca novos dados nas filas de entrada

- 5.2 Calcula o resultado correspondente ou decrementa o contador de AMP

- 5.3 Salva o resultado parcial na memória local e transfere-os para as filas de saída ou transfere as soluções para o processo AMP

- 5.4 Volta ao passo 5.1 ou passo 1

O processo de sincronização de tarefas dentro do sistema durante o processamento é obtido através de uma informação de uma "ficha" - tag, que o próprio dado carrega, semelhante aos computadores data-flow. Isto impede a ocorrência de superposição de eventos, o que conduziria a erros de simulação.

A arquitetura de arranjos de processadores é a forma de processamento escolhida para o projeto do arranjo de MPHs (Model Processing Hardware-element). Estes processadores dedicados à simulação de circuitos devem operar de modo assícrono.

O fluxo de sinais computacionais nos arranjos MPHs é semelhante ao que ocorre em redes reais. A cada vez que um novo subcircuito é mapeado a configuração de

arranjos é colocada, por programação, na rede de chaveamento, uniformente distribuída por todo o arranjo, tal que o número máximo de interconexões possíveis seja conseguida com um número razoável de barramentos e circuitos de chaveamento.

Do exposto acima podemos concluir que cada MPH deve ter a estrutura de um microprocessador dedicado à realização de equacionamentos matemáticos que descrevam os modelos dos componentes eletrônicos presentes nos circuitos.

#### I.4 - Arquitetura do Microprocessador - MPH

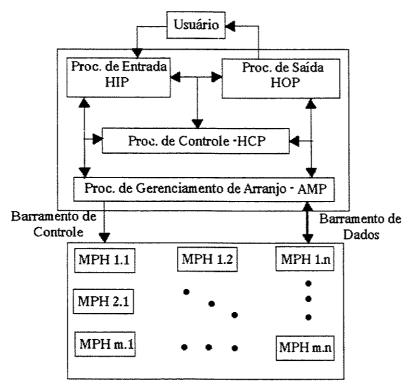

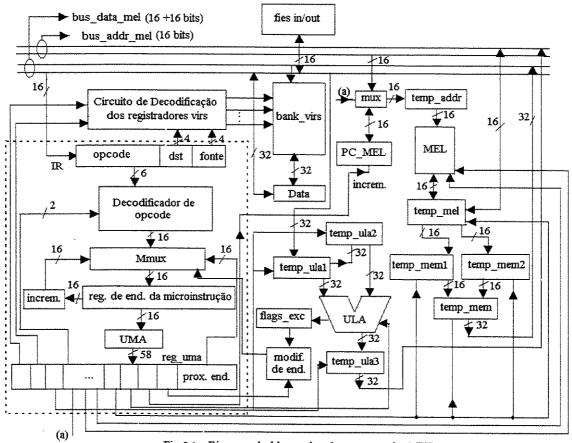

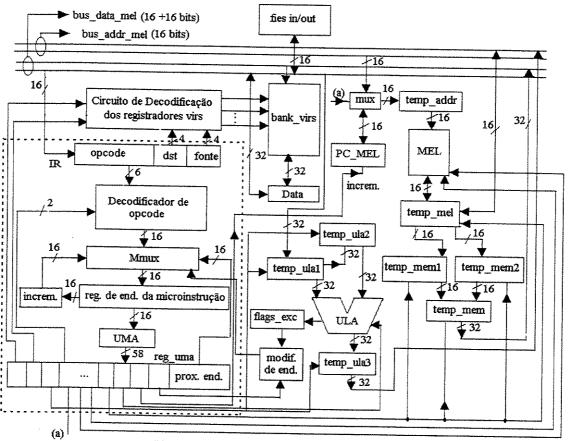

A arquitetura inicialmente prevista para o microprocessador aqui desenvolvido, pode ser visualizada na figura 1.2, a seguir:

- Fila de Entrada/Saída (FIES)

- Unidade Lógica e Aritmética (ULA)

- Unidade Elementar de Controle (UCE)

- Unidade de Modelos Armazenados (UMA)

- Memória de Escrita e Leitura (MEL)

FIES - São *buffers* de alta velocidade, responsáveis pela comunicação necessária entre os MPHs, na etapa de entrada dos dados ou saída dos resultados.

Fig. 1.2 - Arquitetura de um MPH

ULA - A Unidade Aritmética e Lógica é formada por somadores, subtratores, multiplicadores, divisores e unidades de deslocamento. Durante a fase do arranjo de configuração estas unidades podem ser convenientemente configuradas de acordo com os modelos dos dispositivos disponíveis na UMA.

Esta configuração só é alterada quando há o processo de troca do arranjo, ou seja, quando ocorre a mudança do circuito a ser simulado (programa presente na MEL, apresentada abaixo).

As operações matemáticas devem ocorrer com operandos representados em ponto flutuante, dado que os valores de componentes, suas correntes e tensões apresentam uma larga faixa numérica, sendo inviável suas representações por ponto fixo.

UCE - É uma unidade de controle cuja finalidade é controlar tanto o processamento dos MPHs como os seus interfaceamentos com o hospedeiro ou o resto do arranjo. A UCE controla três fluxos de informação: a sinalização para o gerente do estado de convergência do processador; a transferência das informações do gerente e dos resultados da simulação para o gerente e a comunicação dos resultados parciais da simulação entre os processadores. O controle interno de cada MPH é também realizado por esta unidade.

Neste trabalho, somente o controle interno individual de cada MPH será tratado, porque os demais controles, relacionados aos blocos externos ao MPH são realizados pelo controle do sistema *ABACUS* total.

No tipo de arquitetura prevista para este controle, por microprogramação, o procedimento para expansão do controle pode ser realizado de forma simples, como será esclarecido, no transcorer da dissertação.

UMA - É uma memória ROM – (Read Only Memory – memória somente de leitura) ou similar, de conteúdo endereçável, onde os diversos modelos conhecidos pelo ABACUS ficam alocados. Estes modelos podem ser definidos pelo usuário. Os modelos contidos na UMA são responsáveis pela configuração dos circuitos da ULA, durante a simulação de cada subcircuito, de acordo com o dispositivo a ser simulado.

Esta unidade deve ter armazenado um microprograma que aciona a ULA convenientemente, ou seja, a UMA deve armazenar o microprograma correspondente ao dispositivo simulado pelo MPH (resistor, capacitor, transistor, etc).

MEL - É uma memória de acesso aleatório, ou seja, uma RAM (Random Access Memory) utilizada para um armazenamento temporário, de curta duração, dos dados de entrada e dos resultados obtidos na simulação.

Durante o mapeamento do circuito o gerente armazena os dados de cada dispositivo simulado e aqueles relativos às análises, na MEL do MPH correspondente. Durante cada fase da simulação, as MELs ficam dedicadas ao respectivo MPH. A comunicação entre os MPHs se processa pelas filas de entrada e saída disponíveis (FIES). Ao detetar o fim da simulação o gerente lê os resultados na MEL de cada MPH.

Em resumo, esta arquitetura prevê a simulação do circuito por um tratamento real em condições de fluxo de sinais, ou seja, é como se os componentes estivessem alocados sobre uma *protoboard*. Esta forma de análise vislumbra o paralelismo em sua expressão mais ampla, ou seja, somente os instantes inicial e final do funcionamento dos processadores do arranjo são determinados pelo computador hospedeiro porém, durante a execução da simulação, os MPHs operam concorrente e assincronamente tanto entre si como em relação ao hospedeiro.

#### I.5 - Ferramentas utilizadas para o desenvolvimento do projeto

Para o desenvolvimento do projeto utilizamos sofisticadas ferramentas de projeto. As descrições dos circuitos estão na linguagem VHDL [73] ((VHSIC - Very High Speed Integrated Circuits) Hardware Description Language) que começou a ser desenvolvida em 1981 pelo Program Office of Department of Defense of United States com o objetivo de padronizar a linguagem de descrição de circuitos dentro da microeletrônica. Esta linguagem possibilita fazer descrições de circuitos desde altos níveis de abstração até a níveis de componentes, facilitando e documentando de forma significativa o trabalho do projetista de circuitos.

A disponibilidade do compilador desta linguagem (Design Architect) também como do simulador temporal - Quicksim, disponíveis no pacote de software da Mentor Graphics, na rede computacional do DSIF, da Faculdade de Engenharia Elétrica e de Computação, permitiram o desenvolvimento deste trabalho que envolve circuitos de alta complexidade.

#### I.6 - Comentários

Foram aqui expostos a arquitetura do sistema *ABACUS* de simulação, bem como os blocos previstos para o projeto do microprocessador MPH, objetivo deste trabalho. Estas informações nortearam a pesquisa de circuitos que devem ser utilizados em arquiteturas desta complexidade. Seguindo a disposição prevista na introdução, serão abordados no capítulo a seguir, os tratamentos técnicos referentes ao desenvolvimento destes circuitos.

#### Capítulo II

## Fundamentos Teóricos do Projeto

#### II.1 - Introdução

Vamos aqui apresentar os fundamentos teóricos utilizados no projeto do circuito do microprocessador MPH, célula básica do arranjo de microprocessadores do ABACUS [5].

Inicialmente far-se-á um breve relato sobre formas de processamento paralelo, para situar o leitor dentro do contexto. É importante ressaltar que não se fará um prolongado estudo sobre a arquitetura prevista para o sistema *ABACUS*, porque a nossa atenção estará voltada para o projeto do microprocessador MPH, que já exige um amplo conhecimento técnico, na elaboração de seus blocos formadores.

O desenvolvimento do projeto do MPH, requer de forma abrangente, o conhecimento de arquiteturas computacionais muito elaboradas. Faz-se necessário portanto, um estudo detalhado dos blocos formadores da arquitetura:

- Unidade de controle projetada com técnicas de microprogramação,

- Unidade aritmética e lógica que deve operar em ponto flutuante, realizando as quatro operações por *hardware*,

- Memórias e demais blocos formadores do microprocessador.

É importante ressaltar que o enfoque principal deste trabalho é o desenvolvimento do circuito do microprocessador o qual tornará viável a realização do sistema *ABACUS* de simulação.

## II.2 - Processamentos Computacionais

Os computadores tradicionais, realizam o processamento sequencial de tarefas. As instruções são executadas seguindo a ordem prevista pelo programador e é necessário que a execução de uma instrução seja concluída, para que outra venha a ser iniciada [7].

Estes sistemas ainda são muito utilizados; muitas formas de processamento paralelo têm sido desenvolvidas, nas quais os objetivos buscados são: reduzir o tempo de processamento e expandir a capacidade de processamentos.

Os computadores que operam com processamento paralelo podem ser divididos em três categorias [8]:

- Computadores *Pipeline* Um computador *pipeline* realiza computações sobrepostas para explorar o paralelismo temporal.

- Arranjo de Processadores Um arranjo de processadores usa diversas unidades aritméticas e lógicas para executar um paralelismo espacial.

- Sistemas de Multiprocessadores Um sistema de multiprocessadores realiza paralelismo assíncrono através de um conjunto de processadores interativos com recursos compartilhados (memórias, base de dados, etc.).

Estas três formas de paralelismo não são mutuamente exclusivas. Há computadores formados por arranjo de processadores ou sistemas de multiprocessadores e que são também *pipeline*.

Devido ao aumento exagerado na complexidade da unidade de controle, não se utiliza o paralelismo de forma mais ampla. É tarefa do projetista buscar estruturas que permitam conciliar simplicidade e desempenho.

O microprocessador aqui apresentado é, como já citado, a célula básica de um arranjo de processadores dedicado à simulação de circuitos. O esquema apresentado na figura 1.1 elucida o fato de que o sistema em forma de arranjo, explora o paralelismo espacial em procedimentos para simulações de circuitos de alta complexidade.

Faremos, a seguir, um estudo teórico das diversas unidades que compõem o microprocessador, o que permitirá estabelecer sua arquitetura.

## II.3 - Fundamentos sobre arquiteturas computacionais

Quando se projeta a arquitetura de um microprocessador [7],[9]-11] o primeiro passo é definir o caminho que os dados, endereços e resultados parciais de programas computacionais devem percorrer para que, através da execução das instruções, seja obtido como resultado final do processamento das tarefas previamente estabelecidas.

Para se compreender como os dados transitam pelos canais de informação e barramentos do microprocessador é necessário que se defina a sua arquitetura que é o meio físico que deve ser disponibilizado para que ocorra a troca de informações, de maneira organizada e previsível, entre os diversos blocos da máquina.

O meio físico ou circuitos, conhecido na literatura por *hardware*, deve ser projetado de forma a receber das vias de comunicação os sinais que tornam possível a realização de tarefas descritas em forma de programas, ou seja, o *software*.

A arquitetura de um microprocessador de uma forma geral compreende os seguintes blocos principais [7]:

- Entrada e Saída responsáveis pelo interfaceamento do microprocessador com o seu meio externo;

- Unidade Central de Processamento (UCP) formada pelos seguintes blocos:

- Unidade de Controle realiza o gerenciamento de execução de tarefas de forma ordenada;

- Fluxo de Dados constituído pelos seguintes sub-blocos:

- Unidade Aritmética e Lógica formada por circuitos que possibilitam a execução de operações matemáticas e lógicas;

- ◆ Registradores unidades de armazenamento temporário de dados e instruções utilizados no processamento.

- Memória Principal utilizada para o armazenamento do programa a ser executado pelo microprocessador;

Apresentaremos, a seguir estes blocos, enfocando suas principais características.

#### II.4 -Entrada e Saída

As filas ou *buffers* de entrada/saída, são formadas por registradores para o armazenamento temporário dos dados necessários para o processamento. Devem ser projetados de forma a possibilitar um rápido acesso aos dados neles contidos.

#### II.5 - Unidade Central de Processamento

#### II.5.1 – Unidade de Controle

A finalidade principal da Unidade de Controle é gerenciar a execução das tarefas, que são impostas à máquina, na forma de instruções previamente armazenadas em memórias. É o órgão principal do processador que comanda todas as unidades previstas na arquitetura.

Um processamento convencional para a realização de uma instrução compreende três etapas:

- Busca da Instrução

- Decodificação

- Execução

A busca da instrução consiste na captação, na memória que contém o programa a ser executado, da palavra de instrução. Nesta é encontrada, sob a forma de código de operação e de maneira implícita, a forma como os operandos, endereços ou endereços de dados devem ser trabalhados.

A seguir, esta instrução passa pelo processo de decodificação ou interpretação, para definição dos controles que realizem microoperações que levem à execução da instrução.

A execução da instrução se concretizará após o estabelecimento de todas as etapas previstas pelo seu código.

Para se definir a sequência de microoperações necessárias para a execução das instruções é necessário que se defina a forma pela qual a transferência dos dados ou endereços deve ser feita ou controlada, em intervalos de tempo convenientes.

A seguinte metodologia pode ser utilizada [7]:

- Analisam-se as exigências de transferência dos dados e endereços entre registradores

- Estabelecem-se os requisitos de fonte e destinação da Unidade Lógica e Aritmética.

- Simplificam-se os caminhos de dados, dentro das exigências de simultaneidade.

- Consideram-se o *clock* do fluxo de dados, as localizações, os atrasos e as possíveis necessidades dos registradores para reter os dados.

- Analisam-se os atrasos de *gate* do fluxo de dados e estima-se um tempo de ciclo mínimo do fluxo de dados que seja confiável.

Após definida a seqüência de execução das instruções, faz-se necessária a escolha da forma de controle a ser utilizada. Diversas são as técnicas conhecidas para realização desta etapa [9],[12]-[14], porém os controles podem ser classificados [13] em duas categorias:

- hardwired

- por microprogramação

Os controles hardwired são realizados a partir de:

- máquinas de estado de Moore e Mealy [9];

- circuitos combinacionais tais como: redes lógicas, multiplexadores e decodificadores.

A microprogramação [12],[13] utiliza-se de palavras de controle para o acionamento dos blocos formadores da arquitetura e tem se destacado em controles de alta complexidade. Foi a forma escolhida para o gerenciamento das instruções do nosso microprocessador e merecerá uma especial atenção nesta tese. Vejamos, a seguir, seus fundamentos e características.

#### II.5.1.1 - Microprogramação

A microprogramação foi definida por Maurice V. Wilkes da Universidade de Cambridge em 1950, como uma técnica utilizada para fazer a unidade de controle mais sistemática e flexivel [14].

Circuitos de controle projetados por microprogramação recebem instruções, interpreta-as e através de toda uma arquitetura particular, as transforma em sinais necessários ao controle da máquina.

O controle de informação é armazenado na forma de microprograma - sequências de microinstruções armazenadas em uma memória de controle.

Há geralmente um microprograma, ou seja, palavras de controle definidas e distintas para cada tipo de instrução, onde microinstruções são usadas em funções de fetching (procura) de instrução, de endereço ou operando e processos de interrupção. É uma filosofia diferente das unidades de controle que usam PLAs- Programmable Logic Array [9],[18] ou máquinas de estado, onde através de estruturas lógicas são construídos circuitos capazes de executar sequências necessárias para a realização de tarefas.

Na microprogramação o controle se dá por programa, viabilizando controles com maior número de opções ou complexidade, daí o seu uso inclusive em sistemas *pipeline* [8], onde problemas de acessos simultâneos ocasionados pela utilização de uma mesma unidade de processamento por tarefas concorrentes ocorrem com muita facilidade.

A principal exigência para controle microprogramável é que ele proporcione os vários sinais de controle necessários para cada estágio na sequência apropriada.

Um microprograma é executado procurando suas microinstruções uma a uma armazenadas em uma memória de controle. Cada microinstrução é carregada dentro do registro de microinstrução, de onde os correspondentes sinais de controle são obtidos, ocasionalmente depois de uma etapa de decodificação.

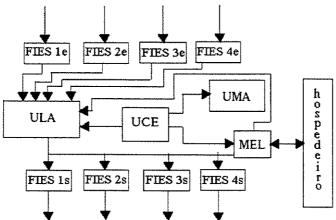

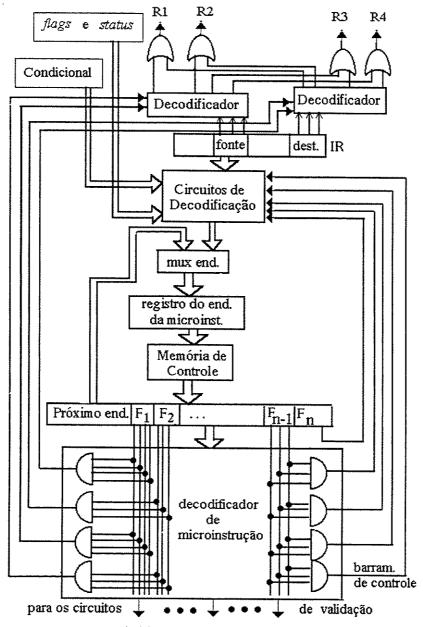

A figura 2.1, apresenta um diagrama de blocos [13] de um controle microprogramado clássico, que servirá de referência para a explicação de um circuito com este propósito. Nesta estrutura o registro de instrução IR é utilizado para armazenamento temporário da instrução que terá o seu código de operação decodificado pelos circuitos de decodificação. Estes fornecerão ao multiplexador (mux) de endereço (end)., o endereço da palavra de controle da instrução presente.

O endereço selecionado é temporariamente armazenado no registro de endereço da microinstrução para ser buscado na memória de controle.

A palavra de controle apresenta campos de próximo endereço e para controles gerais, denominados por  $F_1$  a  $F_n$ . O decodificador de microinstrução acionará convenientemente as unidades correspondentes para a realização da instrução como, por exemplo, habilitando registradores de uso comum R1 ou R2 como fonte e R3 ou R4 como destino de dados.

Nesta forma de representação da palavra de controle, o registro de próximo endereço do microprograma é parte integrante da palavra e faz referência à posição na

Fig. 2.1-Diagrama de blocos de um controle microprogramado clássico

memória de controle, da próxima microinstrução a ser usada.

Análises condicionais e ocorrência de *flags* ou *status* podem produzir desvios na seqüência de execução das instruções.

Em casos onde instruções necessitam de diversas etapas para completa execução, a seqüência de palavras de controle é dada através dos endereços previamente definidos pelo programador, no campo de próximo endereço utiliza-se o incremento de um para a obtenção das diversas etapas de execução e em caso de desvios condicionais, a unidade que realizou o teste da condição é que deve provocar a mudança na seqüência de leitura das palavras de controle.

É uma prática usual colocar a etapa de busca da instrução no endereço zero da memória de controle permitindo que, a cada final de execução de uma instrução o desvio ocorra para aquela posição [13].

É importante que se perceba a distinção entre instrução para máquina e para microprograma. Consideremos por exemplo, uma instrução típica de máquina para um microprocessador de 16 bits onde 6 bits são utilizados para código de operação possibilitando a definição de 64 ( $2^6$ ) instruções. Estas instruções serão decodificadas e uma máquina de estado será acionada para a realização das mesmas.

A instrução típica de microprogramação, por outro lado, pode conter um número maior de bits da ordem de 30 a 128 bits ou até mais bits em máquinas mais velozes [14]. Os diversos campos da palavra de controle microprogramada são usadas diretamente para controlar os vários dispositivos dentro da máquina.

Esta forma de controle é mais direta que o uso de lógica combinacional e conduz a projetos mais organizados[14].

Uma microinstrução geralmente tem duas partes a serem observadas:

- a definição e controle de todas as microoperações elementares a serem executadas.

- a definição e controle do endereço da próxima instrução a ser executada.

As ações controladas por microinstruções tomam a forma de microoperações que podem ser realizadas por *hardware*.

Estas microoperações incluem carregamento de registros, roteamento de dados via multiplexadores, decodificadores, barramentos, etc. Cada microinstrução define um conjunto de uma ou mais microoperações que podem ser realizadas simultaneamente em um ciclo de microinstrução.

Os projetos de microprogramas são geralmente implementados em uma linguagem simbólica chamada de *microassembly language*. O código fonte escrito nesta linguagem é

posteriormente traduzido por um programa *microassembler* e armazenado em uma memória de controle.

Como os microprogramas constituem uma forma de *software* mais próxima do *hardware*, sendo controlada por programas de instruções, são geralmente conhecidas como *firmware*.

Podemos ainda citar algumas características importantes na microprogramação [13]:

- 1. Os controles das funções são implementados por *software (firmware)* ao invés de *hardware*.

- 2. O processo do projeto é ordenado e sistemático.

- 3. Mudanças para acomodar novas especificações do sistema ou para corrigir erros de projeto podem ser implementadas rápida e economicamente.

- 4. Funções complexas tais como aritmética com ponto flutuante podem ser implementadas mais eficientemente por *firmware* do que por rotinas de instruções.

- 5. Microprogramação pode resultar em alguma redução na velocidade de processamento da instrução.

Embora a quinta característica apresente uma desvantagem desta técnica, este fator é compensado pela forma versátil e prática com que se pode realizar controles principalmente de máquinas complexas.

Escolhemos esta técnica devido a complexidade do circuito de controle para nosso microprocessador, como também em razão da necessidade de se conseguir um acionamento direto e imediato do controle a partir dos modelos de descrição dos componentes eletrônicos, buscando assim uma redução no tempo de processamento da simulação dos mesmos.

A primeira hipótese levantada para a utilização da microprogramação surgiu devido a constatação de que, por serem fixos os modelos dos componentes, este tipo de controle tomaria uma forma organizada, acelerando o processo de conclusão das simulações.

Posteriormente, modificamos a utilização da memória de modelos armazenados UMA, tornando-a retentora não mais dos modelos fixos mas, de controles responsáveis pela execução das instruções. Esta mudança contudo, não inviabiliza a forma de controle por microprograma mas, vem ampliar o espectro de utilização do projeto para os mais diversos tipos de aplicações.

#### II.5.2 – Fluxo de Dados

#### II.5.2.1- Unidade Lógica e Aritmética - ULA

Este bloco apresenta significativa importância na formação de uma arquitetura em computadores tanto sequenciais como por processamento paralelo, onde os primeiros constituem a base para o desenvolvimento de todos os sistemas computacionais, podendo estes conceitos serem ampliados para projetos de estruturas mais sofisticadas como é o caso dos que operam por processamento paralelo.

As operações geralmente realizadas por ULAs em microprocessadores, de finalidades matemáticas, são dentre outras as mais comuns: lógicas (*NAND*, *NOR* e *XOR*, etc.), deslocamentos e operações aritméticas, tais como, soma, subtração, multiplicação, divisão, etc. As operações matemáticas podem ser realizadas em ponto fixo ou ponto flutuante dependendo das aplicações previstas para o processador desenvolvido.

Em nosso projeto propomos uma ULA que realize as operações matemáticas necessárias à resolução de expressões que descrevam o comportamento matemático dos elementos de circuitos elétricos. Optamos pela resolução das quatro principais operações matemáticas por *hardware*.

Os valores de componentes, correntes e tensões a serem utilizados neste microprocessador podem utilizar uma ampla faixa de ordens de grandeza, portanto, as operações matemáticas devem ser processadas em ponto flutuante já que esta forma de representação, como veremos em breve, apresenta capacitação adequada para estes casos.

Como veremos, em etapas posteriores desta tese, o procedimento para o cálculo de resultados, quando as operações transcorrem em ponto flutuante, envolve importantes particularidades e mereceram uma descrição pormenorizada.

As operações aritméticas propriamente dita são semelhantes tanto quando trabalhamos com ponto fixo como ponto flutuante porém, neste segundo caso necessita-se de todo um tratamento numérico para a obtenção de resultados intermediários o que exige um alto grau de sofisticação do conjunto de circuitos dedicados para esta finalidade.

Veremos inicialmente, de forma sucinta, alguns conceitos importantes para a compreensão dos passos que, virão a constituir o projeto de uma unidade aritmética e lógica nos moldes aqui citados.

## II.5.2.1-1 - Representações Numéricas Binárias de Números Inteiros Positivos e Negativos

A nossa matemática convencional utiliza-se do sistema decimal (que não foi escolhida por acaso - dez é quantidade de dedos da mão) de representação numérica devido a grande facilidade mental de manipulação dos operandos quando se deseja realizar qualquer operação matemática. Esta forma de representação contudo, não se mostrou adequada quando se pretendeu projetar circuitos eletrônicos dedicados à resoluções matemáticas. Buscou-se na representação binária de sinais a facilidade de implementação utilizando o manuseio de circuitos aliado à alta versatilidade na aquisição de estruturas matemáticas. A álgebra booleana ou binária veio permitir um significativo avanço em projetos nas mais variadas áreas de aplicações.

Ao longo da história da engenharia eletrônica, surgiram diversas codificações binárias que sempre buscaram facilitar a representações de valores passíveis de modelamentos lógicos.

Vamos aqui apresentar as formatações mais utilizadas de representações numéricas que foram sendo padronizadas ao longo dos anos, como uma maneira de tornar homogênea a descrição de valores viabilizando os tratamentos algébricos por meio de máquinas.

Dado que diversas são as formas de representação numérica, é de fundamental importância que se tome conhecimento de qual formato está sendo utilizado durante todo o procedimento de desenvolvimento de projetos aritméticos para que se possa referenciar de maneira correta todo o processo utilizado para cálculos matemáticos.

Vamos abordar as seguintes representações numéricas binárias [7],[9]:

- Sinal e magnitude

- Complemento de um

- Complemento de dois

A representação por sinal e magnitude considera o *bit* mais significativo como referente ao sinal do operando, sendo 0 para positivo e 1 para negativo. Os demais *bits* indicam o valor numérico propriamente dito.

Os valores estão compreendidos no intervalo de  $(-2^{(n-1)} - 1)$  a  $(2^{(n-1)} - 1)$ , onde n é o número de bits utilizado para a representação binária.

Embora esta forma se caracterize por sua grande simplicidade, apresenta o inconveniente de possuir duas representações para o zero, ou seja, teríamos o zero positivo e o negativo. Este fato provoca uma dificuldade acentuada principalmente na realização de operações de adição e subtração.

O Complemento de Um consiste na complementação, ou melhor, na negação de todos os bits formadores do valor positivo, para representá-lo na forma negativa. Surge aqui o mesmo problema ocorrido no caso anterior, ou seja uma representação dupla para o valor zero. O intervalo de valores representáveis é o mesmo do anterior.

O Complemento de Dois consiste em somar mais 1 no *bit* menos significativo do complemento de Um do número. Esta forma veio solucionar o problema surgido nas representações anteriores, com uma única representação para o zero e apresenta valores no intervalo de  $(-2^{(n-1)})$  a  $(+2^{(n-1)})$ .

Os formatos sinal e magnitude e complemento de dois serão utilizados intensivamente durante todo o procedimento de tratamento dos operandos dentro das unidades operadoras de processamentos matemáticos.

#### II.5.2.1-2 - Operações Aritméticas em Ponto Fixo

#### II.5.2.1-2.1 - Soma e Subtração em Ponto Fixo

Estas duas operações podem ser tratadas simultaneamente porque a partir de um controle, que indica o sinal de um dos operandos se positivo ou negativo, pode-se identificar se tratar de uma operação de soma ou subtração respectivamente. Isto facilita a implementação destes dois operadores de uma única vez.

Para se projetar um somador ou qualquer outro operador matemático partimos inicialmente da tabela verdade, construída sob os princípios da álgebra booleana em conformidade com as expressões matemáticas que satisfaçam a realização da operação desejada. O circuito utilizando portas lógicas, deve obedecer a estas expressões, gerando assim a operação matemática propriamente dita.

Inicialmente vejamos a forma mais simples de soma de dois valores, ou seja, um meio somador ou *half adder*, como é denominado na literatura de circuitos digitais [15],[16].

A Tabela 2.1 mostra os possíveis estados do meio somador e a Fig.2.2 apresenta um circuito lógico que implementa esta função.

| A | В | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Tabela 2.1 – Tabela Verdade do meio somador

Na tabela 2.1 A e B correspondem aos operandos de entrada, S é o resultado da soma e C é o *carry*, ou seja, o "vai um" da operação entre os dois operandos.

Por análise, dos termos da expressão lógica que define o resultado da soma S, podemos verificar que a soma consiste da operação lógica *EXCLUSIVE-OR* dos dois operandos e o *carry* é formado pela operação *AND* entre as duas entradas do somador, que simbolicamente representamos por:

Fig. 2.2 - Meio Somador - Half Adder

A ilustração da figura acima, recebe a denominação de meio somador, porque não prevê a propagação do termo "vai um", ou seja, o carry.

Uma configuração mais completa, que segue o comportamento apresentado pela tabela 2.2, prevê a propagação das componentes "vai um" e constitui um somador *Full Adder*, ou seja, somador completo.

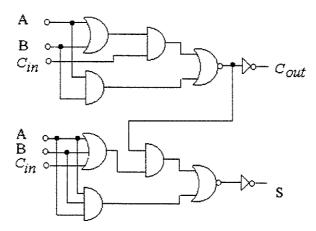

Estes somadores (Fig. 2.3) podem ser facilmente obtidos a partir de circuitos lógicos combinacionais, o que lhes atribui a denominação de somadores combinacionais (combinational adder).

| A | В | Cin | Soma | Cout |

|---|---|-----|------|------|

| 0 | 0 | 0   | 0    | 0    |

| 0 | 0 | 1   | 1    | 0    |

| 0 | 1 | 0   | 1    | 0    |

| 0 | 1 | 1   | 0    | 1    |

| 1 | 0 | 0   | 1    | 0    |

| 1 | 0 | 1   | 0    | 1    |

| 1 | 1 | 0   | 0    | 1    |

| 1 | 1 | 1   | 1    | 1    |

Tabela 2.2 – Tabela Verdade do somador completo

A expressão para a soma, pode ser então obtida:

Soma = A xor B xor Cin

ou seja, a soma é o resultado da operação lógica XOR ou EXCLUSIVE-OR dos dois termos A e B com o Cin (carry de entrada) resultado da soma de parcelas anteriores.

Esta expressão pode ser reescrita a partir de seu equivalente lógico utilizando portas *AND* e *OR*, resultando:

$$Soma = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC}$$

Obs: Os grifados correspondem aos sinais complementares,

O Cout (carry de saída), ou seja, o "vai um" gerado pela soma é dado por:

$$Cout = AB + ACin + BCin$$

Estas são as células básicas utilizadas para a soma de dois *bits* de operandos distintos. Esta estrutura pode ser repetida na intenção de se obter somadores com um maior número de *bits*. Através da repetição destas células pode-se também implementar multiplicadores, como veremos oportunamente.

Fig. 2.3 - Somador Completo - Full Adder

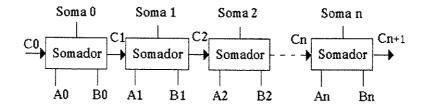

A soma de vários *bits* pode ser realizada pelo simples cascateamento destes somadores onde o sinal de *carry* se propaga pelos estágios, ou seja, a entrada do estágio posterior recebe sinal de *carry* anterior. Isto significa que o sinal de *carry* modula o sinal de entrada. Por este motivo este tipo de circuito é também conhecido por *ripple adder* (somador modulado).

Embora práticos estes somadores apresentam um forte atraso na propagação do sinal de *carry* pela rede de somadores, o que os tornam inadequados para aplicações onde um maior número de *bits* e velocidade de execução da operação de soma são necessários. A figura 2.4, a seguir, apresenta este tipo de arranjo para n *bits*.

Nesta estrutura, um grande atenuador na velocidade de execução de operações de soma é o elemento de *carry* - Cn que deve se propagar de forma rápida por toda a rede somadora, atingindo com isso uma otimização na velocidade de obtenção do resultado.

Fig. 2.4 - Somador ripple carry de n bits

Estes problemas podem ser solucionados por várias técnicas [17]: carry-lookahead, carry-skip, carry-predict, carry-select, também com combinações entre essas técnicas que objetivam a redução no tempo de propagação do carry, onde estes fatores são tratados de forma diferenciada à prevista por ripple carry. O estudo destas técnicas é muito extenso e foge ao objetivo principal deste trabalho, podendo ser minuciosamente conhecido na referência dada acima.

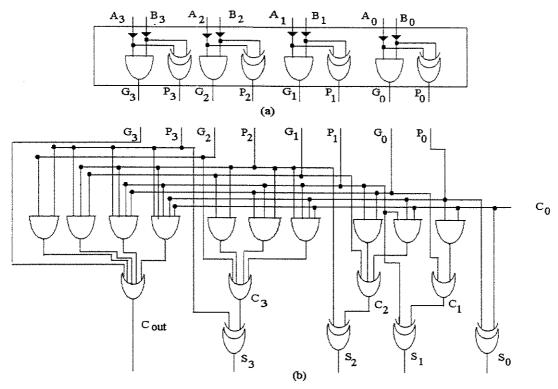

Vamos nos restringir à analise da técnica de *carry-lookahead*, para o tratamento da propagação do *carry*, por ser uma técnica clássica, simples e de eficiência comprovada.

As expressões para soma S e *carry* de saída - Cout de cada parcela, são válidas, independentemente da técnica adotada, contudo, o cálculo antecipado do *carry* de agrupamentos de parcelas, agilizam em muito a obtenção do resultado do *carry* da soma final.

Para tanto iniciemos o processo de análise do somador a partir da observação das propriedades do sinal de *carry*.

Pela tabela verdade anteriormente exposta notamos o seguinte: em situações nas quais as entradas A e B são nulas o *carry* de saída também é nulo. Quando tanto A quanto B são iguais a 1, o *carry* de saída também é igual a 1 e para A e B diferentes entre si o *carry* de saída é igual ao da entrada. Estas propriedades levaram os projetistas a caracterizarem dois tipos de *carries: Propagate* (P) e *Generate* (G), sendo:

$$P = A xor B e G = A and B$$

.

Desta forma uma nova tabela (Tabela 2.3) pôde ser elaborada, onde se observam as diversas expressões que caracterizam um somador completo. Além das expressões de soma e *carry* de saída, já anteriormente constatadas, dispomos agora dos parâmetros P e G para uma melhor avaliação de como se comportam os *carries* envolvidos em somadores com qualquer número de *bits*.

Visto que atrasos relacionados à propagação do *carry* podem se tornar significativos quando há um maior número de *bits*, podemos dividir os *bits* formadores dos operandos em estágios e resolver as parcelas destes estágios simultaneamente, agilizando o processo de obtenção do resultado final.

| Α | В | Cin | P | G | S | Cout |

|---|---|-----|---|---|---|------|

| 0 | 0 | 0   | 0 | 0 | 0 | 0    |

| 0 | 0 | 1   | 0 | 0 | 1 | 0    |

| 0 | 1 | 0   | 1 | 0 | 1 | 0    |

| 0 | 1 | 1   | 1 | 0 | 0 | 1    |

| 1 | 0 | 0   | 1 | 0 | 1 | 0    |

| 1 | 0 | 1   | 1 | 0 | 0 | 1    |

| 1 | 1 | 0   | 0 | 1 | 0 | 1    |

| 1 | 1 | 1   | 0 | 1 | 1 | 1    |

Tabela 2.3 – Tabela verdade para o somador completo com avaliação de *carry generate* (G) e *propagate* (P)

A expressão que define o carry, como analisado anteriormente, é dada por:

$$Cout = AB + (A+B)Cin$$

O carry devido ao iésimo estágio pode ser expresso por:

$$Ci = Gi + Pi \cdot Ci-1 \tag{2.1}$$

onde

$$Gi = Ai \cdot Bi$$

(carry gerado)

$Pi = Ai \oplus Bi$  (carry propagado)

$$Ci-1 = Gi-1 + Pi-1$$

.  $Ci-2$  (2.2)

e assim por diante, por indução, chegamos a uma expressão geral que define a expansão dos *carries* dada por:

$$Ci = Gi + PiGi-1 + Pi Pi-1 Gi-2 + ... + Pi ... P1 C_0$$

(2.3) e para a soma,

$$Si = Pi \oplus Ci + 1 \tag{2.4}$$

Estas expressões condensam o comportamento de somadores *carry-lookahead* e serão amplamente utilizadas na descrição de circuitos que envolvam somas binárias neste projeto.

## II.5.2.1-2.2 - Multiplicação em Ponto Fixo

A multiplicação em sua forma mais simples é realizada envolvendo dois operandos. Seguindo o conhecimento básico de execução desta operação, sabemos que ela é realizada a partir de operações de somas e deslocamentos. O processo se constitui portanto, de duas etapas:

- execução de produtos parciais

- alocação de produtos parciais deslocados

A execução dos produtos parciais consiste da operação *AND* de cada bit do multiplicando por todos do multiplicador seguindo-se deslocamentos para alocação dos produtos parciais de acordo com a posição ocupada pelo *bit* do multiplicador envolvido.

Após a realização dos produtos parciais deve-se proceder os deslocamentos convenientes, para que se processe a soma dos subprodutos de forma correta.

Há várias técnicas para se realizar multiplicações e são inúmeras as arquiteturas elaboradas para esta finalidade, sendo extensa a literatura disponível[16],[18]-[24].

Características tais como, velocidade, precisão numérica, compactação, e multiplicidade de execução de operações entre outras é que nos conduzem a escolha de determinada arquitetura.

O desempenho deve pesar na escolha da complexidade do circuito.

Podemos optar por diversas formas de execução de operações de multiplicação, como exposto a seguir [18]:

- serial

- serial/paralela

- paralela

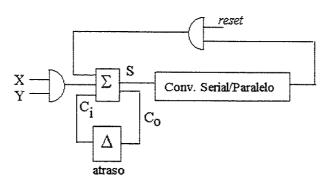

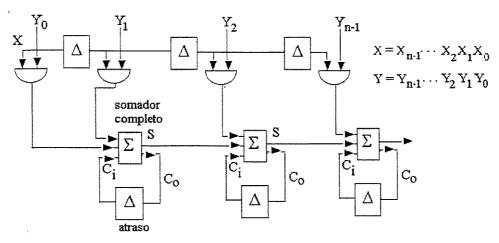

Serial – A forma mais simples de multiplicador serial, ilustrada na figura 2.5, opera

Fig. 2.5 - Um multiplicador serial básico

através de somas sucessivas realizadas por somadores completos—*full adder*. Embora seja facilmente concebível, por se tratar de uma estrutura serial, apresenta significativo comprometimento na velocidade de operação.

Os dados X,Y,Ci são injetados na unidade somadora  $\Sigma$  de forma sequencial, em intervalos de tempos diferenciados para multiplicando e multiplicador. Ocorre um atraso  $\Delta$ , no rearmazenamento do *carry* resultante em cada etapa do resultado parcial.

Os resultados parciais são armazenados temporariamente no conversor serial/paralelo até que todos os *bits* envolvidos na multiplicação sejam convenientemente processados. O sinal de *reset* é acionado a cada início de processamento, para inicialização da geração do resultado.

Serial/Paralela – Fazendo uso de várias unidades da forma anteriormente citada, pode-se obter um produto a partir da soma de sucessivas colunas da matriz de produtos

Fig. 2.6 - Estrutura básica para um multiplicador serial/paralelo

parciais deslocados, fig.2.6. Aqui a principal limitação é a freqüência máxima de operação que é limitada pelo tempo de propagação, pelo arranjo de somadores.

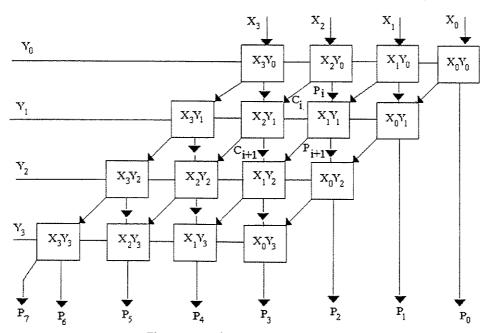

Paralela – Esta forma de obtenção de produto se baseia na possibilidade de que produtos parciais são independentemente calculados e podem ser computados paralelamente. A figura 2.7 mostra uma célula simplificada que pode ser utilizada para construir um multiplicador paralelo. O termo Xi de um dos operandos se propaga verticalmente, enquanto que o termo Yi correspondente ao outro operando e se propaga horizontalmente.  $C_i$  corresponde ao *carry* de entrada,  $P_{i+1}$  ao produto parcial e  $C_{i+1}$  ao *carry* resultante obtido em cada célula.

Vejamos, por exemplo, a multiplicação de dois operandos X e Y, que podem ser representados por uma somatória de dígitos binários, de acordo com a representação usual.

$$X = \sum_{i=0}^{m-1} X_{i2}^{i}$$

,  $Y = \sum_{j=0}^{m-1} Y_{j2}^{j}$

O produto de X por Y fica determinado por P<sub>t</sub>:

$$P_{t} = X_{t}Y = \sum_{i=0}^{m-1} X_{i} 2^{i} \cdot \sum_{j=0}^{m-1} Y_{j} 2^{j} = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} (X_{i} Y_{j}) 2^{i+j} = \sum_{k=0}^{m+n-1} P_{k} 2^{k}$$

Onde  $P_k$  são os produtos parciais. Cada um dos termos dos subprodutos é produzidos por portas AND. Há m x n destes subprodutos produzidos de forma paralela. O problema básico em projetos para alta velocidade é reduzir o tempo de somar os 1s em cada coluna da matriz de subprodutos resultante. Um multiplicador de n x n algarismos [18] necessita de n(n-2) somadores completos, n meio somadores e  $n^2$  portas AND. O atraso de pior caso associado com tal multiplicador é  $(2n+1).\tau_g$ , onde  $\tau_g$  é o atraso de cada somador nestas condições.

As estruturas da fig.2.7 podem ser agrupadas, como ilustrado na fig.2.8, de forma a

Fig. 2.8 - Arranjo multiplicador paralelo

se obter o produto de vários bits, de forma simplificada.

Um fator de atenuação na velocidade de execução da operação nestes multiplicadores é o que se refere ao processo de soma dos diversos fatores de uma mesma coluna obtida dos produtos parciais, devido a presença dos *carries* propagados.

A solução para este problema consiste em se utilizar um arranjo de *carry lookahead* para reduzir o tempo de execução da operação.

#### II.5.2.1-2.3 - Divisão em Ponto Fixo

Várias são as técnicas utilizadas para a obtenção da divisão [16],[19],[21],[22]. Geralmente os processos de divisão consistem de três partes: inicialização dos operandos, geração do quociente e determinação do resto.

Na inicialização dos operandos procede-se a padronização do dividendo e divisor, ou seja, a definição dos operandos em algum sistema de representação numérica e a avaliação do possível *overflow* do quociente.

A geração do quociente consiste na seleção dos dígitos do quociente sequencialmente do mais significativo ao menos significativo.

A obtenção do resto se dá, em geral, automaticamente ao final do processo de geração do quociente.

Os processos de divisão podem ser classificados, dependendo dos valores permitidos de cada dígito do quociente gerado, em duas principais categorias [16]: restoring ou nonrestoring, ou seja, por rearmazenamento ou não, respectivamente.

Em uma divisão por rearmazenamento - restoring com base ou raiz - radix r, cada dígito do quociente é selecionado do conjunto convencional de dígitos

$\{0,1,2,\ldots,r-1\}$ . O valor de cada dígito de quociente  $q_{j+1}$  para  $j=0,1,\ldots n-1$  é selecionada para satisfazer a equação:

$$0 \leqslant R_{j+1} \le D$$

, onde R é o resto

O critério de seleção de quociente pode ser implementado com sucessivas subtrações do divisor D do dividendo parcial corrente r x R<sub>j</sub>, até que a diferença se torne negativa. O número de subtrações realizadas antes que o resto se torne negativo determina o valor do dígito do quociente a ser selecionado.

Vejamos um exemplo:

Dados:

dividendo  $(0.1257)_{10}$

divisor D = 0.39 para r = 10

resulta em:

1.257 - 0.39 = 0.867 (> 0) - primeira subtração

0.867 - 0.39 = 0.477 (> 0) - segunda subtração

0.477 - 0.39 = 0.087 (> 0) - terceira subtração

0.087 - 0.39 = -0.69 (< 0) - quarta subtração

resultando  $q_1 = 3$  (número de vezes, com resultado positivo, que o divisor foi subtraído do dividendo)

> restoring ou rearmazenamento para adição  $0.087 \rightarrow 0.87$ 0.87 - 0.39 = 0.48 (> 0) - primeira subtração 0.48 - 0.39 = 0.09 (> 0) - segunda subtração 0.09 - 0.39 = -0.30 (< 0) - terceira subtração resultando  $q_2 = 2$  (idem ao anterior)

Portanto o quociente será: 0.32

O resto será 0.09 x 10-2

Na divisão nonrestoring os dígitos do quociente são selecionados do conjunto de dígitos sinalizados, com zero excluído. A operação a ser realizada por cada resultado parcial do arranjo nonrestoring é adição ou subtração dependendo se o sinal do resultado anterior é o mesmo sinal do dividendo.

$$\{-(r-1), -(r-2), \ldots, -1, +1, \ldots, r-2, r-1\}$$

Exemplo:

Dividendo N =  $(0.101001)_2$  =  $(41/16)_{10}$

Divisor D =  $(0.111)_2 = (7/8)_{10}$

Subtração:

0.101001 - 1.001 - divisor em complemento de 2 = 1.110001 < 0

$q_0 = 0$  - resto parcial negativo

Resto deslocado: 1.10001

1.10001 + 0.111 = 0.01101 > 0 $q_1 = 1$

Resto deslocado: 0.1101

0.1101 - 1.001 = 1.11111 < 0 $q_2 = 0$

Resto deslocado: 1.111

1.111 + 0.111 = 0.110 > 0 $q_3 = 1$

Quociente  $Q = q_0 q_1 q_2 q_3 = (0.101)_2 = (5/8)_{10}$

Resto =  $(0.00r_3r_4r_5r_6)_2 = (0.000110)_2 = (6/64)_{10}$

Por análise da exposição sobre as operações de multiplicação e divisão, concluímos que as duas operações podem ser solucionadas utilizando circuitos de soma ou subtração contínuas, respectivamente.

Das opções de arquitetura de circuitos apreciadas nas diversas estruturas, que permitem a realização destas operações, escolhemos a referência [19], por esta apresentar uma forma circuital muito transparente de visualização e com excelente nível de precisão de resultados.

Esta escolha, embora muito interessante pela precisão apresentada, mostrou-se de difícil obtenção em termos de descrição de circuito na linguagem VHDL, tendo exigido particular atenção na definição de índices e expressões lógicas, vindo a culminar na criação de uma variação na arquitetura exposta na referência. No capítulo III será apresentado o diagrama da referência citada e discutidas as modificações realizadas.

As formas de obtenção de operadores vistas até aqui constituem os casos clássicos de operadores com ponto fixo, ou seja, aqui os operandos são tratados como números inteiros e as operações podem ser realizadas normalmente, com alocação dos operandos nas redes de cálculo simplesmente. Estes circuitos podem ser utilizados tanto para processamentos següenciais como paralelos.

Tendo adquirido o conhecimento das formas de implementação dos operadores matemáticos em ponto fixo, utilizaremos oportunamente estas estruturas em operadores para ponto flutuante.

As operações em ponto flutuante exigem, no entanto, que outros conhecimentos sejam a estes incorporados em aspectos referentes ao seu formato, onde a representação numérica não se restringe a definir o número de forma extensa em sinal e magnitude mas prevê um campo para sinal, expoente e mantissa e com isso a expansão de valores representáveis.

Serão feitas, a seguir, a apresentação e as considerações referentes às particularidades que envolvem tal tipo de representação.

#### II.5.2.1-3 - Padrão IEEE e Aritmética em Ponto Flutuante

As resoluções de operações matemáticas, em ponto fixo, vistas acima podem ser realizadas, a princípio, com qualquer número de *bits* que desejarmos.

Devido a ampla escolha possível para o tamanho dos operandos e consequente obtenção de resultados muito extensos aliada a adequação da representação binária de operandos e por razões comerciais, foram padronizadas normas que permitiram uma maior homogenidade entre os diversos fabricantes de circuitos integrados.

Assim surgiu a IEEE/ANSI (Institute of Electrical and Electronic Engineers/American National Standards Institute) Standard 754 que normatiza projetos de CIs.

Para implementar operadores matemáticos em ponto flutuante segundo o padrão ANSI/IEEE 754, deve-se estabelecer inicialmente um dos formatos padronizados de representação dos valores numéricos[24]: formatos básicos ou estendido com precisão

simples ou dupla. Os mais utilizados são os básicos sendo os estendidos usados quando se tem em vista reduzir erros de arredondamento.

#### II.5.2.1-3.1 - Formatos Básicos

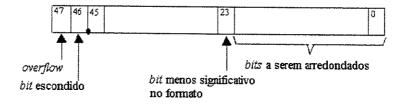

Os formatos básicos (Fig. 2.9) compreendem:

- Um bit de sinal (s)

- Expoente polarizado e = E + polarização

- Fração ou mantissa (f)

| Ĭ |   |          | _        |

|---|---|----------|----------|

| I | S | expoente | mantissa |

|   |   |          |          |

Fig. 2.9 - Formato para números em ponto flutuante

O formato básico de precisão simples adota a representação dos operandos com 32 bits, distribuidos em três campos: 1 bit para o sinal (s), 8 bits para a parte exponencial (e) e 23 bits para a mantissa ou parte fracionária (f).

O formato básico de precisão dupla apresenta a seguinte distribuição: 1 *bit* de sinal, 11 *bits* para o expoente e 52 *bits* para a mantissa, totalizando 64 *bits*.

Vamos apresentar mais detalhadamente as características do formato básico de precisão simples, porque este foi o adotado neste trabalho.

É importante esclarecer que o desenvolvimento do projeto em si, não está atrelado somente a esta representação podendo ser utilizado, tomadas as devidas proporções, formatos maiores para os operadores.

O campo de sinal s estabelece que se o *bit* é zero o número é positivo, caso contrário, negativo. Este é considerado o *bit* de maior importância desta representação, daí sua posição ser a de *bit* mais significativo.

No formato de precisão simples o campo de representação binária de expoente é de 8 bits, o que possibilita a representação de 28 - 1 = 255 números.

A precisão simples, pode ser descrita por uma representação, onde os 32 *bits*, podem ser assim visualizados:

$(-1)^s$   $(1.f_1f_2 ... f_{23})$  2 (e-127), onde **f** simboliza a mantissa ou parte fracionária, como também pode ser denominada, e **e** representa o expoente.