# Universidade Estadual de Campinas

Faculdade de Engenharia Elétrica e Computação Departamento de Eletrônica e Microeletrônica

## "PROJETO DE UM CIRCUITO INTEGRADO DIVISOR DE FREQUÊNCIAS / CONTADOR DE DÉCADA EM TECNOLOGIA GaAs – FAMÍLIA DCFL – PARA OPERAÇÃO COM CLOCK NA FAIXA DE 1 GHz"

Daniel Cardoso de Souza

Orientador Prof. Dr. Luiz Carlos Kretly

Dissertação apresentada à Faculdade de Engenharia Elétrica e Computação como parte dos pré-requisitos necessários para a obtenção do título de Mestre em Engenharia Elétrica.

Julho - 1998.

| UNIDADE IS                         |

|------------------------------------|

| N.º CHAMADA:                       |

|                                    |

| V. Ex.                             |

| T. Med BC/35241                    |

| PROC. 395/98                       |

|                                    |

| PRECO 78 \$ 11,00<br>DATA 01,10,98 |

| N. CPO                             |

| 1                                  |

CM-00117192-3

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

Souza, Daniel Cardoso de

So89p Projeto de um circuito integrado divisor de frequências / contador de década em tecnologia GaAs – família DCFL – para operação com clock na faixa de 1 GHz. / Daniel

Cardoso de Souza.--Campinas, SP: [s.n.], 1998.

Orientador: Luiz Carlos Kretly Dissertação (mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Circuitos eletrônicos – Projetos. 2. Circuitos integrados digitais. 3. Arsenieto de gálio. 4. Circuitos integrados de altíssima velocidade. I. Kretly, Luiz Carlos. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

### AGRADECIMENTOS.

A Deus;

A meus queridos pais e irmão, Edilson e Maria Guiomar Cardoso de Souza, e Ricardo Cardoso de Souza;

A meu orientador, Prof. Luiz Carlos Kretly;

Aos professores que participaram da minha banca de defesa de Mestrado: Prof. Ioshiaki Dói, Prof. Luiz C. Barbosa e Prof. Edmundo S. Braga;

À CAPES, que concedeu a minha bolsa de Mestrado por meio do programa PICDT, e à FAPESP, que arcou com o custo de fabricação e encapsulamento do CI, por meio do seu programa de PMU.

Quero agradecer às seguintes pessoas que, direta ou indiretamente, colaboraram para o término deste trabalho: Ademilde Félix, Alexander G. Ghilardi, André M. Teixeira, Antônio H. de Sousa, Antônio Ricardo Z. Nascimento, Emílio C. Bortolucci, Evandro M. Martins, Fernando F. de Melo, Hayram Nicácio, Ivo Carvalho S. Jr., Jacobus W. Swart, Marcos A. V. da Silva, Paulo H. Machado, Walter José M. de M. Jr., Walter M. S. de Marco, Wilmar B. de Moraes e Zelinda da Providência D. Cardoso.

### RESUMO.

A crescente ênfase sobre a operação portátil de computadores e sistemas de telecomunicação prioriza circuitos de baixa potência, ainda que de alta velocidade. As opções tecnológicas existentes para aplicações digitais na faixa de 100 MHz até 1 GHz são as famílias ECL em silício, DCFL em arseneto de gálio (GaAs), bem como ASICs CMOS realizados em processos avançados de Si, e somente as duas últimas podem proporcionar baixos consumos de potência. Em GaAs, DCFL é a principal opção de família digital de baixa potência.

Neste trabalho, descreve-se o projeto *full-custom* de um CI divisor de frequências de módulo variável e contador de década, realizado na família DCFL de GaAs. A topologia deste CI é inteiramente baseada na arquitetura clássica do TTL 7490, que foi escolhida por causa de sua versatilidade, e toda a sua funcionalidade lógica é mantida: o CI proposto pode operar tanto como um contador BCD quanto como um divisor de frequências por N, com N na faixa de 2 até 10. A razão da divisão, N, pode ser configurada unicamente através de conexões diretas entre pinos do CI. Por isso, o CI projetado neste trabalho será referido como o 7490-like. Suas aplicações são em síntese/divisão de frequências, contagem, instrumentação de alta frequência e na composição de circuitos digitais de alta velocidade, podendo-se usá-lo na entrada de outros blocos.

Todas as configurações de operação do circuito foram simuladas no *software* HSPICE, e os resultados mostram a operação do contador com taxas de *clock* de até 1 GHz, para capacitâncias de carga totais de 5 pF nas suas saídas e uma tensão de alimentação de 2V. O CI 7490-like foi implementado na tecnologia de MESFETs **HGaAs-III**, com comprimento de porta de 0,6 μm, pela *foundry* norte-americana Vitesse, por intermédio do Projeto Multi-Usuário brasileiro (PMU/FAPESP) em cooperação com o CMP francês. A área total do chip foi de 2,616 x 2,805 mm². Entretanto, os protótipos do CI demoraram para ser entregues à Unicamp, e não foi possível testá-los dentro do prazo de conclusão desta Dissertação.

Este projeto foi concebido principalmente para fins educacionais, mas tem um conteúdo inovativo a nível internacional, tendo em vista que não há publicação na literatura técnica internacional, até onde foi possível pesquisar, de um CI com arquitetura clássica como a do 7490, mas operando próximo a 1GHz e com tecnologia de GaAs, mantendo sua equivalência funcional. Esta Dissertação pretende ser um guia para futuros projetistas de CIs, apresentando um roteiro bastante didático das etapas de um trabalho de projeto. O CI escolhido para esse fim foi um MSI com um nível de complexidade intermediário, não sendo nem muito simples nem complexo demais, mas adequado a um primeiro projeto. Outra contribuição é a formação de recursos humanos em projeto de CIs.

Este trabalho já foi parcialmente publicado na XII Conferência da Sociedade Brasileira de Microeletrônica, realizada em 1997, com o título "Design of a 7490-like Decade Counter Integrated Circuit, Using GaAs MESFET DCFL Family, for Frequencies Up to 1 GHz".

#### ABSTRACT.

The increasing emphasis on the portable operation of computers and communication systems has placed a priority on low-power, yet high-speed, circuits. The existing viable technologies for digital applications in the range from 100 MHz up to 1 GHz are Si ECL and GaAs DCFL families, as well as high-speed CMOS ASICs implemented in advanced Si processes, and only the last two options offer low power consumption. In GaAs technology, DCFL is the main choice for a low-power digital family.

In this work, a variable modulus frequency divider and decade counter IC was designed in the GaAs DCFL family. This work describes the full-custom design procedures for this IC, starting from its logic design, until the completion of the final layout version. This DCFL counter circuit topology is entirely based upon the classical TTL 7490 architecture, which was chosen because of its versatility, and all its functionality is retained: this IC can operate either as a decade (BCD) counter, or as a frequency divider by N, being N any integer in the range from 2 to 10. The frequency division modulus N can be set solely by means of **direct** connections between certain IC pins. Therefore, the IC designed in this work will be referred to as the 7490-like. This circuit's usual applications are: frequency synthesis or division, counting, high frequency instrumentation and as a block in the composition of high speed digital circuits; the IC can also be used before the input to other blocks.

All the circuit operating configurations were simulated in the HSPICE software, and results show counter operation with clock rates up to 1 GHz, with 5 pF total load capacitances in its outputs and the use of a 2V supply. The 7490-like IC was implemented in the HGaAs-III MESFET technology, featuring 0.6 µm gate lengths, by the north-american foundry Vitesse Semiconductor, specialized in GaAs ASICs manufacturing, via Brazilian multi-user-projects (PMU/FAPESP) cooperation with the French CMP. The total chip area was 2,616 x 2,805 mm². Unfortunately, the IC prototypes took too long to arrive at Unicamp, therefore it was not possible to test them in time to meet the deadline for the conclusion of this Dissertation.

This project was envisaged **mainly** for educational purposes, but it bears an innovative content at international level, given that there is no publication in the international technical literature (at least not as far as it was possible to investigate) of an IC with a classical architecture like that of the 7490, but operating close to 1 GHz in GaAs technology, keeping its functional equivalence. This Dissertation also aims to be a guide for future GaAs IC designers, presenting a very didactic outline of the steps of a design effort. To keep with this purpose, the chosen IC was an MSI with an intermediate complexity level, which is neither too simple nor too complex, being just well-suited for a first design.

This work has been published in part at the XII Conference of the Brazilian Microelectronics Society, under the title "Design of a 7490-like Decade Counter Integrated Circuit, Using GaAs MESFET DCFL Family, for Frequencies Up to 1 GHz".

# CONTEÚDO.

| Glossário de Siglas e Abreviações                                                                                                                                                                                                                                                                                                                                                                                                           |                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| Lista de Símbolos Deste Trabalho                                                                                                                                                                                                                                                                                                                                                                                                            | xi                                   |  |

| 1. Materiais, Dispositivos e Tecnologia de GaAs                                                                                                                                                                                                                                                                                                                                                                                             | 1                                    |  |

| 1.1. A Justificativa para o Projeto de CIs em GaAs                                                                                                                                                                                                                                                                                                                                                                                          | 1                                    |  |

| 1.2. Propriedades do GaAs e Comparação com o Si ao Nível de Materiais Semicondutores 1.2.1. Vantagens do GaAs em relação ao Si 1.2.2. Desvantagens do GaAs em relação ao Si                                                                                                                                                                                                                                                                 | 2<br>2<br>5                          |  |

| <ul> <li>1.3. Princípios dos Dispositivos Planares em GaAs e Processos de Fabricação</li> <li>1.3.1. Teoria da Operação do Diodo Schottky</li> <li>1.3.2. Teoria da Operação do MESFET</li> <li>1.3.2.1. Transcondutância e Frequência de Ganho Unitário</li> <li>1.3.2.2. Não-idealidades do MESFET</li> <li>1.3.3. Processos de Fabricação de MESFETs de GaAs</li> <li>1.3.3.1. Os Contatos Ôhmicos</li> <li>1.3.3.2. O MESFET</li> </ul> | 6<br>8<br>11<br>11<br>14<br>14<br>15 |  |

| <ul> <li>1.4. Aplicações de CIs de GaAs</li> <li>1.4.1. Aplicações de Circuitos Digitais Rápidos em GaAs</li> <li>1.4.2. Aplicações de Circuitos Analógicos de Alta Frequência em GaAs</li> </ul>                                                                                                                                                                                                                                           | 16<br>16<br>17                       |  |

| 1.5. Os Problemas do Uso do GaAs na Implementação de CIs                                                                                                                                                                                                                                                                                                                                                                                    | 17                                   |  |

| 1.6. Justificativa e Objetivos Deste Trabalho                                                                                                                                                                                                                                                                                                                                                                                               | 19                                   |  |

| 1.7. Roteiro do Texto                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                   |  |

| 2. CIs Digitais de Alta Velocidade em GaAs.                                                                                                                                                                                                                                                                                                                                                                                                 | 22                                   |  |

| 2.1. Histórico do Desenvolvimento da Tecnologia de CIs Digitais de MESFETs de GaAs.                                                                                                                                                                                                                                                                                                                                                         | 22                                   |  |

| 2.2. Estado-da-arte dos CIs Digitais de GaAs.                                                                                                                                                                                                                                                                                                                                                                                               | 24                                   |  |

| 2.3. Características das Famílias Lógicas E/D em GaAs. 2.3.1. Família Lógica DCFL ( <i>Direct-Coupled FET Logic</i> ). 2.3.2. Família Lógica SCFL ( <i>Source-Coupled FET Logic</i> ).                                                                                                                                                                                                                                                      | 26<br>26<br>30                       |  |

| 2.3.3. Comparação Entre as Famílias Lógicas DCFL e SCFL.                                                  | 32       |

|-----------------------------------------------------------------------------------------------------------|----------|

| 2.4. Conclusão.                                                                                           | 32       |

| 2.4. Conclusão.                                                                                           |          |

|                                                                                                           |          |

| 3. Projeto de Portas Lógicas Básicas em DCFL.                                                             | 34       |

| 3.1. Conceitos de Projeto de CIs Digitais em GaAs, com Ênfase em DCFL.                                    | 34       |

| 3.1.1. Margens de Ruído (NMs).                                                                            | 34       |

| 3.1.2. Dissipação de Potência.                                                                            | 37<br>38 |

| 3.1.3. Tempos de Transição e Atrasos de Propagação.                                                       | 30       |

| 3.1.4. Modelos de Dispositivos para a Simulação de CIs de GaAs no Processo                                | 40       |

| da Vitesse.                                                                                               | 40       |

| 2.0. Duista de Inversores DCFI                                                                            | 43       |

| 3.2. Projeto de Inversores DCFL. 3.2.1. Filosofia de Projeto.                                             | 49       |

| 3.2.2. Parâmetros Fixos do Projeto.                                                                       | 49       |

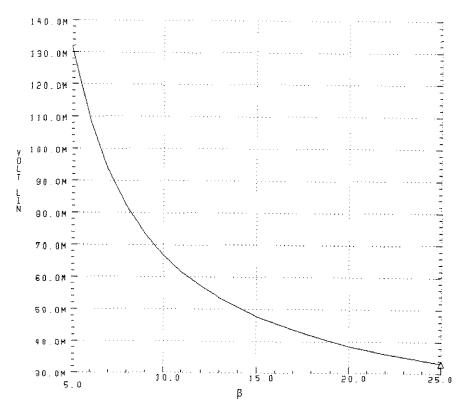

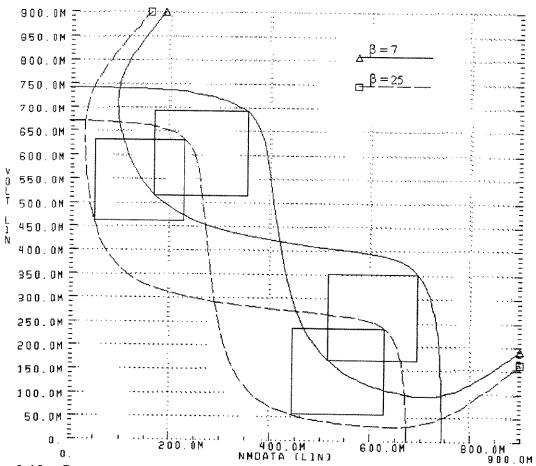

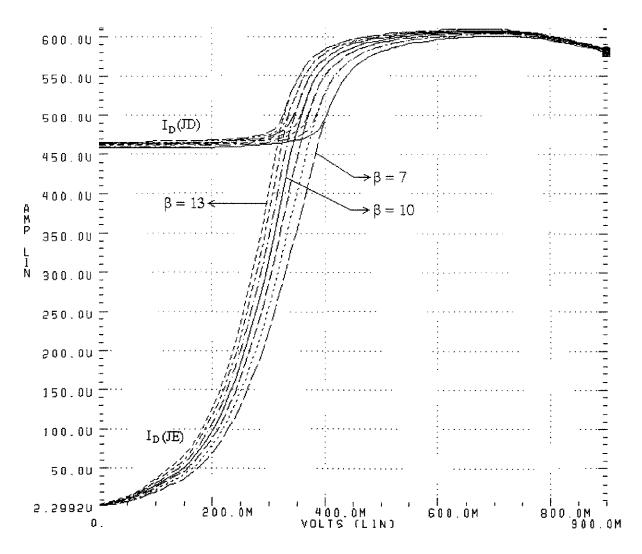

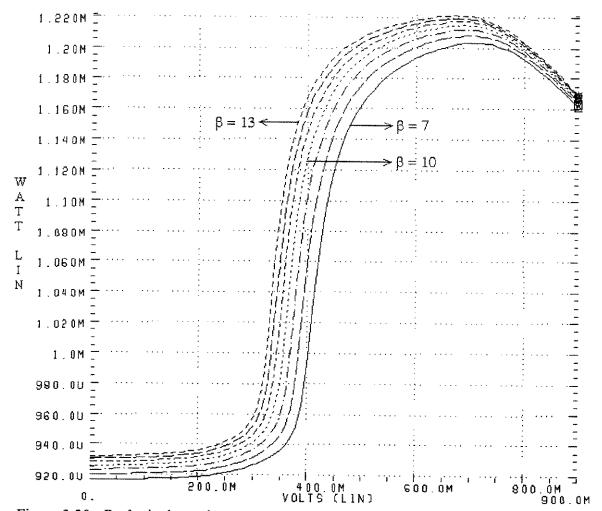

| 3.2.3. A Influência do Parâmetro β no Projeto de um Inversor.                                             | 51       |

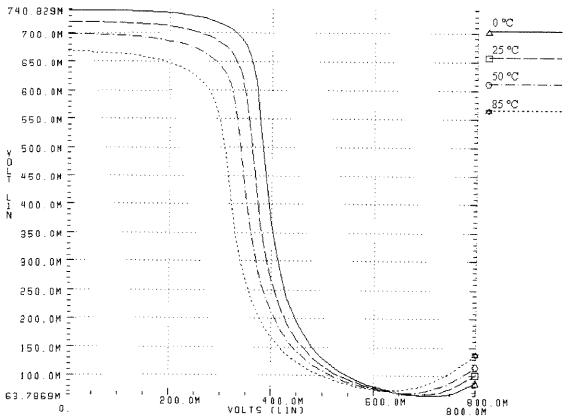

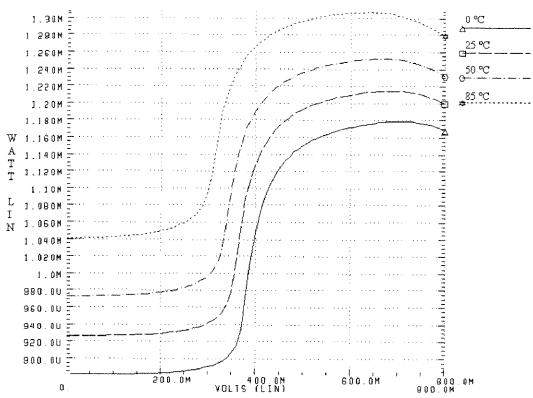

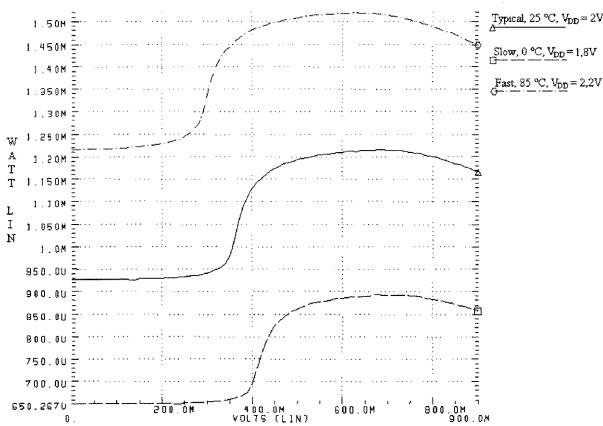

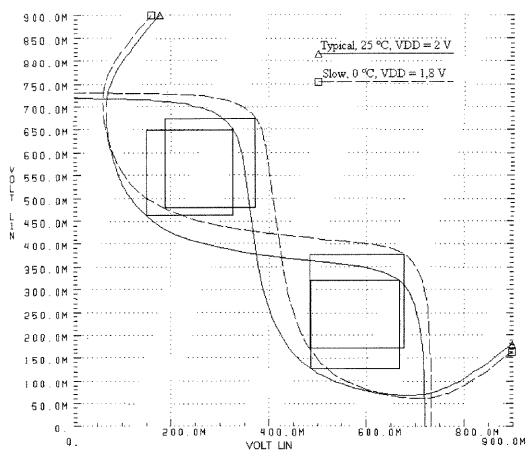

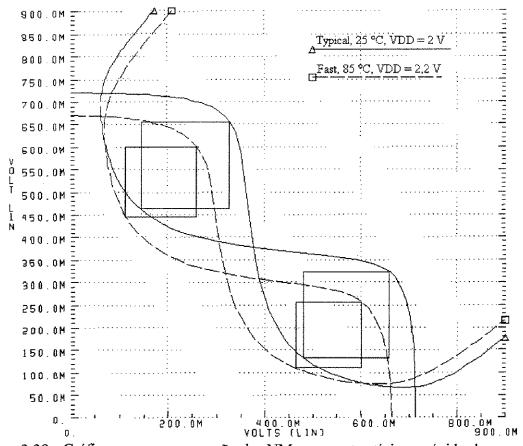

| 3.2.3.1. Simulações DC.                                                                                   | 51       |

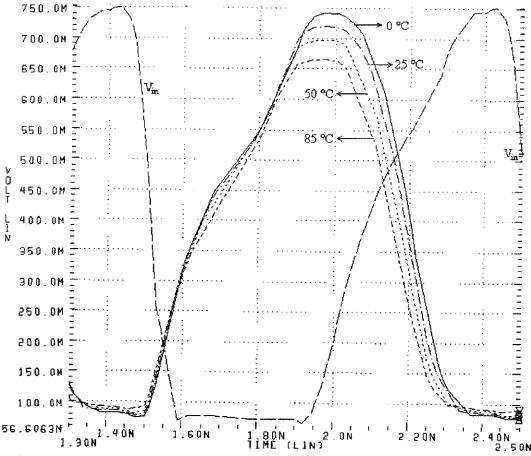

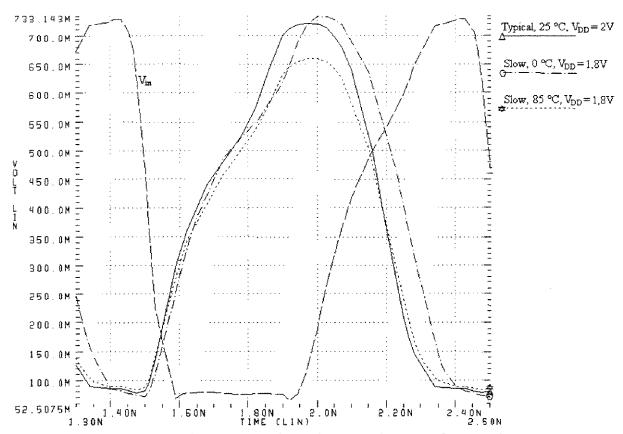

| 3.2.3.2. Simulações Transientes.                                                                          | 56       |

| 3.2.4 A Influência de W <sub>D</sub> .                                                                    | 62       |

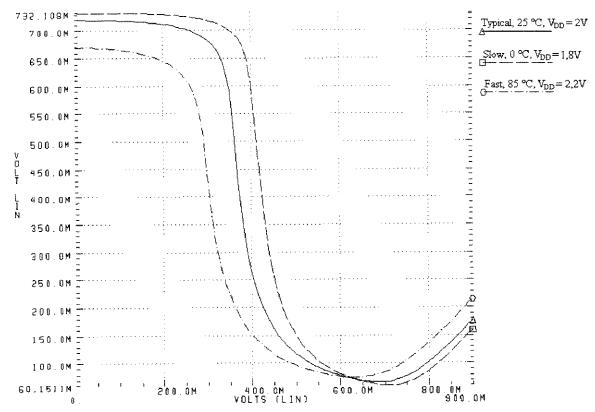

| 3.2.5. Variações da Temperatura, Processo, Fonte de Alimentação e Fan-Out.                                | 66       |

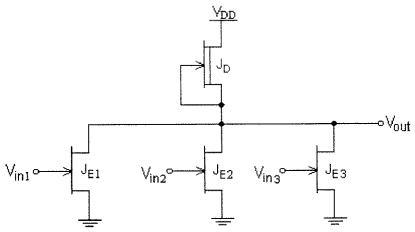

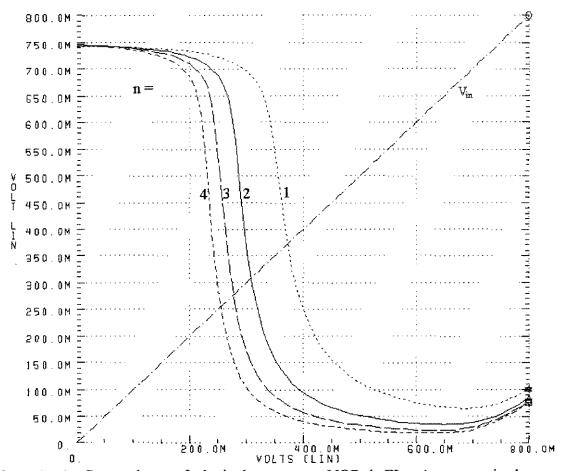

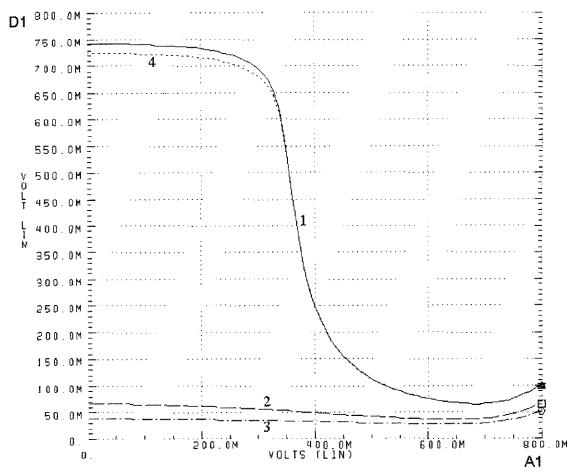

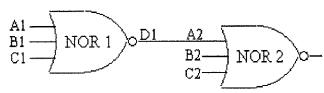

| 3.3. Projeto de Portas NOR DCFL.                                                                          | 74       |

| Duitana SDCEL a Ruffare de Entrada                                                                        | 80       |

| 3.4. Projeto de <i>Drivers</i> SDCFL e <i>Buffers</i> de Entrada. 3.4.1. Projeto de Portas Lógicas SDCFL. | 80       |

| 3.4.2. Projeto dos <i>Buffers</i> de Entrada.                                                             | 91       |

| 5.4.2. 1 Togeto dos 2 19,9 or 11 or 11                                                                    |          |

| 4. Projeto do CI Contador e Divisor de Frequências 7490-like.                                             | 94       |

| 4.1. Contador de Década TTL 7490.                                                                         | 94       |

| 4.2. Projeto Lógico do Circuito Integrado 7490-like.                                                      | 98       |

| The Incident of Circuits Integrade 7400 like                                                              | 101      |

| 4.3. Projeto Elétrico do Circuito Integrado 7490-like.                                                    | 101      |

| 4.3.1. Especificações. 4.3.2. Projeto do FF J'K' para Atender às Especificações do 7490-like.             | 104      |

| 4.3.2. Projeto do FF J R para Atender as Especimenços do 11.4.3.3. Descrição do 7490-like no Simulador.   | 109      |

| 4.5.5. Descrição do 7770 mile no simulator.                                                               |          |

| 4.4. Conclusão.                                                                                           | 115      |

| 5. Layout do CI 7490-like.                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| 5.1. Informações Gerais para o Layout de CIs.                                                                                                                                                                                                                                                                                                                                                                                                                     | 116                                                  |  |

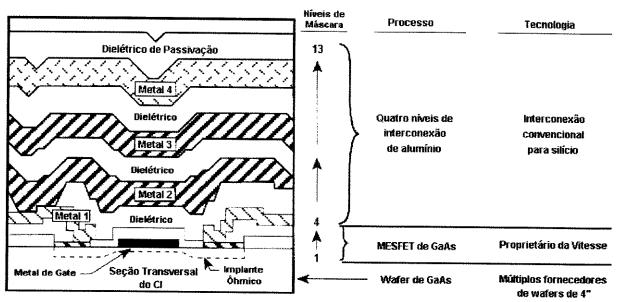

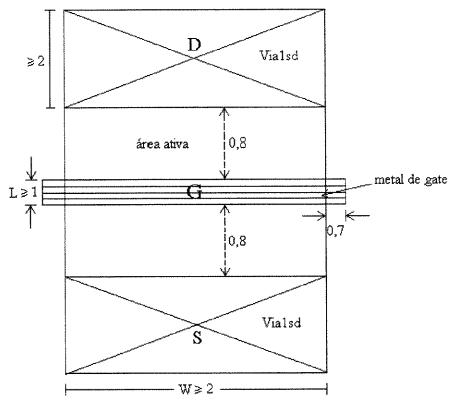

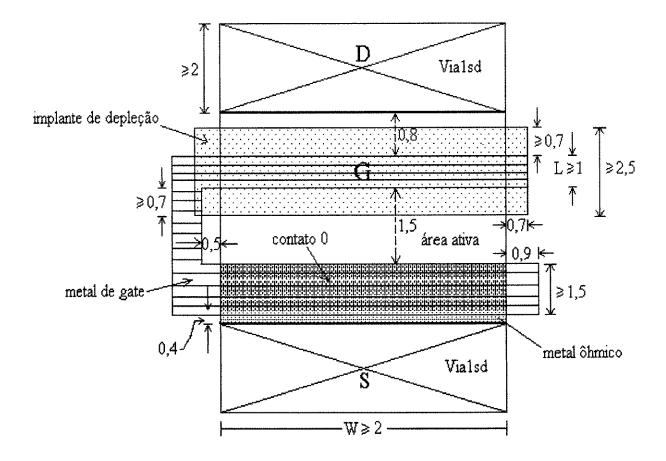

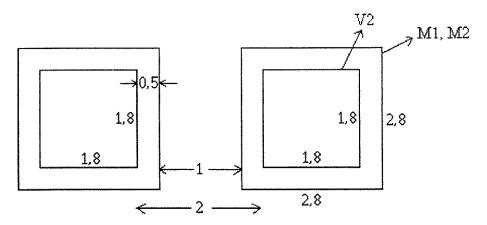

| 5.2. As Camadas do Processo da Vitesse e suas Características.                                                                                                                                                                                                                                                                                                                                                                                                    | 117                                                  |  |

| 5.3. Problemas de <i>Layout</i> de CIs. 5.3.1. <i>Layout</i> de CIs Digitais de Alta Velocidade                                                                                                                                                                                                                                                                                                                                                                   | 123<br>126                                           |  |

| <ul> <li>5.4. Desenho do Layout do CI 7490-like no Software Magic.</li> <li>5.4.1. A Configuração do Arquivo de Tecnologia para o Magic.</li> <li>5.4.2. As Etapas para o Desenho do Layout.</li> <li>5.4.2.1. Layout dos Flip-Flops.</li> <li>5.4.2.2. Projeto do Resistor de Terminação de Entrada.</li> <li>5.4.2.3. Projeto da Distribuição da Alimentação e dos Pads.</li> <li>5.4.2.4. LVS.</li> <li>5.4.3. Extração do Circuito e de Parasitas.</li> </ul> | 129<br>129<br>130<br>131<br>135<br>136<br>138<br>142 |  |

| 5.5. Encapsulamento e Diagrama de Pinagem.                                                                                                                                                                                                                                                                                                                                                                                                                        | 144                                                  |  |

| 5.6. Recomendações para o Teste do CI.                                                                                                                                                                                                                                                                                                                                                                                                                            | 145                                                  |  |

| 6. Conclusões e Sugestões para Futuros Trabalhos.                                                                                                                                                                                                                                                                                                                                                                                                                 | 149                                                  |  |

| Apêndice 1.  Roteiro para a Inclusão de Gráficos de Simulações do HSPICE em um Documento do Word for Windows 7.0.  Arquivos Netlist de Entrada para Simulação no HSPICE.                                                                                                                                                                                                                                                                                          | 152<br>153                                           |  |

| Apêndice 2.  Arquivo de Tecnologia "cmp.tech26" Fornecido pelo CMP para o Software Magic, Processo HGaAs-III da Vitesse.                                                                                                                                                                                                                                                                                                                                          | 220                                                  |  |

| Apêndice 3. Simulações das Configurações de Divisão de Frequência do CI 7490-like.                                                                                                                                                                                                                                                                                                                                                                                | 233                                                  |  |

| Apêndice 4.<br>Células de Portas Lógicas Usadas no <i>Chip 7490-like</i> .                                                                                                                                                                                                                                                                                                                                                                                        | 239                                                  |  |

| Apêndice 5. O Novo Processo HGaAs-IV.                                                                                                                                                                                                                                                                                                                                                                                                                             | 261                                                  |  |

| Referências Bibliográficas.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 264                                                  |  |

# GLOSSÁRIO DE SIGLAS E ABREVIAÇÕES.

AMS: Austria Mikro-Systemè (Micro-Sistemas da Austria).

ASIC: Application-Specific Integrated Circuit (Circuito Integrado de Aplicação Específica).

BCD: Binary-Coded Decimal (Decimal Codificado em Binário).

BDCFL: Buffered DCFL (DCFL "Bufferizada"). O mesmo que SDCFL.

BFL: Buffered FET Logic (Lógica FET com Buffer).

BiCMOS: Bipolar-CMOS.

BJT: Bipolar Junction Transistor (Transistor Bipolar de Junção).

CAD: Computer-Aided Design (Projeto Auxiliado por Computador).

CCS: Centro de Componentes Semicondutores.

CDFL: Capacitor-Diode FET Logic (Lógica FET de Capacitor e Diodo).

CI: Circuito Integrado.

CIF: Caltech Interchange Format (Formato para Intercâmbio do Caltech).

CML: Current-Mode Logic (Lógica em Modo de Corrente).

CMOS: Complementary MOS (MOS Complementar).

CMP: Circuits Multi-Projets (Circuitos Multi-Projetos).

DBS: Direct Broadcast Satellite (Satélite de Radiodifusão Direta).

DCFL: Direct-Coupled FET Logic (Lógica FET de Acoplamento Direto).

DCTL: Direct-Coupled Transistor Logic (Lógica de Transistores de Acoplamento Direto).

DFET: Depletion FET (FET de Depleção).

D.P: Delay x Power product (produto atraso x potência).

ECL: Emitter-Coupled Logic (Lógica com Acoplamento de Emissor).

EDA: Electronic Design Automation (Automação de Projeto Eletrônico).

EFET: Enhancement FET (FET de Enriquecimento).

ES2: European Silicon Structures (Estruturas de Silicio da Europa).

FET: Field-Effect Transistor (Transistor de Efeito de Campo).

FF: Flip-Flop.

FL: FET Logic (Lógica de FET).

GPS: Global Positioning System (Sistema de Posicionamento Global).

GSI: Graphical Simulation Interface (Interface de Simulação Gráfica).

HBT: Heterojunction Bipolar Transistor (Transistor Bipolar de Heterojunção).

HEMT: High Electron Mobility Transistor (Transistor de Alta Mobilidade Eletrônica).

IGFET: Insulated-Gate FET (FET de Porta Isolada).

I/O: Input/Output (Entrada/Saída).

JFET: Junction FET (Transistor de Efeito de Campo de Junção).

LBFL: Low-power BFL (BFL de Baixa Potência).

LDCC: LeaDed Ceramic chip Carrier (Porta-chip Cerâmico com Pinos).

LED: Light-Emitting Diode (Diodo Emissor de Luz).

LSCFL: Low-power SCFL (SCFL de Baixa Potência).

LSI: Large-Scale Integration (Integração em Alta Escala).

MCM: Multi-Chip Module (Módulo Multi-Chips).

MES: MEtal-Semiconductor (Metal-Semicondutor).

MESFET: MEtal-Semiconductor FET (Transistor de Efeito de Campo de Junção Metal-Semicondutor).

MMIC: Monolithic Microwave Integrated Circuit (Circuito Integrado Monolitico de Microondas).

MOS: Metal-Oxide-Semiconductor (Metal-Óxido-Semicondutor).

MS: Master-Slave (Mestre-Escravo).

MSI: Medium-Scale Integration (Integração em Média Escala).

NMOS: N-channel MOS (MOS de Canal N).

PCS: Personal Communications Services (Serviços de Comunicação Pessoal).

PLD: Programmable Logic Device (Dispositivo Lógico Programável).

PLL: Phase-Locked Loop (Malha de Fase Travada).

PML: Philips Microwave Limeil.

PMU: Projeto Multi-Usuário.

RAM: Random-Access Memory (Memória de Acesso Aleatório).

RISC: Reduced Instruction Set Computer (Computador com Conjunto de Instruções Reduzido).

SBD: Schottky-Barrier Diode (Diodo de Barreira Schottky).

SCFL: Source-Coupled FET Logic (Lógica FET com Acoplamento pela Fonte).

SDCFL: Source-follower DCFL (DCFL com Seguidor de fonte). O mesmo que BDCFL.

SDFL: Schottky Diode-FET Logic (Lógica FET com Diodo Schottky).

SDH: Synchronous Digital Hierarchy (Hierarquia Digital Síncrona).

SI: Semi-Insulating (Semi-Isolante).

SOI: Silicon On Insulator (Silicio Sobre Isolante).

SONET: Synchronous Optical NETwork (Rede Óptica Síncrona).

SPEC: Systems and Processes Engineering Corporation (Corporação de Sistemas e Processos de Engenharia).

SPICE: Simulation Program with Integrated Circuit Emphasis (Programa de Simulação com Ênfase em Circuitos Integrados).

SSI: Small-Scale Integration (Integração em Pequena Escala).

TTL: Transistor-Transistor Logic (Lógica Transistor-Transistor).

UHF: Ultra High Frequency (Frequência Ultra Alta).

VHSIC: Very High Speed Integrated Circuit (Circuito Integrado de Velocidade Muito Alta).

VLSI: Very Large-Scale Integration (Integração em Escala Muito Alta).

### LISTA DE SÍMBOLOS DESTE TRABALHO.

$a = prefixo atto (10^{-18}).$

A = área da seção transversal de um diodo; área de porta de um MESFET; área da seção transversal de uma linha de interconexão.

$A_v = ganho de tensão$ .

b = altura da área ativa implantada, em um MESFET ou SBD.

$\beta$  = razão entre as razões  $W_g/L_{g,proj}$  dos EFETs e DFETs, na lógica DCFL.

$\beta_0$  = parâmetro de transcondutância de um MESFET.

c = velocidade da luz no vácuo (3.10<sup>8</sup> m/s).

C<sub>D</sub> = capacitância de depleção de uma junção MES ou pn.

C<sub>FO</sub> = capacitância devida ao fan-out na saída de uma porta.

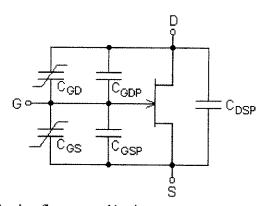

$C_{GS}$ ,  $C_{GD}$  = capacitâncias de depleção (não-lineares) das junções de porta-fonte e porta-dreno de um FET.

$C_{GSP}$ ,  $C_{GDP}$ ,  $C_{DSP}$  = capacitâncias parasitas entre os terminais de porta e fonte, porta e dreno e dreno e fonte, respectivamente.

C<sub>in</sub> = capacitância de entrada de uma porta lógica.

C<sub>j0</sub> = capacitância de depleção de uma junção não-polarizada.

C<sub>L</sub> = capacitância de carga na saída de uma porta ou circuito lógicos.

Cwire = capacitância parasita total de uma linha de interconexão.

E = campo elétrico no canal de um FET.

$E_c$  = valor do campo elétrico crítico para a máxima velocidade dos elétrons.

$\varepsilon_r = \text{constante dielétrica}$ .

f = prefixo femto (10<sup>-15</sup>); frequência de operação de um circuito.

FI: fan-in.

FO: fan-out.

$f_t$  = frequência de ganho de corrente unitário de um FET.

$g_{ds}$  = condutância entre dreno e fonte de um FET.

$g_m$  = transcondutância de um FET.

g<sub>m,e</sub> = transcondutância extrínseca de um FET.

g<sub>m,i</sub> = transcondutância intrínseca de um FET.

I = corrente genérica.

$I_D$  = corrente direta de um diodo; corrente de dreno de um FET.

$I_{D,D}$  = corrente de dreno de um DFET.

$I_{\text{D.E}} = \text{corrente} \text{ de dreno de um EFET}.$

$I_{D,sat}$  = corrente de saturação de um FET.

I<sub>GS</sub> = corrente da junção de porta-fonte de um MESFET.

I<sub>maxP2</sub> = corrente máxima em um pad que seja ligado ao circuito por "metal 2".

$I_{maxP3}$  = corrente máxima em um pad que seja ligado ao circuito por "metal 3".

I<sub>maxP4</sub> = corrente máxima em um pad que seja ligado ao circuito por "metal 4".

$I_S$  = corrente de saturação do diodo, tipicamente na faixa de  $10^{-15}$  a  $10^{-14}$  A.

$I_{SUB}$  = corrente de sub-limiar do MESFET.

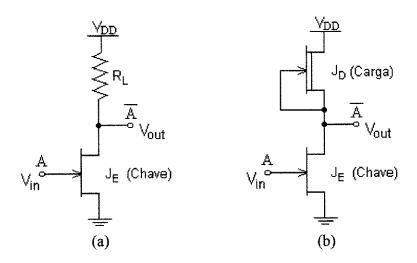

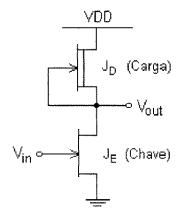

$J_D$  = designação de um DFET em circuitos, e para simulação no HSPICE.

$J_E$  = designação de um EFET em circuitos, e para simulação no HSPICE.

$J_s$  = densidade de corrente na seção transversal de um diodo.

$k = constante de Boltzmann (1,381x10^{-23} J/K)$ ; fator de escalonamento linear de um circuito.

L = comprimento de uma interconexão do circuito; o comprimento de um resistor (da área ativa); a indutância de uma interconexão do circuito.

$\lambda$  = parâmetro de modulação do comprimento do canal.

$L_D$  = comprimento de porta de um DFET (valor de projeto).

$L_E$  = comprimento de porta de um EFET (valor de projeto).

$L_2$  = valor real do comprimento de porta de um FET; o comprimento de um diodo.

L<sub>g,proj</sub> = valor de projeto do comprimento de porta de um FET; valor de projeto do comprimento de um diodo.

m = coeficiente de dopagem.

$\mu_n$  = mobilidade de elétrons livres.

$\mu_p$  = mobilidade de lacunas.

N = razão da divisão de frequências do CI 7490-like, podendo estar na faixa de 2 até 10.

n = coeficiente de emissão ou fator de idealidade do diodo ( $\cong 1$ ); ou o número de entradas que chaveiam simultaneamente em uma porta NOR.

N<sub>D</sub> = concentração de impurezas doadoras (dopantes).

NM = margem de ruído.

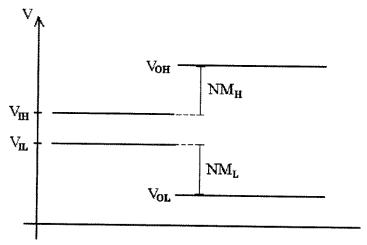

$NM_H$  = margem de ruído alta ( $NM_H$  =  $V_{OH} - V_{IH}$ ), conforme a figura 3.1.

$NM_L$  = margem de ruído baixa ( $NM_L = V_{IL} - V_{OL}$ ), conforme a figura 3.1.

P<sub>D. dyn</sub> = dissipação de potência dinâmica.

P<sub>D, st</sub> = dissipação de potência estática.

pw = largura do ciclo positivo de um sinal (pulse width).

$q = carga do elétron (1,6.10^{-19} C).$

R = resistência de um resistor do *chip*.

R<sub>D</sub> = resistência parasita série de dreno de um FET.

r<sub>ds</sub> = resistência de pequenos sinais entre dreno e fonte de um FET.

R<sub>L</sub> = resistência de carga na saída de um circuito, para simulação.

R<sub>out</sub> = resistência de saída de uma porta lógica ou driver.

R<sub>s</sub> = resistência de folha de uma camada de inteconexão.

R<sub>S</sub> = resistência parasita série de fonte de um FET; resistência série de um SBD.

R<sub>wire</sub> = resistência série de uma trilha de interconexão.

t = espessura de uma linha de interconexão.

T = temperatura absoluta.

$\tau$  = período de um sinal.

$\Delta t = o$  intervalo de tempo de carga ou descarga de um capacitor.

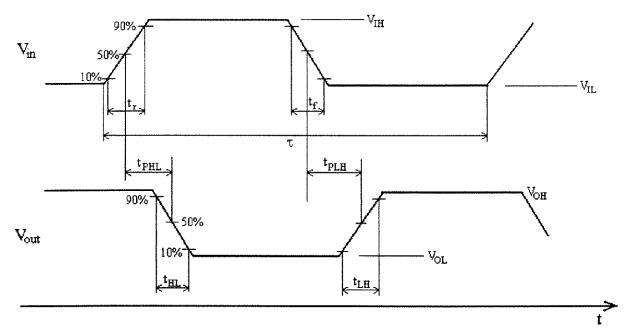

$t_{HL}$  = tempo de transição de um sinal do nível alto para o baixo. Ver figura 3.4.

$t_{LH}$  = tempo de transição de um sinal do nível baixo para o alto. Ver figura 3.4.

$t_{PD}$  = atraso de propagação de um sinal em um circuito lógico, definido como a média entre  $t_{PHL}$  e  $t_{PLH}$ .

$t_{\mathrm{PD,LT}}$  = atraso de propagação de um sinal em uma linha de transmissão.

$t_{PHL}$  = atraso de propagação de um sinal, para a saída variando do nível alto para o baixo. Ver figura 3.4.

$t_{\rm PLH}$  = atraso de propagação de um sinal, para a saída variando do nível baixo para o alto. Ver figura 3.4.

$\mathbf{v}$  = velocidade de deriva de portadores de carga.

$v_{\text{sat}}$  = valor saturado da velocidade de deriva de portadores de carga.

V<sub>BG</sub> = tensão de backgate.

V<sub>bi</sub> = tensão da barreira de potencial de uma junção.

$V_D$  = tensão no terminal de dreno de um FET.

$V_{\mathrm{D.e}}$  = tensão aplicada sobre um diodo real.

$V_{\mathrm{D,i}}$  = tensão aplicada sobre um diodo ideal, ou tensão intrinseca sobre a junção do diodo.

$V_{DS}$  = tensão entre dreno e fonte de um FET.

$V_{DS,sat}$  = tensão entre dreno e fonte para o início da saturação de um FET.

$V_F$  = tensão direta aplicada sobre uma junção MES.

$V_G$  = tensão no terminal de porta de um FET.

$v_{gs}$  = tensão de pequeno sinal entre os terminais de porta e fonte de um FET.

$V_{GS}$  = tensão DC entre os terminais de porta e fonte de um FET.

$V_{GS,e}$  = tensão DC extrínseca entre os terminais de porta e fonte de um FET.

$V_{GS,i}$  = tensão DC intrínseca entre os terminais de porta e fonte de um FET.

$V_{IH}$  = mínima tensão na entrada de um circuito lógico, que este ainda interpretará como um nível lógico alto "1".

$V_{IL}$  = máxima tensão na entrada de um circuito lógico, que este ainda interpretará como um nível lógico baixo "0".

V<sub>in</sub> = tensão de entrada em um circuito qualquer.

V<sub>MS</sub> = margem de ruído segundo o "método do máximo quadrado".

$V_{MS,H}$  = margem de ruído alta segundo o "método do máximo quadrado".

V<sub>MS,L</sub> = margem de ruído baixa segundo o "método do máximo quadrado".

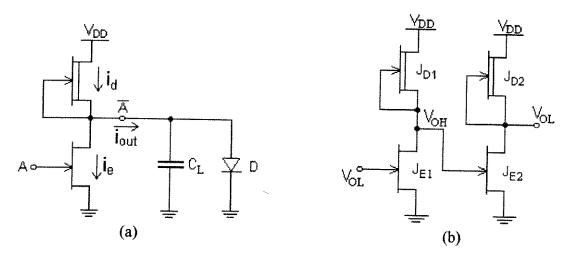

$V_{OH}$  = tensão típica de nível lógico alto na saída de um circuito lógico.

V<sub>OL</sub> = tensão típica de nível lógico baixo na saída de um circuito lógico.

Vout = tensão de saída de um circuito qualquer.

v<sub>p</sub> = velocidade de propagação de um sinal em uma linha de transmissão.

$V_{pp}$  = excursão pico-a-pico de uma tensão.

V<sub>R</sub> = tensão reversa aplicada sobre uma junção MES.

$V_T$  = tensão térmica, dada por kT/q e igual a 26 mV na temperatura ambiente.

$V_t$  = tensão de limiar de um FET.

V<sub>t,D</sub> = tensão de limiar de um FET de depleção.

V<sub>t,E</sub> = tensão de limiar de um FET de enriquecimento.

W = largura de uma interconexão do circuito; largura de um resistor (da área ativa).

$W_D$  = largura de porta de um DFET.

$W_E$  = largura de porta de um EFET.

W<sub>g</sub> = largura de porta de um FET; largura de um diodo.

x<sub>n</sub> = altura da região de depleção, abaixo da barreira Schottky de um MESFET ou SBD.

### CAPÍTULO 1.

## Materiais, Dispositivos e Tecnologia de GaAs.

#### 1.1. A Justificativa para o Projeto de CIs em GaAs.

A principal razão para o emprego de transistores de GaAs na implementação de circuitos é a velocidade de chaveamento muito alta desses dispositivos, no caso de circuitos digitais, ou a largura de banda muito alta, no caso de circuitos analógicos. Assim, as portas lógicas feitas com transistores de GaAs impõem muito menos atraso de propagação aos sinais, do que portas equivalentes feitas com transistores de silício, e assim os circuitos digitais de GaAs alcançam velocidades de operação muito mais altas, e com um consumo total de potência relativamente baixo. A grande motivação para o GaAs, portanto, é esta: alcançar-se o melhor desempenho possível com um CI. Existem ainda outras fortes razões para o emprego de dispositivos de GaAs, como por exemplo, para se obter circuitos tolerantes a radiação, circuitos para operação em temperaturas extremas, ou para se obter sistemas optoeletrônicos mais eficientes (isto será detalhado adiante).

Os atrasos de propagação mínimos para portas lógicas de GaAs são da ordem de dezenas de picosegundos, contra centenas de picosegundos para portas na tecnologia ECL F100K da National [1], que é a família digital comercial mais rápida em Si. Já no tocante ao consumo de potência, embora as portas lógicas de GaAs dissipem uma potência estática, ao contrário, por exemplo, das portas CMOS, elas consomem muito menos potência dinâmica [2], e dessa maneira, o produto atraso-potência (D.P), que é um índice de mérito comparativo, coloca algumas famílias lógicas de GaAs em vantagem de desempenho, se comparadas tanto com CMOS quanto com ECL. Alguns gráficos comparativos entre famílias de Si e GaAs são apresentados em [4], [5] e [6].

Atualmente, os CIs de GaAs já são um sucesso comercial, graças à acelerada expansão das telecomunicações nas faixas de UHF e microondas, motivada por um mercado de consumidores finais e de altíssima demanda, como é o caso da telefonia e computação móveis e da televisão via satélite. O futuro do emprego do GaAs na Eletrônica e Optoeletrônica é ainda mais promissor [7].

O processo de fabricação dos CIs de GaAs adapta um pouco da tecnologia dos CIs de Si, principalmente CMOS. Hoje, CIs VLSI de GaAs, com mais de um milhão de transistores, já se tornaram uma realidade, exibindo um desempenho que seria impossível, ou pelo menos difícil, de ser atingido com CIs equivalentes de Si. Portanto, a tecnologia de CIs VLSI de GaAs já tem sido empregada para realizar-se versões mais rápidas de outros CIs em Si. Em alguns casos, o ganho de velocidade oferecido pelos transistores de GaAs chega a reduzir ou eliminar a necessidade de um processamento paralelo de dados, resultando em um sistema de implementação lógica mais simples, compacta e de menor custo, porque usa menos transistores [2]. Em um futuro próximo, a mesma tecnologia será certamente usada para a construção de chips optoeletrônicos ou todo-ópticos, aproveitando a propriedade de bandgap direto do GaAs.

Os dois principais dispositivos eletrônicos construídos em tecnologia de GaAs são o diodo Schottky e o transistor MESFET. No campo dos dispositivos ópticos, LEDs, *lasers*, células solares e fotodetectores são as principais aplicações da tecnologia.

# 1.2. Propriedades do GaAs e Comparação com o Si ao Nível de Materiais Semicondutores.

A obtenção do arseneto de gálio, enquanto matéria-prima para a Microeletrônica, é bem mais complicada que a obtenção do silício, pois o GaAs é um cristal semicondutor composto (binário) que não existe na natureza.

O gálio é um elemento raro, tóxico, sendo obtido como um co-produto do refino de bauxita para a produção de alumínio, e também como um co-produto da obtenção de zinco. Processos padrão de purificação permitem obter-se gálio com altíssima pureza. O Ga é totalmente aplicado em processos de fabricação de semicondutores.

O arsênio é um co-produto (muito venenoso) da fusão de minérios de zinco e chumbo, podendo também ser obtido a partir de compostos sulfurosos como As<sub>2</sub>S<sub>4</sub> ou As<sub>2</sub>S<sub>3</sub>. A estrutura mais estável do arsênio é um metal cristalino. O As é produzido em quantidades cinco vezes maiores que o gálio, de onde resulta que é bem mais barato que este, porém é mais difícil de purificar do que o Ga. Somente 20% da produção total de arsênio são usados na indústria de semicondutores.

O Ga é um elemento químico da coluna IIIA da tabela periódica, e o As é um elemento da coluna VA; por isso, o GaAs é referido como um **composto III-V**. Além dele, existem vários outros semicondutores compostos de elementos das colunas III e V.

#### 1.2.1. Vantagens do GaAs em relação ao Si.

As vantagens do GaAs sobre o Si, para a fabricação de dispositivos de alta velocidade e componentes optoeletrônicos, têm sua causa básica nos diagramas de bandas de energia para os dois materiais.

GaAs é um semicondutor de bandgap direto, isto é, o mínimo energético da sua banda de condução e o máximo energético da sua banda de valência estão situados no mesmo momento. Essa propriedade é muito favorável para a construção de dispositivos emissores de luz de GaAs porque, em um material de bandgap direto, um elétron desce da banda de condução para a de valência sem a emissão de um fonon, a qual ocorreria se houvesse também uma mudança de momento. Ou seja, a recombinação é mais eficiente no GaAs [5]. Isto torna o seu uso muito interessante para a implementação de dispositivos ópticos, e facilita a integração destes com dispositivos eletrônicos, formando funções optoeletrônicas. O Si, por outro lado, é um semicondutor de bandgap indireto porque a menor separação energética entre sua banda de condução e sua banda de valência não ocorre no mesmo momento.

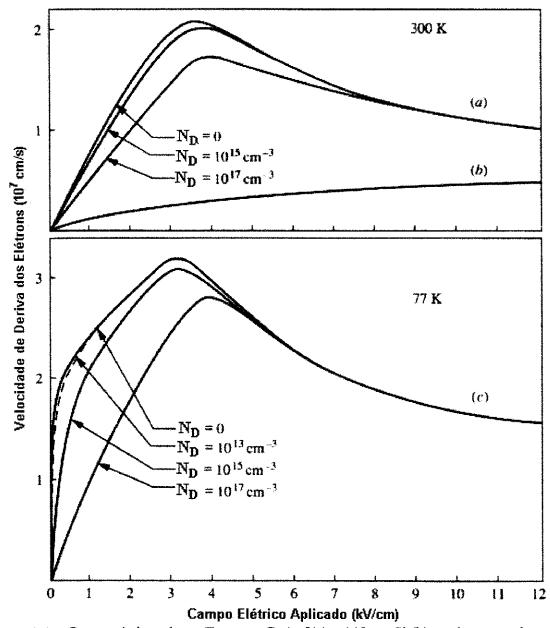

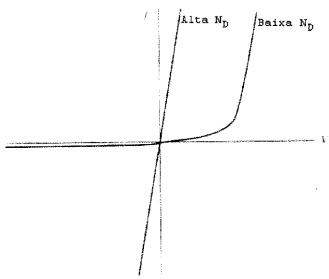

As estruturas das bandas de energia do Si e do GaAs levam às suas curvas de velocidade de deriva dos elétrons, v, em função do campo elétrico aplicado, E, mostradas na figura 1.1. Seja a mobilidade de um portador de carga definida como a derivada da sua

velocidade em relação ao campo elétrico que o acelera, e simbolizada por  $\mu_n$ , para os elétrons, e  $\mu_p$ , para as lacunas. Analisando-se a curva de  $\mathbf{v} \times \mathbf{E}$  do GaAs na figura 1.1(a), observa-se que seus elétrons livres têm uma  $\mu_n$  muito alta para pequenas intensidades de  $\mathbf{E}$  (cerca de seis a oito vezes maior do que no Si, na região de baixos campos  $\mathbf{E}$ ), o que significa uma alta velocidade dos elétrons para baixas tensões aplicadas (baixos campos elétricos no material).

Esta característica do GaAs é decorrente da estrutura de sua banda de condução, que apresenta um "vale" estreito, onde a massa efetiva dos elétrons é muito pequena. Os elétrons no Si têm massa efetiva bem maior do que no GaAs, daí eles terem uma  $\mu_n$  bem menor (sua v aumenta lentamente com a aplicação de E). Esta propriedade do GaAs leva a uma redução dos tempos de atraso de propagação de dispositivos, e é a principal responsável por torná-lo mais atrativo que o Si para para transistores de alta frequência, que também precisam operar com baixas tensões para economizar potência. Tempos de trânsito tão pequenos quanto 15 a 10 ps, correspondendo a frequências de ganho de corrente unitário,  $f_t$ , na faixa de 15 a 25 GHz, podem ser obtidos para MESFETs com portas de comprimentos  $L_g$  na faixa de 0,5 a 1  $\mu$ m, representando uma vantagem de três a cinco vezes sobre FETs de Si [5].

Em seguida, v atinge um pico em um valor relativamente baixo de campo elétrico (o campo crítico  $E_o$ , tipicamente de 3,5 kV/cm), e a partir daí começa a decair lentamente para maiores valores de E ( $\mu_n$  pequena e negativa). A v no GaAs satura para campos E mais intensos, e seu valor na saturação, embora seja só um pouco maior do que o do Si, já é atingido com um campo E quatro vezes menor do que neste material [5].

Na figura 1.1, à medida que  $N_D$  aumenta,  $\mu_n$  diminui, isto é, diminui v para um mesmo valor de E, por efeito de maior espalhamento nas impurezas presentes na rede cristalina. Observa-se na figura 1.1(c) que, em temperaturas próximas de 0 K, as  $\mu_n$ 's são muito maiores do que na temperatura ambiente (300 K). Curvas de  $\mu_n$  em função da temperatura, parametrizadas para vários valores de  $N_D$  e  $L_g$ , são apresentadas em [6].

Além da vantagem intrínseca do GaAs sobre o Si no tocante a  $\mu_n$ , a tecnologia de fabricação dos substratos de GaAs onde serão processados os circuitos também colabora para melhorar ainda mais a velocidade desses circuitos. O fato é que o GaAs intrínseco pode ser crescido com uma alta resistividade, da ordem de  $10^7$  a  $10^9$   $\Omega$ .cm, chamado de GaAs semi-isolante (SI). Um substrato SI de GaAs já proporciona, por si só, uma melhor e mais fácil isolação entre os dispositivos em um CI, impedindo o fluxo de cargas que poderia causar alguma interação em altas frequências entre os FETs, portanto simplificando o processo de fabricação e viabilizando maior densidade de integração. Outra grande vantagem do substrato SI de GaAs é que ele proporciona baixas capacitâncias parasitas dos dispositivos para o substrato, menores do que para dispositivos de Si de mesma área (contudo, as tecnologias SOI já viabilizam capacitâncias ao substrato igualmente baixas para transistores de Si). Enfim, um substrato SI de GaAs também permite a construção de indutores e capacitores de melhor qualidade, e aumenta a imunidade dos transistores à radiação ionizante.

O GaAs possui alta tolerância natural à radiação ionizante, maior do que a do Si. Componentes de GaAs podem ser empregados para a construção de circuitos eletrônicos para ambientes com altos níveis de radiação. Algumas aplicações que exigem esses componentes rad-hard são: espaciais (satélites), nucleares (usinas), militares (sistemas de guiamento de mísseis), e em equipamentos médicos e industriais. Nestes campos de aplicação, os componentes ficam sujeitos a colisões de íons de alta energia que, apesar de não destruírem os

dispositivos, causam uma alteração de estados lógicos e um erro na informação que estiver armazenada ou sendo transmitida [8].

Figura 1.1 – Características de v x E para o GaAs [(a) e (c)] e o Si (b), ambos com dopagem tipo n, tendo N<sub>D</sub> como parâmetro [11].

O maior valor do *bandgap* do GaAs permite que ele possa operar em uma faixa mais ampla de temperaturas do que o Si, indo de -200 a 200 °C [5]. Os elétrons no GaAs também apresentam menor potência de ruído do que no Si [9], viabilizando dispositivos de menor ruído em altas frequências.

Por causa de todas essas vantagens do GaAs, chegou-se a pensar que ele viria a substituir o Si para a construção de CIs. Mas o Si é superior em algumas características físicas, que são enumeradas na próxima seção, e os dispositivos de Si também foram se tornando mais rápidos e atingindo maiores frequências.

#### 1.2.2. Desvantagens do GaAs em relação ao Si.

A tecnologia do GaAs é mais cara e complexa do que a do Si. A primeira dificuldade é o maior custo das wafers SI de GaAs, pois o processo de obtenção do cristal é mais difícil. O Si é cerca de vinte vezes mais barato do que o GaAs [10], devido à abundância de matéria-prima de boa pureza (quartzo). O Si também é mais robusto, ou seja, menos quebradiço, e de fácil purificação para a forma monocristalina. O GaAs, por outro lado, requer muitos cuidados extras na fabricação e manipulação das wafers, e a sua tecnologia de fabricação é recente em comparação com a do Si, que já vem sendo aprimorada há muito mais tempo. Portanto, mesmo que algumas topologias em GaAs garantam uma vantagem técnica quando comparadas com o Si, o fator custo muitas vezes é decisivo para a escolha.

Não se conseguiu realizar ainda um óxido estável, não-reativo e compatível com o GaAs, o que permitiria a fabricação de MOSFETs de GaAs. Assim, nos FETs de GaAs viáveis na prática, o eletrodo de controle do canal tem que ser ou uma junção Schottky metal/semicondutor (MESFET), ou uma junção **pn** (JFET) e, em ambos os casos, a tensão de porta é limitada pela condução direta dessas junções. Para o Si, ao contrário, existe um óxido compatível, estável e de ótima qualidade, o SiO<sub>2</sub>, crescido sobre a superfície do Si para isolar o terminal de porta e o canal. Isso gera um MOSFET, que permite uma excursão muito maior da tensão de porta sem que a haja a condução desta, levando a maiores margens de ruído.

Outra desvantagem do GaAs, em comparação com o Si, surge quando se tenta fabricar dispositivos complementares de GaAs, como MESFETs de canal  $\bf p$ . A mobilidade das lacunas é menor do que a dos elétrons em ambos os materiais. O problema é que, no GaAs, a disparidade entre esses valores de mobilidade é muito grande:  $\mu_n = 5000~\text{cm}^2/(\text{V.s})$  contra  $\mu_p = 250~\text{cm}^2/(\text{V.s})$ . A  $\mu_p$  no GaAs é até mesmo um pouco menor do que no Si, para as mesmas concentrações de átomos aceitadores. Assim, FETs de GaAs de canal  $\bf p$  só iriam introduzir um grande atraso de propagação se fossem usados em portas lógicas, ou uma limitação de frequência de operação, se usados em aplicações analógicas. Como a principal razão para se usar dispositivos de GaAs é atingir velocidades e frequências cada vez maiores, os dispositivos de canal  $\bf p$  quase não são empregados na construção de circuitos.

O Si possui uma condutividade térmica cerca de três vezes maior que o GaAs [10], facilitando a dissipação de calor pelo *chip*, evitando a formação de "pontos quentes" e permitindo maiores níveis de integração.

As diversas vantagens físicas do Si o fazem ser a única escolha para a grande maioria das aplicações, que exigem baixo custo e produção em massa. A escala de integração em Si há muito tempo já excedeu a marca de um milhão de transistores por *chip*. Seu processo de fabricação nessas escalas já está bem caracterizado, e isso concorre para a redução de custo dos CIs fabricados e a sua maior confiabilidade, com um produto D.P razoável. Enquanto isso, a tecnologia de MESFETs de GaAs deve ser reservada para aplicações que requeiram o seu desempenho superior.

Uma tabela comparando as propriedades eletrônicas do GaAs e do Si, a nível de materiais semicondutores, é mostrada em [11]. Para uma discussão bastante aprofundada da física e das propriedades de transporte de dispositivos de GaAs, ver [6].

#### 1.3. Princípios dos Dispositivos Planares em GaAs e Processos de Fabricação.

#### 1.3.1. Teoria da Operação do Diodo Schottky.

A junção metal-semicondutor (MES), ou contato Schottky, exibe uma barreira de potencial eletrostático na interface entre os dois materiais, chamada de barreira Schottky. A junção MES serve como eletrodo de porta para a construção de um MESFET, ou pode ser usada simplesmente como um diodo Schottky; mas também é empregada para fazer-se os contatos dos terminais de fonte e dreno do MESFET com o seu canal. As diferenças de fabricação e funcionamento entre a junção MES destes contatos ôhmicos e a junção retificadora do diodo Schottky, serão esclarecidas na seção 1.3.3.1.

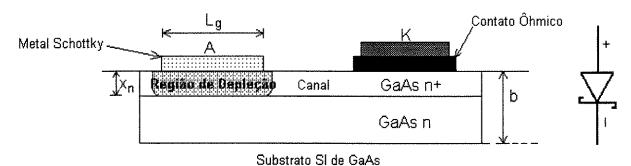

Os diodos Schottky para aplicações em CIs de GaAs são planares, isto é, ambos os contatos (Schottky e ôhmico) ficam na superfície de uma camada condutiva de GaAs tipo n, a qual é definida sobre um substrato semi-isolante de GaAs. A figura 1.2 mostra um desenho em corte do SBD e o seu símbolo esquemático. A largura do diodo, W<sub>g</sub>, que é definida como a largura do metal Schottky de ânodo, é medida perpendicularmente ao plano da página.

Figura 1.2 – Esquema em corte longitudinal do SBD e símbolo para circuitos.

Em toda a literatura sobre o assunto, é comum representar-se o SBD de GaAs pelo mesmo símbolo do diodo de junção **pn**, prática que também será adotada no restante deste trabalho. Portanto, o símbolo esquemático da figura 1.2 não será mais usado.

Ao contrário do diodo de junção pn, o SBD é um dispositivo exclusivamente de portadores majoritários. Apesar desta diferença fundamental, a corrente no SBD ainda depende exponencialmente da tensão intrínseca da junção,  $V_{D,i}$  segundo a mesma equação do diodo pn ideal:

$$I_{D} = I_{S} \left[ exp \left( \frac{V_{D,i}}{nV_{T}} \right) - 1 \right]$$

(1.1)

A equação (1.1) descreve a característica I-V de um diodo ideal, isto é, apenas a junção em si. Diodos reais também incluem um efeito parasita na forma de uma resistência em série  $R_S$ , que provém da resistência dos contatos, da resistência de corpo do semicondutor, e de outros efeitos.  $R_S$  é inversamente proporcional a  $W_g$ , e a queda de tensão sobre ela reduz a tensão vista pelo diodo ideal interno,  $V_{D,i}$ , conforme a equação:

$$V_{D,i} = V_{D,e} - I_{D}R_{S}$$

(1.2)

onde  $V_{D,e}$  é a tensão externa aplicada nos terminais do diodo real. Correntes diretas altas no diodo são limitadas por  $R_S$ . A equação (1.2) pode ser visualizada no circuito equivalente do SBD, mostrado na figura 1.3:

Figura 1.3 - Circuito equivalente do modelo do diodo Schottky usado no SPICE.

Neste circuito,  $I_D$  é uma fonte de corrente controlada por  $V_{D,i}$ , provendo a corrente do diodo segundo a equação (1.1).  $C_D$  é uma capacitância não-linear que modela a carga armazenada na região de depleção da junção MES do SBD, e a sua equação é igual a da capacitância de depleção de uma junção **pn**.

A constante de tempo que limita a resposta em frequência de um SBD é dada por R<sub>S</sub>.C<sub>D</sub>. Além de C<sub>D</sub>, existe também a capacitância parasita geométrica do dispositivo, que aparece em paralelo com os contatos, mas na maioria dos casos C<sub>D</sub> é muito maior do que essa capacitância [6]. No SBD não existe a capacitância de difusão (que é a principal causa da capacitância direta da junção pn), e assim o seu tempo de trânsito é muito menor do que o do diodo de junção pn, o que leva a uma resposta muito mais rápida sob polarização direta. Isso possibilita ao SBD ser usado como componente para circuitos na faixa de microondas.

Nas regras de projeto de *foundries*, normalmente o comprimento  $L_g$  do contato Schottky já vem pré-fixado em um valor adequado para reduzir a  $R_S$  dos diodos; no processo da Vitesse, usado neste trabalho, todos os diodos devem ter  $L_g$  = 0,6  $\mu$ m (como estabelecido na página 4-9 de [12], que é o manual de projeto da Vitesse e descreve o seu processo HGaAs-III de 0,6  $\mu$ m). Já a largura  $W_g$  dos diodos pode ser escalonada pelo projetista, conforme as exigências da aplicação no circuito. Mas se o projetista tiver controle também sobre  $L_g$ , é preciso lembrar que a corrente em um diodo diminui exponencialmente com o aumento do seu comprimento [11]. A razão para isso é que, quanto maior  $L_g$ , maior a queda IR no diodo e menor a tensão intrínseca  $V_{D,i}$ , diminuindo a corrente. Por isso, de qualquer maneira, os diodos devem ser projetados com  $L_g$  fixo, e a sua área deve ser ajustada por meio de  $W_g$ .

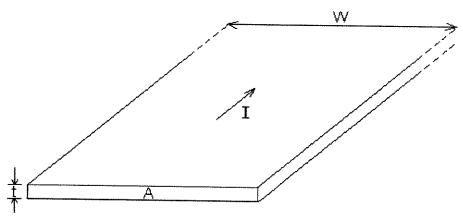

A dependência dos parâmetros do diodo com a área da sua seção transversal,  $A = W_g.L_g$ , é linearmente proporcional, conforme indicado nas relações (1.3). Os parâmetros do modelo de diodo do SPICE, usados para o SBD de GaAs, e métodos para a sua extração, são explicados em [11] e [13].

$$A \uparrow \Rightarrow I_S \uparrow, C_{j0} \uparrow, R_S \downarrow \tag{1.3}$$

#### 1.3.2. Teoria da Operação do MESFET.

O MESFET é um dispositivo de estrutura planar, sendo o tipo de transistor mais conveniente para a fabricação em GaAs, pois, ao contrário do JFET, o MESFET não requer a utilização de regiões com dopagem tipo **p**.

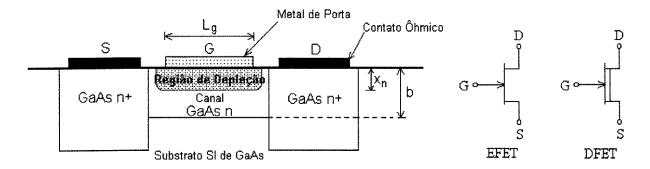

A mesma discussão feita para o MESFET também é válida para o JFET, pois ambos são dispositivos unipolares de lei quadrática (não são exponenciais como o BJT). A diferença entre o JFET e o MESFET é que, neste, o contato da porta é uma junção MES retificadora (um diodo Schottky), e no JFET a junção da porta com o canal é uma junção pn, ambas desempenhando a mesma função. Porém, como os dois tipos de junção têm basicamente as mesmas características, o MESFET resulta muito parecido com o JFET a nível de terminais (mas é mais rápido). A estrutura idealizada em seção longitudinal de um MESFET é mostrada na figura 1.4.

A dopagem e a espessura da camada ativa tipo  $\mathbf{n}$  são dimensionadas de modo que o canal possa ser totalmente depletado por meio da tensão  $V_{GS}$  aplicada entre porta e fonte, havendo, idealmente, o corte da corrente de dreno do transistor para  $V_{GS}$  menor ou igual a um certo valor, chamado de tensão de limiar (threshold voltage),  $V_t$ .

Figura 1.4 – Seção de um MESFET. A largura  $W_g$  do transistor é perpendicular ao plano da página, e  $x_n$  é a profundidade da região de depleção abaixo da porta.

Os desempenhos relativos de transistores de GaAs e Si têm sido muito discutidos na literatura [6]. As principais diferenças entre os MESFETs de GaAs e os MOSFETs de Si estão nas seguintes características:

- 1. A forma de acoplamento entre o contato de porta e o canal: a porta metálica de um MESFET faz contato direto com o canal, enquanto que, no MOSFET, o eletrodo de porta é separado do canal por uma fina camada isolante de SiO<sub>2</sub>. Assim, a junção Schottky de porta do MESFET conduz uma corrente I<sub>GS</sub> para a sua fonte, quando polarizada diretamente. Com o fluxo de corrente para o terminal de porta, o nível lógico alto fica grampeado em 0,7 V pela tensão da barreira de potencial.

- 2. O mecanismo de formação do canal: o canal de um MESFET, quer ele seja de enriquecimento ou de depleção, já é previamente implantado durante o seu processo de fabricação, e a sua espessura é controlada pela tensão aplicada na junção MES. O canal do transistor NMOS de enriquecimento é formado durante a operação do dispositivo em um circuito, quando a superfície do Si tipo  $\bf p$  é invertida, passando a conter uma alta densidade de elétrons. E o MOSFET de depleção é formado com uma leve dopagem do canal, para deslocar o seu limiar de operação  $V_t$  para um valor negativo e torná-lo normalmente ligado.

- 3. A viabilidade de transistores complementares: não compensa utilizar FETs de GaAs de canal  $\bf p$  para a construção de circuitos, porque suas frequências  $f_t$  são muito mais baixas que as dos FETs de canal  $\bf n$ . A razão para isso é que  $\mu_p << \mu_n$ . As vantagens de uma lógica complementar (que usa transistores complementares na mesma porta lógica) podem ser vistas comparando-se NMOS com CMOS: maior excursão da tensão de saída e menor dissipação de potência. Circuitos complementares com JFETs de GaAs foram construídos e demonstraram uma velocidade razoável de chaveamento, porém limitada pela baixa  $\mu_p$ , que leva a uma transcondutância muito baixa em  $\bf p$ -JFETs. O projeto complementar de CIs de GaAs só é útil quando uma redução de potência torna-se obrigatória [14].

- 4. Menores capacitâncias: um FET de GaAs não tem junções pn em torno de seus contatos de fonte e dreno, e portanto as capacitâncias inter-eletródicas em dispositivos de GaAs são muito menores. Essas diferenças entre os dispositivos influenciam os projetos de circuitos em GaAs e em MOS de modo decisivo, tornando-os bastante diferentes.

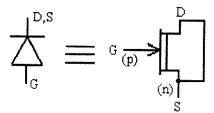

Os MESFETs atualmente usados em CIs podem ser de dois tipos: de enriquecimento (EFET) ou de depleção (DFET), dependendo do sinal de  $V_t$ : o EFET tem uma  $V_t$  positiva, enquanto o DFET tem uma  $V_t$  negativa. O MESFET de enriquecimento é dito "normalmente desligado" porque um  $V_{GS}$  positivo é necessário para abrir o canal para os elétrons fluírem da fonte para o dreno; isto é, ele não "funciona" com  $V_{GS}=0$ . O MESFET de depleção é dito "normalmente ligado" porque ele requer a aplicação de uma tensão  $V_{GS}$  negativa para cortar a corrente de dreno,  $I_D$ ; isto é, ele "funciona" mesmo com  $V_{GS}=0$  V.

Tanto EFETs como DFETs operam pelo mesmo princípio, a depleção de um canal já existente e dopado; a região de depleção é obtida através da junção MES da porta. As alturas dos canais de ambos os tipos de MESFET são controladas pela altura da região de depleção,  $x_n$ , através de  $V_{GS}$ . A única diferença é que o canal do DFET está aberto para  $V_{GS} = 0$ .

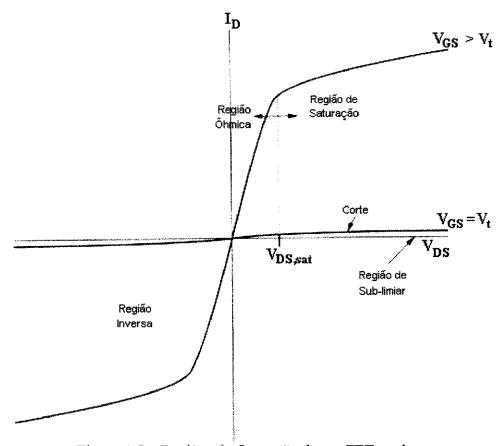

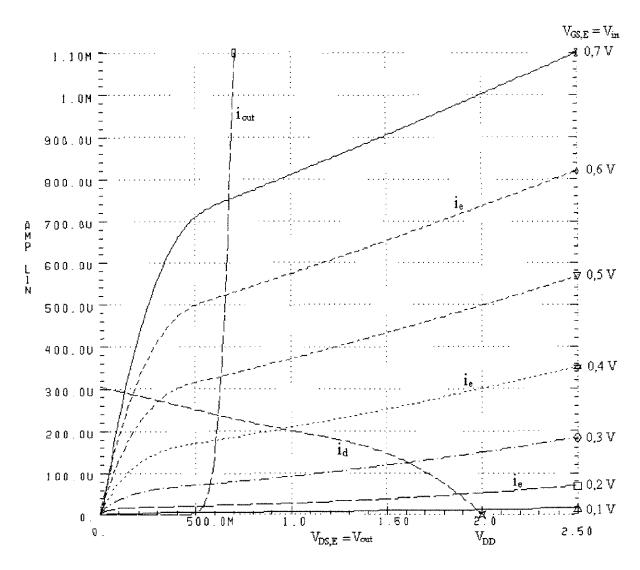

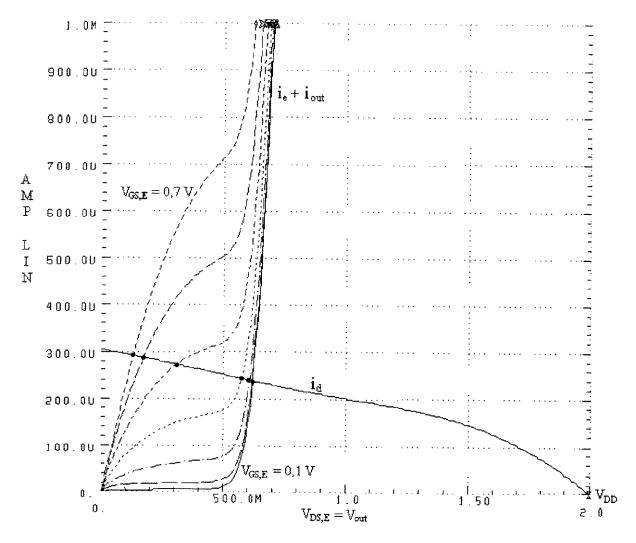

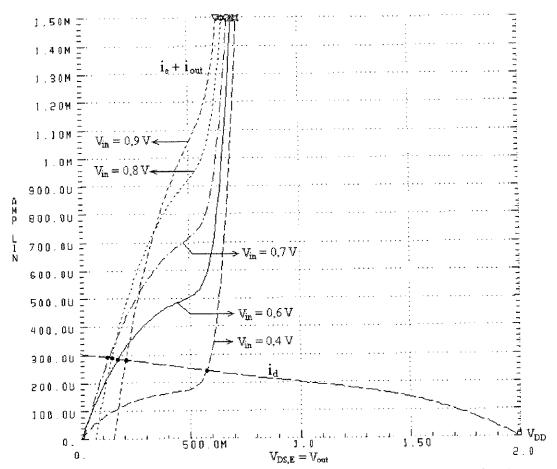

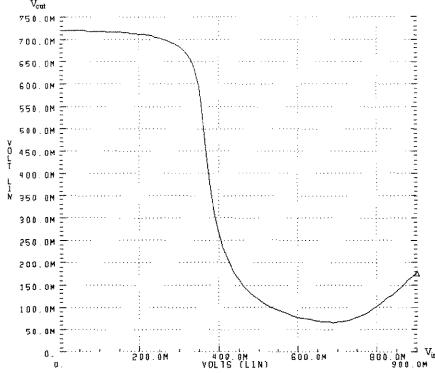

A figura 1.5 ilustra as regiões de operação de um FET genérico. Inicialmente, observase que as curvas características I-V de um FET são simétricas em torno da origem dos eixos, por causa da simetria de construção do dispositivo, resultando na existência das mesmas regiões de operação no primeiro e no terceiro quadrantes.

No **corte**, a região de depleção da porta penetra completamente através do canal, bloqueando o fluxo de elétrons e cortando  $I_D$ . Em uma primeira aproximação, o FET está no corte enquanto  $V_{GS} \leq V_t$ , mas se for desejada maior precisão de análise, pode-se considerar a existência da  $I_D$  residual para essa região de operação, que passa a se chamar **região de sub-limiar**. Mais detalhes sobre a região de sub-limiar serão dados adiante.

Quando  $V_{GS}$  é maior do que o valor de  $V_t$  do dispositivo, e uma pequena tensão  $V_{DS}$  é mantida aplicada ao FET, o seu canal passa a se comportar como um resistor de seção transversal retangular e área igual a  $W_g$  ( $b-x_n$ ), onde  $x_n$  é definida na figura 1.4. Se  $V_{GS}$  aumenta,  $x_n$  diminui proporcionalmente, aumentando a área do resistor de canal e reduzindo a sua resistência. Essa região de operação, válida para pequenos valores de  $V_{DS}$ , é chamada de **região linear ou ôhmica** da curva I-V do MESFET, porque nela o transistor se comporta como uma resistência linear  $r_{ds}$ , inversamente proporcional a  $V_{GS}$ . Da mesma forma que em um MOSFET, quanto maior a tensão  $V_{GS}$ , maior será a inclinação da "reta"  $I_D \times V_{DS}$  na região linear, que representa a condutância de pequenos sinais entre dreno e fonte:

$$g_{ds} = \left[\frac{\partial I_{D}}{\partial V_{DS}}\right]_{V_{GS} \text{ constante}}$$

(1.4)

A linearidade da resistência de canal  $r_{ds}$  ocorre dentro de uma faixa limitada de  $V_{DS}$ . À medida em que  $V_{DS}$  aumenta, a inclinação da curva  $I_{D} \times V_{DS}$  diminui gradualmente, e  $r_{ds}$  aumenta. Depois que  $V_{DS}$  atinge e supera o seu valor de saturação  $V_{DS,sat}$ , com  $V_{GS} > V_t$ ,  $I_{D}$  torna-se quase constante e igual a um valor  $I_{D,sat}$ , e assim permanece para aumentos posteriores de  $V_{DS}$ , o que pode ser constatado na figura 1.5. Nessa nova região de operação, chamada de **região de saturação**, o FET opera por um novo mecanismo, havendo dois modelos para explicar o seu funcionamento: o modelo clássico de canal gradual, proposto por W. Shockley, e o modelo de saturação da velocidade dos elétrons. Uma análise matemática detalhada dos dois modelos é apresentada em [6].

Figura 1.5 – Regiões de Operação de um FET qualquer.

O modelo de canal gradual aplica-se bem somente a FETs de porta longa ( $L_g$  muito maior do que a altura do canal, b -  $x_n$ ), e portanto não será usado neste trabalho. Já o modelo de saturação de velocidade atribui a saturação de  $I_D$  à saturação da velocidade dos elétrons no canal, que começa a ocorrer com o crescimento de E além de  $E_c$  (= 3,5 kV/cm), como visto na figura 1.1. Este modelo dá uma descrição melhor do funcionamento de MESFETs de porta curta ( $L_g$  < 2  $\mu$ m), porque  $E_c$  pode ser atingido, no canal, com uma menor  $V_{GS}$ , já que

$$E_{c} = \frac{V_{GS} - V_{t}}{L_{g}} \tag{1.5}$$

e assim o canal não chega a sofrer constrição para haver a saturação de  $I_D$ , porque a velocidade dos elétrons atinge um valor limite antes que isso aconteça, se  $L_g$  é curto. O ponto onde  ${\bf v}$  satura inicialmente é a extremidade do canal próxima ao dreno. A tensão  $V_{DS,sat}$  e a corrente  $I_{D,sat}$ , para FETs de canal curto, são muito menores do que os valores previstos pelo modelo de canal gradual; a menor  $I_{D,sat}$  deve-se ao fato de que  ${\bf v}$  agora tende a um limite.

Quando  $V_{DS}$  é aumentado já dentro da região de saturação, a corrente  $I_D$  continua a crescer, embora mais lentamente do que na região linear. O mecanismo que gera essa condutância finita  $g_{ds}$  na saturação é chamado de modulação do comprimento do canal; a interpretação do fenômeno, para FETs de canal curto, é dada em [11].

Menores comprimentos de porta  $L_g$  levam a maiores correntes de dreno por unidade de largura de porta,  $W_g$  [6].  $I_D$  só é inversamente proporcional a  $L_g$  para FETs de porta longa; para dispositivos de porta curta, se  $L_g$  é reduzido ainda mais,  $I_D$  também cresce, mas a uma taxa menor do que  $1/L_g$ . Isso se deve aos efeitos de saturação da velocidade.

A corrente  $I_D$  do MESFET, na região linear e na saturação, é diretamente proporcional a  $W_g$ , para  $W_g \geq 3~\mu m$ . Para larguras menores, os efeitos de canal estreito (frangeamentos laterais) invalidam essa relação, e além disso as tolerâncias do processo na definição de larguras causam flutuações indesejáveis no valor projetado de  $I_D$ . Por isso, MESFETs estreitos não devem ser utilizados.

#### 1.3.2.1. Transcondutância e Frequência de Ganho Unitário.

A transcondutância  $(g_m)$  de um FET de GaAs é muito maior do que a de um FET de Si de mesmo  $L_g$ , tipicamente por um fator de três ou quatro, em níveis de tensão usuais. A alta  $g_m$  melhora muito a velocidade porque, com uma excursão  $v_{gs}$  menor obtém-se a mesma corrente de pico, para carregar ou descarregar uma capacitância de carga. Para fins de projeto,  $g_m$  é diretamente proporcional a  $W_g$ , e também é maior para MESFETs de menor  $L_g$ .

A frequência de ganho de corrente unitário,  $f_t$ , de um MESFET, que é o seu produto (ganho de corrente)x(largura de banda), determina a velocidade máxima de chaveamento do transistor. O MESFET não sofre efeitos de armazenagem de portadores minoritários, o que lhe confere alta velocidade de chaveamento e altas  $f_t$ 's. As capacitâncias não-lineares e as parasitas fixas reduzem a  $f_t$ , e para combater o seu efeito é importante que o transistor possua uma alta  $g_m$ .

O valor de f<sub>t</sub> é inversamente proporcional ao L<sub>g</sub> do MESFET, contanto que as capacitâncias de porta não sejam dominadas pelas componentes de frangeamento, o que acontece para L<sub>g</sub>'s muito curtos. Isso pode ser evitado com maiores níveis de dopagem do canal. O valor da frequência de corte f<sub>t</sub>, para MESFETs fabricados em processos modernos, é da ordem de 35 GHz [15].

#### 1.3.2.2. Não-idealidades do MESFET.

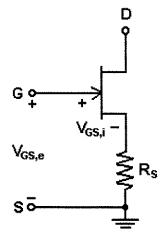

A resistência parasita da fonte,  $R_S$ , é a resistência existente entre o contato de fonte e a borda da porta, proporcional à separação entre eles. O efeito de  $R_S$  é o de reduzir a tensão  $V_{GS}$  aplicada nos terminais (extrínseca),  $V_{GS,e}$ , pela queda de tensão através de  $R_S$ , como ilustrado na figura 1.6. Desse modo, a tensão  $V_{GS}$  realmente vista pela junção de porta (intrínseca),  $V_{GS,i}$ , é dada por

Figura 1.6 – R<sub>S</sub> reduz a tensão V<sub>GS</sub> intrínseca, diminuindo I<sub>D</sub> e g<sub>m</sub>.

$R_S$  também produz um efeito similar em  $g_m$ : a  $g_m$  disponível nos terminais de um MESFET é reduzida por  $R_S$ . Certamente, também existe uma resistência parasita de dreno,  $R_D$ , que deve ser igual a  $R_S$  para manter-se a simetria do dispositivo. Os valores típicos de  $R_S$  e  $R_D$  situam-se na faixa de dezenas de ohms.  $R_S$  e  $R_D$  dependem principalmente dos espaçamentos entre os terminais de porta e fonte e de porta e dreno, sendo proporcionais a esses espaçamentos.

A corrente de porta  $I_{GS}$  de um MESFET resulta da polarização direta da junção entre porta e fonte, uma vez que não existe isolamento entre a porta e o canal. Quando o terminal de porta é polarizado com  $0.7 \sim 0.8$  V acima do potencial de fonte, a corrente da junção torna-se considerável e é atingido o limite de tensão direta. Isso limita a excursão de tensão na saída de uma porta lógica que aciona a entrada de outra porta (porque limita o valor de  $V_{OH}$ ), limitando portanto as margens de ruído nos nós internos de um circuito, o que será detalhado no Capítulo 2. Este é um efeito indesejável da operação do MESFET, que não ocorre com circuitos MOS. A corrente  $I_{GS}$  faz com que o estágio acionado represente uma carga para o estágio acionador, e tem um efeito degradante sobre o desempenho de um circuito.

Se, por efeito do projeto das portas lógicas de um circuito, o  $V_{GS}$  aplicado em um FET ficar muito alto (digamos,  $V_{GS} = 0.8$  V), então  $I_{GS}$  torna-se alta demais e irá causar uma queda de tensão  $V_{DS} = I_{GS}.R_S$  adicional sobre  $R_S$ . Essa tensão extra faz com que a curva característica do MESFET desloque-se para a direita por esse valor; isso pode ser visualizado nas figuras 1.5 e 3.11. Esse *offset* de  $V_{DS}$  é nocivo para uma porta lógica, porque causa um aumento da tensão de nível lógico baixo  $V_{OL}$ , com a correspondente redução da margem de ruído. Outros efeitos de uma tensão de entrada excessiva serão analisados no Capítulo 3.

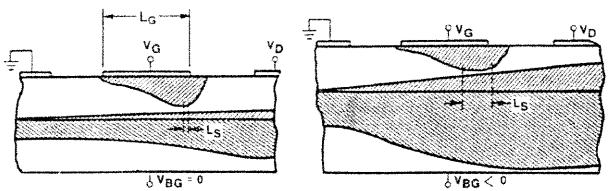

O fenômeno de backgating (também chamado de sidegating) consiste na redução da corrente de dreno de um MESFET, causada pelo aumento do valor da sua tensão V<sub>t</sub>, que por sua vez é provocado pela polarização negativa do substrato em relação ao seu canal. Este efeito é induzido em um MESFET por outros MESFETs próximos (daí o nome sidegating), cujas fontes estejam polarizadas negativamente em relação à fonte do primeiro MESFET. A tensão de fonte em um FET afeta a condução no canal de FETs adjacentes através de uma modulação da região de depleção existente na interface canal/substrato. Surge, portanto, uma interação parasita entre dispositivos vizinhos na superfície do substrato. Geralmente, a

intensidade dessa interação depende da distância e diferença de potencial entre os dispositivos, e é dependente do processo.

O backgating nos FETs de GaAs é um efeito relacionado com a junção entre o canal (área ativa) e o substrato semi-isolante que está por baixo; é equivalente ao efeito de corpo observado nos MOSFETs. A altura da região de depleção que se estende dentro do canal, junto à interface com o substrato, é quase diretamente proporcional ao valor da tensão de polarização negativa do substrato em relação ao canal [6], chamada de tensão de backgate, V<sub>BG</sub>; seus efeitos no formato dessa região de depleção são mostrados na figura 1.7. As resistências série de fonte e dreno R<sub>S</sub> e R<sub>D</sub>, também crescem com o aumento da tensão reversa V<sub>BG</sub>, o que tem um efeito profundo no desempenho de circuitos de FETs de GaAs [16].

O backgating pode exercer uma grande influência no desempenho de circuitos digitais, mas pode ser desprezado para circuitos que operem com tensões de alimentação médias ou baixas, e para operação na temperatura ambiente ou acima dela. Os circuitos suscetíveis ao backgating são aqueles que operam com tensões de alimentação elevadas e/ou em baixas temperaturas (abaixo de 0°C). A influência do backgating em um circuito também depende do seu projeto.

Figura 1.7 – Efeito de uma tensão V<sub>BG</sub> negativa sobre a forma da região de depleção entre canal e substrato [6].

Os efeitos de *backgating* não são observados para substratos polarizados positivamente. Por isso, os CIs fabricados pela Vitesse devem receber uma polarização de substrato  $V_{BG} > 0$  V, aplicada sob os chips (por baixo da *die*), de valor igual a 0,6 V acima da menor tensão de alimentação aplicada ao CI. Os encapsulamentos LDCC oferecidos pela Vitesse possuem um pino próprio para a aplicação da tensão  $V_{BG}$ , e o modelo de MESFET da Vitesse para o SPICE inclui o nó de *backgate* para simular a influência dessa polarização. Para uma explicação mais detalhada e um equacionamento dos mecanismos desse fenômeno, consultar [11], [6] e [16].

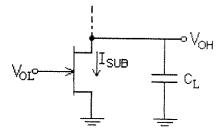

A corrente de dreno de um FET não se anula quando  $V_{GS} \leq V_t$ , existindo uma pequena corrente  $I_D$  de fuga residual que é chamada **corrente de sub-limiar**,  $I_{SUB}$ . Essa corrente depende exponencialmente de  $V_{DS}$  e  $V_{GS}$ , e é inversamente proporcional a  $L_g$ .  $I_D$  continua a fluir mesmo com  $V_{GS}$  estando muitos décimos de volt abaixo de  $V_t$ , o que seria a região de corte em uma aproximação de primeira ordem.

A corrente  $I_{SUB}$  é irrelevante para o projeto de circuitos lógicos otimizados para alta velocidade, nos quais a dissipação de potência é de média para alta (> 1 mW / porta lógica), mas é muito importante para o modelamento de circuitos de potência muito baixa (< 0,1 mW /

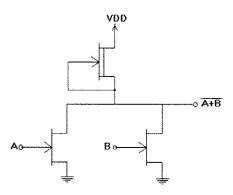

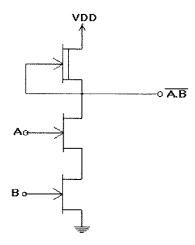

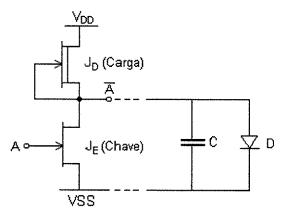

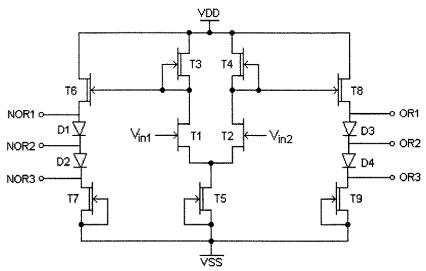

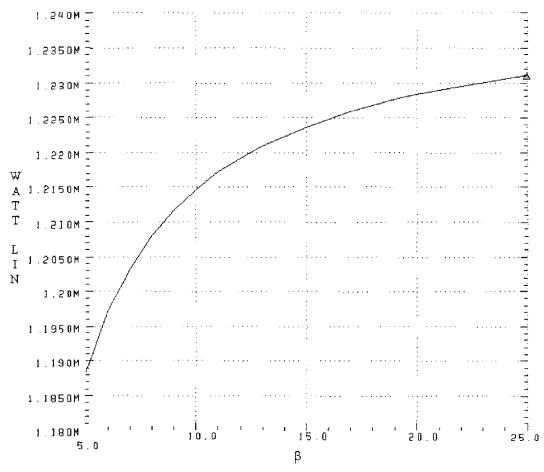

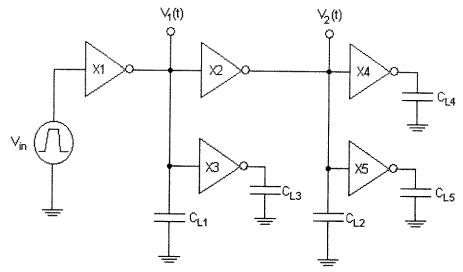

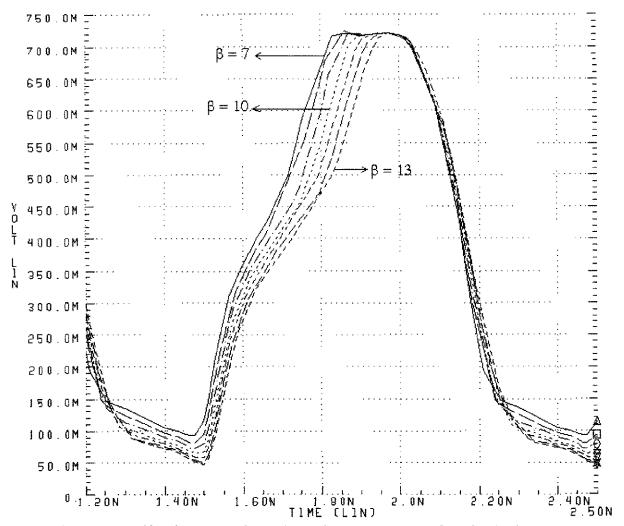

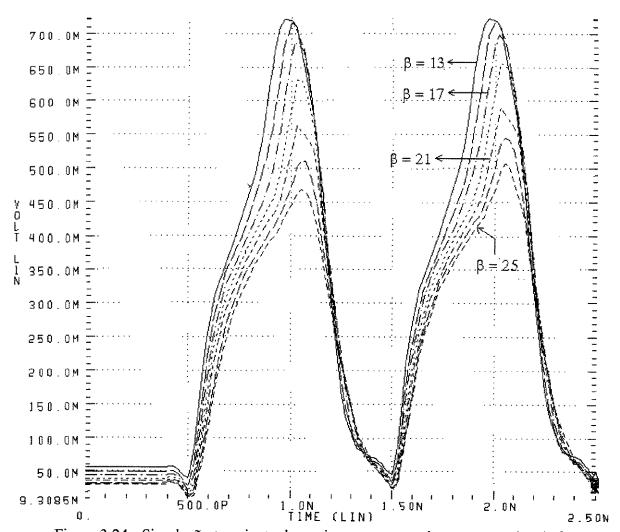

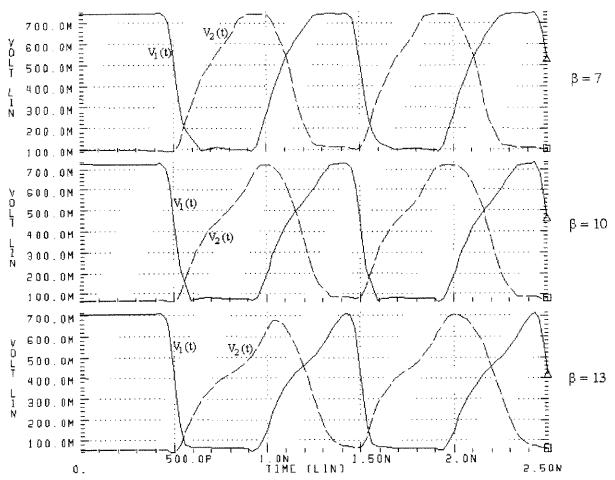

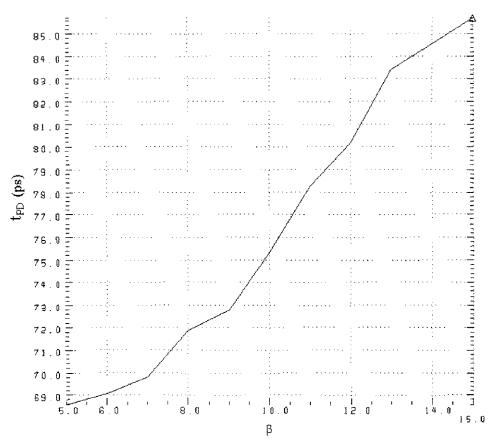

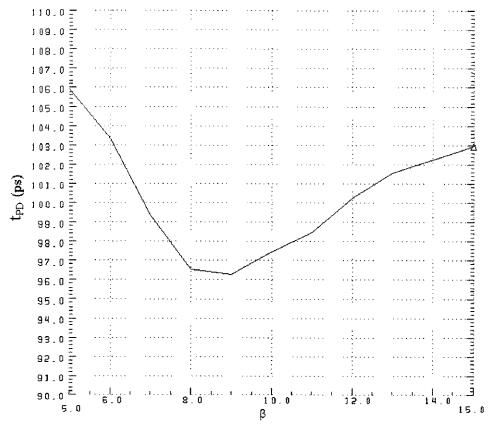

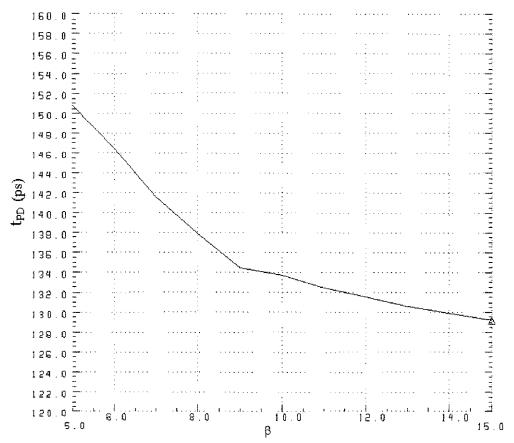

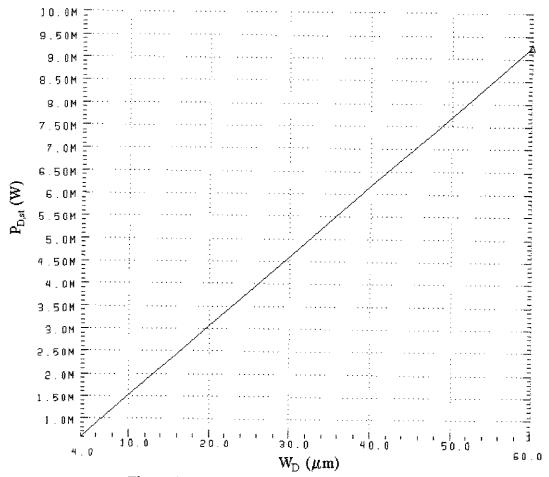

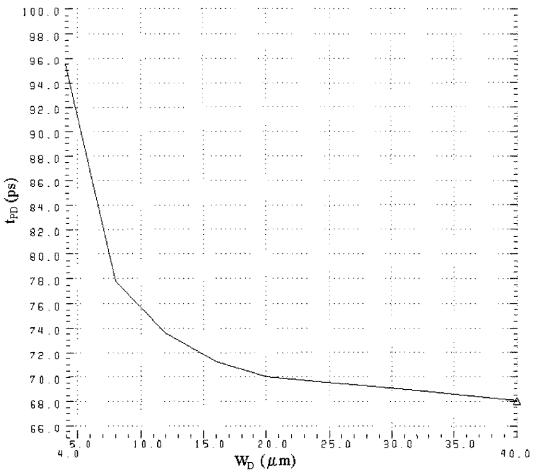

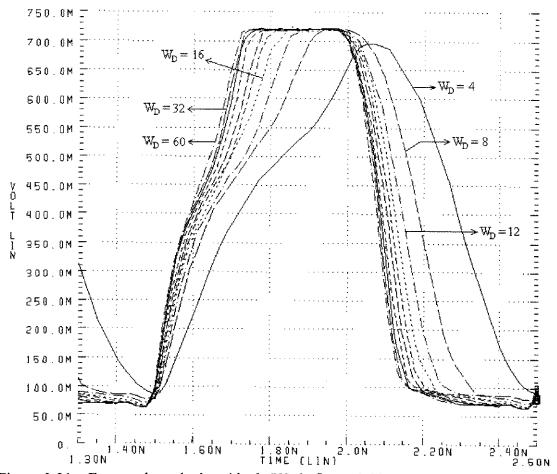

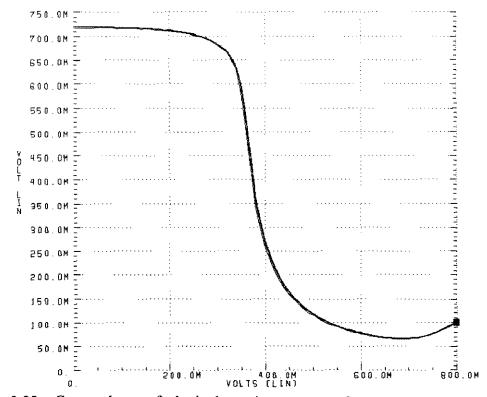

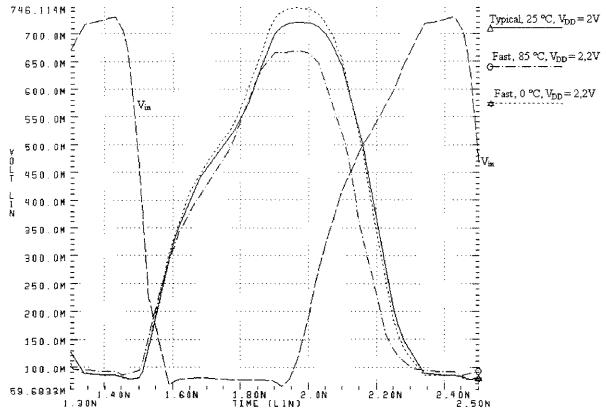

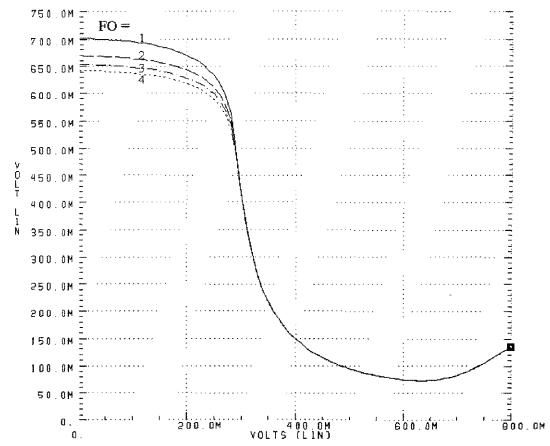

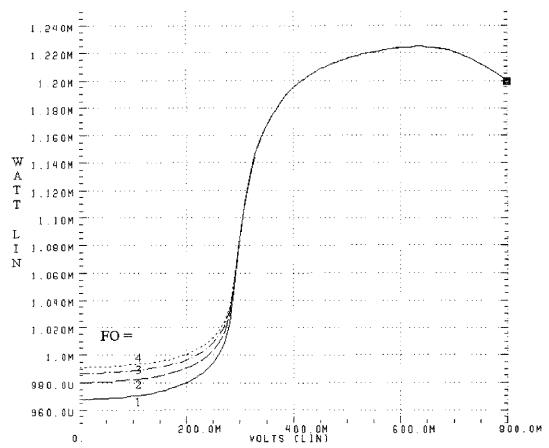

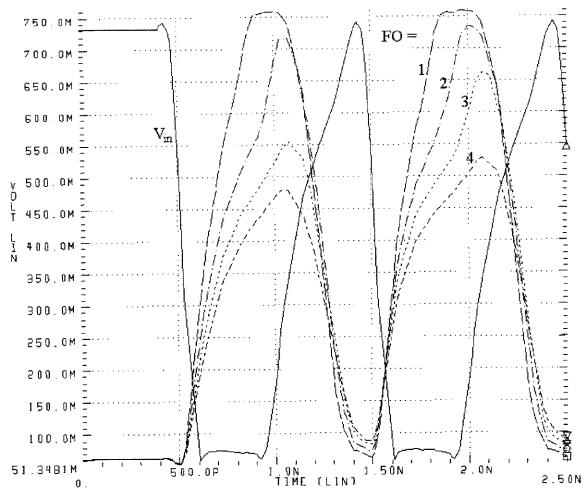

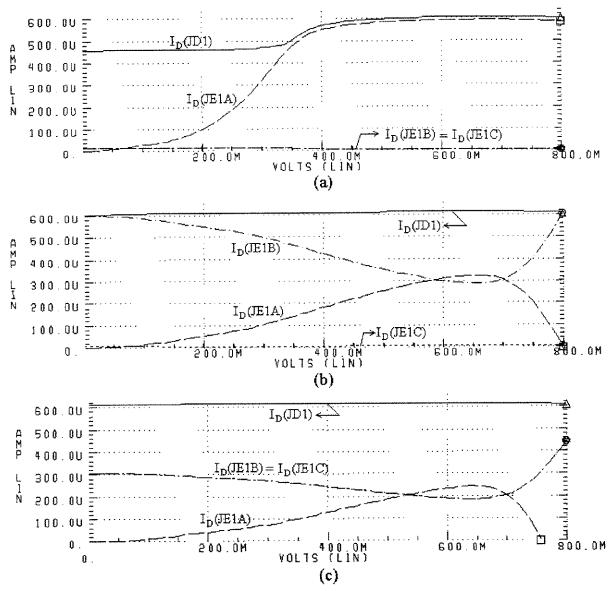

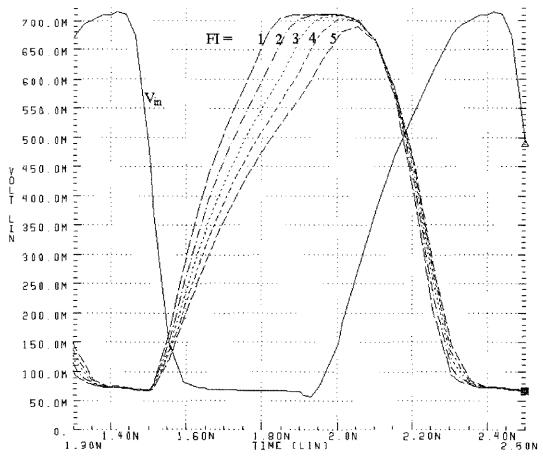

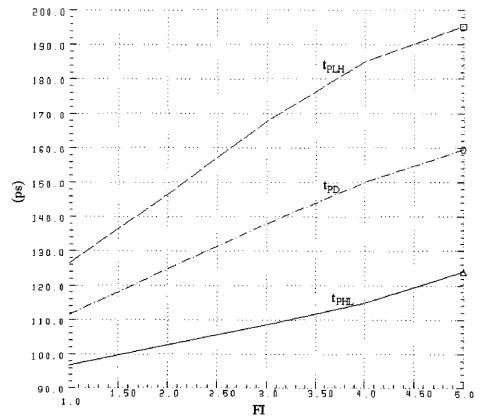

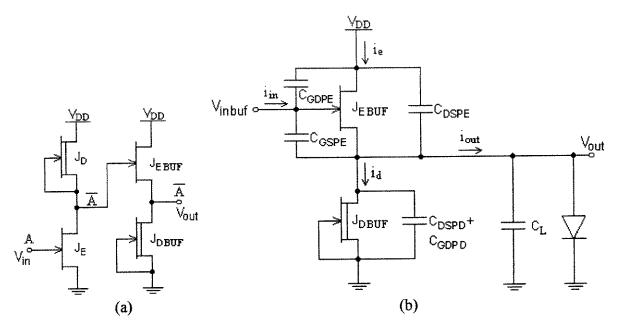

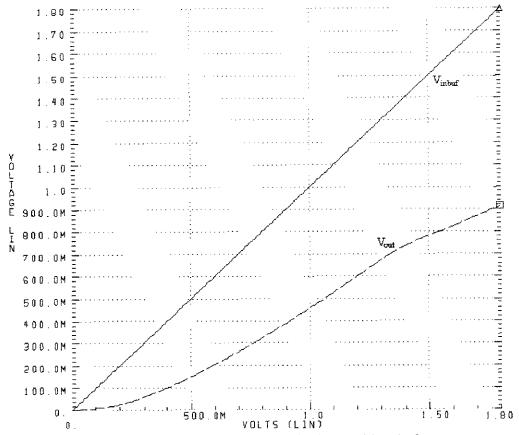

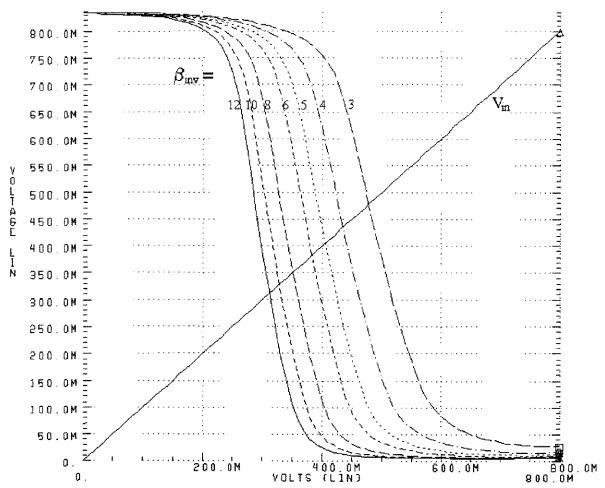

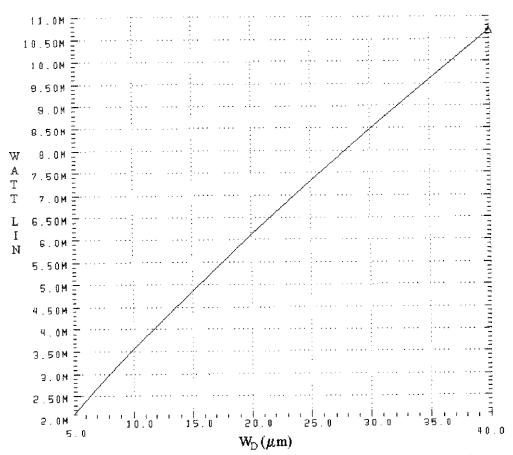

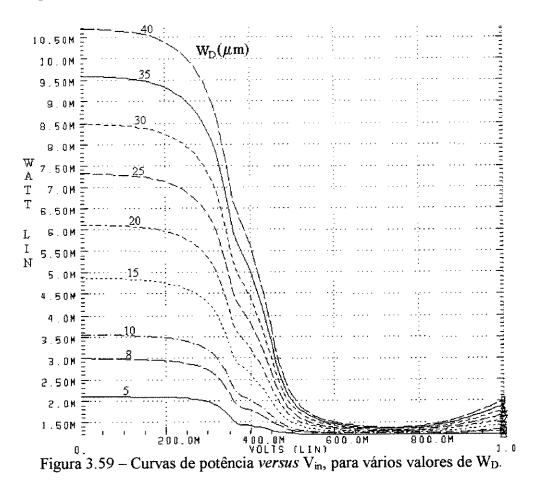

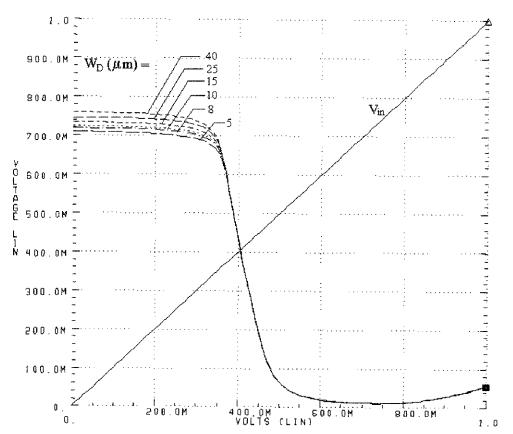

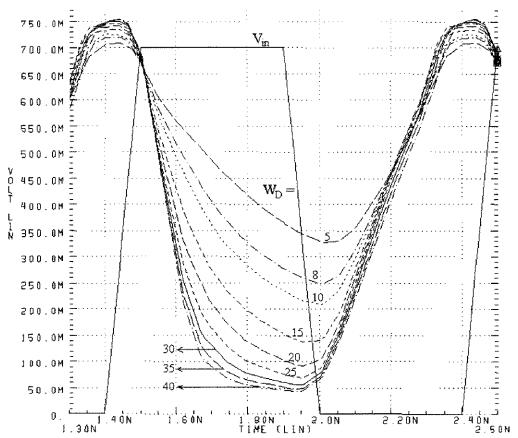

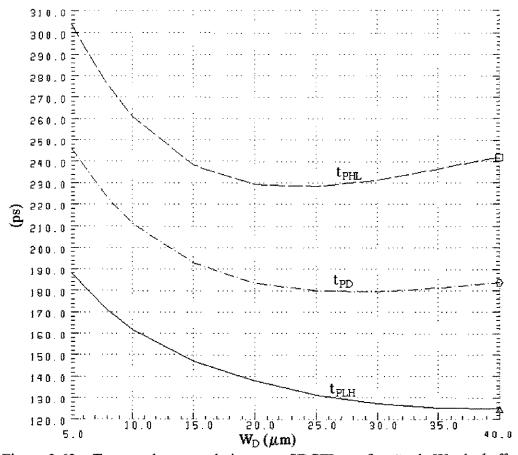

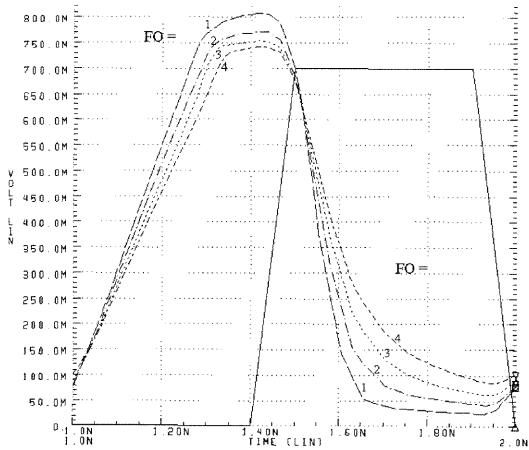

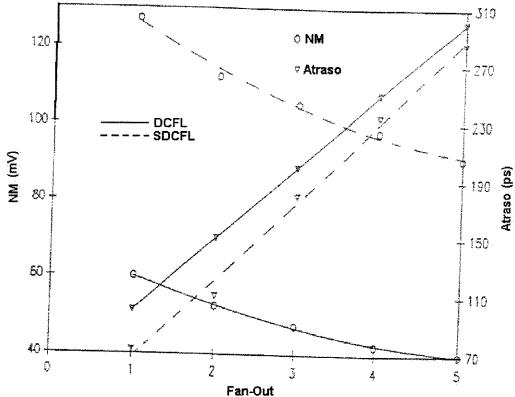

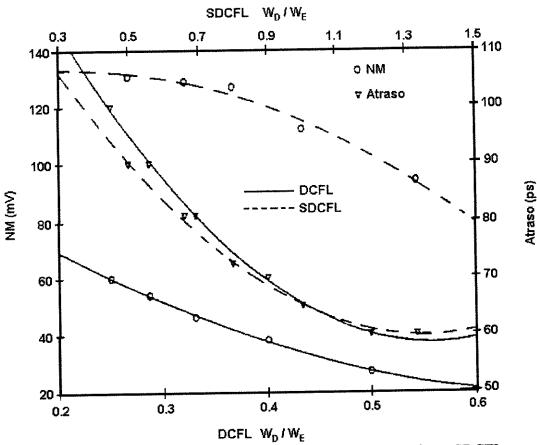

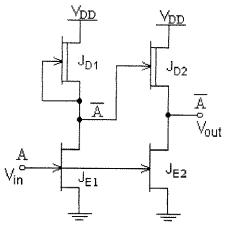

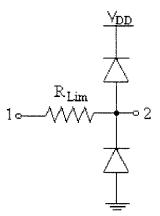

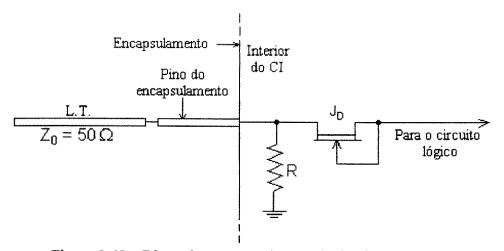

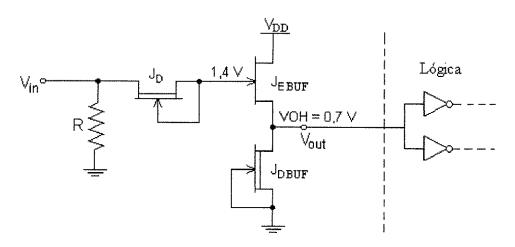

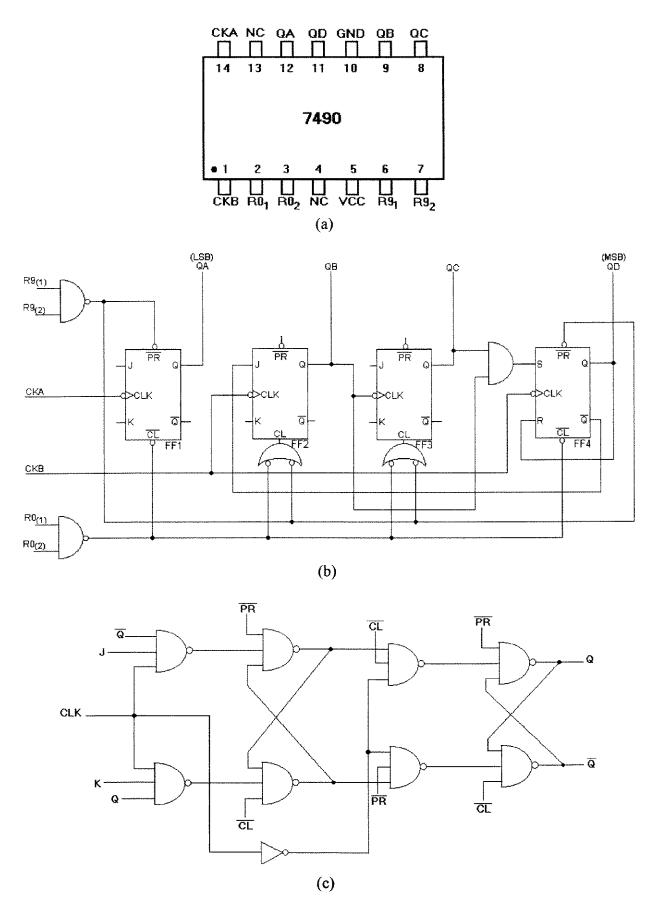

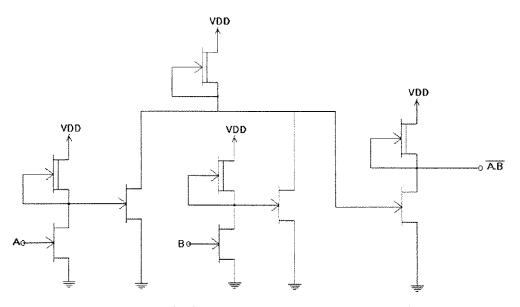

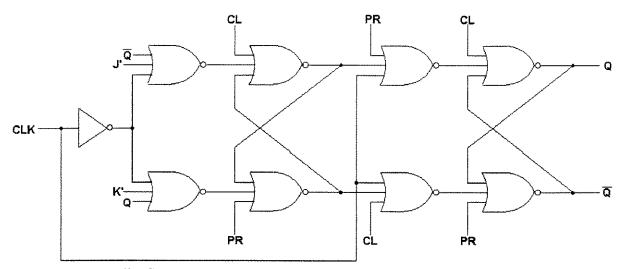

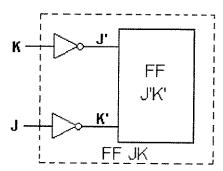

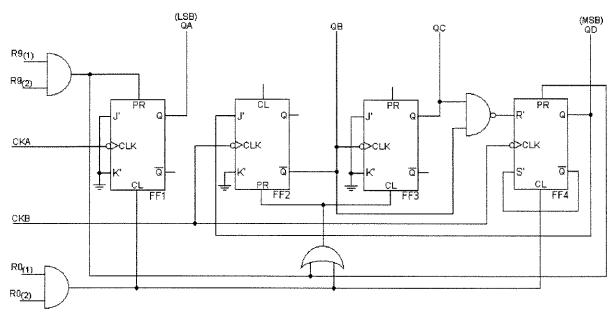

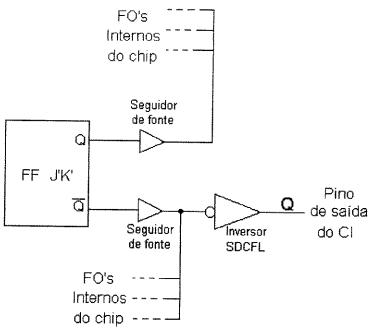

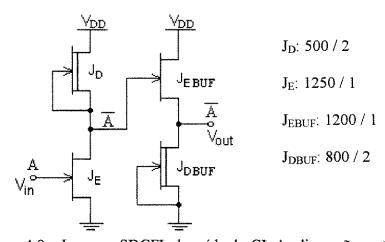

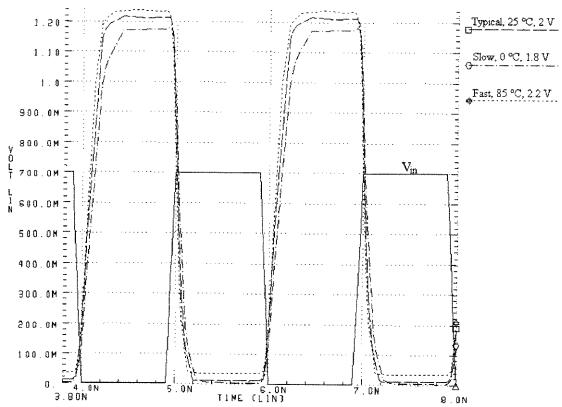

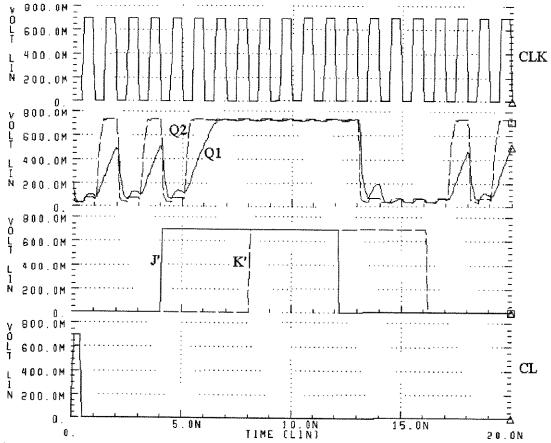

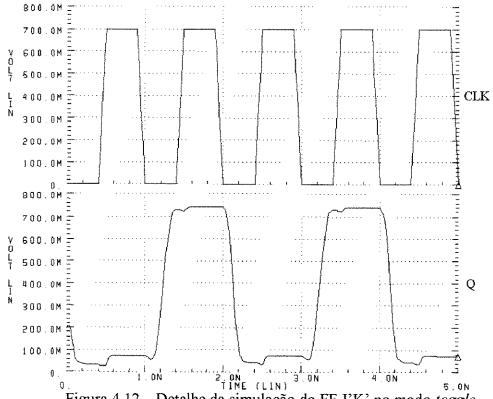

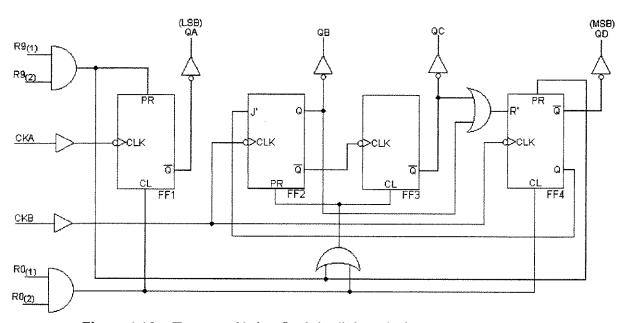

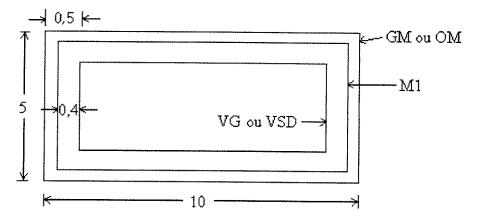

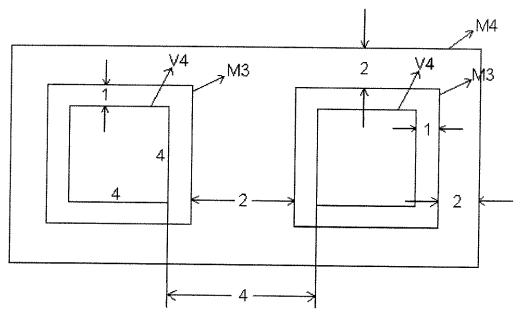

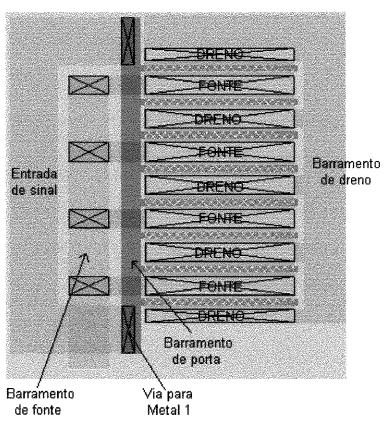

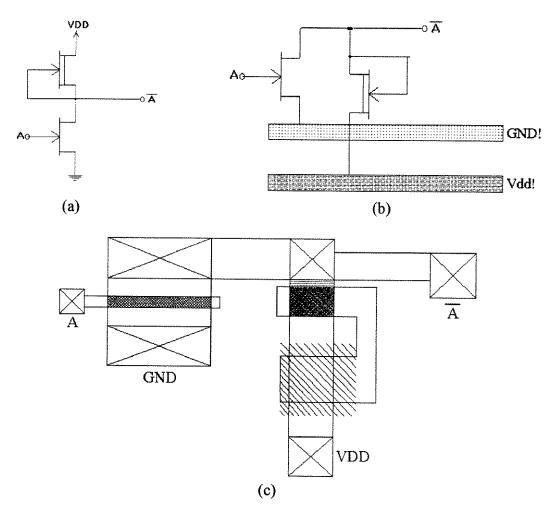

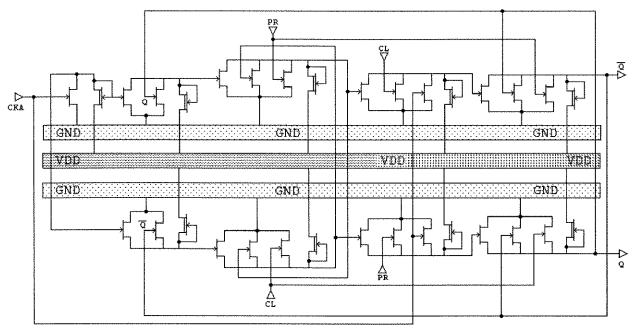

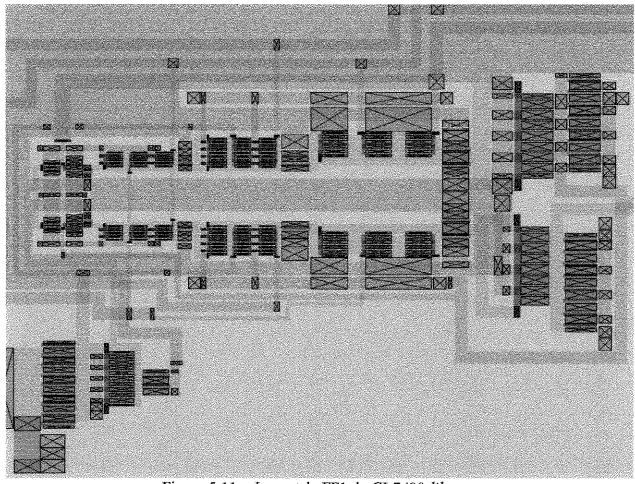

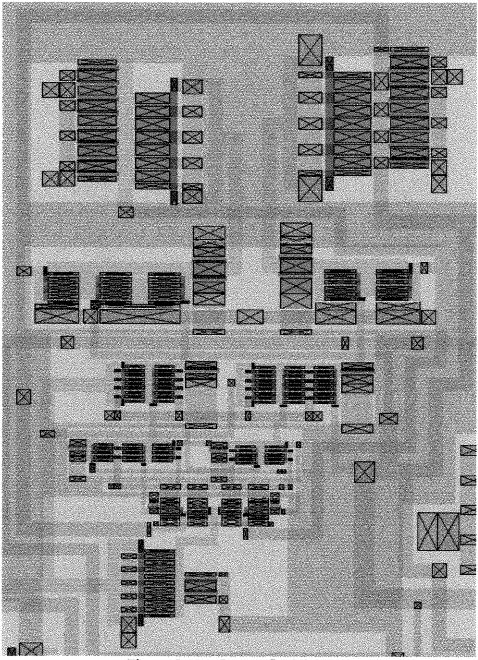

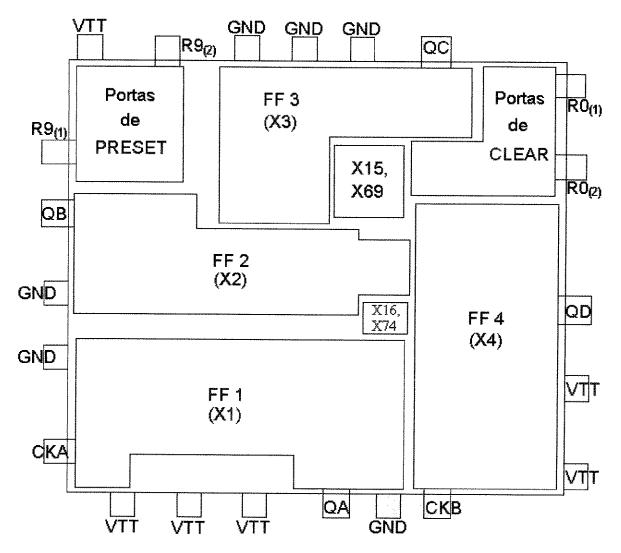

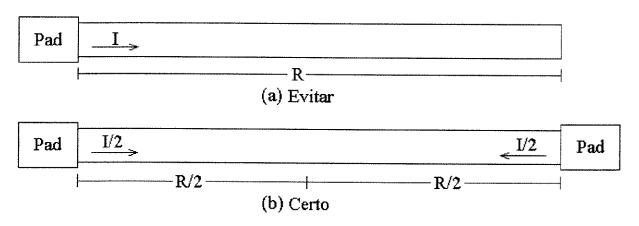

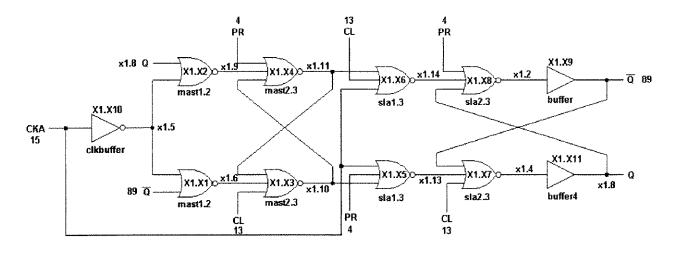

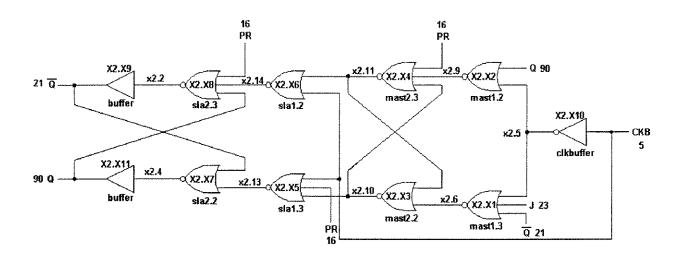

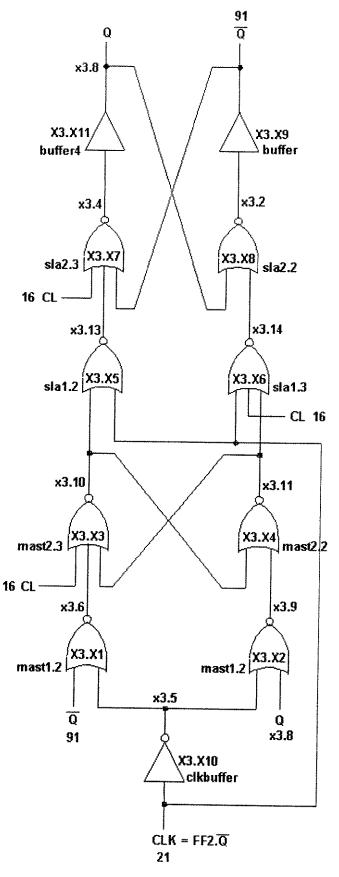

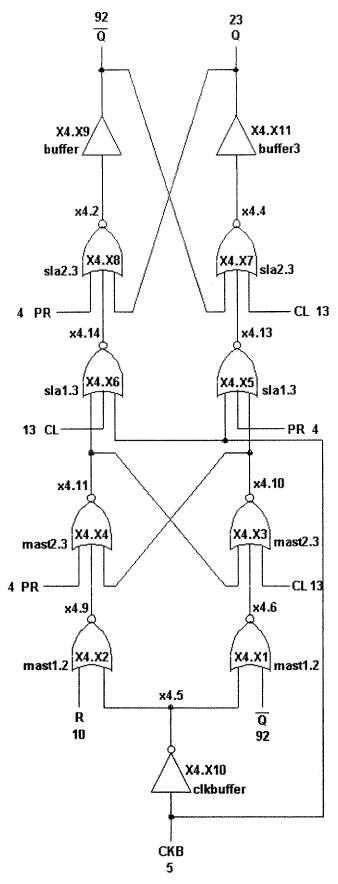

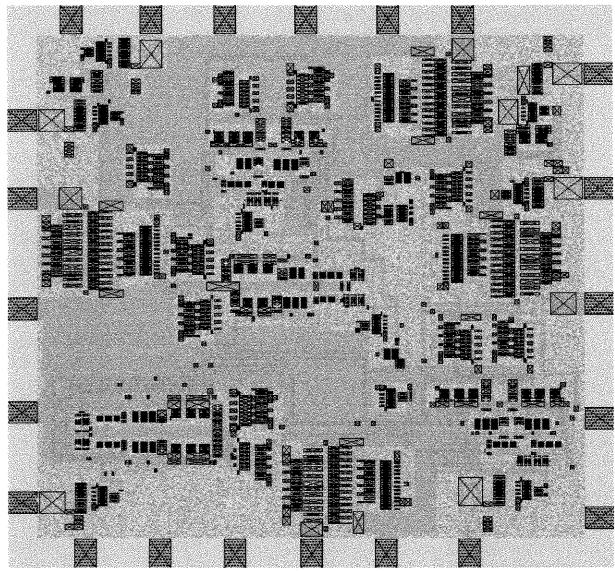

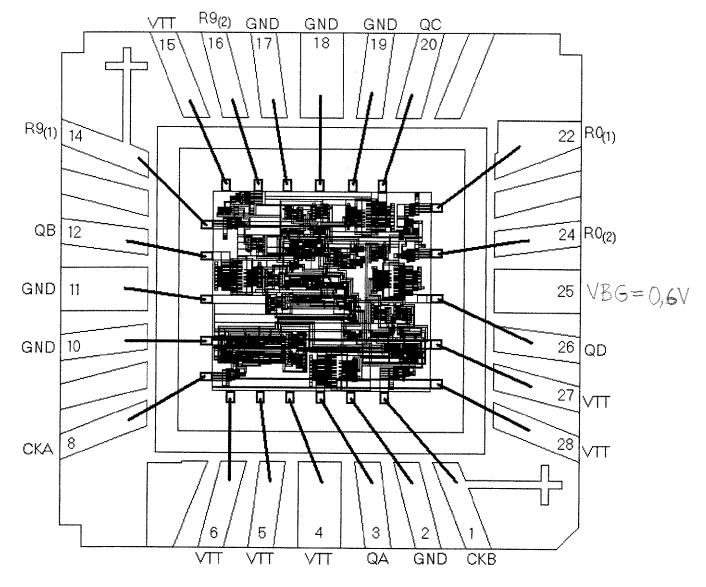

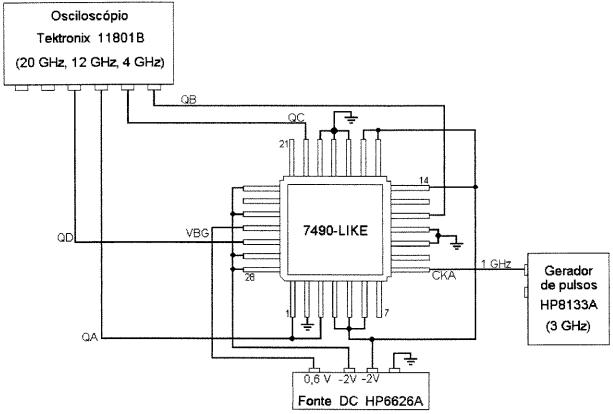

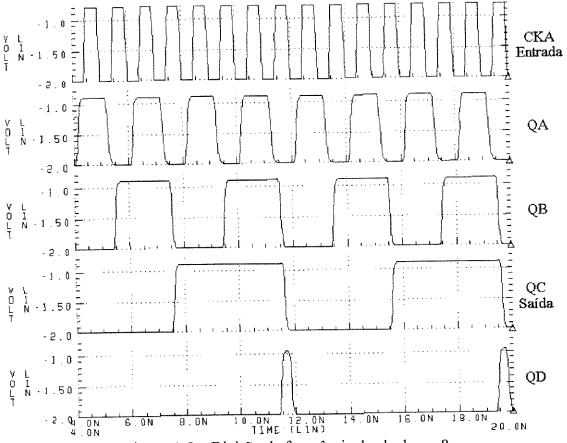

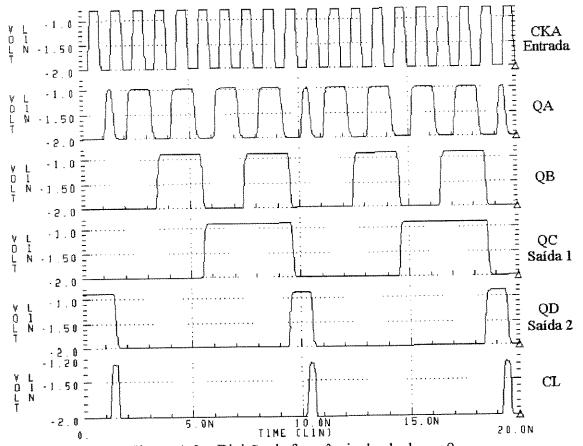

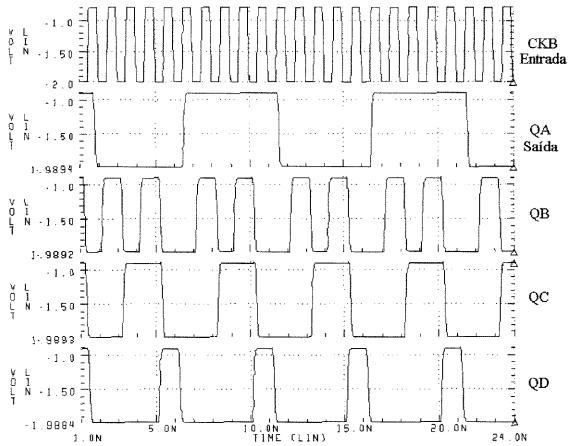

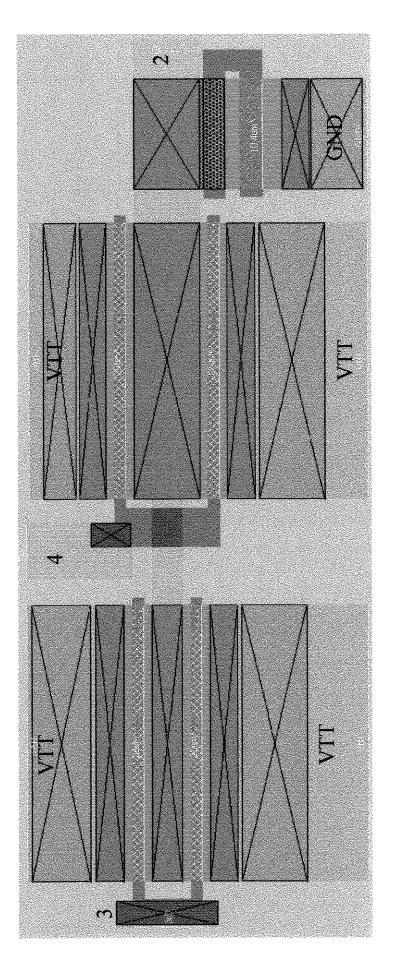

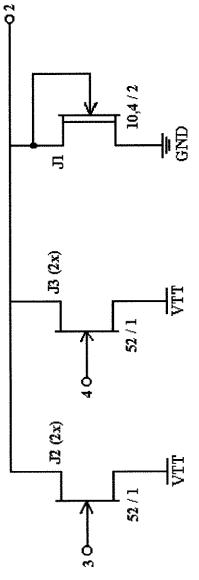

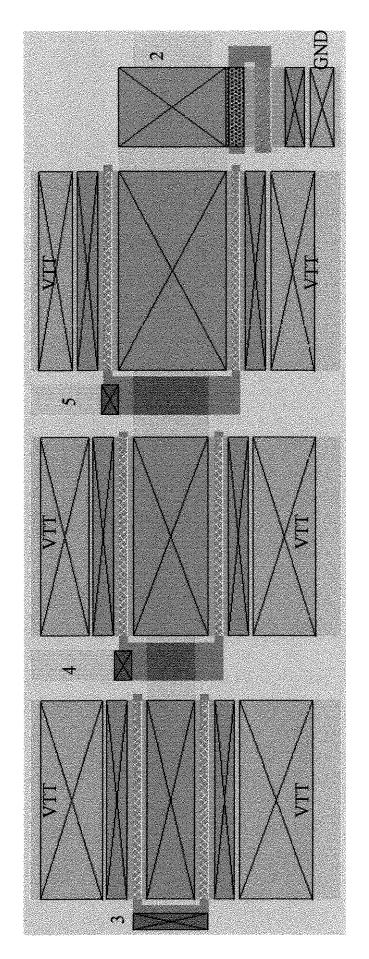

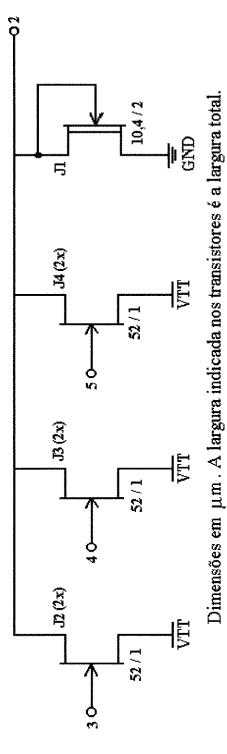

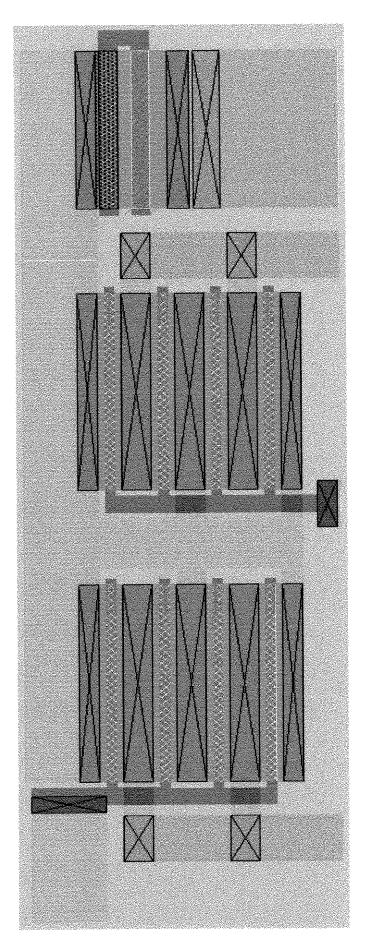

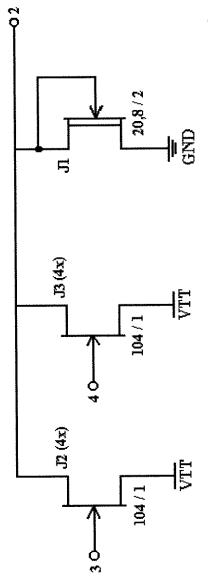

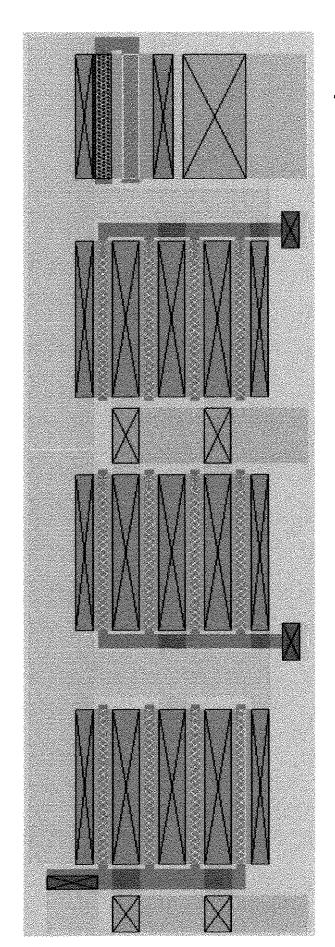

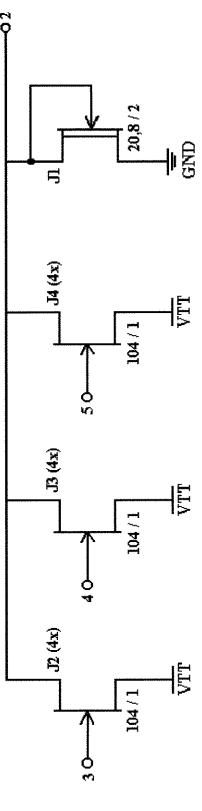

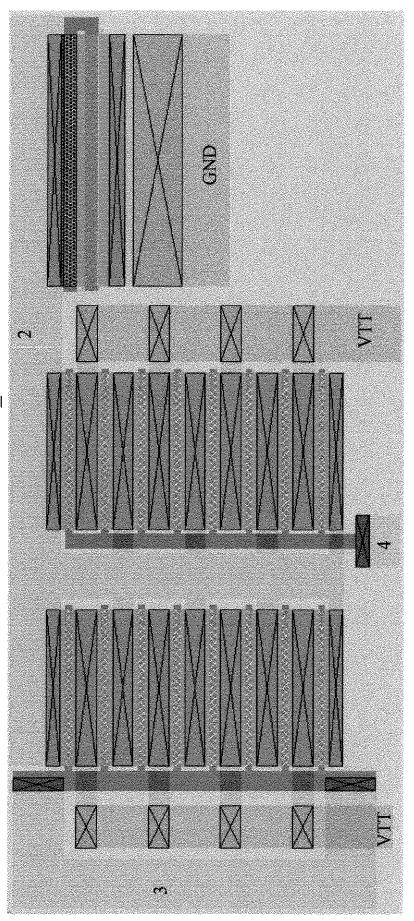

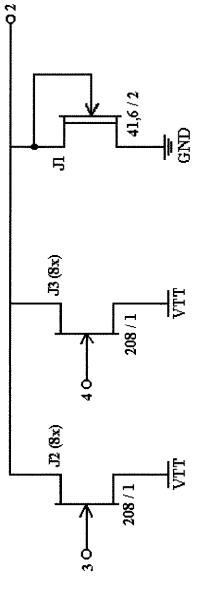

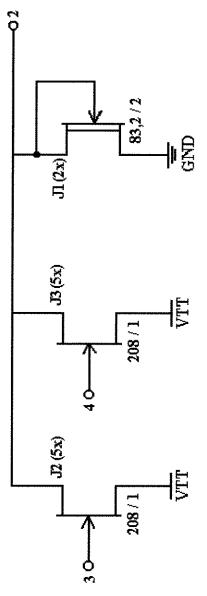

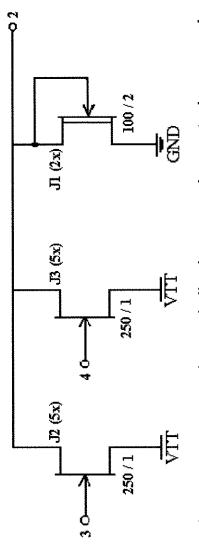

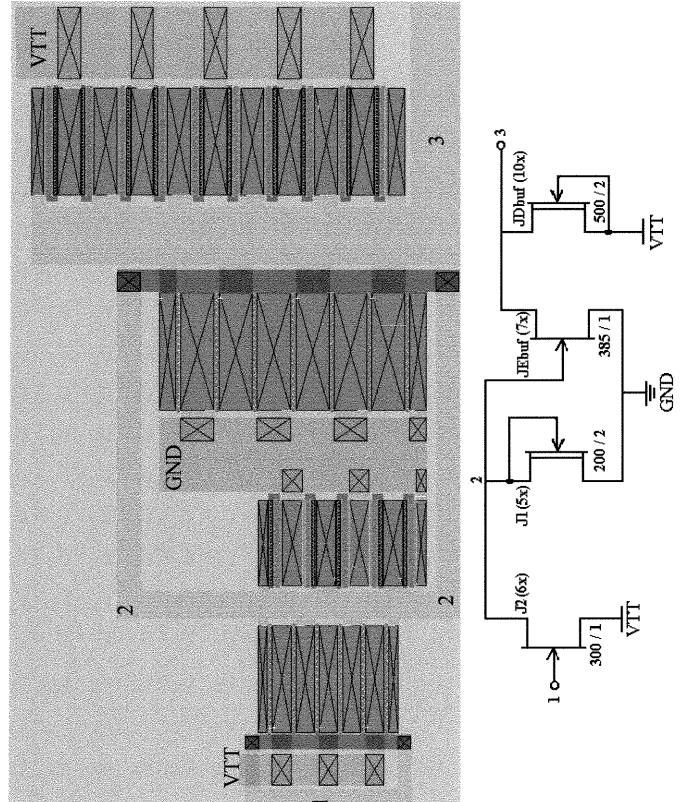

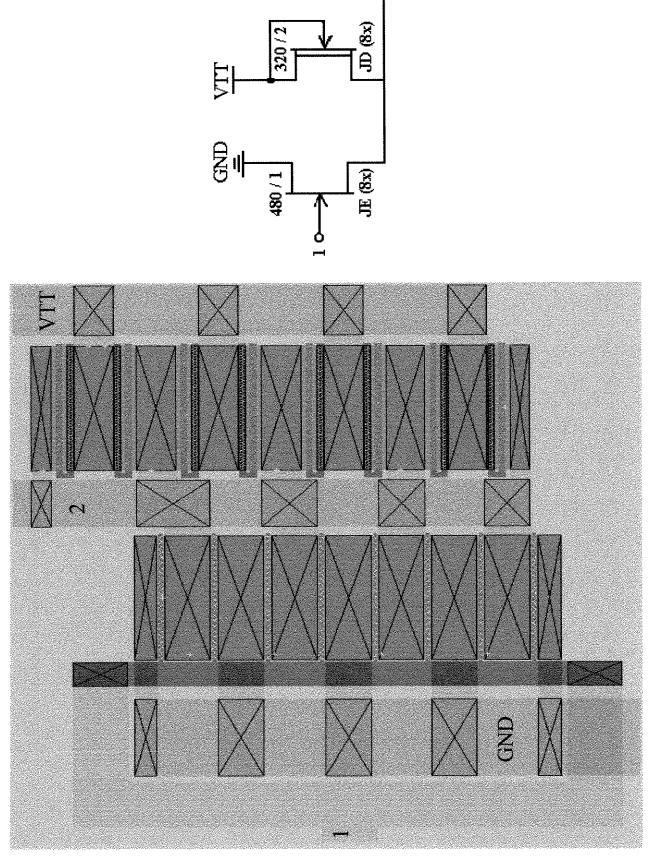

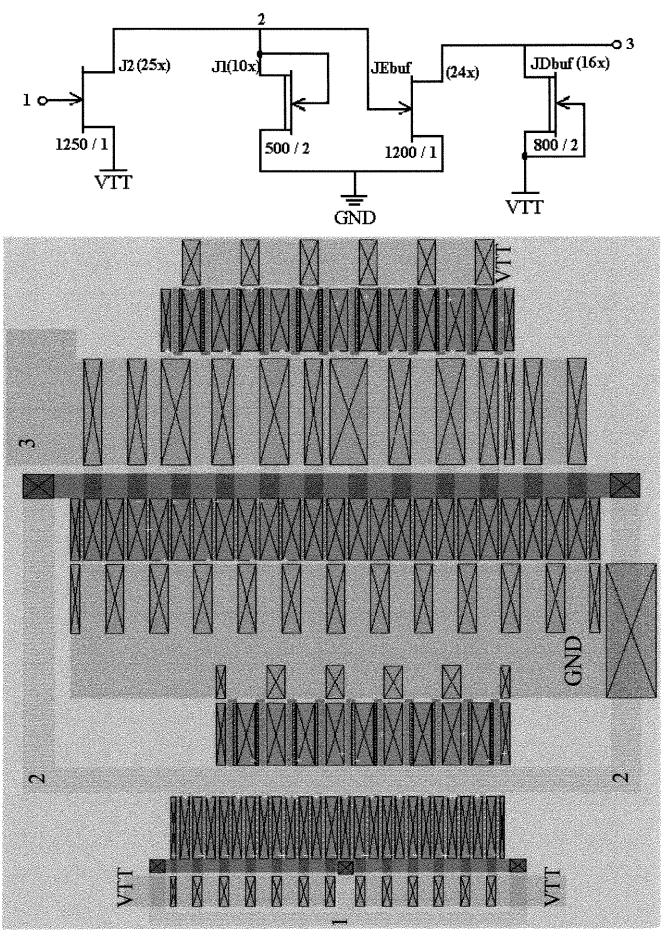

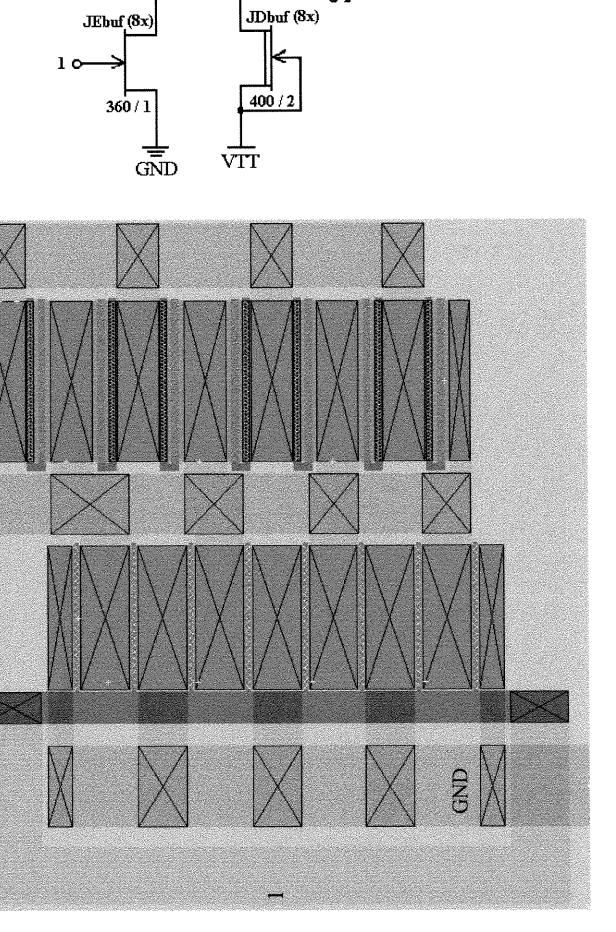

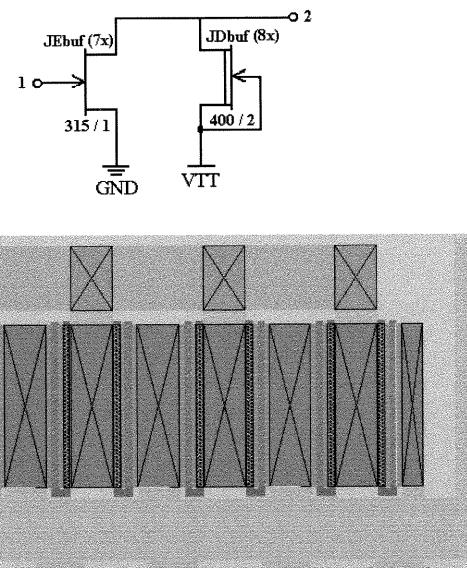

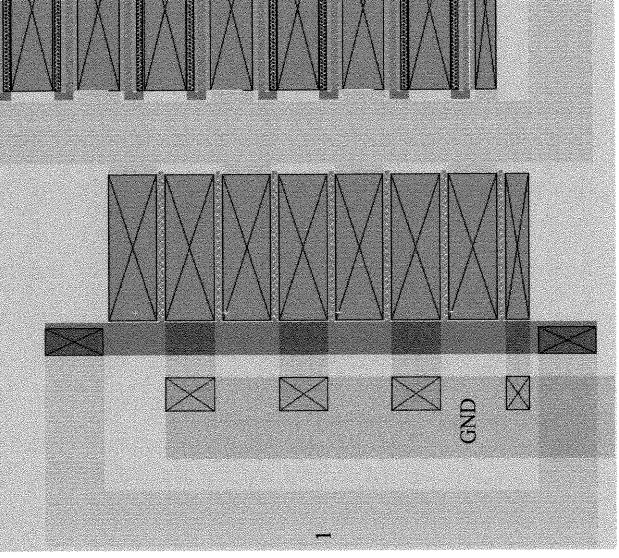

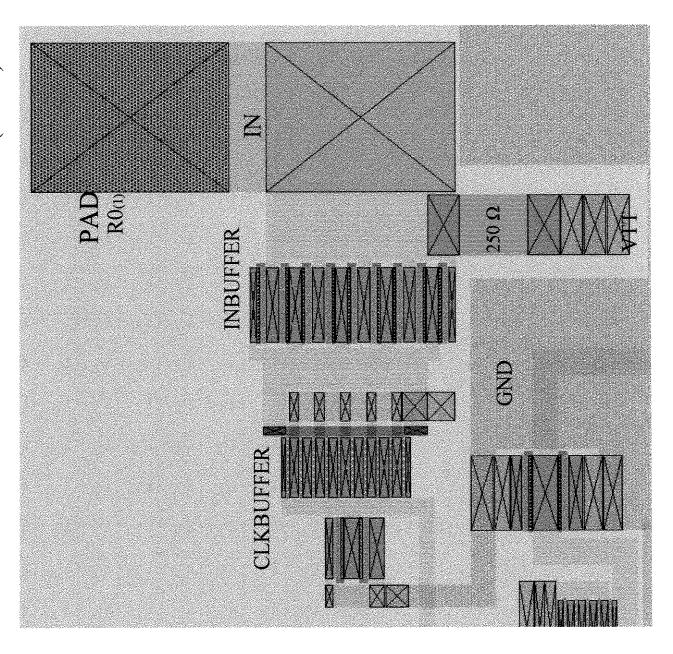

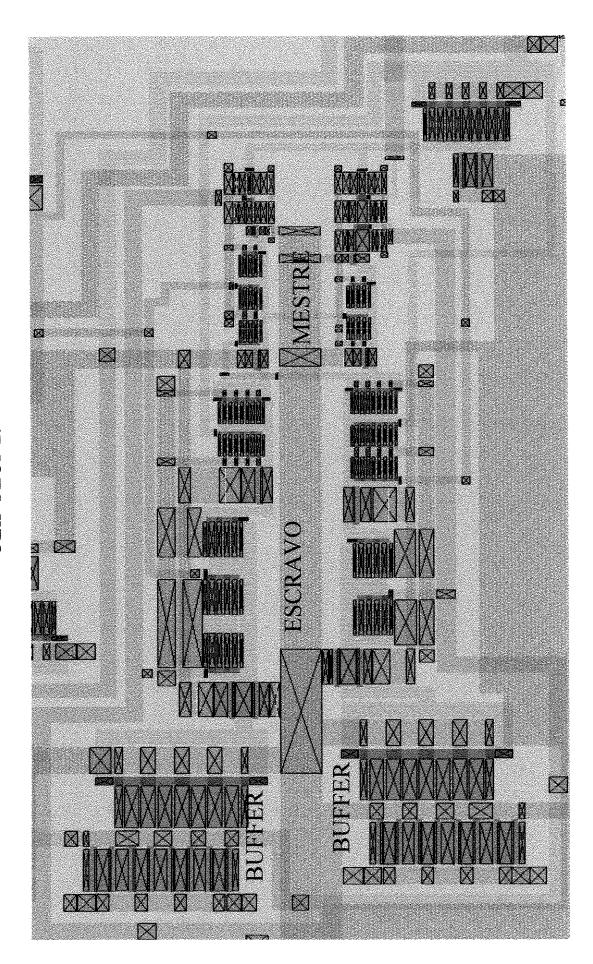

porta lógica), ou para circuitos sensíveis a correntes de fuga, como circuitos de lógica dinâmica ou memórias.  $I_{SUB}$  aumenta exponencialmente com a temperatura, como todas as correntes de fuga, portanto circuitos de baixa potência operando em altas temperaturas têm mais chance de serem afetados.