#### TESE

preparada no

# Laboratório de Eletrônica e Dispositivos - LED da Faculdade de Engenharia Elétrica da UNICAMP

visando a obtenção

#### do Título de Mestre em Engenharia Elétrica FEE/UNICAMP

Especialidade: Eletrônica

por

#### **Marcus Marchesi Martins**

Engenheiro Elétrico

# UM REGULADOR DE TENSÃO CMOS PARA APLICAÇÃO AUTOMOTIVA

| i | R | _ | n | ^ | 9 | F | v | Ω. | r | n | i | n | a | ۸ | ır | 2 | , |

|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|----|---|---|

|   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |    |   |   |

Prof. Dr. José Antonio Siqueira Dias (Orientador) LED/DEMIC/FEE/UNICAMP.

Prof. Dr. Wilmar Bueno de Moraes - LED/DEMIC/FEE/UNICAMP.

Prof. Dr. Galdenoro Botura Jr. - DEE/FEG/UNESP.

|       |          |      |        | \$\$\$\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |           |       |                                         | agroporace car elements |

|-------|----------|------|--------|-------------------------------------------|-----------|-------|-----------------------------------------|-------------------------|

| Este  | exemplar |      | ebrace | in the                                    | ` \       | final | da t                                    | 058                     |

| defan | di di    | Mara | n N    | land                                      | ren.      | Ma    | ntm                                     | 1                       |

|       |          |      |        |                                           |           |       |                                         |                         |

| Julga | don      | 19   | 12     | 92                                        |           | *     |                                         |                         |

|       |          |      | 1      | 1                                         | -5        | Jan   |                                         |                         |

|       |          |      |        | <i>f</i> 7.                               | in a Help |       |                                         |                         |

|       |          |      |        | · ······                                  | A         |       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                         |

USETARS MERCONOTO CONTRAL

| Meus agradecimentos:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A TIVAY COME TO A COME TO THE POLICE OF THE |

| A Vértice Sistemas Integrados, em especial a Armando Gomes da Silva Jr, pelo apoio necessário para que este trabalho se concretizasse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ao meu orientador José Antônio, pela troca de idéias e informações.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Minha especial gratidão a minha esposa e aos meus pais, pelo incentivo constante.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# ÍNDICE

| INTRODUÇÃO                                                                           | 1  |

|--------------------------------------------------------------------------------------|----|

| CAPÍTULO 1 - O Regulador Shunt como Disposistivo de Regulação e Proteção             | 3  |

| 1.1 - O Ambiente Elétrico Automotivo                                                 | 3  |

| 1.2 - Apresentação do Regulador Shunt                                                | 6  |

| CAPÍTULO 2 - Especificações de Projeto                                               | 9  |

| CAPÍTULO 3 - Projeto Elétrico                                                        | 12 |

| 3.1 - A referência de Bandgap                                                        | 12 |

| 3.2 - Multiplicação de V <sub>REF</sub> com Divisor Resistivo                        | 17 |

| 3.2.1 - Definição e Cálculo dos Transistores e Resistores                            | 19 |

| 3.2.2 - Resultados da Simulação Elétrica                                             | 24 |

| 3.2.2.1 - Modelos de Simulação                                                       | 24 |

| 3.2.2.2 - Escolha de MR                                                              | 25 |

| 3.2.2.3 - Simulações do Regulador                                                    | 27 |

| CAPÍTULO 4 - Multiplicação de V <sub>REF</sub> Através da Soma de V <sub>BE</sub> 's | 40 |

| 4.1 - Definição e Cálculo dos Transistores e Resistores                              | 44 |

| 4.2 - O Problema da Estabilidade em Frequência                                       | 48 |

| 4.3 - Resultados da Simulação Elétrica                                               | 51 |

| 4.3.1 - A Dispersão de Processo                                                      | 51 |

| 4.3.2 - Off-set                                                                      | 59 |

| 4.3.3 - A tensão $V_{\rm BAT}$                                                       | 61 |

| 4.3.4 - Os Pulsos de Load-Dump                                                       | 63 |

| 4.3.5 - A Subida de V <sub>BAT</sub>                     | 68 |

|----------------------------------------------------------|----|

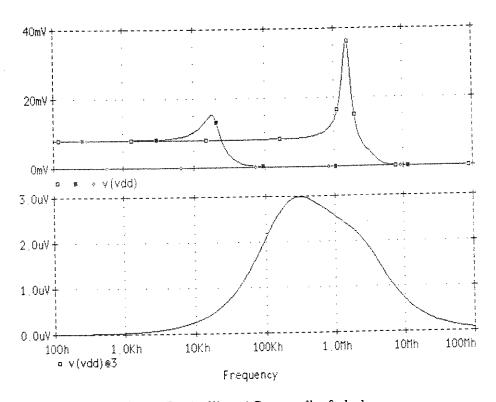

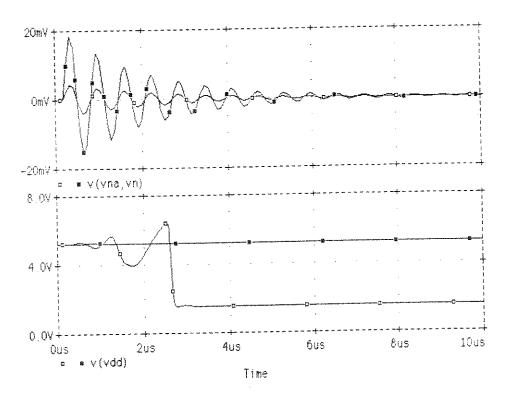

| 4.3.6 - A Simulação da Estabilidade em Frequência        | 69 |

|                                                          |    |

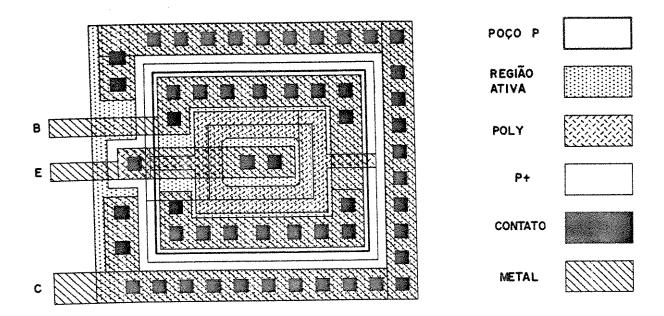

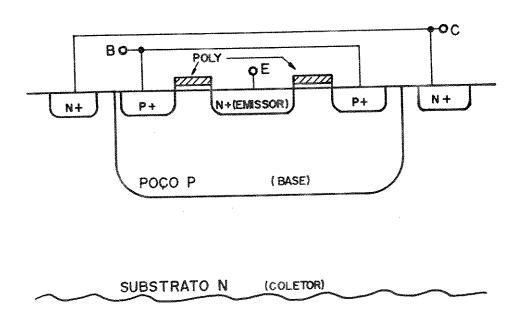

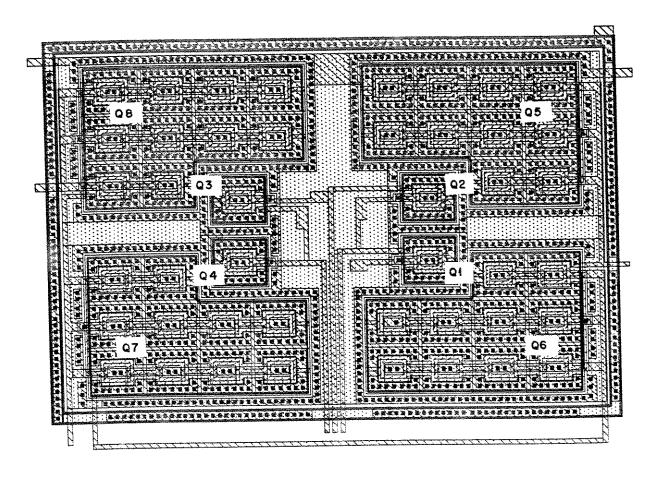

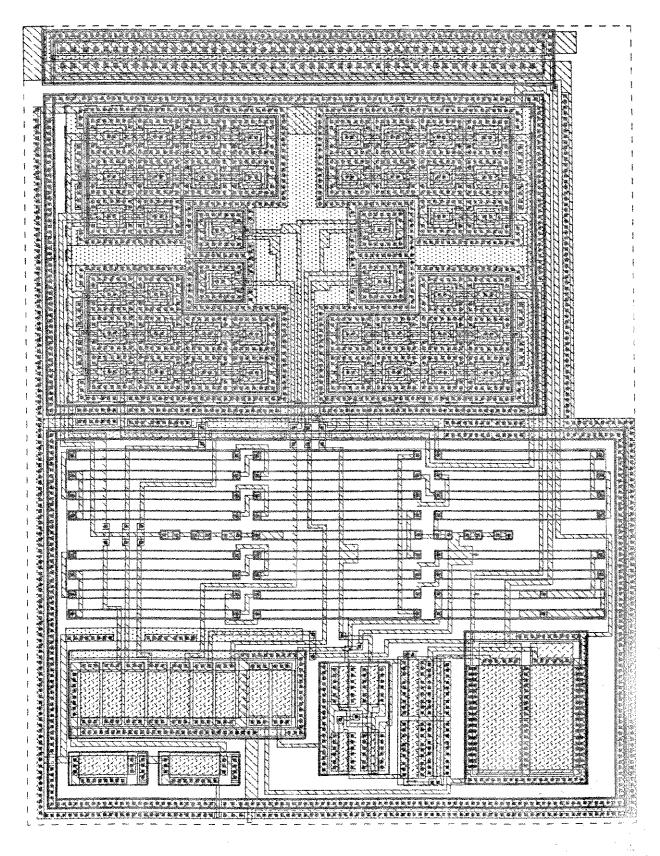

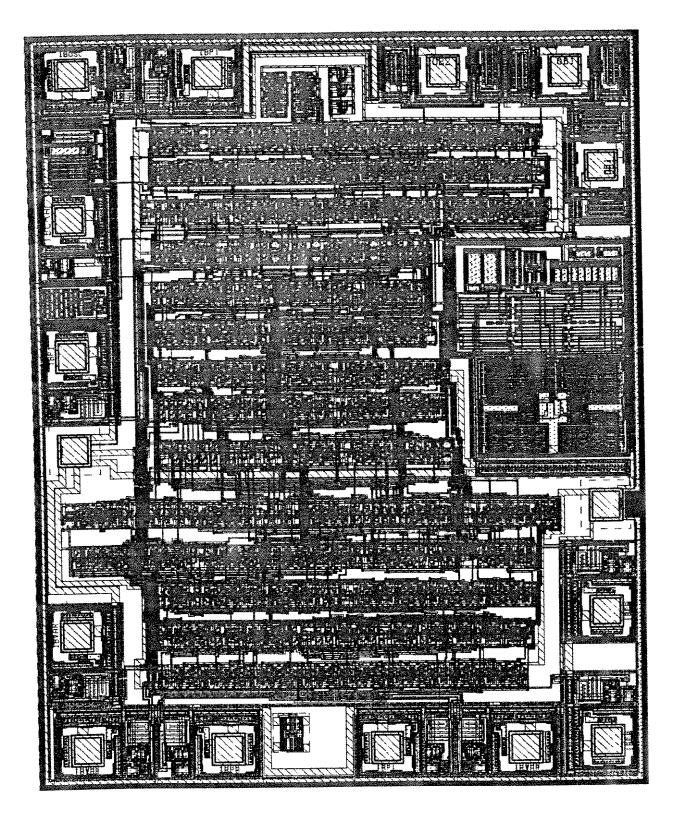

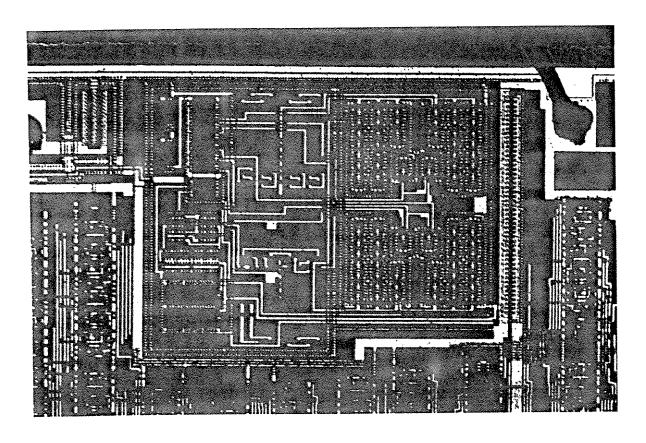

| CAPÍTULO 5 - Layout                                      | 74 |

| 5.1 - Os Transistores Bipolares                          | 74 |

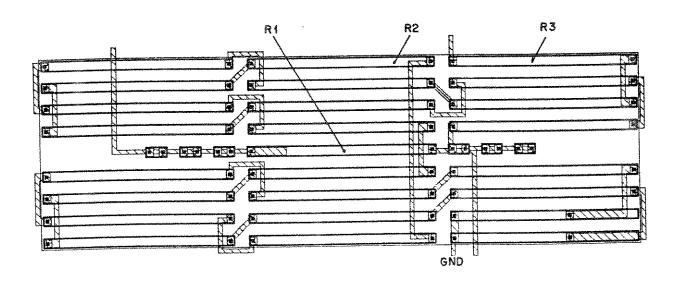

| 5.2 - Os Resistores de P-Well                            | 77 |

| 5.3 - O Layout Global do Regulador CMOS                  | 79 |

|                                                          |    |

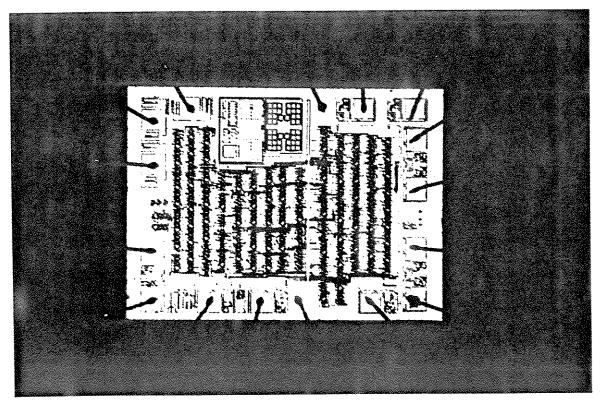

| CAPÍTULO 6 - Resultados Experimentais                    | 84 |

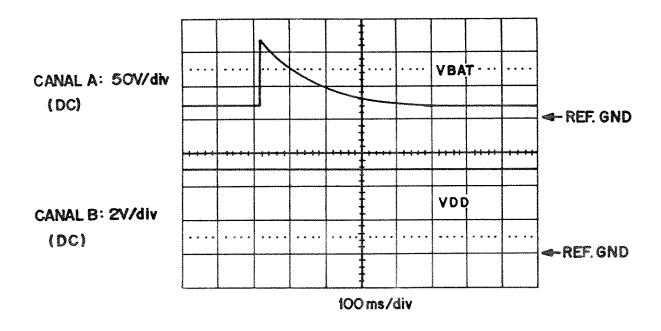

| 6.1 - Variação de $V_{DD}$ em Função da Tensão $V_{BAT}$ | 85 |

| $6.2$ - Variação de $V_{\rm DD}$ com a Temperatura       | 86 |

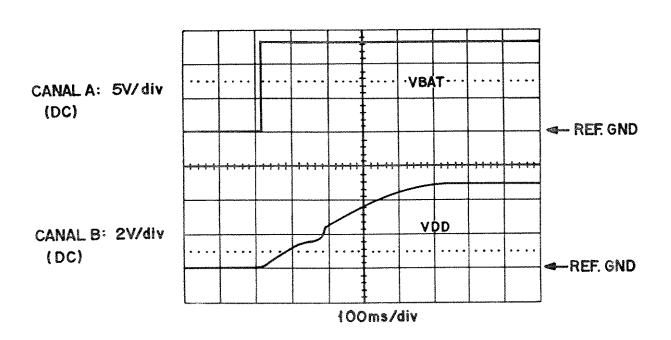

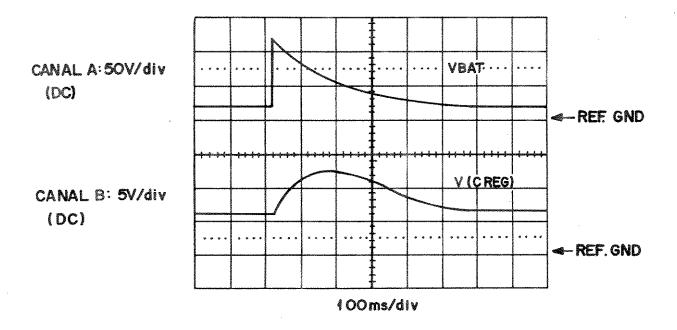

| $6.3$ - Subida da Tensão $V_{ m DD}$                     | 87 |

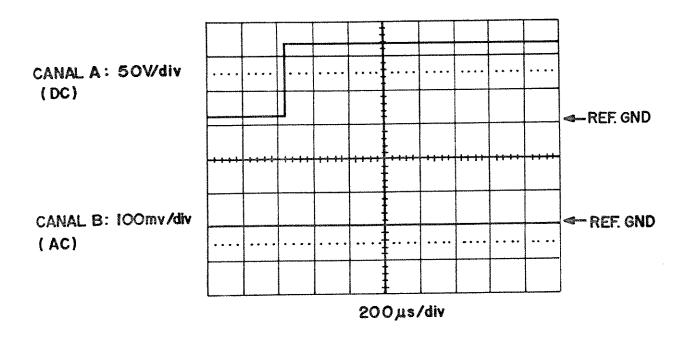

| 6.4 - Load Dump                                          | 87 |

|                                                          |    |

| CONCLUSÃO                                                | 90 |

|                                                          |    |

| REFERÊNCIAS                                              | 91 |

## INTRODUÇÃO

Segundo alguns analistas técnicos, a eletrônica embarcada (automotiva) promete ser o segmento da indústria eletrônica que sofrerá o maior crescimento nos próximos anos. Os novos padrões de controle de emissão de poluentes, segurança e economia de combustível estão impulsionando os fabricantes para uma solução eletrônica, capaz de aliar baixos custos com maior desempenho, funcionalidade, integração, conforto e precisão [1]-[4].

A eletrônica já é parte integrante dos veículos atuais. Alarmes, sistemas de freio ABS, computadores de bordo, injeção eletrônica, piloto automático e a suspensão ativa computadorizada são apenas alguns exemplos, sem falar nos sofisticados sistemas de audio de alta fidelidade e imunidade a ruídos. Hoje estão em andamento projetos de substituição da cabeação elétrica por circuitos multiplexados utilizando fibra óptica, o que significará uma grande mudança na filosofia dos sistemas e dispositivos elétricos envolvidos. Também, em fase de testes, encontramos os sistemas de monitoramento de tráfego (que interligam usuários de veículos a uma central de informações), que são particularmente interessantes em grandes centros onde a ocorrência dos congestionamentos de trânsito é muito comum.

Apesar desse grande desenvolvimento e aperfeiçoamento da eletrônica automotiva e das vantagens e facilidades introduzidas, devemos salientar que o ambiente automotivo é um dos mais agressivos para o funcionamento dos dispositivos eletrônicos, especialmente para os circuitos integrados. Estes podem estar sujeitos a condições extremas de humidade e vibração mecânica, temperaturas de -40 a +120°C, transientes de tensão com picos que podem ultrapassar ± 100V, tensão de alimentação que pode variar de 6 a 18V, além de outras condições de stress de efeitos também danosos, conforme descreveremos mais adiante.

Dentre as tecnologias de circuito integrado utilizadas na eletrônica embarcada atualmente, a tecnologia MOS tem apresentado grande indice de crescimento, devido a sua

alta velocidade de processamento aliada ao baixo consumo de potência, quesito imprescindível nos equipamentos automotivos. Entretanto os circuitos integrados MOS são os mais suceptíveis às avarias provocadas pelos transientes de tensão e descargas eletrostáticas, necessitando esquemas especiais de proteção.

O regulador de tensão CMOS aqui apresentado vem sugerir uma solução bastante interessante, no que se refere à proteção e ao fornecimento de uma tensão de alimentação estabilizada, para um circuito integrado CMOS digital, de aplicação automotiva. Ele regula e protege a própria alimentação  $V_{DD}$  do integrado, razão pela qual também o designamos de Regulador Shunt, uma vez que ele se situa em paralelo com a alimentação. A descrição do seu projeto e implementação é objetivo deste trabalho.

# CAPÍTULO 1

# O REGULADOR SHUNT COMO DISPOSITIVO DE REGULAÇÃO E PROTEÇÃO

#### 1.1- O AMBIENTE ELÉTRICO AUTOMOTIVO

A alimentação dos circuitos e módulos eletrônicos dentro de um veículo é normalmente fornecida pela bateria, através de longos fios que podem apresentar significativa indutância série. Além disto, esses fios podem estar ligados a diversas cargas indutivas de alta corrente, de tal forma que, se houver um chaveamento dessas correntes, ocorrerão fortes transientes de tensão na linha, o que pode causar a destruição dos componentes que não tiverem a devida proteção [5]-[7].

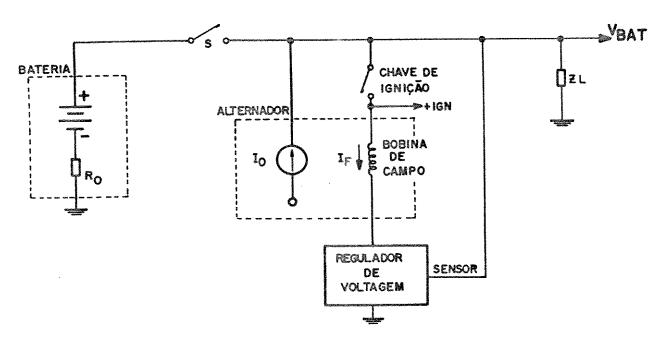

Outra fonte de possíveis transientes é o alternador responsável pela carga da bateria. O alternador girando numa certa rotação pode ser representado, de maneira simplificada, por uma fonte de corrente dependente  $I_O$ , proporcional a sua corrente de campo  $I_F$ , conforme figura a seguir.

Fig. 1.1 - O sistema elétrico de carga da bateria

Quando a bateria está ligada ao sistema (chave S fechada), um transiente negativo de tensão de alta amplitude pode ocorrer no fio da ignição quando a mesma é desligada, devido ao decaimento da corrente através da bobina de campo e das outras cargas indutivas ligadas ao fio da ignição. Este transiente negativo é conhecido como *field decay* e pode atingir tensões negativas de até 80V e duração de 100ms.

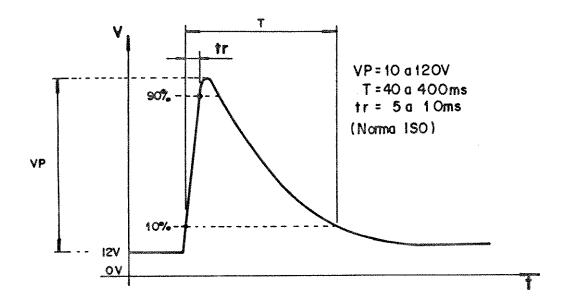

Por outro lado, a ocorrência de pulsos de tensão positiva também é comum. Dentre eles existe um que recebe particular importância, não só pelo seu elevado valor de tensão, que pode chegar a 100V, mas pela sua duração, que pode atingir até 400ms. Este pulso positivo, conhecido como *load dump*, ocorre no fio  $V_{BAT}$  quando a bateria, que apresenta baixa impedância, é desconectada do sistema (por exemplo abrindo a chave S) enquanto o alternador está gerando corrente. Desde que a mudança na impedância vista pelo fio  $V_{BAT}$  pode ser rápida e significante (variando da impedância  $R_O$  da bateria para impedância de carga  $Z_L$ ), e como a corrente de saída  $I_O$  do alternador permanece praticamente constante durante esta mudança de impedância, pois a corrente  $I_F$  não pode mudar instantaneamente, a voltagem  $V_{BAT}$  sofre um brusco aumento, até atingir a condição de tensão de saída de circuito aberto do alternador.

A amplitude do load dump depende do nível de excitação da bobina de campo do alternador e da diferença entre  $R_o$  e  $Z_L$ . Será máxima quando o alternador estiver a plena carga (bateria totalmente descarregada) e todos os acessórios (cargas) estiverem desligados no momento em que a bateria é desconectada.

Além dos pulsos de *load dump* e *field decay*, existem outros transientes automotivos [8]-[11] que podem ter picos de tensão acima de ± 200V. Porém, são pulsos de pequena duração, portanto de baixa energia, que no nosso caso não representam perigo como os anteriores, pois são passíveis de filtragem.

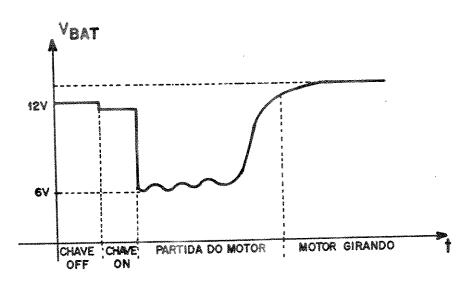

Outra grave situação ocorre na partida do motor, principalmente quando o motor está frio [5],[7]. Uma partida em condições de baixa temperatura pode drenar uma corrente de até 100A da bateria, devido ao alto torque exigido nestas condições, o que pode provocar uma queda momentânea da tensão da bateria, do seu valor nominal de 12V, para valores próximos de 6V. A figura 2 ilustra o que ocorre com essa tensão numa condição de partida a frio.

Fig. 1.2 - Tensão da bateria na partida a frio

A própria alimentação nominal  $V_{BAT}$  de 12V está mais associada ao valor apresentado pela bateria quando em repouso. Em operações típicas, com a bateria ligada ao circuito, o sistema de carga regula a saída do alternador para fornecer tensão suficiente para manter a bateria carregada, sob várias condições de temperatura e carga. A tensão  $V_{BAT}$  pode, então,

assumir valores de 12V a valores acima de 15V. Nominalmente, para temperatura e carga típicas, esta tensão está situada próxima de 13,8V.

Em determinadas condições de temperatura muito baixa, principalmente em países da Europa e América do Norte, é comum a utilização de duas baterias em série para estabelecer a partida do motor. Nestas condições, expõe-se os dispositivos eletrônicos à uma tensão de alimentação de 20 a 24V. Por outro lado, uma conexão reversa da bateria é outra situação possível de ocorrer, o que pode impor uma tensão de até -13V DC aos circuitos do veículo.

Todas estas situações de agressão aos componentes elétricos e eletrônicos devem ser levadas em consideração no momento do projeto de tais dispositivos, tendo-se em vista que muitas vezes o conceito de proteção significa a certeza de um perfeito funcionamento não só depois, mas também durante a ocorrência do stress elétrico.

#### 1.2- APRESENTAÇÃO DO REGULADOR SHUNT

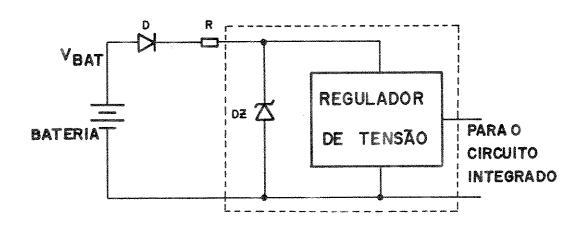

Uma maneira de se realizar a proteção de um circuito integrado contra os transientes de tensão e contra a inversão de polaridade da bateria é apresentado na figura 1.3 [6],[7].

Fig. 1.3 - O circuito de proteção convencional

O diodo D faz a proteção contra os picos negativos e inversão da polaridade da bateria, ao passo que o diodo zener limita os picos positivos da tensão a níveis suportáveis pelo regulador, de tal forma que o CI possa receber uma alimentação limpa e regulada.

O regulador de tensão CMOS proposto aqui seria o equivalente paralelo do diodo zener DZ mais o regulador, conforme destaque em tracejado. Ele, por si só, gera uma alimentação estável e protegida contra os surtos de tensão.

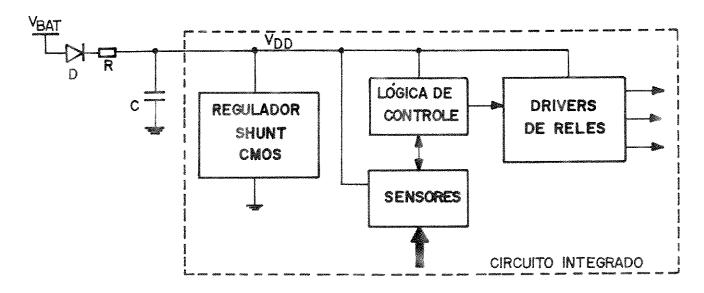

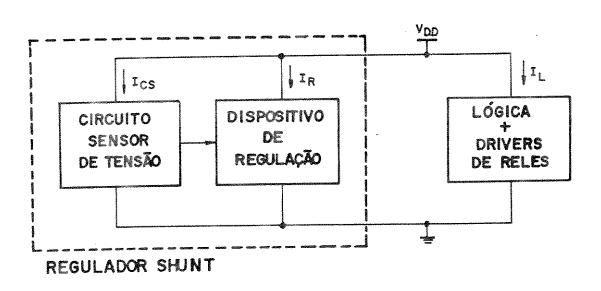

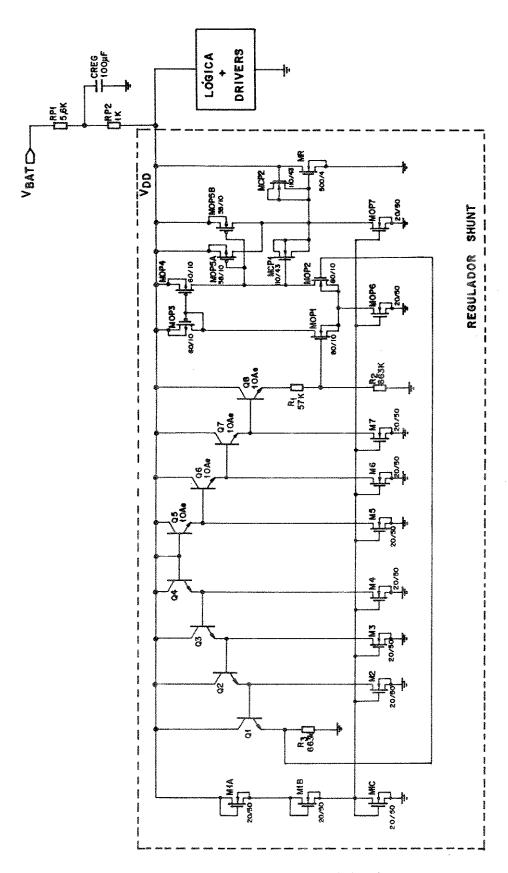

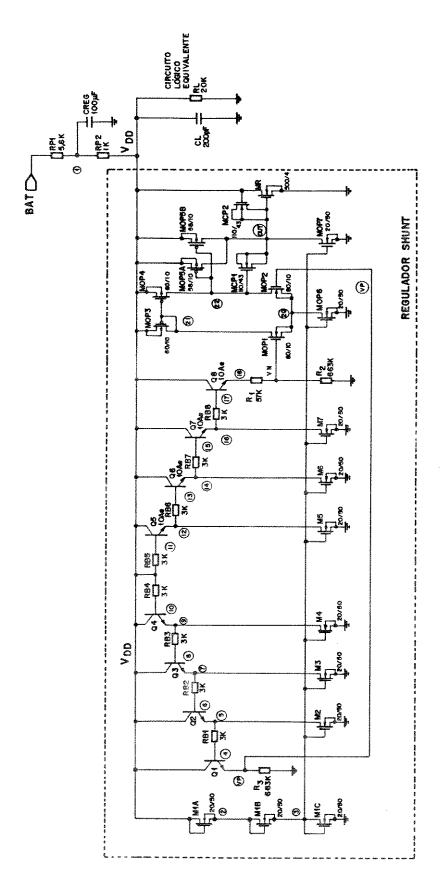

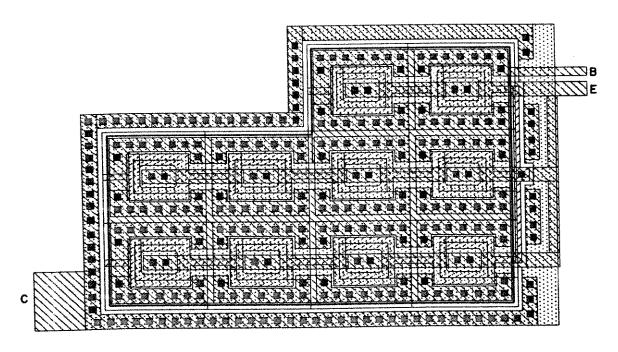

O circuito integrado automotivo, para o qual foi desenvolvido este regulador, é um chip que controla o acionamento dos motores elétricos das travas das portas do veículo. Na figura 1.4 temos um diagrama em blocos simplificado mostrando o regulador CMOS dentro do CI e os componentes externos ligados a ele. Podemos observar que o bloco do regulador shunt está em paralelo com  $V_{DD}$ , substituindo o conjunto zener mais regulador da figura 1.3.

O capacitor C faz parte do processo de filtragem do ruído (sempre presente no ambiente automotivo) e dos transientes de alta frequência e baixa energia. O resistor R também faz parte do filtro, além de limitar a corrente pelo chip.

Fig. 1.4 - Diagrama em blocos simplificado do chip

Em alguns casos, onde a tensão  $V_{CC}$  ( $V_{DD}$ ) do circuito deve ser alta, a queda de tensão provocada pelo diodo D e pelo resistor R pode comprometer a alimentação do circuito, principalmente nas partidas a frio quando a tensão  $V_{BAT}$ , como já dissemos, cai a valores bem críticos. No nosso caso esse problema é minimizado, pois a tensão de alimentação a ser gerada é relativamente baixa (+5V).

# CAPÍTULO 2

## ESPECIFICAÇÕES DE PROJETO

As especificações do regulador de tensão estão diretamente relacionadas com as especificações globais do circuito integrado. O chip foi projetado utilizando uma tecnologia CMOS, com p-well, 3µm, single poly e single metal, escolhida de acordo com os requisitos dos circuitos da parte digital.

Para maior clareza, podemos dividir o regulador shunt da figura 1.4 em 2 partes, conforme apresentado abaixo.

Fig. 2.1 - Circuito sensor e dispositivo de regulação

As especificações do chip determinam, no caso tipico, uma tensão de alimentação de 5V e uma corrente DC de 1.3mA. Para satisfazer essas condições, bem como as condições

de consumo da parte lógica e circuitos de drivers de relés, ficou estabelecido que a corrente  $I_{CS}$  máxima, do circuito sensor da tensão  $V_{DD}$ , é 180 $\mu$ A, já considerando as dispersões de processo, tolerâncias de componentes externos (resistores de 5%) e variações de  $V_{BAT}$  e temperatura. Em termos de temperatura de junção, o chip pode trabalhar de -35°C a +95°C.

Este regulador deve manter a tensão  $V_{DD}$  dentro de 5V  $\pm$  10%. Para isto, o dispositivo de regulação trabalha com corrente de acomodação  $I_R$  de 0 a valores próximos de 15mA (situação de *load dump*), drenando menos ou mais corrente, conforme a necessidade do circuito de carga (lógica + drivers).

Resumindo, podemos apresentar o seguinte quadro de especificações para o regulador shunt CMOS:

| TEMPERATURA                              | -35°C a +95°C                                                                    |

|------------------------------------------|----------------------------------------------------------------------------------|

| REGULAÇÃO DE $V_{\scriptscriptstyle DD}$ | 5V ± 10%                                                                         |

| $I_{CS}$ MÁXIMO                          | 180μΑ<br>(excluindo dispos. de regulação)                                        |

| $I_R$ ( DISPOSITIVO DE REGUL.)           | 0 a 15mA                                                                         |

| $V_{\it BAT}$                            | 8 a 18V (normal) 24V (dupla bateria) 6V (partida a frio) - 13V (bateria reversa) |

| DISPERSÕES DE PROCESSO                   | Conforme dados da foundry                                                        |

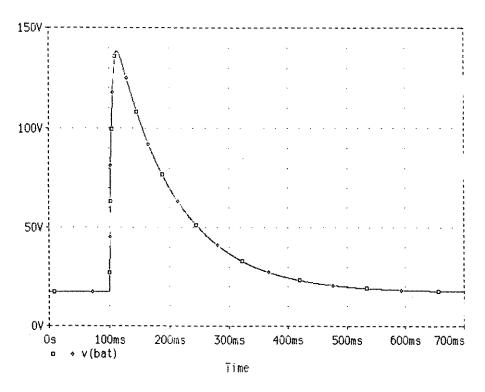

Além dessas, existem as especificações de transientes que o regulador deve suportar. Dentre estas, citadas no capítulo 1, o pulso de *load dump*, em particular, é o mais crítico. Os pulsos de *field decay* são barrados pelo diodo (vide fig. 1.4) e os outros pulsos de alta frequência são filtrados pelo circuito RC externo.

Segundo a norma ISO [10], o pulso de *load dump* pode atingir até 120V, embora para maioria das especificações das montadoras este pulso tenha valor máximo de 85V [9]. Sua forma de onda pode ser vista na figura a seguir.

Fig. 2.2 - O pulso de load dump

Sabendo que a especificação de  $V_{DD}$  é de 5V  $\pm$  10%, se levarmos em conta as dispersões e incertezas a respeito do processo, devemos então trabalhar com uma estabilidade de temperatura da ordem de 100ppm/ $^{\circ}$ C, conforme veremos mais adiante.

## CAPÍTULO 3

#### PROJETO ELÉTRICO

Aparentemente uma regulação de 5V ± 10%, apesar das condições, não é um problema que exija grandes artimanhas de projeto. No entanto, o processo utilizado é um processo CMOS otimizado para aplicações digitais. A caracterização do processo e modelamento dos dispositivos visaram principalmente o seu funcionamento nas regiões de corte e saturação, tendo-se pouca informação a respeito dos coeficientes térmicos e dispersões dos resistores, componentes estes que necessariamente fazem parte do circuito de um regulador. Além disso, considerando a alimentação de 5V, não existe nenhuma opção para utilização de diodos zener.

Concluímos então que, como não dispomos de uma boa informação a respeito das dispersões de processo, resta-nos fazer um projeto que dependa o mínimo dos parâmetros absolutos de processo e que seja o mais estável possível com relação à temperatura, sob pena de incorrermos numa soma de erros.

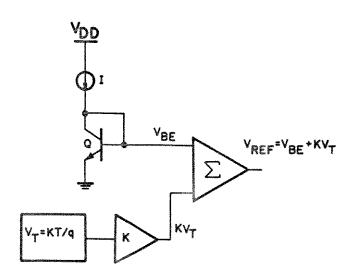

#### 3.1 - A REFERÊNCIA DE BANDGAP

Dentre as opcões disponíveis, decidimos utilizar uma célula de bandgap, que apresenta uma alta estabilidade em temperatura, e adapta-la de forma a gerar uma tensão de referência que coincidisse com a própria tensão de  $V_{\rm DD}$ .

O princípio da referência de bandgap é ilustrado na figura 3.1 [12],[13]. A tensão  $V_{BE}$  possui um coeficiente negativo de temperatura (aproximadamente -2.2mV/°C a 27°C), enquanto que a tensão  $V_T = K.T/q$  possui um coeficiente positivo (próximo de 0.085mV/°C a 27°C).

Fig. 3.1 - Princípio da referência de bandgap

Se multiplicarmos a tensão  $V_T$  por K e somarmos com a tensão de  $V_{BE}$  obteremos

$$V_{REF} = V_{BE} + K V_T \tag{3.1}$$

Utilizando um valor adequado de K, podemos compensar as diferenças nos valores absolutos dos coeficientes térmicos de  $V_{BE}$  e  $V_T$ , de tal forma a obtermos um coeficiente térmico próximo de zero para a tensão  $V_{REF}$ .

A geração da tensão PTAT  $(K.V_T)$  pode ser implementada de duas maneiras clássicas. A primeira consiste na diferença entre as tensões de  $V_{BE}$  de dois transistores NPN distintos, ao passo que a segunda seria a obtenção através da diferença entre as tensões gate-fonte de dois transistores MOS. Esta segunda alternativa implica na operação dos transistores MOS no modo de inversão fraca [19],[20].

Considerando as dispersões de processo de difusão e a grande faixa de variação da temperatura, torna-se dificil garantir que o transistor MOS irá permanecer operando na região de inversão fraca, em todas as situações possíveis. Além disso, o modelamento dos transistores MOS está voltado mais para a aplicação no modo digital (operação nas regiões de corte e saturação). O projeto baseado nesta segunda alternativa poderia levar a graves erros de simulação, distanciando os valores teóricos simulados dos valores práticos a serem obtidos.

Por esta razão optamos por gerar a tensão de  $K.V_T$  através de transistores bipolares. Mesmo possuindo pouca informação a cerca do modelo de simulação do transistor NPN, ainda assim o erro seria menor que no caso de utilizarmos transistores MOS na inversão fraca, pois as equações que regem o comportamento do transistor bipolar apresentam caráter universal.

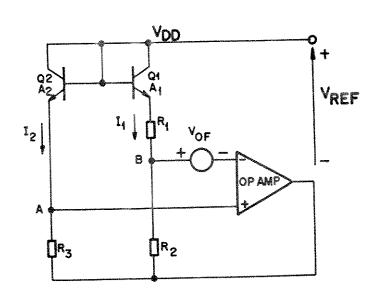

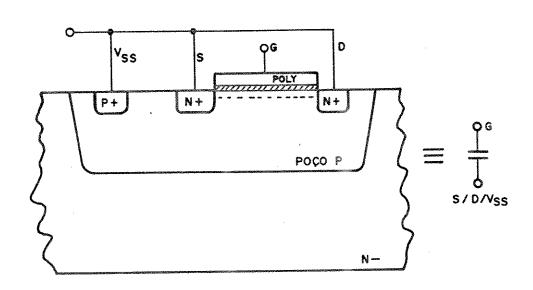

Fig. 3.2 - Célula de bandgap num processo CMOS com poço P

Uma referência de bandgap CMOS, num processo com poço P, onde a tensão  $K.V_T$  é gerada pela diferença entre duas tensões de  $V_{BE}$ , é ilustrado na figura 3.2 [12]. Nesse processo o transistor bipolar utilizado é o transistor NPN vertical, formado pelo substrato N (coletor), poço P (base) e implante N (emissor). Como o substrato está conectado à tensão mais positiva, ou seja,  $V_{DD}$ , então obrigatoriamente todos os coletores estão ligados a  $V_{DD}$ .

A tensão de off-set,  $V_{OF}$ , foi incluida para que possamos considerar o op-amp ideal. Se os transistores Q1 e Q2 têm área de emissor  $A_I$  e  $A_2$ , respectivamente, e assumindo  $V_{OF}$  inicialmente igual a zero, temos que a tensão sobre  $R_1$  vale :

$$V_{R1} = V_{BE2} - V_{BE1} = V_T \ln \left( \frac{J_2}{J_{S2}} \right) - V_T \ln \left( \frac{J_1}{J_{S1}} \right)$$

(3.2)

$$V_{R1} = V_T \ln \left( \frac{I_2}{I_1} \frac{A_1}{A_2} \right) \tag{3.3}$$

onde  $J_1$  e  $J_2$  são as densidades de corrente de coletor de Q1 e Q2 enquanto que  $J_{SI}$  e  $J_{S2}$  são as respectivas densidades de corrente de saturação.

O amplificador operacional força a mesma tensão nos pontos A e B, de tal forma que:

$$I_1 R_2 = I_2 R_3$$

(3.4)

A tensão de referência  $V_{REF}$  pode, então, ser escrita como:

$$V_{REF} = V_{BE2} + I_1 R_2 \tag{3.5}$$

Utilizando (3.3) e (3.4) chegamos a:

$$V_{REF} = V_{BE2} + \frac{R_2}{R_1} V_T \ln \left( \frac{R_2}{R_3} \frac{A_1}{A_2} \right)$$

(3.6)

Se compararmos (3.6) com (3.1), veremos que a constante K vale:

$$K = \frac{R_2}{R_1} \ln \left( \frac{R_2}{R_3} \frac{A_1}{A_2} \right) \tag{3.7}$$

Através do ajuste de K, podemos fazer com que que a tensão  $V_{\it REF}$  tenha uma coeficiente de temperatura igual a zero numa determinada temperatura  $T_{\it o}$ , ou seja, os valores

absolutos dos coeficientes térmicos de  $V_{BE2}$  e  $K.V_T$  sejam iguais. Feito este ajuste vemos que a tensão  $V_{REF}$ , nesta temperatura  $T_0$ , deve valer [12],[13]:

$$V_{REF}|_{T_0} = VGO + V_{TO} (\gamma - \alpha)$$

(3.8)

onde VGO é a tensão de bandgap do silício (1,205V conforme literatura),  $V_{T0}$  a tensão  $V_{T}$  na temperatura  $T_{0}$ ,  $\gamma$  é um coeficiente térmico relacionado com a tensão de  $V_{BE}$  e possui um valor típico de 3,2 e  $\alpha$  é um coeficiente térmico relacionado com a densidade de corrente na junção de  $V_{BE}$ , e no nosso caso, conforme veremos, tem valor entre 0 e -1.

Portanto, para temperaturas próximas da temperatura ambiente ( $T_0$  = 300K), onde  $V_{T0}$  = 26mV, encontramos que  $V_{REF} \approx 1,3$ V. Considerando este valor e utilizando (3.6) e (3.7) podemos escrever:

$$K = \frac{V_{REF} - V_{BE2}}{V_T} = \frac{1, 3V - V_{BE2O}}{V_{TO}}$$

(3.9)

onde  $V_{\it BE2o}$  é o valor de  $V_{\it BE2}$  em  $T_{\it 0}$ .

Através desta expressão calculamos K e portanto, utilizando (3.7), podemos encontrar os valores adequados de  $R_1$ ,  $R_2$ ,  $R_3$ ,  $A_1$  e  $A_2$ , fixando algumas variáveis e calculando as outras.

Se levarmos em conta a tensão de off-set do op-amp  $(V_{OF})$  a expressão (3.6) se torna:

$$V_{REF} = V_{BE2} + \frac{R_2}{R_1} V_T \ln \left( \frac{R_2}{R_3} \frac{A_1}{A_2} \right) - \left( 1 + \frac{R_2}{R_1} \right) V_{OF} + \frac{R_2}{R_1} V_T \ln \left( 1 - \frac{V_{OF}}{I_1 R_2} \right)$$

(3.10)

Como podemos observar, a tensão de off-set, principalmente através do primeiro termo  $[1 + (R_2/R_{\nu})]V_{OF}$ , introduz um desvio na tensão  $V_{REF}$  obtida através de (3.6). Isto é um fator importante, principalmente pelo fato do op-amp ser implementado com transistores MOS, que, por princípio físico, já possuem off-set elevado. Além do mais a tensão  $V_{OF}$  pode estar sujeita à variações com temperatura, contribuindo com o desequilíbrio na estabilidade de

$V_{REF}$ . Adicionado a tudo isto existe ainda o fato, já mencionado, de estarmos utilizando uma tecnologia MOS voltada exclusivamente para circuitos digitais e portanto não existindo uma preocupação, nem dados precisos, com respeito a  $V_{OF}$ . Levando tudo isto em conta, não estaríamos superestimando se considerássemos essa tensão de off-set acima de 20mV. Fica claro, então, a necessidade de minimizarmos as influências de  $V_{OF}$ , escolhendo a mínima relação possível de  $R_2/R_1$  e utilizando técnicas adequadas de layout que dessensibilizem ao máximo a sua influência.

O nosso objetivo é gerar uma tensão de referência coincidente com o próprio  $V_{DD}$  do chip. Como essa tensão de  $V_{REF}$  é muito baixa, necessitamos de algum circuito capaz de amplifica-la, de forma a obtermos a tensão de 5V desejada.

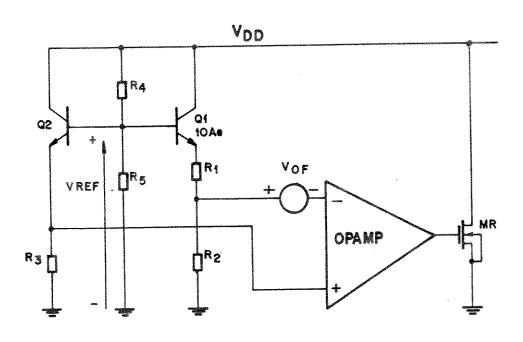

# 3.2 - MULTIPLICAÇÃO DE VREF COM DIVISOR RESISTIVO

Uma solução para obtermos  $V_{DD}$  consiste em multiplicarmos  $V_{REF}$  utilizando um divisor resistivo entre  $V_{DD}$ , as bases de Q1 e Q2 e o GND, conforme apresentado na figura 3.3 a seguir:

Fig. 3.3 - Multiplicação de  $V_{\it REF}$  com divisor resistivo

A tensão  $V_{REF}$  continua sendo a mesma expressa por (3.10). Dessa forma, se desprezarmos as correntes de base de Q1 e Q2, podemos escrever que:

$$V_{DD} = \left(\frac{R_4 + R_5}{R_5}\right) V_{REF} \tag{3.11}$$

Substituindo (3.10) encontramos:

$$V_{DD} = \left(\frac{R_4 + R_5}{R_5}\right) \left[V_{BEZ} + \frac{R_2}{R_1} V_T \ln\left(\frac{R_2}{R_3} \frac{A_1}{A_2}\right)\right] - \left(\frac{R_4 + R_5}{R_5}\right) \left(1 + \frac{R_2}{R_1}\right) V_{OF} \qquad (3.12)$$

onde desconsideramos o segundo termo de V<sub>OF</sub>, frente ao primeiro, por ser bem menor que este.

Comparando (3.12) com (3.10), vemos que a tensão de off-set continua influenciando a tensão de  $V_{DD}$  e aqui esta influência é ainda mais crítica, pois o termo de  $V_{OF}$  aparece multiplicado pelo termo  $(R_4 + R_5)/R_5$ , o qual é maior que um. Isto significa que este circuito, embora muito simples, é bastante sensível ao off-set, conforme veremos a seguir.

Na saída do op-amp foi acrescentado o transistor MR com capacidade de acionar correntes próximas de 15mA (situações de *load-dump*). Este transistor faz o papel do dispositivo de regulação da figura 2.1, enquanto o restante do circuito forma o elemento sensor de tensão.

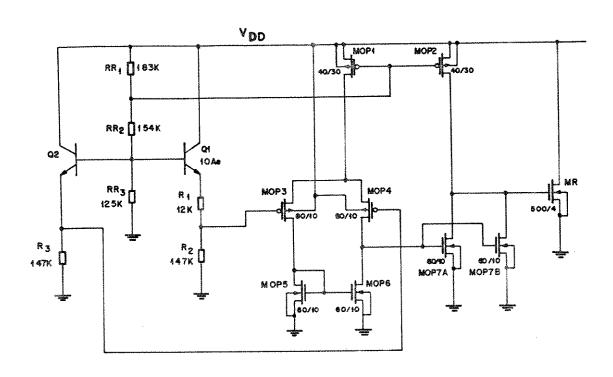

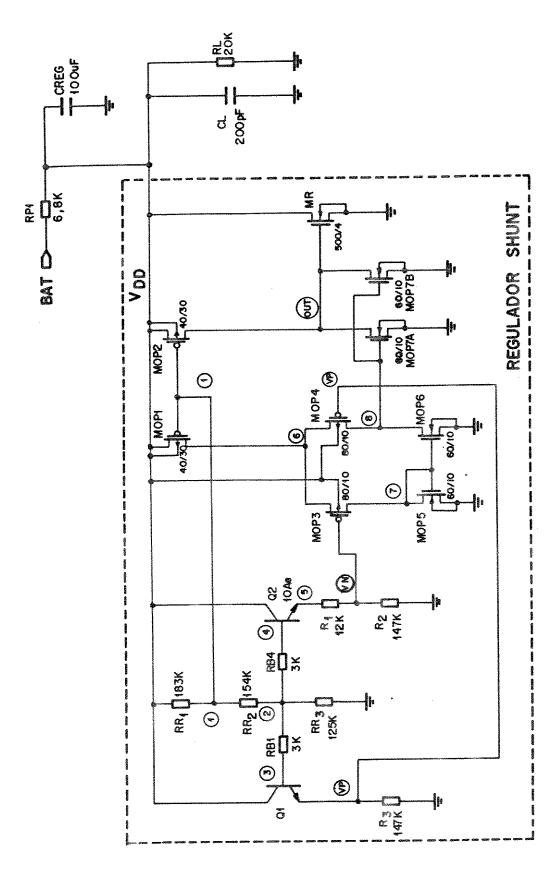

Quando o circuito é alimentado,  $V_{DD}$  sobe devido a passagem de corrente por  $R_4$  e  $R_5$ . A tensão de base dos transistores Q1 e Q2 acompanha esta subida e, quando  $V_{DD}$  atinge a tensão expressa por (3.12), a base dos transistores Q1 e Q2 atinge  $V_{REF}$ . A partir daí,  $V_{DD}$  e  $V_{REF}$  ficam estabilizadas. Um aumento em  $V_{DD}$  faz com que a tensão na entrada (+) do opamp suba acima daquela na entrada (-), com isto a tensão  $V_{GS}$  de MR aumenta, forçando-o a conduzir mais corrente e assim puxando  $V_{DD}$  para baixo. Se  $V_{DD}$  tende a baixar, ocorre o oposto, a tensão V-do op-amp supera  $V^+$ ,  $V_{GS}$  diminui e MR conduz menos, permitindo que  $V_{DD}$  suba novamente para seu estado de equilíbrio. O circuito completo deste regulador, incluindo os transistores do op-amp, é apresentado na figura 3.4. Os resistores  $R_4$  e  $R_5$  foram

substituídos por  $R_{RI}$ ,  $R_{R2}$  e  $R_{R3}$ . A divisão de  $R_4$  em  $R_{RI}$  e  $R_{R2}$  teve por objetivo a obtenção de uma tensão de polarização intermediária para os gates de MOP1 e MOP2 (transistores do opamp).

Fig. 3.4 - Circuito do regulador com divisor resistivo

## 3.2.1 - DEFINIÇÃO E CÁLCULO DOS TRANSISTORES E RESISTORES

A seguir apresentamos os cálculos efetuados para se chegar aos valores e dimensões dos componentes da figura 3.4.

## A - Resistores $R_1$ , $R_2$ , $R_3$ , $R_{RI}$ , $R_{R2}$ e $R_{R3}$

Para obtermos um melhor casamento entre Q1 e Q2 forçamos a mesma corrente pelos dois transistores, fazendo  $R_2$  e  $R_3$  iguais. Para minimizar o consumo definimos esta corrente

como sendo 5µA no caso tipico. Utilizando (3.5) escrevemos que:

$$R_2 = R_3 = \frac{V_{REF} - V_{BE2}}{I_1} \tag{3.13}$$

No caso típico a temperatura de operação está próxima de 27°C. Considerando esta temperatura e a corrente de  $5\mu A$ , estimamos que  $V_{BE2}$  vale aproximadamente 600mV. Utilizando (3.13) e sabendo que  $V_{REF}$  é igual a 1,3V podemos escrever:

$$R_2 = R_3 = \frac{1.3V - 0.6V}{5\mu A} = 140 K\Omega \tag{3.14}$$

O valor de  $R_1$  é encontrado substituindo esses valores de  $R_2$  e  $R_3$  em (3.6), supondo para este cálculo que  $V_{OF}$  é igual a zero e que  $V_T$  nesta temperatura típica vale aproximadamente 26mV. Antes porém, precisamos determinar os valores das áreas de emissor de Q1 e Q2.

Uma observação na expressão (3.12) nos leva a concluir que, para minimizarmos a ação do off-set se torna bastante interessante trabalharmos com a relação  $R_2/R_1$  a menor possível, já que a relação (R4+R5)/R5 está fixada pelos valores de  $V_{REF}$  e  $V_{DD}$ . No entanto  $R_2/R_1$  também faz parte do termo PTAT de  $K.V_T$  (segundo termo entre colchetes), o qual necessita contrabalançar o termo de  $V_{BE}$ , que apresenta coeficiente negativo de temperatura. A solução, então, é baixar a relação  $R_2/R_1$  e aumentar a relação de áreas  $A_1/A_2$ , já que esta última só participa do termo de  $K.V_T$ , não influenciando o off-set.

A área  $A_2$ , suposta unitária, foi feita a menor possível levando em conta considerações de processo e regras de layout. Quanto a  $A_1$ , do ponto de vista de layout, fazer com que esta seja muito grande, além de causar um aumento na área de silício, implica num certo grau de complexidade, dada a necessidade de um perfeito casamento entre Q1 e Q2 e uma disposição simétrica dos dispositivos, necessária para evitar problemas de temperatura. Levando-se tudo isto em consideração, julgamos que o melhor seria trabalharmos com  $A_1$  igual a 10 vezes a área  $A_2$ .

Substituindo todos esses valores em (3.6) encontramos que:

$$\frac{R_2}{R_1} = 11,69 \tag{3.15}$$

Portanto:

$$R_1 = \frac{R_2}{11,69} = \frac{140 \, K\Omega}{11,69} \approx 12 \, K\Omega \tag{3.16}$$

Quanto aos resistores  $R_{RI}$ ,  $R_{R2}$  e  $R_{R3}$ , foram calculados considerando uma corrente, no ramo destes resistores, igual a  $10\mu A$  no caso típico. Esta corrente foi feita maior que as correntes por  $R_2$  e  $R_3$  para que a influência das correntes de base dos transistores bipolares fosse desprezível. Considerando as correntes de  $5\mu A$  por Q1 e Q2, conforme dados da foundry utilizada [23], o  $\beta$  desses transitores está por volta de 100. Não é fornecido os valores máximo e mínimo de  $\beta$ , no entanto, mesmo se o valor mínimo fosse 50, o que daria uma corrente de base de  $0.1\mu A$ , ainda assim teríamos um fator 100 vezes menor em relação a corrente de  $10\mu A$ . Por outro lado limitamos em  $10\mu A$  para evitar que o consumo em baixas temperaturas (pior caso) fosse excessivo.

Assim podemos escrever:

$$R_{R3} = \frac{V_{REF}}{10\mu A} = \frac{1.3V}{10\mu A} = 130K\Omega$$

(3.17)

Para a polarização dos transistores MOP1 e MOP2, que formam as fontes de corrente do op-amp, escolhemos um tensão correspondente a 2/3 de  $V_{DD}$ . Esta tensão garante que esses transistores operem na saturação, onde a corrente  $I_D$  só depende de  $V_{GS}$ . Dessa forma encontramos  $R_{RI}$  e  $R_{R2}$ :

$$R_{R1} + R_{R2} = \frac{V_{DD} - V_{REF}}{10 \, \mu A} = \frac{5 \, V - 1 \,, 3 \, V}{10 \, \mu A} = 370 \, K\Omega \tag{3.18}$$

$$R_{R1} = \frac{V_{DD}}{3} \frac{1}{10 \,\mu A} \approx 167 \, K\Omega \tag{3.19}$$

$$R_{R2} = 370 K\Omega - 167 K\Omega = 203 K\Omega \tag{3.20}$$

Posteriormente, com ajuda do simulador, verificamos que a corrente através dos transistores do op-amp ficou pequena nas altas temperaturas. Um ajuste foi feito então, onde elevamos a tensão de  $V_{GS}$  de MOP1 e MOP2, aumentando  $R_{RI}$  e baixando  $R_{R2}$ .

Os valores finais de todos os resistores, após pequenos ajustes com o simulador, ficaram estabelecidos em:

| $R_i = 12 \text{K}\Omega$ | $R_{RI}$ =183K $\Omega$      |

|---------------------------|------------------------------|

| $R_2=147\mathrm{K}\Omega$ | $R_{R2}=154\mathrm{K}\Omega$ |

| $R_3=147\Omega$           | $R_{R3}$ =125K $\Omega$      |

Do ponto de vista prático nos deparamos com o seguinte problema: os resistores de difusão e de polisilício de que dispomos apresentam todos resistência de quadrado menor que  $100\Omega$ , o que implicaria em resistores de grandes dimensões. A melhor solução que encontramos foi utilizar resistores de poço, que apresentam resistência de quadrado típica de  $3.2 \mathrm{K}\Omega$  [17]. A desvantagem, no entanto, é que a dispersão de processo desse tipo de resistor é de  $\pm$  40% em relação ao valor típico. Além do mais, o coeficiente linear de temperatura associado a esta resistência é de aproximadamente 1%°C (R dobra a cada 100°C de variação da temperatura). Este coeficiente foi extraído da literatura, já que a documentação do processo que utilizamos não cita especificamente este parâmetro.

#### **B** - O Amplificador Operacional

A estrutura do op-amp foi projetada para ser a mais simples possível, tendo em vista a finalidade de compactação, pois o objetivo é a utilização desta célula em outros CI's automotivos futuros.

Os transistores MOP1 e MOP2 formam as fontes de corrente. Os seus valores de W e L foram escolhidos para satisfazer uma corrente típica de  $5\mu$ A, a qual por sua vez, foi escolhida para ser a menor possível, da mesma forma que as correntes por Q1 e Q2. Posteriormente, conforme dissemos, houve uma alteração neste valor de  $5\mu$ A, através do ajuste de  $R_{RJ}$  e  $R_{R2}$ .

Embora do ponto de vista do off-set, a entrada do op-amp seria melhor se realizada com transistores NMOS, que possuem uma maior transcondutância, neste op-amp utilizamos um par diferencial formado por transistores PMOS. A razão é o fato das tensões nas entradas V+ e V- estarem próximas de 0,6V, o que impediria a colocação de uma fonte de corrente ligada a um par diferencial formado por transistores NMOS.

As dimensões de MOP3 e MOP4 ( $W/L=80\mu\text{m}/10\mu\text{m}$ ) foram estabelecidas num compromisso entre minimizar o off-set intrínsico (W e L grandes) e maximizar a compactação (W e L pequenos).

MOP7B formam a carga ativa do par diferencial enquanto MOP2, MOP7A e MOP7B formam o estagio de ganho de saída, que transforma a entrada diferencial em saída simples. A presença de dois transistores MOP7A e MOP7B tem por finalidade a minimização do off-set sistemático. Este off-set é aquele associado com o equilibrio das correntes. Quando a tensão diferencial de entrada é zero, as correntes por MOP7A e MOP7B são iguais as correntes por MOP5 e MOP6. Logo a tensão  $V_{DS}$  de MOP6 é igual a de MOP5, garantindo off-set zero na saída.

#### C - O Transistor MR

A escolha das dimensões de W e L do transistor MR foi feita considerando que na condição de load-dump a corrente através desse transistor pode atingir valores próximos de 15 mA e, nos piores casos de temperatura e desvio de processo, a tensão  $V_{GS}$ , necessária ao fornecimento dessa corrente, não pode ultrapassar o valor de  $V_{DD}$  (valor máximo possível que a tensão  $V_{GS}$  de MR pode atingir sem alterar a condição de regulação).

O valores ótimos para W e L foram alcançados através da simulação elétrica conforme apresentaremos mais adiante.

#### 3.2.2 - RESULTADOS DA SIMULAÇÃO ELÉTRICA

#### 3,2.2.1 - MODELOS DE SIMULAÇÃO

Nas simulações elétricas realizadas foram utilizados os modelos de transistores MOS fornecidos pela *foundry* [23], os quais aparecem referenciados nos arquivos de simulação através da linha de comando .*lib ccbami.lib*, que chama os modelos diretamente da biblioteca. Existem 3 modelos, **nb**, **nt** e **nw**, para cada tipo de transistor NMOS utilizado, os quais são descritos a seguir. O mesmo vale para os transistores PMOS, onde temos **pb**, **pt** e **pw**.

nb = trans. NMOS "best case" - VTO mínimo

nt = trans. NMOS "typical case" - VTO típico

nw = trans. NMOS "worst case" - VTO máximo

Quanto ao modelo dos transistores bipolares NPN, a foundry forneceu apenas dados de IS, BF, BR, VA, VB e a curva  $\beta \times IC$ , tudo relativo a um transistor NPN típico com área de emissor de 250 µm. A partir desses dados calculamos um novo IS, equivalente à área de emissor do transistor que iríamos construir (17 µm x 11 µm) e, tomando também por base outros modelos similares [24], construímos um modelo próprio o qual julgamos compatível com os transistores que iríamos utilizar. Por esta razão fizemos todas as simulações considerando este único modelo, sem levar em conta as eventuais dispersões de processo. Uma ressalva é feita quanto as resistências de base desses transistores. Como as bases são formadas pelo poço P, então cada resistência de base foi emulada por um resistor de p-well de valor igual a  $3K\Omega$  - correspondente a aproximadamente um quadrado - externo ao transistor e sofrendo, portanto, as mesmas variações de processo que os resistores  $R_1$ ,  $R_2$  e  $R_3$ . Essas são as razões porque afirmamos que o modelamento dos transistores bipolares não teria muita precisão.

Já para o modelo do resistor de p-well, foi fornecido apenas as resistências de quadrado mínima, típica e máxima. O coeficiente linear de temperatura foi assumido como sendo o valor típico fornecido pela literatura (1%/°C).

#### 3.2.2.2 - ESCOLHA DE MR

O transistor MR foi dimensionado para suportar as altas correntes produzidas no momento da ocorrência dos pulsos de load-dump. No momento em que ocorre um pulso de load-dump a tensão da bateria sobe para valores relativamente altos. Embora a norma ISO especifique este pulso de tensão como tendo amplitude de 10 a 120V, o valor máximo admitido pelas montadoras é de 85V ( $V_{BAT}$  sobe 85V acima de seu valor nominal). Se fizermos uma hipótese que este pulso de load-dump tenha uma duração suficiente para não ser atenuado pelo filtro externo formado por  $R_{PI}$  e  $C_{REG}$ , então podemos calcular que a corrente através de MR, durante o pulso de load-dump, pode chegar a:

$$I_{D}(MR) = \frac{85V + V_{BAT_{MAX}} - V_{DD}}{R_{P1}}$$

(3.21)

ou seia:

$$I_D(MR) = \frac{85V + 18V - 5V}{6,8K\Omega} = 14,4mA$$

(3.22)

A corrente na prática não chegará a este valor, pois o filtro externo exerce uma boa atenuação. Por outro lado, se dimensionamos MR para suportar esta corrente, mesmo na hipótese de falha do capacitor (capacitor aberto), o CI não será destruído, tornando o produto robusto por características de projeto. Sendo assim, considerando o resultado de (3.22), assumimos que MR deve suportar correntes de até 15mA.

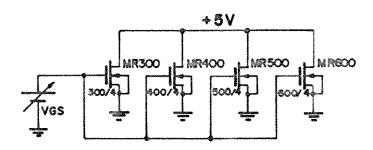

Na condição de load-dump o opamp deve então fornecer uma tensão para o gate de MR suficiente para este conduzir a corrente de 15mA. Esta tensão de gate possui um limite máximo que é o próprio  $V_{DD}$ . Para determinar as dimensões de MR fizemos uma simulação

com quatro transistores dispostos como mostra a figura 3.5. Todos têm  $L=4\mu m$  (mínimo valor de acordo com regras de layout) e W de 300, 400, 500 e 600 $\mu m$ . A tensão  $V_{DS}$  (que seria o próprio  $V_{DD}$  no circuito do regulador) foi feita igual a 5V, enquanto a tensão  $V_{GS}$  foi varrida através da simulação .DC de 0,5V a 5V. O momento que  $V_{GS}$  atinge 5V corresponde a situação de máxima corrente  $I_D$  através de MR.

Fig. 3.5 - Definição das dimensões de MR

O arquivo de simulação utilizado foi o seguinte:

```

TRANSISTOR MR WT

* simulacao para determinar o valor de W e L de mr

* .options reltol=0.0001

.temp 100

* simulacao

.dc vgs 0.5v 5v 0.01v

.probe

* .lib ccbami.lib

* vds 1 0 5v

vgs 2 0 1v

mr300 1 2 0 0 nw l=4u w=300u

mr400 1 2 0 0 nw l=4u w=400u

mr500 1 2 0 0 nw l=4u w=500u

mr600 1 2 0 0 nw l=4u w=600u

* .end

```

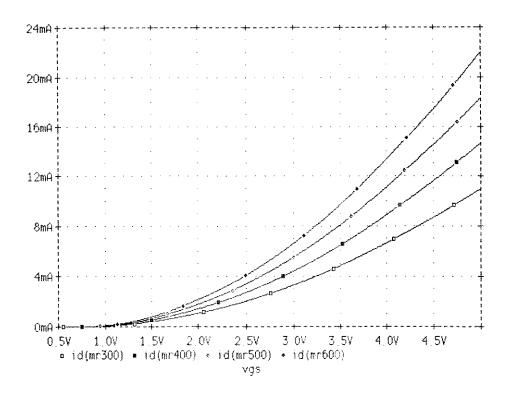

A simulação foi feita considerando transistores  $\mathbf{n}\mathbf{w}$  e temperatura de 100°C, situação esta correspondente ao pior caso, onde para um determinado valor da corrente  $I_D$ ,  $V_{GS}$  tem

valor máximo. Na figura 3.6 temos um plot das curvas das correntes  $I_D$ , em função da tensão  $V_{GS}$ , através dos quatro transistores.

Fig. 3.6 - Curvas de  $I_D \times V_{GS}$  para vários tamanhos de MR

Através da observação dessas curvas e considerando a corrente de 15mA, escolhemos W igual a 500 $\mu$ m como sendo o valor mais apropriado para o transistor MR. Assim, para um  $V_{GS}$  de 5V temos  $I_D$  igual a 18mA, o que garante uma certa margem de segurança em relação aos 15mA. Um W de 600 $\mu$ m seria desnecessário ao passo que com 300 $\mu$ m teríamos uma margem de segurança muito pequena.

#### 3.2.2.3 - SIMULAÇÕES DO REGULADOR

As simulações do regulador shunt são baseadas no circuito da figura 3.7, onde apresentamos o circuito completo com a nomeação dos nós e as resistências de base dos

transistores NPN. O circuito digital é representado de maneira simplificada por uma carga resistiva  $(R_L)$  representando o seu consumo DC. O capacitor  $C_L$  representa a carga capacitiva total vista pelo pino de  $V_{DD}$ . O valor de 200pF para  $C_L$  foi obtido extrapolando a capacitância poço-substrato pela área total estimada para o chip (obviamente é uma hipótese conservadora).

Inicialmente as simulações do regulador foram feitas considerando apenas as dispersões de processo relativas aos resistores de p-well e transistores MOS, com o off-set igual a zero. O arquivo de simulação utilizado, bgap.cir, é visto a seguir.

```

BANDGAP CMOS TP

* caso tipico : trans. tp , res. tp

*** SIMULACOES ***

.dc temp -40 100 4

.probe

*** MODELOS ***

.model rpw res (r=1 tc1=0.01); modelo do resistor de p-well

*** CIRCUITO ***

vbat bat 0 13.1v

voff vn vna 0v

.inc cct_tp

* circuito digital equivalente

rl vdd 0 20k

; carga DC do circuito logico

cl vdd 0 200pF

; carga AC vista no pad de VDD

* componentes externos

rp1 bat vdd 6.8k

creg vdd 0 100uF

.end

BANDGAP CMOS PC1

* pior caso 1 : trans. wt , res. max

*** SIMULACOES ***

.dc temp -40 100 4

.probe

*** MODELOS ***

.model rpw res (r=1.407 tc1=0.01); modelo do resistor de p-well

*** CIRCUITO ***

vbat bat 0 13.1v

voff vn vna 0v

inc cct w

```

Fig. 3.7 - Circuito de simulação do regulador

```

* circuito digital equivalente

; carga DC do circuito logico

rl vdd 0 20k

; carga AC vista no pad de VDD

cl vdd 0 200pF

* componentes externos

rp1 bat vdd 6.8k

creg vdd 0 100uF

.end

BANDGAP CMOS PC2

* pior caso 2 : trans. bt , res. min

*** SIMULACOES ***

.dc temp -40 100 4

.probe

*** MODELOS ***

.model rpw res (r=0.625 tc1=0.01); modelo do resistor de p-well

*** CIRCUITO ***

vbat bat 0 13.1v

voff vn vna 0v

inc cct b

circuito digital equivalente

; carga DC do circuito logico

rl vdd 0 20k

cl vdd 0 200pF ; carga AC vista no pad de VDD

* componentes externos

rp1 bat vdd 6.8k

creg vdd 0 100uF

.end

```

Como podemos ver, neste arquivo fizemos três simulações .dc temp varrendo a temperatura de -40 a +100°C de 4 em 4 graus. A primeira corresponde a um caso típico de processo, e as outras duas corresponde, uma com transistores MOS worst e resistência de p-well máxima, ao melhor caso de consumo e a outra, com transistores MOS best e resistência de p-well mínima, ao pior caso de consumo. A tensão  $V_{BAT}$  foi considerada com valor típico de 13,8V, mas para simplificar não colocamos o diodo série da figura 1.3 e portanto as simulações foram feitas com um  $V_{BAT}$  de 13,1V (13,8V menos a queda do diodo).

Para maior facilidade e clareza dividimos **bgap.cir** em 2 partes. A primeira se refere as descrições dos tipos e estímulos da simulação e está presente no próprio arquivo **bgap.cir**.

A segunda parte diz respeito aos componentes do circuito e está implícita através da chamada .inc de cct\_tp, cct\_w e cct\_b, os quais apresentam:

```

cct_tp - circuito com transistores MOS típico.

cct_w - circuito com transistores MOS worst-case

cct_b - circuito com transistores MOS best-case

```

Mostramos a seguir apenas o arquivo cct\_tp, já que os outros dois diferem apenas no modelo do transistor MOS (nw e nb no lugar de nt, pw e pb no lugar de pt).

```

* CIRCUITO TIPICO

*** MODELOS ***

.lib ../ccbami.lib ; transist. MOS

.model nbp npn (is=4.5e-16 bf=189.928 nf=1.01139 ikf=8.79702e-3

+ise=7e-16 ne=1.46798 vaf=42 var=8.3 br=3.06069 nr=1.01385

+rb=15 rbm=15 re=12.5474 rc=159.766

+ikr=1.46665e-3 isc=1.08641e-13 nc=1.45675

+eg=1.193 \text{ xtb}=1.2 \text{ xti}=3.0

+cjs=0.424p vjs=0.35 mjs=0.2

+cjc=0.285p vjc=0.62 mjc=0.35 xcjc=0.15

+cie=0.305p vie=0.74 mje=0.38

+tf=435p \text{ vtf}=9 \text{ xtf}=1 \text{ itf}=.1u

*** DEFINICOES ***

options itl1=200 itl2=200.

*** CIRCUITO ***

* transistores bipolares

q1 vdd 3 vp nbp

q2 vdd 4 5 nbp 10

* resistores de base (p-well) dos trans. bipol.

rb1 2 3 rpw 3k

rb2 2 4 rpw 3k

* resistores que geram K*VT

rl 5 vn rpw 12k

r2 vn 0 rpw 147k

r3 vp 0 rpw 147k

* resistires da relação de amplificação

rrl vdd 1 rpw 183k

rr2 1 2 rpw 154k

nr3 2 0 npw 125k

* amplificador operacional

mop1 6 1 vdd vdd pt 1=30u w=40u ad=320p as=320p pd=96u ps=96u

```

mop2 out 1 vdd vdd pt l=30u w=40u ad=320p as=320p pd=96u ps=96u mop3 7 vna 6 vdd pt l=10u w=80u ad=640p as=640p pd=196u ps=196u mop4 8 vp 6 vdd pt l=10u w=80u ad=640p as=640p pd=196u ps=196u mop5 7 7 0 0 nt l=10u w=60u ad=480p as=480p pd=136u ps=136u mop6 8 7 0 0 nt l=10u w=60u ad=480p as=480p pd=136u ps=136u mop7a out 8 0 0 nt l=10u w=60u ad=480p as=480p pd=136u ps=136u mop7b out 8 0 0 nt l=10u w=60u ad=480p as=480p pd=136u ps=136u

\* transistor de regulação mr vdd out 0 0 nt l=4u w=500u ad=7000p as=7000p pd=1028u ps=1028u \*

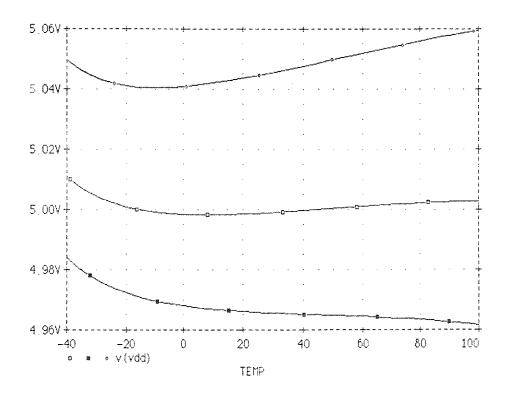

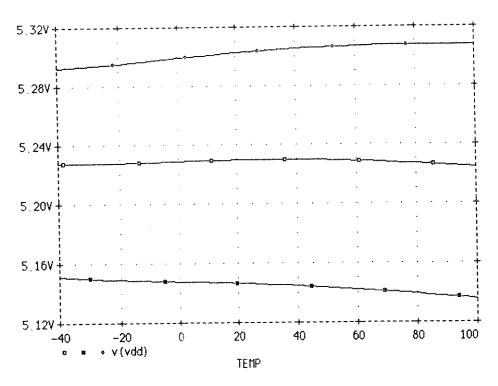

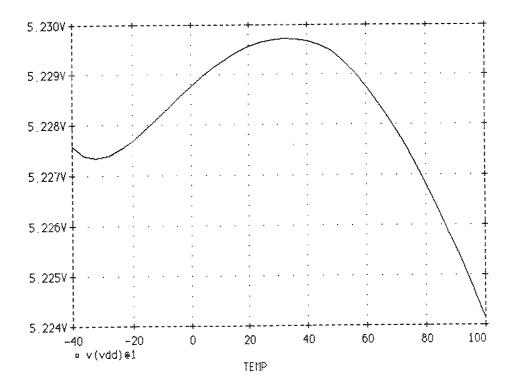

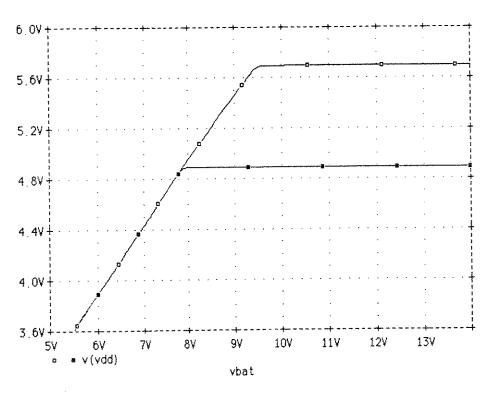

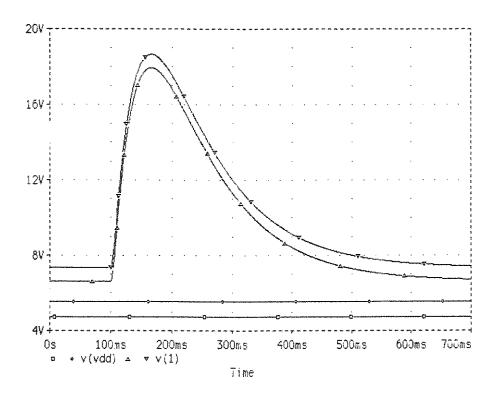

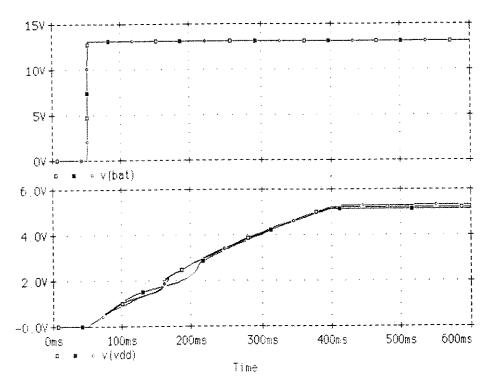

Os resultados dessas simulações são apresentados nas figuras 3.8, 3.9, 3.10 e 3.11. A figura 3.8a mostra as curvas de  $V_{DD}$  para os três casos, em função da temperatura, enquanto na figura 3.8b temos uma visão ampliada apenas do caso típico. Conforme podemos ver, no caso típico,  $V_{DD}$  está bem próximo de 5V na temperatura de 30°C (temperatura na qual acreditamos que os transistores internos do chip estarão trabalhando no caso de consumo típico).

Fig. 3.8a - Curvas de  $V_{\it DD}$  em função da temperatura

Fig. 3.8b - Curva de  $V_{\it DD}$  típica

Observando ainda a figura 3.8a vemos que a tensão  $V_{DD}$ , embora varie muito pouco, é função basicamente das dispersões de processo, sofrendo pouca influência da temperatura. Isto ocorre porque nós ajustamos o ponto de inflexão da curva  $V_{DD}$  X TEMPERATURA do caso típico, de maneira a deixa-la a mais plana possível em torno da temperatura de 30°C.

Este acerto é no entanto teórico, feito através do simulador. Na prática muitas vezes se faz necessário uma correção no formato desta curva, através de um ajuste nos valores de  $R_1$ ,  $R_2$  e  $R_3$ .

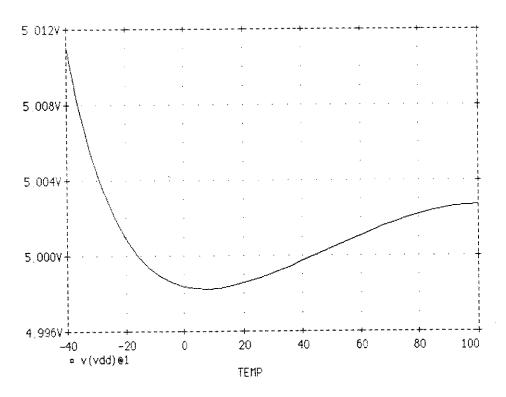

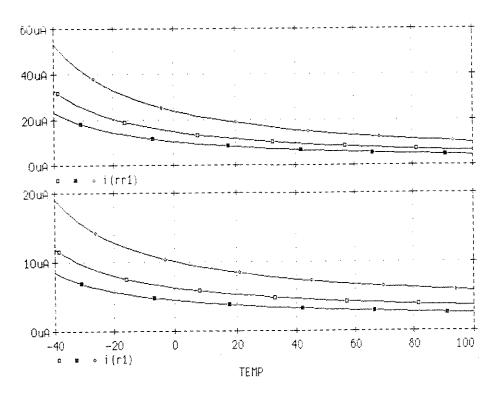

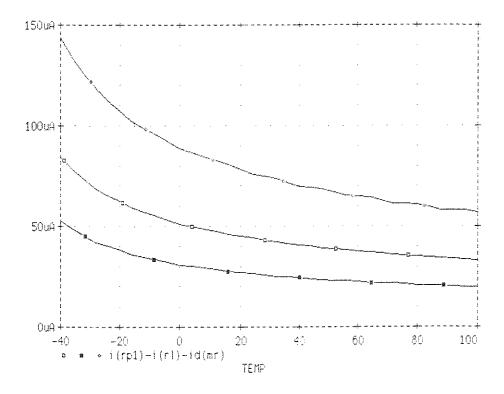

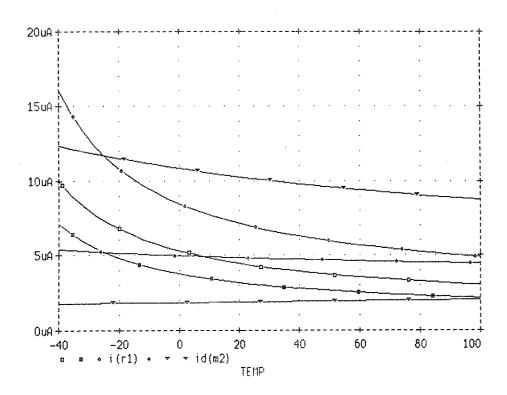

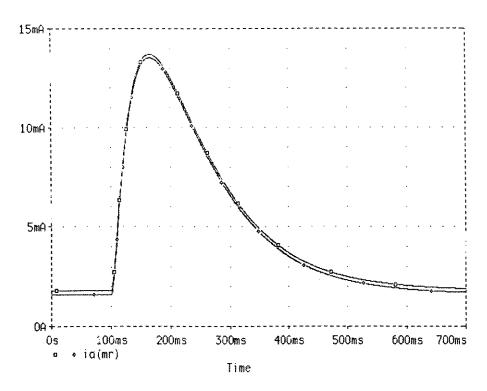

Na figura 3.9 vemos as curvas das correntes que circulam por Q1 e Q2 (corrente por  $R_I$ ) e por  $R_{RI}$ . Essas correntes apresentam coeficiente de temperatura negativo devido ao carater dominante do coeficiente positivo dos resitores de p-well. Podemos observar ainda que, no caso típico e na temperatura de 30°C, a corrente por Q1 e Q2 vale aproximadamente  $5\mu A$ , enquanto  $I(R_{RI})$  vale aproximadamente  $10\mu A$ . Estes valores, conforme dissemos, foram ajustados através do ajuste dos resistores.

Fig. 3.9 - Correntes por Q1, Q2 e  $R_{RI}$

Fig. 3.10 - Corrente pelo circuito sensor de  $V_{\it DD}$

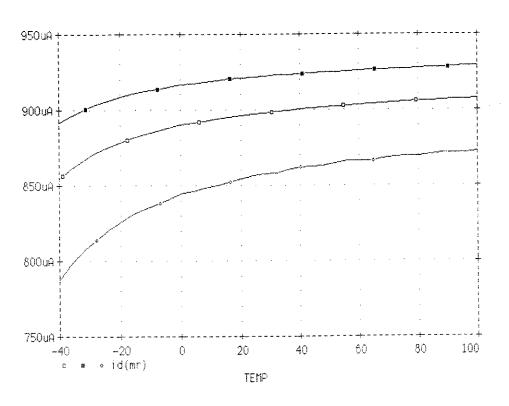

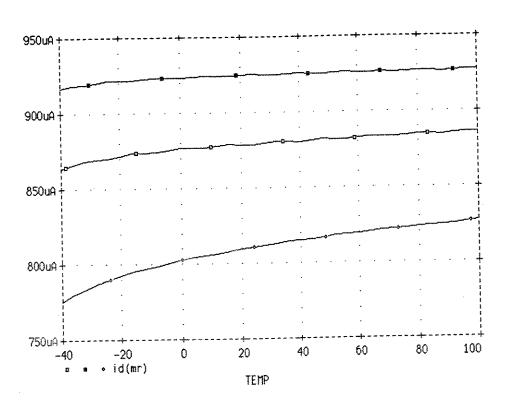

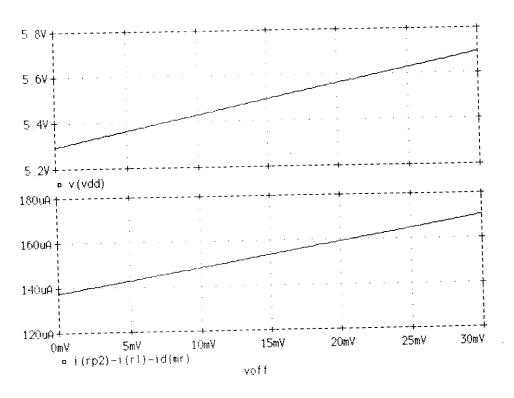

Por fim, na figura 3.10, temos a corrente  $I_{CS}$  (corrente pelo circuito sensor de  $V_{DD}$ ) e na figura 3.11, a corrente pelo transistor MR. Podemos verificar que  $I_{CS}$  diminui conforme a temperatura aumenta, seguindo a mesma tendencia das correntes por Q1, Q2 e  $R_{RI}$ . Como a tensão  $V_{DD}$  permanece praticamente constante, a corrente externa quase não se altera e, portanto, a corrente através de MR se ajusta de forma a satisfazer as outras correntes pelo circuito.

Fig. 3.11 - Corrente por MR

### O problema do off-set

Observando novamente as figuras 3.8a e 3.10 podemos identificar que os dois piores casos de funcionamento do circuito regulador ocorrem nos dois extremos de temperatura. Para temperaturas baixas, próximas de -35°C, o problema ocorre com o consumo de corrente, e nas altas temperaturas, próximas de 100°C, o problema ocorre com a dispersão da tensão  $V_{DD}$ .

Por esta razão, para maior facilidade nas nossas análises, estudamos a ocorrência do off-set do amplificador operacional apenas nesses casos extremos, pois garantindo a especificação nesses casos, todos os outros ficam automaticamente assegurados.

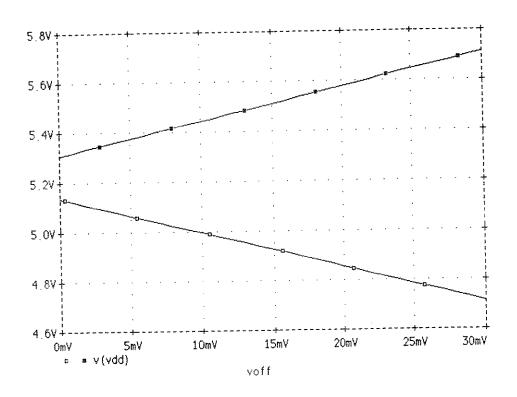

Fizemos assim três simulações, varrendo a tensão de off-set de 0 a 30mV, com step de 1mV e com a temperatura fixa em 100 ou -35°C. O arquivo referente a primeira simulação é apresentado a seguir. Utilizamos transistores worst, resistores máximos e off-set positivo. No arquivo da segunda simulação o circuito é igual, porém utilizamos transistores best e resistores mínimos, além de off-set negativo.

```

OFF-SET 1

* pior caso de vdd 1 : trans. wt , res. max, temp 100

*** SIMULACOES ***

.dc voff 0 30mv 1mv

probe

.temp 100

nodeset v(vdd) = 4.96v

*** MODELOS ***

model rpw res (r=1.407 tc1=0.01); resistor de p-well

*** CIRCUITO ***

vbat bat 0 13.1v

voff vn vna 30mv ; off-set positivo

inc cct w

* circuito digital equivalente

; carga DC do circuito logico

rl vdd 0 20k

cl vdd 0 200pF ; carga AC vista no pad de VDD

* componentes externos

rol bat vdd 6.8k

creg vdd 0 100uF

.end

```

Nessas duas primeiras simulações a temperatura foi fixada em  $100^{\circ}\text{C}$  porque o objetivo era observar o comportamento da dispersão de  $V_{DD}$ . Na tentativa de explorar a pior condição possível e tendo em vista os resultados apresentados na fig. 3.8a, acrescentamos um off-set positivo ao circuito que apresentou o menor  $V_{DD}$  (conforme arquivo acima), forçando  $V_{DD}$  a diminuir ainda mais e, no circuito que apresentou o maior  $V_{DD}$ , acrescentamos um off-set negativo, forçando esta tensão a aumentar mais ainda (caso da simulação 2).

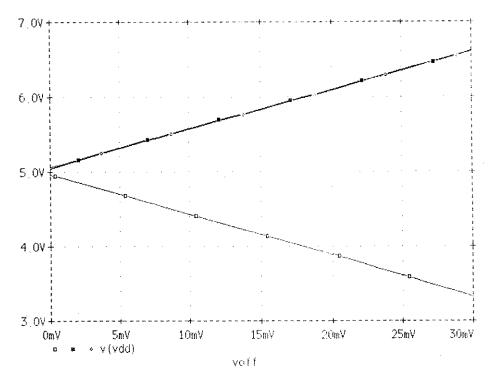

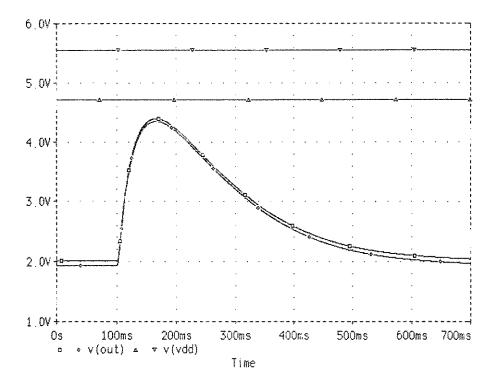

Fig. 3.12 - A dispersão de  $V_{\scriptscriptstyle DD}$

Na figura 3.12 vemos o resultado conjunto dessas simulações, o qual representa os valores máximo e mínimo da tensão  $V_{DD}$ . Podemos observar que para um off-set de  $\pm 10 \mathrm{mV}$  a dispersão já está acima dos 10% especificado.

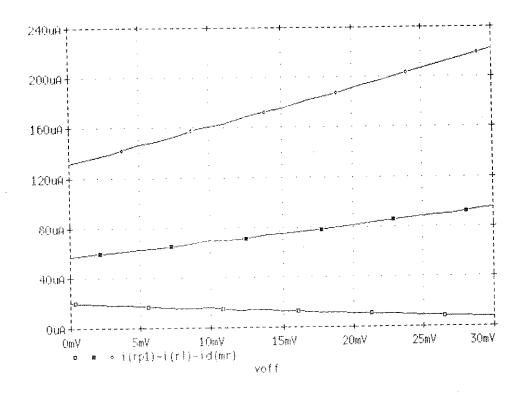

A terceira simulação é praticamente igual a segunda porém com temperatura de -35°C. Isto porque agora estamos preocupados com o máximo consumo do regulador, o que acontece nas baixas temperaturas (vide figura 3.10). A figura 3.13 mostra as curvas da corrente  $I_{CS}$  nestes três piores casos simulados. Podemos ver que no caso correspondente a terceira simulação, a corrente ultrapassa facilmente o limite de 180uA estabelecido pela especificação.

Este circuito, baseado no ganho de  $V_{REF}$  através de divisor resisivo, tem a vantagem de ser bastante simples e permitir a utilização de resistores com valores relativamente baixos (pelo menos em comparação com o outro circuito que iremos apresentar), além de permitir um ajuste da centralização de  $V_{DD}$  em 5V. Em contrapartida ele apresenta um problema muito sério de off-set, conforme observamos nas simulações anteriores. Se tomarmos os valores

finais dos resistores e substituirmos na expressão (3.12), iremos encontrar que a tensão  $V_{OF}$  aparece na composição de  $V_{DD}$  amplificada por um fator de aproximadamente 50 vezes, ou seja, num pior caso de  $V_{OF}=\pm 20 \mathrm{mV}$ , teremos uma dispersão de  $V_{DD}$  de  $\pm 1 \mathrm{V}$ , somente relativo ao off-set. Isto pode ser verificado na figura 3.12, onde a tensão  $V_{DD}$  aparece em função da tensão  $V_{OF}$ .

Fig. 3.13 - Curvas da corrente  $I_{CS}$

Esta solução se torna, portanto, bastante atraente para op-amps de baixo off-set, razão pela qual não deixamos de apresentar este circuito neste trabalho. No entanto, este não é o nosso caso, pois o off-set de um amplificador CMOS já e naturalmente de valor elevado. Se adicionarmos a este fato todos os problemas já enumerados, certamente cairemos numa situação onde o off-set possui valores bastante expressivos. O problema é ainda um pouco mais crítico com entradas em gates de transistores PMOS, já que a transcondutância destes transistores é menor que para os NMOS (de mesmas dimensões).

A idéia de se fazer um circuito para cancelamento do off-set acaba esbarrando numa

arquitetura mais complexa, quando não, envolvendo clocks de amostragens e elementos de memória (capacitores), com cancelamento do off-set somente por determinados períodos de tempo, o que não se aplica no nosso caso, onde se exige um cancelamento integral no tempo.

Para contornarmos estes problemas optamos por uma estrutura de regulador que, embora seja um pouco mais complexa em termos de circuito, possui uma dependência bem menor em relação ao off-set. Esta estrutura é apresentada no capítulo seguinte.

# CAPÍTULO 4

# MULTIPLICAÇÃO DE VREF ATRAVÉS DA SOMA DE VBE'S

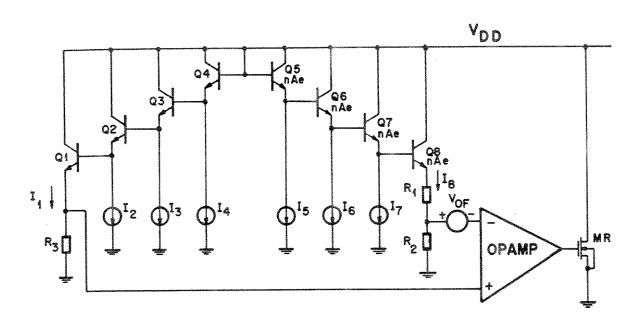

A solução adotada, que melhor satisfaz as exigências e dificuldades presentes, consiste em empilharmos transistores NPNs multiplicando a parcela de  $V_{BE}$  da equação (3.5), com consequente multiplicação da parcela  $I_1R_2$ , obtendo-se então um novo valor de  $V_{REF}$  que corresponde ao próprio valor de  $V_{DD}$  desejado. A figura 4.1 a seguir ilustra de maneira simplificada, o circuito de que estamos falando:

Fig. 4.1 - A solução empilhando transistores NPNs

Num procedimento análogo ao anterior podemos escrever (desconsiderando inicialmente a tensão de off-set do op amp):

$$V_{DD} = V_{BE1} + V_{BE2} + V_{BE3} + V_{BE4} + V_{R3}$$

(4.1)

$$V_{DD} = V_{BE1} + V_{BE2} + V_{BE3} + V_{BE4} + \frac{R_2}{R_1} V_{R1}$$

(4.2)

onde  $V_{RI}$  e  $V_{R3}$  são as quedas de tensão em  $R_I$  e  $R_3$  respectivamente.