### Universidade Estadual de Campinas - UNICAMP Faculdade de Engenharia Elétrica e de Computação - FEEC Departamento de Engenharia de Computação e Automação Industrial - DCA

# Aplicação de Controlador Evolutivo a Pêndulo Servo Acionado

#### André Luiz Delai

Dissertação submetida à Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas, como parte dos requisitos exigidos para obtenção do título de Mestre em Engenharia Elétrica

#### Banca Examinadora:

Prof. Dr. José Raimundo de Oliveira (Orientador) - DCA/FEEC/UNICAMP

Profa. Dra. Tatiane Jesus de Campos - ANHANGUERA EDUCACIONAL

Prof. Dr. Marconi Kolm Madrid - DSCE/FEEC/UNICAMP

Prof. Dr. Rafael Santos Mendes - DCA/FEEC/UNICAMP

### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA E ARQUITETURA - BAE - UNICAMP

D372a

Delai, André Luiz

Aplicação de controlador evolutivo a pêndulo servo acionado / André Luiz Delai. --Campinas, SP: [s.n.], 2008.

Orientador: José Raimundo de Oliveira Dissertação (Mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Sistema de controle digital. 2. Hardware. 3. Algoritmos evolutivos. 4. VHDL (Linguagem descritiva de hardware). 5. Dispositivos lógico programáveis. I. Oliveira, José Raimundo de. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

Título em Inglês: Application of evolutionary controller to a pendulum driver Palavras-chave em Inglês: Control systems, Evolutionary hardware, Reconfigurable hardware, FPGA, VHDL

Área de concentração: Engenharia de Computação

Titulação: Mestre em Engenharia Elétrica

Banca examinadora: Tatiane de Jesus Campos, Marconi Kolm Madrid, Rafael Santos

Mendes

Data da defesa: 25/01/2008

Programa de Pós-Graduação: Engenharia Elétrica

## COMISSÃO JULGADORA - TESE DE MESTRADO

| C    | lidata  | André | Luiz | Dolai |

|------|---------|-------|------|-------|

| Cano | ildato. | Andre | LUIZ | Delai |

Data da Defesa: 25 de janeiro de 2008

Título da Tese: "Aplicação de Controlador Evolutivo a Pêndulo Servo Acionado"

Prof. Dr. José Raimundo de Oliveira (Presidente)

Profa. Dra. Tatiane Jesus de Campos:

Prof. Dr. Marconi Kolm Madrid:

Prof. Dr. Rafael Santos Mendes:

\*\*Color Marconi Kolm Madrid: Marconi Kolm Marc

## Resumo

O uso de técnicas evolutivas empregando algorítmos genéticos na obtenção de projetos de circuitos eletrônicos analógicos e digitais já é fato e vêm sendo estudado a alguns anos. Neste contexto, o objetivo deste trabalho foi o de implementar em *hardware* reconfigurável a proposta de um controlador para pêndulo não-linear amortecido, obtido através de técnicas de *Hardware* Evolutivo. Para desenvolver um modelo físico baseado no modelo teórico (simulado) foram utilizadas tecnologias tais como a dos *Field Programable Gate Arrays* (FPGAs) e também a linguagem de descrição de *hardware VHSIC Hardware Description Language* (VHDL), dentre outros recursos.

**Palavras-chave**: Sistemas de Controle, *Hardware* Evolutivo, *Hardware* Reconfigurável, FPGA, VHDL.

## Abstract

The use of genetic algorithms using evolutionary techniques in obtaining projects of analogue and digital electronic circuits is already fact and have been studied for some years. In this context, the objective of this work was the implementation in reconfigurable hardware of a driver for non-linear damped pendulum, obtained through Evolvable Hardware approach. Technologies such as the Field Programable Gate Arrays (FPGA's) and VHDL were used to develop a physical model based on the theoretical model (simulated), among other resources.

**Keywords**: Control Systems, Evolvable Hardware, Reconfigurable Hardware, FPGA, VHDL.

# Agradecimentos

Agradeço às pessoas que de alguma forma contribuíram para a realização deste trabalho. Em especial, quero agradecer:

A meu orientador Prof. Dr. José Raimundo de Oliveira, por ter me aceitado como seu aluno e me guiado com paciência e competência durante todo o meu mestrado.

Ao Prof. Dr. Marconi Kolm Madrid por ter me disponibilizado acesso ao Laboratório de Sistemas Modulares Robóticos (LSMR) e pelo grande apoio moral.

Ao professor Dr. José Antenor Pomílio por ter gentilmente cedido um de seus módulos de potência, que foi usado no acionamento do motor do pêndulo.

A Tatiane Campos, pelas conversas, dicas e pelo excelente trabalho de doutorado o qual serviu de base para esta dissertação.

Aos professores da pós-graduação da FEEC, por toda a bagagem de conhecimento transmitida durante os cursos.

Ao meu pai Hélio, minha mãe Maria Lindaci e meu irmão Fábio, por terem acreditado em mim em todos os momentos e me ajudado a percorrer mais essa trajetória.

A minha avó Emília (*in memorian*), pelo amor infinito e dedicação dados a mim durante todos os momentos da minha vida.

Ao meu grande e verdadeiro amigo Filipe Fazanaro (exímio jogador de *Counter Strike Source*) que me apoiou, incentivou e me ajudou a concluir esse trabalho.

A todos os meus amigos, pela paciência e companheirismo.

A CAPES pelo apoio financeiro.

| "Existem comprimentos de ondas que pessoas não podem enxergar, sons que pessoas não podem ouvir, e talvez computadores tenham pensamentos que pessoas não poderiam ter. | e |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Richard Hammin                                                                                                                                                          | g |

|                                                                                                                                                                         |   |

|                                                                                                                                                                         |   |

|                                                                                                                                                                         |   |

|                                                                                                                                                                         |   |

|                                                                                                                                                                         |   |

|                                                                                                                                                                         |   |

|                                                                                                                                                                         |   |

# Sumário

| Resumo                           |                        | iv          |

|----------------------------------|------------------------|-------------|

| Abstract                         |                        | v           |

| Agradecimentos                   |                        | vi          |

| Dedicatória                      | 7                      | / <b>ii</b> |

| Epígrafe                         | $\mathbf{v}$           | iii         |

| Sumário                          |                        | ix          |

| Lista de Abreviaturas            | 3                      | ζii         |

| Lista de Figuras                 | x                      | iv          |

| Lista de Tabelas                 | xv                     | / <b>ii</b> |

| ı INTRODUÇÃO                     |                        | 1           |

| 1.1 Objetivo Contribuição e Orga | anização do Trabalho   | 2           |

| 2 COMPUTAÇÃO EVOLUTIVA           | A E HARDWARE EVOLUTIVO | 4           |

| 2.1 Computação Evolutiva         |                        | 4           |

| 2.1.1 Resumo da Teoria da        | Seleção Natural        | 4           |

SUMÁRIO x

|   |                                                                     | 2.1.2  | Inteligência de Máquina                               | 7       |

|---|---------------------------------------------------------------------|--------|-------------------------------------------------------|---------|

|   |                                                                     | 2.1.3  | Algoritmos Evolutivos                                 | 7       |

|   | 2.2                                                                 | Hardu  | vare Evolutivo                                        | 13      |

|   |                                                                     | 2.2.1  | Síntese de <i>Hardware</i> Digital                    | 13      |

|   |                                                                     | 2.2.2  | Justificativas Vantagens e Aplicabilidade             | 15      |

|   |                                                                     | 2.2.3  | Funcionamento da Técnica                              | 17      |

| 3 | LÓGICA RECONFIGURÁVEL E A LINGUAGEM DE DESCRIÇÃO DE $HARDWARE$ VHDL |        |                                                       | E<br>18 |

|   | 3.1                                                                 | Field  | Programable Gate Array                                | 18      |

|   |                                                                     | 3.1.1  | Projetos Utilizando Dispositivos Lógicos Programáveis | 19      |

|   | 3.2                                                                 | A Ling | guagem VHDL                                           | 21      |

|   |                                                                     | 3.2.1  | Entidade de Projeto                                   | 22      |

|   |                                                                     | 3.2.2  | Síntese de Circuitos Usando VHDL                      | 23      |

| 4 | CO                                                                  | NTRO   | LE APLICADO AO PÊNDULO                                | 25      |

|   | 4.1                                                                 | Sistem | nas Automáticos                                       | 25      |

|   | 4.2                                                                 | Sistem | na de Controle em Malha Fechada                       | 26      |

|   | 4.3                                                                 | Contro | ole do Pêndulo                                        | 26      |

|   | 4.4                                                                 | Especi | ficações Técnicas                                     | 27      |

|   | 4.5                                                                 | Pêndu  | lo Amortecido                                         | 27      |

|   | 4.6                                                                 | Contro | olador Proporcional, Integral e Derivativo            | 28      |

|   | 4.7                                                                 | Técnio | ea Utilizada no Projeto dos Controladores             | 29      |

| 5 | AP                                                                  | LICAÇ  | ÇÃO E RESULTADOS EXPERIMENTAIS                        | 33      |

|   | 5.1                                                                 | Imple  | mentação Física do Sistema de Controle                | 33      |

|   |                                                                     | 5 1 1  | Pêndulo Servo Acionado                                | 34      |

SUMÁRIO xi

| Re           | eferê | ncias E | Bibliográficas                            | 61 |

|--------------|-------|---------|-------------------------------------------|----|

| $\mathbf{A}$ | Diag  | gramas  | 5                                         | 58 |

|              | 6.1   | Trabal  | hos Futuros                               | 57 |

| 6            | CO    | NCLU    | $	ilde{SAO}$                              | 56 |

|              | 5.6   | Cálcul  | o do Erro Médio Quadrático                | 54 |

|              | 5.5   | Dados   | Obtidos                                   | 48 |

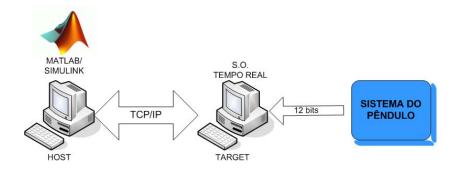

|              | 5.4   | Sistem  | a de Aquisição de Dados                   | 47 |

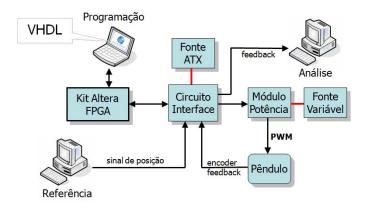

|              | 5.3   | Panora  | ama Geral do Sistema                      | 46 |

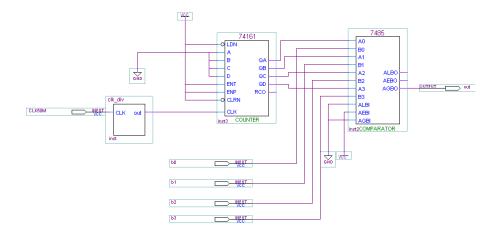

|              |       | 5.2.10  | Bloco Gerador de Sinal PWM                | 45 |

|              |       | 5.2.9   | Bloco Tradutor PWM                        | 44 |

|              |       | 5.2.8   | Bloco do Controlador                      | 43 |

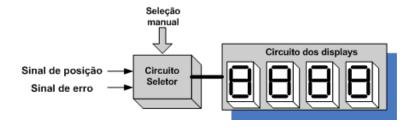

|              |       | 5.2.7   | Bloco Decodificador do Display            | 43 |

|              |       | 5.2.6   | Bloco Seletor de Sinais                   | 42 |

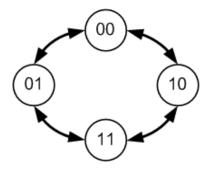

|              |       | 5.2.5   | Bloco Decodificador do Encoder            | 41 |

|              |       | 5.2.4   | Bloco de Saturação do Sinal de Erro       | 41 |

|              |       | 5.2.3   | Blocos de Ajuste de Referência            | 41 |

|              |       | 5.2.2   | Bloco Somador                             | 40 |

|              |       | 5.2.1   | Bloco de Interface com o PC               | 39 |

|              | 5.2   |         | e do Sistema em FPGA                      |    |

|              |       | 5.1.6   | Módulo de Potência                        |    |

|              |       | 5.1.5   | Sistema de Geração de Sinal de Referência |    |

|              |       | 5.1.4   | Kit Fpga de Desenvolvimento               |    |

|              |       | 5.1.3   | Circuito de Interfaceamento               |    |

|              |       | 5.1.2   | Alimentação do Sistema                    | 34 |

# Lista de Abreviaturas

AG Algoritmo Genético

CC Corrente Contínua

E/S Entrada/Saida

**EDA** Electronic Design Automation

EHW Evolvable Hardware

FPGA Field Programmable Gate Array

HDL Hardware Description Language

IBM International Business Machines

**IEEE** Institute of Electrical and Electronic Engineers

**IP** Internet Protocol

JTAG Joint Test Action Group

LE Logic Element

LSMR Laboratório de Sistemas Modulares Robóticos

PC Personal Computer

PD Proporcional Derivativo

PI Proporcional Integral

PID Proporcional Integral Derivativo

Lista de Abreviaturas xiii

${\bf PLD}\ \textit{Programable Logic Device}$

PROM Programable Read Only Memory

PWM Pulse Width Modulation

SRAM Static Random Access Memory

${\bf TCP} \ \ Transmission \ \ Control \ Protocol$

**ULA** Unidade Lógica Aritmética

VHDL VHSIC Hardware Description Language

VHSIC Very-High-Speed Integrated Circuit

Mbps Megabits por segundo

# Lista de Figuras

| 2.1  | Charles Darwin                                                               | 4  |

|------|------------------------------------------------------------------------------|----|

| 2.2  | Gregor Mendel                                                                | 6  |

| 2.3  | Cromossomos                                                                  | 10 |

| 2.4  | Método da Seleção por Roleta                                                 | 11 |

| 2.5  | Crossover de ponto único                                                     | 11 |

| 2.6  | Mutação simples                                                              | 11 |

| 2.7  | Diagrama de fluxo dos AG's                                                   | 12 |

| 2.8  | Modelo de representação do processo de projeto de sistemas digitais proposto |    |

|      | por Suzim                                                                    | 13 |

| 2.9  | Diagrama Y                                                                   | 14 |

| 2.10 | Processo EHW                                                                 | 15 |

| 3.1  | Estrutura Básica de um FPGA                                                  | 19 |

| 3.2  | Fluxo de projeto lógico programável                                          | 19 |

| 3.3  | Descrição VHDL de Circuito Lógico                                            | 22 |

| 3.4  | Etapas de um projeto                                                         | 23 |

| 4.1  | Conceito de planta                                                           | 25 |

| 4.2  | Diagrama de sistema de controle em malha fechada                             | 26 |

| 4.3  | Acionamento por PWM                                                          | 26 |

LISTA DE FIGURAS xv

| 4.4  | Ilustração de pêndulo simples                                                           | 27 |

|------|-----------------------------------------------------------------------------------------|----|

| 4.5  | Codificação dos ganhos do controlador                                                   | 30 |

| 4.6  | Codificação netlist para controlador EHW $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 30 |

| 4.7  | Comportamento dos controladores Proporcional e EHW                                      | 32 |

| 5.1  | Diagrama geral do controlador                                                           | 33 |

| 5.2  | Pêndulo servo-acionado                                                                  | 34 |

| 5.3  | Fonte do acionador do pêndulo                                                           | 35 |

| 5.4  | Fonte do circuito de interfaceamento                                                    | 35 |

| 5.5  | Circuito de interface                                                                   | 36 |

| 5.6  | Kit de Desenvolvimento Altera                                                           | 36 |

| 5.7  | Esquema do gerador de referência                                                        | 37 |

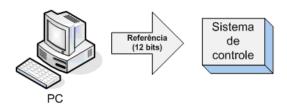

| 5.8  | PC gerador de sinal de referência                                                       | 37 |

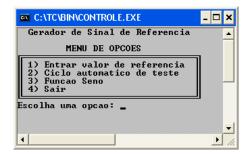

| 5.9  | Interface do Sofware                                                                    | 38 |

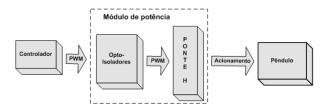

| 5.10 | Diagrama do módulo de potência                                                          | 38 |

| 5.11 | Interface paralela IBM/PC                                                               | 39 |

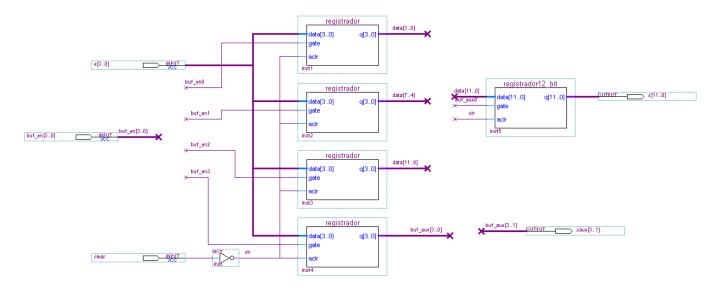

| 5.12 | Bloco de interface com PC (expandido)                                                   | 40 |

| 5.13 | Sinais provenientes do encoder                                                          | 42 |

| 5.14 | Estados da máquina do decodificador                                                     | 42 |

| 5.15 | Esquema do bloco seletor                                                                | 43 |

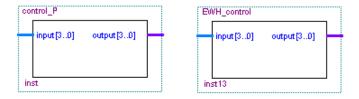

| 5.16 | Blocos de controle propocional e EHW                                                    | 44 |

| 5.17 | Diagrama do bloco gerador de sinal PWM (expandido)                                      | 46 |

| 5.18 | Diagrama dos componentes de hardware                                                    | 47 |

| 5.19 | Bancada experimental                                                                    | 47 |

| 5.20 | Sistema de aquisição de dados XPC target                                                | 48 |

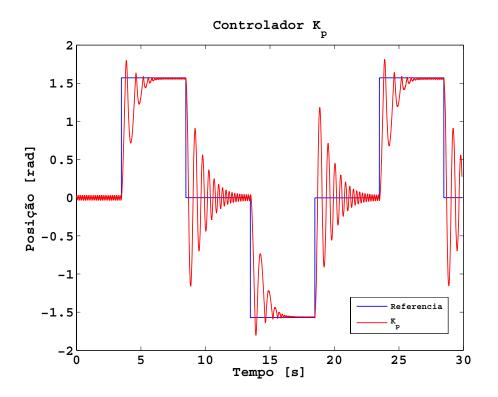

| 5.21 | Resposta temporal do sinal de posição - kp                                              | 49 |

LISTA DE FIGURAS xvi

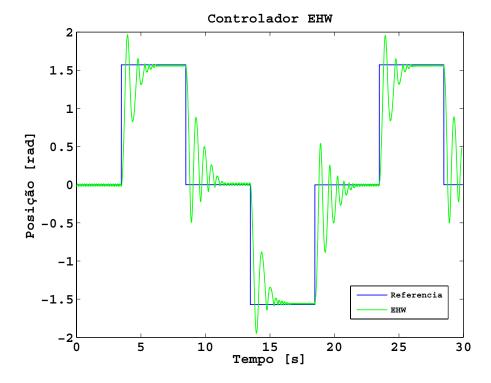

| 5.22 Resposta temporal do sinal de posição - EHW                                    | 49   |

|-------------------------------------------------------------------------------------|------|

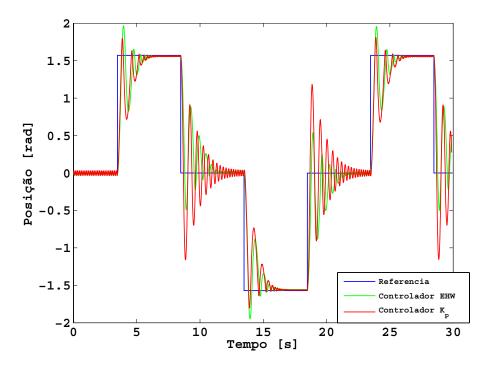

| 5.23 Resposta temporal do sinal de posição - Kp e EHW                               | 50   |

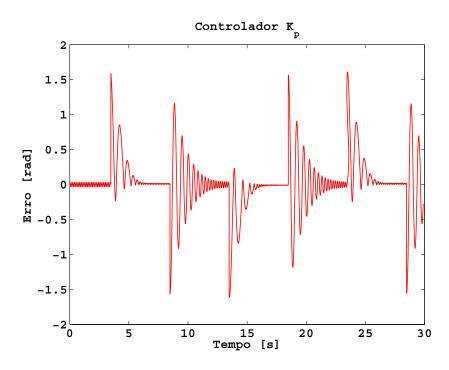

| 5.24 Resposta temporal do sinal de erro - Kp                                        | 50   |

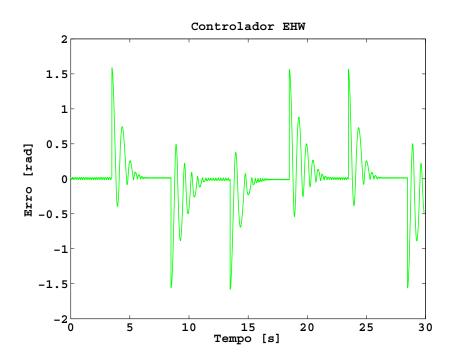

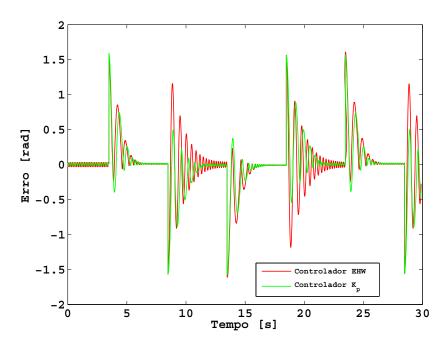

| 5.25 Resposta temporal do sinal de erro - ehw                                       | 51   |

| 5.26 Resposta temporal do sinal de erro - Kp e ehw                                  | 51   |

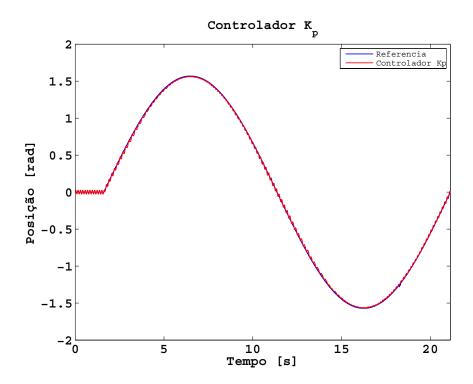

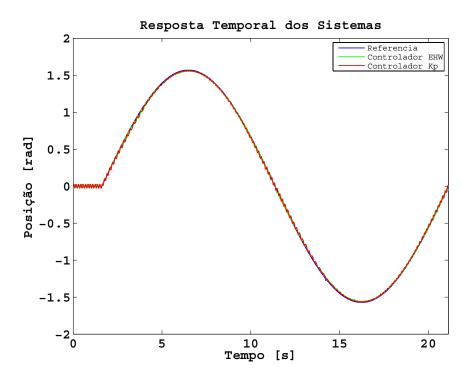

| 5.27 Resposta temporal do sinal de posição em função seno - Kp $\dots \dots \dots$  | 52   |

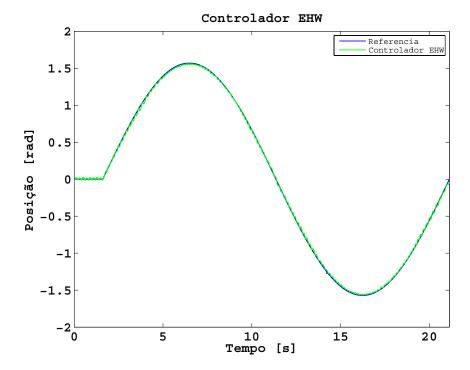

| 5.28 Resposta temporal do sinal de posição em função seno - EHW                     | 52   |

| $5.29$ Resposta temporal do sinal de posição em função seno - EHW e Kp $\dots\dots$ | 53   |

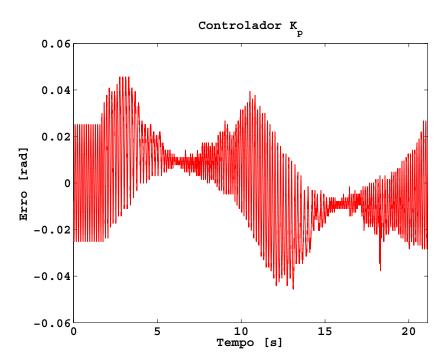

| 5.30 Resposta temporal do sinal de erro senoidal - Kp                               | 53   |

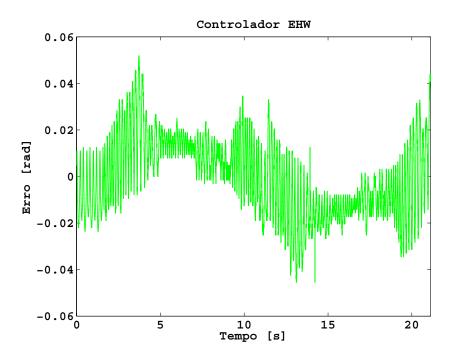

| 5.31 Resposta temporal do sinal de erro senoidal - EHW                              | 54   |

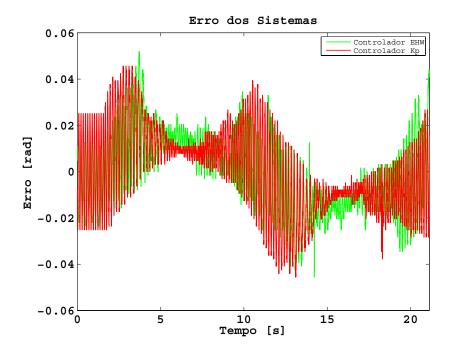

| 5.32 Resposta temporal do sinal de erro senoidal - EHW e Kp                         | 54   |

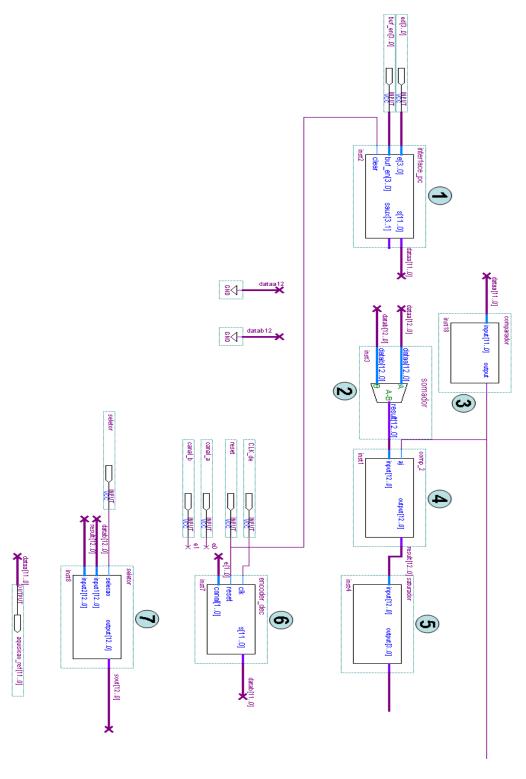

| A.1 Diagrama do sistema de controle (parte 1)                                       | 59   |

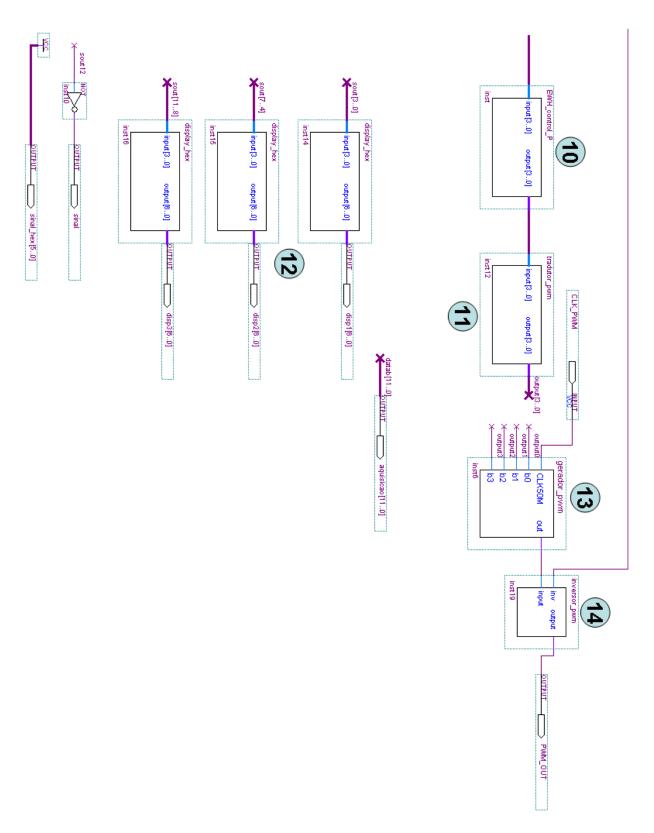

| A.2 Diagrama do sistema de controle (parte 2)                                       |      |

| - A.A. DIAPIANA UU SISLEMA UE COMHUE CHARLE AL                                      | ()() |

# Lista de Tabelas

| 4.1 | Tabela verdade Kp e EHW                    | 31 |

|-----|--------------------------------------------|----|

| 5.1 | Sinais do bloco tradutor e PWM             | 45 |

| 5.2 | Valor RMS do erro para referência quadrada | 55 |

| 5.3 | Valor RMS do erro para referência senoidal | 55 |

# Capítulo 1

# INTRODUÇÃO

A automação no processo de síntese de circuitos eletrônicos é empregada a muitos anos. Projetar circuitos eletrônicos, analógicos ou digitais, confiáveis, de baixo consumo e otimizados é, muitas vezes, uma tarefa difícil e que pode demandar um longo tempo de projeto. Em um mundo com fronteiras comerciais cada vez menores, tecnologia de ponta significa dinheiro e, novas técnicas de projeto que venham a somar ítens como produtividade, baixo custo e desempenho serão sempre bem vindas para a indústria da eletrônica.

Uma nova abordagem para o projeto automatizado de controladores foi proposta por Campos (2007), a qual realiza um processo heurístico buscando o melhor circuito eletrônico para uma determinada aplicação (naquele trabalho, um controlador digital para pêndulo). A busca é realizada através da técnica conhecida como hardware evolutivo, que emprega algoritmos evolutivos com o objetivo de evoluir circuitos até um estágio satisfatório a sua aplicação. A técnica EHW aplicada a controle de sistemas é uma alternativa aos métodos tradicionais, ela usa algoritmo genético no projeto e não para a sintonia de controladores. Nesta tese, os controladores evolutivos são comparados aos controladores clássicos Proporcionais e Proporcionais-Derivativos com ganhos sintonizados por meio de algoritmos genéticos (AG's), obtendo resultados promissores e inspirando a escolha do tema desta dissertação, que buscou validar a técnica através de um modelo experimental de bancada.

O desenvolvimento e testes dos controladores propostos por Campos (2007) foram realizados exclusivamente em ambiente computacional, sendo que os controladores foram simulados para análise de comportamento frente ao controle posicional de um pêndulo não-linear, e os dados obtidos na simulação utilizados como feedback no processo de evolução do hardware.

## 1.1 Objetivo Contribuição e Organização do Trabalho

O trabalho realizado como parte desta dissertação visou a implementação em laboratório do sistema simulado em computador por Campos (2007) para teste dos controladores evolutivos. O objetivo da construção física do sistema foi o de verificar o desempenho dos controladores através de testes em um pêndulo real. Ele contribuiu como um complemento daquele trabalho, pois colocou a prova o controlador evolutivo digital de 4 bits frente a um controlador proporcional também de 4 bits no controle de um pêndulo servo acionado, tendo-se imposto as condições de testes idênticas para ambos os controladores.

O texto está organizado em 5 capítulos, começando por este de introdução e os demais capítulos que são descritos a seguir. O capítulo 2 inicia com uma introdução aos conceitos fundamentais descrevendo um resumo sobre a área de computação evolutiva, a sua base na teoria neo-darwiniana e seu principal algoritmo evolutivo, o algoritmo genético (Holland, 1975), amplamente usado na pesquisa da evolução de circuitos eletrônicos. No âmbito dos algoritmos genéticos são detalhados os principais componentes dos algoritmos evolutivos como a codificação, avaliação e operadores de seleção e reprodução. Neste mesmo capítulo é apresentada a área de hardware evolutivo, que tem como base os conceitos abordados no capítulo anterior. São descritos os principais conceitos, benefícios e motivações desta área de pesquisa.

O capítulo 3 apresenta a tecnologia de dispositivos lógicos reconfiguráveis Field Programmable Gate Array (FPGA), que baseia o chip reconfigurável escolhido para ser utilizado na execução do projeto. Também é apresentada uma breve descrição da VHSIC Hardware Description Language (VHDL), utilizada na programação deste dispositivo.

Conceitos básicos e detalhes sobre o objeto do controle (pêndulo), controladores PID, a forma como o sistema atua sobre o pêndulo e também a técnica utilizada na geração do controlador evolutivo podem ser vistos no capítulo 4.

No capítulo 5 inicia-se com a descrição do trabalho propriamente dito onde é mostrada a teoria básica do sistema de um pêndulo e também a técnica utilizada na criação dos controladores. Na seqüencia são mostrados os recursos técnicos utilizados no desenvolvimento do sistema de controle do pêndulo em bancada, tal como a alimentação do sistema, circuito de interface e kit de desenvolvimento. Por fim são descritos de forma detalhada todos os módulos sintetizados dentro do *chip* digital reconfigurável, os quais são responsáveis pelo controle do sistema. Naquele capítulo também é vista a descrição do sistema de aquisição de dados utilizado para amostrar os sinais que tornaram possível a criação dos gráficos de análise comportamental dos controladores. São exibidos os gráficos obtidos assim como um cálculo comparativo de erro

entre os controladores evolutivo e proporcional sintonizado por AG.

O último capítulo contém as considerações finais sobre o trabalho, apresentando uma análise geral sobre os testes, a técnica de construção de controladores evolutivos e também uma discussão sobre trabalhos futuros.

# Capítulo 2

# COMPUTAÇÃO EVOLUTIVA E HARDWARE EVOLUTIVO

## 2.1 Computação Evolutiva

## 2.1.1 Resumo da Teoria da Seleção Natural

Em meados do século dezenove Charles Darwin apresentava à comunidade científica uma teoria muito polêmica que visava, em suma, explicar a diversidade biológica abundante em nosso planeta. A primeira edição do livro a Origem das Espécies esgotou-se do mercado no primeiro dia de publicação, 24 de novembro de 1859.

Figura 2.1: Charles Darwin

Darwin não foi o primeiro a propor a idéia de que as espécies de plantas e de animais

podem sofrer modificações com o passar do tempo. Na última década do séc. XVIII, o avô de Charles, Erasmus Darwin, escreveu um tratado sobre a evolução e logo depois, em 1809, o naturalista francês Jean Baptiste de Lamarck publicou sua Filosofia Zoológica, na qual apresenta estudos sobre a mutabilidade das espécies biológicas (Green, 2006). Entretanto, é de Darwin que se origina a moderna teoria da evolução.

Entre 1831 e 1836 Darwin realizou uma viagem à bordo do H. M. S. Beagle trabalhando como naturalista e colecionando e observando os diversos fenômenos geológicos e biológicos que encontrava. Até a apresentação de seu livro em 1859 realizou extensas leituras e fez experiências cuidadosas para fundamentar sua teoria.

Basicamente a teoria da seleção natural afirma que as espécies biológicas existentes hoje, ou em qualquer outra época, estão sujeitas à seleção por seu meio ambiente. Dessa forma, os indivíduos (seres biológicos) são forçados a se adaptar ao ambiente para terem melhores chances de sobrevivência e reprodução como, por exemplo, fugindo de predadores e conseguindo alimento. Os indivíduos com baixo nível de adaptação conseqüentemente perecem. Devido à variação, cujos resultados podem ser observados amplamente, a Seleção Natural pode, segundo Darwin, explicar a evolução biológica, ou o que ele chamava de "descendência com modificação".

De acordo com a teoria de Darwin, o chamado Darwinismo, para que haja a evolução, os indivíduos necessitam ser submetidos a três processos:

- Reprodução com herança

- Variação

- Seleção Natural

Na reprodução com herança os indivíduos transmitem aos seus descendentes características anteriormente premiadas pelo ambiente. Já na variação, mudanças aleatórias ocorrem para geração de novas características a serem testadas pela seleção natural. Dessa forma, o "motor evolucionário" reside na reprodução com variação e na seleção pelo meio ambiente.

#### Neodarwinismo

Darwin conhecia as alterações que ocorriam nos seres, e que algumas delas pelo menos eram hereditárias, porém não conhecia o mecanismo da hereditariedade devido ao fato de que, até então, não se haviam estabelecidos os conceitos da genética.

Gregor Mendel, monge austríaco, realizou por volta de 1866 experiências com plantas de horta, especialmente ervilhas, cujos resultados o levaram a propor a idéia de herança particulada. Mendel notou ao estudar algumas características como a cor das flores, a altura da planta, o formato e a textura da semente, que as contribuições parentais são expressas desigualmente a combinação não ocorre (Green, 2006).

Figura 2.2: Gregor Mendel

Para explicar seus resultados, Mendel sugeriu a idéia de que esses traços são herdados como elementos (que hoje chamamos de genes), sendo cada elemento recebido de um dos pais. Alguns elementos são dominantes, outros recessivos, de modo que se um descendente possui dois elementos dominantes, ou um dominante e um recessivo, o traço dominante é que será aparente. O recessivo só aparecerá quando estiverem presentes dois elementos recessivos ou seja, a ausência de um dominante.

O próprio Mendel desenvolveu os conceitos de dominância e recessividade, e seu trabalho inclui uma distinção clara entre genótipo e fenótipo. O fenótipo é o que se observa (cor dos olhos, formato da semente), ao passo que só pode-se conhecer o genótipo básico por meios mais sutis. Através da genética moderna sabe-se hoje que os genes estão agrupados em uma molécula de ARN (Ácido Ribonucléico) dentro dos cromossomos, que por sua vez estão situados no núcleo das células.

Dessa forma uma parte faltante na teoria de Darwin foi preenchida pela genética, e a união de ambas ficou sendo conhecida como Neodarwinismo, que é a teoria mais aceita nos dias de hoje para explicar questões como a da biodiversidade.

Demais informações sobre o tema podem ser encontradas em (Green, 2006).

### 2.1.2 Inteligência de Máquina

Inteligência pode ser definida como a capacidade de um sistema de adaptar seu comportamento para encontrar metas desejadas em uma gama de ambientes (Fogel, 2006).

Inteligência artificial é uma área de pesquisa que tem por objetivo simular em sistemas computacionais a capacidade humana de resolver problemas, não implicando, necessariamente, que a máquina "pense" da mesma forma que um ser humano.

De acordo com Piennar (Piennar, 1998) o fundamental para a inteligência, seja biológica ou de máquina, é o método pelo qual a informação é organizada para criar representações internas. Essas representações são por sua vez processadas por um sistema visando satisfazer as metas condicionais.

O professor Herbert A. Simon definiu a "ciência do artificial" como a maneira pela qual um sistema de tratamento de informação pode representar a informação coletada do mundo exterior, e utilizá-la para elaborar suas próprias ações (Pessis-Pasternnak *et al.*, 1992).

A evolução tem criado criaturas de crescente inteligência o tempo todo (Bäck *et al.*, 2000).

## 2.1.3 Algoritmos Evolutivos

A essência dos algoritmos evolutivos está contida na informática bio-inspirada, uma linha de pesquisa que visa obter soluções para problemas computacionais complexos através do estudo de sistemas biológicos naturais.

Ao longo do tempo, graças a teoria Neodarwinista, surgiram vários algoritmos evolutivos que são aplicados às mais diversas áreas.

Desde a década de 40, cientistas da computação têm tentado usar mecanismos naturais como metáforas para a computação. Redes Neurais Artificiais certamente são o exemplo mais popular. No final dos anos 50 cientistas começaram a pesquisar os princípios da evolução biológica visando desenvolver novos modelos para a computação, dando assim os primeiros passos para o que viria a se tornar a Computação Evolutiva. Problemas de otimização têm sido o principal foco de aplicação desta nova metodologia. Evolução é um processo de otimização (Mayr, 1988).

Algoritmos Evolutivos são tipicamente aplicados para resolver problemas de busca na

forma:

$$f: S \to \mathbb{R}$$

(2.1)

onde S é um espaço de busca que é constituído por todas as possíveis soluções para um problema em particular (Zebulum et~al., 2002). Dependendo das particularidades do problema, as soluções podem ser representadas por vetores de n-dimensionais, binários, inteiros ou de números reais. Para todas as soluções existentes em S um número real é associado, chamado de valor de fitness (Equação 2.1), provendo um modo de medir o quão adequada a solução é para resolver tal problema. Em outras palavras o valor associado ao fitness mostra o quanto este indivíduo está adaptado ao meio ambiente (problema). A primeira tarefa de um algoritmo evolutivo é a de amostrar eficientemente um amplo espaço de busca S encontrando soluções em conformidade com o objetivo do problema.

Algoritmos evolutivos utilizam o processo de aprendizado coletivo de uma população de indivíduos, o que implica em um paralelismo na busca por soluções. Usualmente, cada indivíduo representa (ou codifica) um ponto de busca no espaço de potenciais soluções para um dado problema. A essa população é aplicado um processo de evolução, permitindo através de várias gerações, o surgimento de soluções melhores que as anteriores. Algoritmos Evolutivos não são garantia para a obtenção de soluções ótimas, ao lidar-se com amplos e complexos espaços de busca, a otimalidade pode ser algo de difícil obtenção sendo possível esperar-se soluções satisfatórias.

Aplicações envolvendo Computação Evolutiva recaem em uma ampla gama de áreas, tais como planejamento, projeto, simulação e identificação, controle e classificação (Bäck *et al.*, 2000). Os principais algoritmos evolutivos disponíveis atualmente são:

- Algoritmos Genéticos (AG)

- Estratégias Evolutivas (EE)

- Programação Evolutiva (PE)

- Programação Genética (PG)

- Sistemas Classificadores (SC)

Com base na teoria neo-Darwiniana da evolução das espécies, é possível propor um algoritmo evolutivo básico ou padrão com as seguintes características:

- Uma população de candidatos a darem solução (denominados indivíduos ou cromossomos) que se reproduz com herança genética. Onde cada um dos indivíduos da população corresponde a uma estrutura de dados que representa ou codifica um ponto em um espaço de busca. Os indivíduos se reproduzem de forma sexuada ou assexuada, gerando filhos que terão parte de seu material genético proveniente de seu(s) pai(s). Na reprodução sexuada em particular existe a troca de material genético (crossover ou recombinação) entre dois ou mais indivíduos pais. Já no caso da reprodução assexuada o filho ou os filhos serão cópias com variações que os diferenciarão de seus genitores.

- Variação genética: durante o processo reprodutivo os filhos, não apenas herdam as características paternas, como também podem sofrer mutações responsáveis por alterações em seu código genético.

- Seleção Natural: a avaliação dos indivíduos em seu ambiente através de uma função de avaliação ou *fitness* deste indivíduo. Os valores individuais de *fitness* são a base que resultará em uma competição pela sobrevivência e reprodução no ambiente. Os indivíduos com altos valores de *fitness* têm maior vantagem frente a indivíduos com *fitness* menores.

Devido ao foco do trabalho, os AG's serão abordados com maior ênfase. Demais informações a respeito dos algoritmos evolutivos citados até então podem ser encontradas em (Bäck et al., 2000) e (Zebulum et al., 2002).

#### Algoritmos Genéticos

Algoritmos genéticos são uma classe de algoritmos estudada e analisada primeiramente por John Holland (Holland, 1975). Seus objetivos eram a investigação de processos adaptativos em sistemas naturais, e a criação de programas de computador que mostrassem comportamento similar com respeito aos sistemas naturais investigados. Assim como os demais, estes algoritmos também possuem inspiração biológica utilizando-se de conceitos extraídos da teoria neodarwinista, como a genética.

AGs tornaram-se os mais populares algoritmos evolutivos devido à bem-sucedida aplicação na otimização de problemas de busca, particularmente naqueles problemas em que o tamanho ou a complexidade do espaço de busca torna impraticável o uso de outras técnicas de otimização (Zebulum *et al.*, 2002).

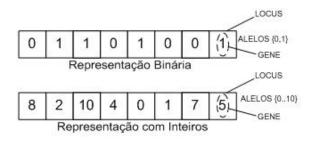

Existem três características que distinguem um AG dos demais algoritmos evolutivos: representação dos indivíduos utilizando *bitstrings*; método de seleção dos indivíduos proporcio-

nal ao seu valor de *fitness*; e o método primário de produção de variação e cruzamento genético (crossover) (Bäck et al., 2000). Dentre as três, contudo, a ênfase situada no crossover é que faz a distinção do AG frente aos demais algoritmos evolutivos. Algumas subseqüentes implementações de algoritmos genéticos tem optado por utilizar métodos alternativos de seleção tais como seleção por torneio ou rank e representações diferentes de bitstrings, como por exemplo a representação de indivíduos com valores inteiros ao invés de valores binários, em virtude de um melhor tratamento de problemas. Ao agrupamento de genes que representa uma solução no espaço de busca dá-se o nome de cromossomo. Exemplos de cromossomos podem ser vistos na figura 2.3 .

Figura 2.3: Cromossomos

Onde locus é a posição do gene no cromossomo e os alelos os valores que o gene pode assumir.

#### Mecanismos de Seleção, Cruzamento e Mutação

Os operadores genéticos utilizados no AG clássico como mecanismos evolutivos são o crossover de ponto único, a mutação e a seleção probabilística por roleta.

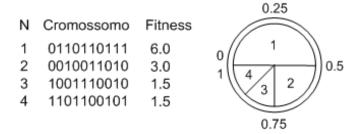

A seleção por roleta é um método que atribui a probabilidade de escolha de um indivíduo (para cruzamento e conseqüente propagação de material genético) ao seu valor de *fitness*, em outras palavras indivíduos com *fitness* mais elevados terão uma fatia maior da roleta, como mostrado na figura 2.4 . A roleta é um gerador de números pseudo-aleatórios com distribuição uniforme, com números gerados dentro do intervalo dado pela soma dos valores de *fitness* de todos os indivíduos.

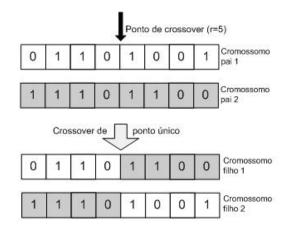

O operador de *crossover* realiza a mistura do material genético de dois pais pré-selecionados pelo operador de seleção dando origem a dois novos filhos, criando uma nova geração com novos indivíduos que possuem herança genética proveniente dos indivíduos pais (figura 2.5). Após esses indivíduos sofrerão pequenas modificações através de um processo de mutação.

Figura 2.4: Método da Seleção por Roleta

Figura 2.5: Crossover de ponto único

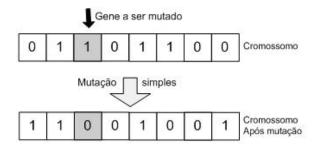

O operador de mutação realiza pequenas mudanças nos indivíduos da nova geração com o intuito de promover maior diversidade (figura 2.6) e não estagnar o processo evolutivo, o que vem a ser muito interessante para uma melhor exploração do espaço de busca evitando que a busca estagne em ótimos locais.

Figura 2.6: Mutação simples

As etapas de maior importância na utilização de algoritmos evolutivos, e conseqüentemente as que requerem maior atenção, são a codificação (a forma como as soluções serão representadas no AG) e a função de *fitness* que avaliará as soluções codificadas. Codificações e

funções de *fitness* mal elaboradas podem comprometer todo o processo evolutivo dentro de um AG, ou qualquer outro algoritmo evolutivo.

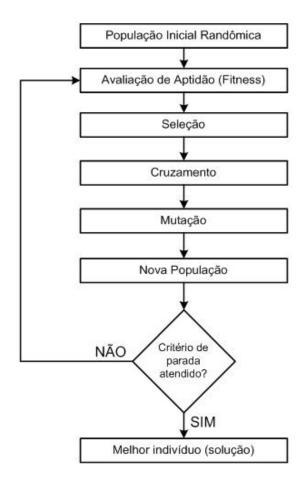

O diagrama da figura 2.7 mostra o fluxo básico dos algoritmos genéticos.

Figura 2.7: Diagrama de fluxo dos AG's

Os algoritmos genéticos são projetados para a simulação de evolução, não propriamente para resolver problemas. Contudo, a evolução traz consigo alguns projetos interessantes, mas deve-se ter em vista que, de fato, a evolução é um processo oportunista operando em um ambiente que está em constante mudança (Bäck *et al.*, 2000).

### 2.2 Hardware Evolutivo

### 2.2.1 Síntese de *Hardware* Digital

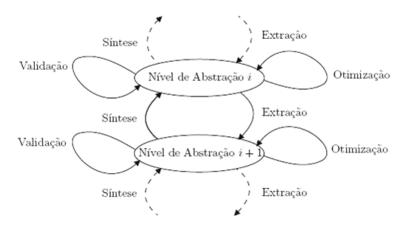

Projetos de sistemas digitais podem ser definidos como a transformação de uma descrição inicial do sistema (especificação) em uma descrição final. Isso se dá através de sucessivas etapas podendo envolver diversos tipos de níveis de abstração, onde a principal diferença está no fato desta última conter todas as informações necessárias a sua fabricação (Calazans, 1998). A manipulação destas etapas, chamada de projeto de *hardware*, pode ser classificada como síntese, extração, validação e otimização (Suzim, 1998), e pode ser observada no diagrama da figura 2.8.

Figura 2.8: Modelo de representação do processo de projeto de sistemas digitais proposto por Suzim

A operação de síntese é a tradução de uma descrição em um dado nível para uma descrição em nível inferior, que ocorre através do acréscimo de informação permitindo a criação de uma descrição menos abstrata. Já a operação de extração, gera uma descrição mais abstrata, com menos detalhes e características de implementação. Tanto a operação de síntese quanto a operação de extração ocorrem sobre descrições de um mesmo nível.

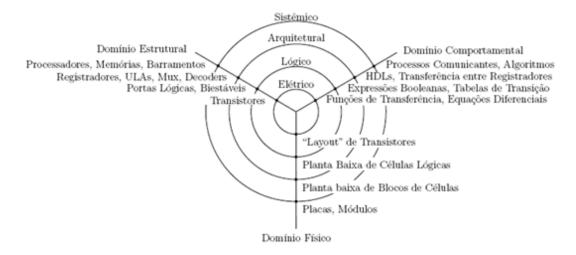

Pode-se encontrar diversas metodologias para representar um projeto de *hardware* sendo a mais comum o Diagrama Y, proposto inicialmente por Gajski e Kuhn (Gajski e Kuhn, 1983). Este diagrama tem o objetivo de estratificar o processo de projeto de sistema digitais em diferentes níveis de abstração e domínios de descrição (figura 2.9).

Nesta representação, os círculos correspondem aos níveis de abstração e os segmentos de retas correspondem aos domínios de descrição.

2.2 Hardware Evolutivo 14

Figura 2.9: Diagrama Y

Sistemas digitais podem ser geralmente classificados em quatro níveis diferentes de abstração: nível elétrico, como por exemplo, transistores e resistores, nível lógico aonde se encontram as portas lógicas, *flip-flops* e equações booleanas, o nível arquitetural aonde se pode exemplificar com ULAs e multiplexadores, e os níveis sistêmicos representados processadores, memórias e afins.

Além dos níveis de abstração é possível classificar as descrições em relação ao tipo de informação contida nelas. Dessa forma as descrições podem ser classificadas em três tipos diferentes: Físico, Comportamental e Estrutural. O tipo físico contém informações sobre os componentes/módulos, o tipo comportamental possui informações referentes ao comportamento do sistema, e o tipo estrutural que contém informações de interconexão entre os diversos blocos.

A região central do Diagrama Y corresponde à descrição onde se encontram todas as informações necessárias à fabricação do sistema, também chamada de descrição final. Cada intersecção de um círculo com um segmento de reta representa um tipo de descrição diferente. Automatizar as etapas de descrições acima é algo imprescindível na redução do tempo de projeto. Entretanto, à medida em que a escala de integração aumenta cresce a dificuldade em se obter projetos livres de erros (Calazans, 1998). Dessa forma, ferramentas para automatizar o processo de projeto deverão sofrer constante evolução.

### 2.2.2 Justificativas Vantagens e Aplicabilidade

Com a evolução da eletrônica, circuitos integrados cada vez mais complexos e de grande escala de integração são produzidos visando atender um mercado interessado em dispositivos onde muitas vezes tamanho reduzido e baixo consumo são premissas inevitáveis.

A automação vem sendo usada na síntese de circuitos por muitos anos. Um projeto simples e tradicional de circuitos digitais envolve o desenvolvimento de um circuito aplicado a uma tecnologia específica com a utilização de técnicas de minimização, além de algumas regras de posicionamento e de roteamento (placement and routing rules) (Campos et al., 2006).

Em decorrência do crescimento da indústria eletrônica e de problemas de projeto tais como escalabilidade, roteamento, tempo de desenvolvimento, confiabilidade entre outros, técnicas utilizadas para o projeto de circuitos no passado tornaram-se obsoletas, sendo que as técnicas clássicas atuais muitas vezes não conseguem manter uma taxa de crescimento análoga. Na atualidade projetos de *hardware* exigem a capacidade de sintetizar circuitos cada vez mais complexos, gerando a necessidade de técnicas mais aprimoradas, que resolvam problemas combinatórios com alto grau de complexidade e em tempo hábil.

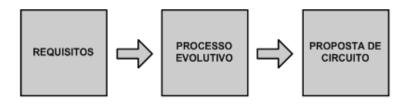

Dessa forma, o hardware evolutivo ou EHW (Evolvable Hardware) propõe a automatização de circuitos eletrônicos visando prover soluções mais generalizadas. EHW é uma área de pesquisa recente, formalizada em 1997 em um encontro de pesquisadores na Universidade de Napier, Escócia (Zebulum et al., 2002). Ela propõe a utilização de algoritmos evolutivos para o projeto de circuitos eletrônicos, unindo eletrônica e Computação Evolutiva com o objetivo de automatizar o processo e síntese de circuitos digitais ou analógicos, a partir de sua descrição comportamental (figura 2.10).

Figura 2.10: Processo EHW

Usar evolução para o projeto de circuitos pode trazer benefícios importantes como à automação e a descoberta de novos circuitos e arquiteturas não antes realizadas para uma escala crescente de aplicações. Além dessas técnicas poderem minimizar consumo, volume e custo dos circuitos projetados.

2.2 Hardware Evolutivo 16

Eletrônica Evolutiva lida com enormes espaços de busca, requerendo, portanto, sofisticadas técnicas para tal. Naturalmente, quando o espaço de busca é muito amplo, somente buscas aleatórias têm alguma chance de ter sucesso (Zebulum *et al.*, 2002). Contudo, alguns procedimentos devem ser seguidos:

- O espaço de busca amostrado pelo algoritmo deve ter tamanho limitado. Embora seja importante amostrar uma ampla variedade de topologias, alguns critérios devem ser escolhidos para controlar o número de possíveis soluções.

- Geralmente é necessário adaptar as técnicas de busca para as particularidades do projeto problema.

Pode-se descrever as mais notáveis características de circuitos evoluídos observada em pequena ou grande escala como sendo:

- Potencial de encontrar novos circuitos.

- Possibilidade de encontrar novas regras de projeto a partir de novos circuitos obtidos.

- Métodos evolutivos podem contemplar um grande conjunto de especificações de projeto comparado com técnicas de projetos feitos por humanos.

- Sistemas evolutivos são hábeis em conseguir circuitos competitivos quando comparado a outros circuitos existentes no estado atual da arte da eletrônica.

Dentre as características citadas acima, a terceira deve ser enfatizada. Atualmente, é importante conseguir circuitos eletrônicos que atendam a muitas especificações: bom desempenho; área reduzida; baixo consumo de energia; velocidade; e em alguns casos, tolerância a falhas. Métodos convencionais de projeto geralmente não são apropriados quando muitas especificações são consideradas.

Algoritmos evolutivos podem explorar algumas regiões do espaço de projeto que estão além do escopo dos métodos convencionais, como por exemplo o mapa de Karnaugh ((Karnaugh, 1953)) e a álgebra Booleana.

#### 2.2.3 Funcionamento da Técnica

Em Hardware Evolutivo um algoritmo evolutivo, geralmente o algoritmo genético, é aplicado a uma população de indivíduos (soluções candidatas) codificados na forma de cromossomos, onde cada um deles representa um circuito eletrônico. Usualmente esses indivíduos são strings binárias de comprimento fixo e estão contidos em uma população de tamanho constante. É importante salientar que outras abordagens utilizando outros algoritmos evolutivos podem ser encontradas, como a utilização de programação evolutiva por Coello (Coello et al., 1996) onde os autores utilizam uma codificação em árvore baseada em multiplexadores para síntese de funções lógicas. Outra abordagem é a proposta por Levi (Levi, 2000), utilizando um algoritmo híbrido intitulado HereBoy.

Ao se iniciar o processo evolutivo, os valores internos dos cromossomos da primeira população são gerados aleatoriamente. A avaliação dos cromossomos (fitness) é obtida através da evolução extrínseca, sendo os circuitos simulados em computador, ou através de evolução intrínseca, aonde os circuitos são implementados em dispositivos físicos reconfiguráveis (usualmente FPGA's), e mais recentemente em evolução mixtrínseca onde os circuitos são evoluídos parte em software e parte em hardware. A aptidão do circuito em atingir seu objetivo é avaliada através da inserção de um conjunto de determinados valores de entrada, e a observação das respostas dos sinais de suas saídas. O operador de seleção presente no processo é probabilístico, de forma que os cromossomos com maior aptidão terão maiores chances de serem selecionados. Após isso, os operadores evolutivos são aplicados aos cromossomos selecionados, tais como crossover e mutação para a geração da nova população.

De forma geral, EHW é um processo exploratório de busca em um domínio pré-estabelecido, visando obter o indivíduo com as melhores características dentre todas as iterações efetuadas pelo algoritmo.

A utilização de algoritmos evolutivos no projeto de circuitos eletrônicos, como visto neste capítulo, é uma ferramenta alternativa que pode ser muito interessante em algumas aplicações de engenharia. O próximo capítulo aborda o tema de circuitos lógicos reconfiguráveis, linguagem descritiva de hardware e noções de controle com aplicação ao problema do pêndulo.

# Capítulo 3

# LÓGICA RECONFIGURÁVEL E A LINGUAGEM DE DESCRIÇÃO DE HARDWARE VHDL

## 3.1 Field Programable Gate Array

Os *chips* FPGA (Field Programable Gate Array) são circuitos eletrônicos integrados que possuem uma engenharia de reconfiguração interna permitindo a implementação de circuitos lógicos. Esses chips pertencem à classe dos dispositivos lógicos reprogramáveis.

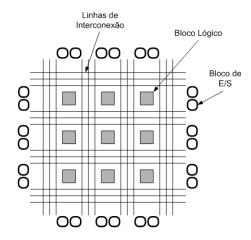

O termo dispositivo lógico programável (*Program Logic Device* - PLD) refere-se a qualquer tipo de circuito usado para implementar circuitos digitais, onde o dispositivo pode ser configurado pelo usuário para realizar uma vasta gama de projetos (Brow e Rose, 1996) . A configuração de um PLD freqüentemente envolve a colocação do componente em uma unidade especial de programação, mas alguns componentes também podem ser configurados pelo próprio sistema (*in-system*).

Os PLD's para propósitos gerais com maior densidade disponíveis na atualidade são os conhecidos como FPGA's. Os FPGA's são constituídos por um conjunto de elementos de circuitos, chamados de elementos lógicos (logic elements - LE's), circundados por blocos de entrada e saída (E/S) (figura 3.1). Os LEs implementam funções lógicas simples, e seus blocos de E/S são conectados entre si por meio de interconexões programáveis. Essas interligações programáveis permitem que diversos LE's possam ser conectados para implementar circuitos

sequenciais e/ou combinacionais complexos.

Figura 3.1: Estrutura Básica de um FPGA

## 3.1.1 Projetos Utilizando Dispositivos Lógicos Programáveis

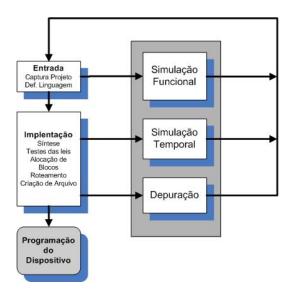

O projeto de sistemas digitais destinados a implementação em dispositivos lógicos programáveis é realizado por ferramentas que pertencem a uma classe denominada de EDA (*Eletronic Design Automation*). Uma ferramenta de EDA para PLD típica inclui programas para as seguintes tarefas: entrada inicial para o projeto, otimização, adequação ao dispositivo, simulação e configuração (figura 3.2).

Figura 3.2: Fluxo de projeto lógico programável

Existem algumas ferramentas computacionais usuais e apropriadas para a realização da entrada de projeto. Alguns projetistas preferem a entrada através de esquemáticos, enquanto outros preferem o uso das linguagens de descrição de hardware (Hardware Description Languages - HDL), tais como Verilog e VHDL.

Tradicionalmente, as ferramentas baseadas em diagramas esquemáticos propiciam maior controle sobre o particionamento e posicionamento da lógica do dispositivo. Porém, tal benefício vem em detrimento do tempo gasto na realização do projeto, uma vez que ele é executado no nível de portas lógicas (Nicolato, 2002). Em contrapartida, as ferramentas baseadas em linguagens HDL permitem que o projeto seja realizado num nível de abstração mais elevado (por ex. descrição comportamental em VHDL), possibilitando maior agilidade no processo de desenvolvimento de projetos digitais. As desvantagens comuns a tais linguagens são a diminuição do desempenho e a densidade lógica necessária (quantidade de lógica implementada por área do componente).

Atualmente, os principais fabricantes de PLDs disponibilizam bibliotecas de funções (em alguns casos, parametrizadas) básicas tais como somadores, multiplicadores, multiplicadores, memórias etc, que podem ser "chamadas" a partir de editores de esquemáticos ou instanciadas por meio de HDL. Adicionalmente, há uma ampla pesquisa sobre tradutores que fazem a conversão de programas escritos em linguagem de alto nível para níveis lógicos inferiores (Sankaran e Haggard, 2001).

A verificação ocorre em vários níveis, e durante vários passos do procedimento, dependendo dos critérios adotados pelo projetista. Existem alguns tipos básicos de verificação quando são utilizados dispositivos de lógicas programáveis. A simulação funcional é realizada em conjunto com a entrada do projeto, mas antes do posicionamento e roteamento, objetivando a verificação de sua funcionalidade lógica. A simulação considerando as características de temporização é realizada em uma etapa posterior ao posicionamento e roteamento. Nesse passo, o programa de desenvolvimento determina os atrasos do circuito, possibilitando a verificação completa de sua temporização.

Uma boa técnica para projetos com lógica programável é, primeiramente, realizar uma simulação funcional para determinar o funcionamento correto do circuito, verificar a temporização e, finalmente, verificar a funcionalidade completa testando-o no sistema, incluindo dispositivos físicos e as exigências ambientais da aplicação (Nicolato, 2002).

Muitos dispositivos de lógica programável têm a grande vantagem de poderem ser programados, ou re-programados, no sistema, isto é, não necessitam de uma unidade especial de

programação. Assim, o projeto pode ser facilmente verificado no sistema real, reduzindo a necessidade da criação de vetores de simulação muito complexos.

Depois da criação do arquivo de programação, o dispositivo é configurado e estará pronto para operar. O método de programação depende da tecnologia dos componentes alvo. Algumas tecnologias, por exemplo as PROMs (*Programable Read Only Memory*), requerem algum tipo de dispositivo de programação. Dispositivos que podem ser programados no sistema nem sempre necessitam de um programador físico externo, mas requerem algum tipo de recurso para carregar o arquivo de programação no *chip*. Isso pode ser realizado com o auxílio de um microprocessador, microcontrolador ou via portas no padrão JTAG.

Seja qual for o fabricante ou a tecnologia, é importante ressaltar que o conhecimento da arquitetura do componente, bem como das ferramentas de projeto são muito importantes para obtenção de bons resultados.

### 3.2 A Linguagem VHDL

A linguagem VHDL (Very High Description Language) é uma linguagem usada para descrever a arquitetura e o comportamento de circuitos eletrônicos. Essa linguagem representa uma alternativa à descrição de circuitos através de diagramas elétricos ou esquemáticos.

Historicamente, o desenvolvimento da linguagem de descrição de circuitos VHDL deveuse à necessidade de uma ferramenta de projeto e documentação padrão para o projeto VHSIC (Very High Speed Integrated Circuit), do Departamento de Defesa dos Estados Unidos da América (DARPA). No começo da década de oitenta, mas precisamente em 1981, esse departamento patrocinou um encontro de especialistas para discutir métodos para descrição de circuitos. Em 1983, o Departamento de Defesa definiu os requisitos de uma linguagem de descrição de circuitos padrão e concedeu às firmas "IBM", "Texas" e "Intermetrics" um contrato para o desenvolvimento da linguagem e ferramentas.

VHDL suporta projetos com múltiplos níveis de hierarquia, dessa maneira a descrição pode consistir na interligação de outras descrições menores, a um código que representa o comportamento esperado do circuito. Esses estilos são denominados estrutural e comportamental, e podem ser mesclados em uma mesma descrição. A estrutura hierárquica e a opção de combinar diversos estilos de descrição facilitam a condução de projetos complexos que partem de um nível mais elevado para um nível mais baixo de especificação, conhecidos como top down design ((d'Amore, 2005)).

#### 3.2.1 Entidade de Projeto

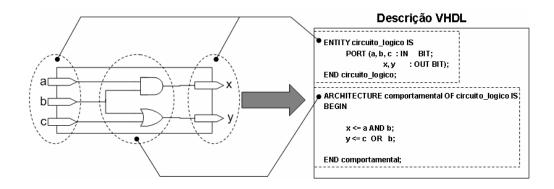

Uma entidade de projeto, ou design entity, pode representar desde uma simples porta lógica a um sistema completo, e é composta de duas partes: declaração da entidade (Entity) e arquitetura (architecture). A declaração de entidade especifica a interface entre a entidade e o ambiente exterior, como, por exemplo, entradas e saídas. A arquitetura possui a definição das relações entre as entradas e saídas de uma entidade. A figura 3.3 ilustra uma representação de circuito lógico em VHDL exibindo um código básico e as relações entidade/arquitetura com o circuito descrito por ele. A analogia normalmente feita com um projeto em captura esquemática, objetiva comparar a declaração da entidade ao símbolo de um bloco, e a arquitetura ao esquema contido no bloco.

Figura 3.3: Descrição VHDL de Circuito Lógico

A linguagem VHDL é estruturada e tem sua sintaxe semelhante à linguagem de programação Pascal. Com exceção de regiões específicas, todos os comandos são executados de forma concorrente, ou seja, paralelamente. Isto significa que a ordem em relação a apresentação dos comandos é irrelevante para o comportamento da descrição. A ocorrência de um evento em um sinal leva à execução de todos os comandos sensíveis àquele sinal, da mesma forma que, em um circuito, a mudança de um valor em um determinado nó afeta todas as entradas ligadas a esse ponto do circuito.

Como o código é concorrente, a mudança de valor em "b" na figura 3.3, leva à execução em paralelo dos comandos contidos nas linhas 8 e 9. A ordem da avaliação dos comandos executada pelo simulador é irrelevante, e o resultado será sempre o mesmo. As operações internas executadas pelo simulador, contudo, são efetuadas de forma seqüencial. Dessa forma, a ferramenta de simulação necessita de um mecanismo interno para armazenar o resultado de cada comando, até que a avaliação de todos os comandos envolvidos tenho sido realizada.

A linguagem VHDL também permite delimitar regiões de código executados sequencialmente, onde a execução dos comandos se dá na ordem de sua apresentação no código. Para essas regiões são usados comandos específicos, que não podem ser empregados na região de código concorrente. Subprogramas e processos são regiões de código seqüencial.

#### 3.2.2 Síntese de Circuitos Usando VHDL

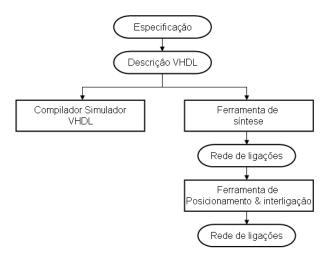

Originalmente, VHDL não foi criada para a síntese de circuitos digitais; assim, nem todas as construções definidas são suportadas pelas ferramentas de síntese. As limitações devem-se a falta de correspondência da construção com um circuito digital, à impossibilidade da síntese com precisão, ou à falta de detalhamento para um síntese direta. Essas limitações não devem ser consideradas como um problema da ferramenta de síntese ou da linguagem, mas sim uma falha na própria descrição que está muito afastada de um circuito real ((d'Amore, 2005)). Por exemplo, um projetista pode descrever no código um elemento de memória sensível tanto a transição de subida quanto a transição de descida de um sinal de clock. Do ponto de vista do simulador VHDL, a descrição pode ser simulada sem problemas; entretanto, a ferramenta de síntese poderá não ter sucesso em sintetizar a descrição devido a ausência de um elemento desse tipo no mundo real. Os três passos em um projeto empregando uma linguagem de descrição de hardware podem ser vistos na figura 3.4.

Figura 3.4: Etapas de um projeto

A partir da especificação de um projeto, é gerada uma descrição VHDL, que é submetida a um simulador para a verificação da correspondência entre a especificação e o código. A mesma descrição é interpretada por uma ferramenta de síntese que infere as estruturas necessárias para

um circuito que corresponda à descrição. Como resultado dessa etapa obtém-se um arquivo contendo uma rede de ligações de elementos básicos disponíveis na tecnologia do dispositivo empregado. Esses elementos atuam como blocos construtivos realizando a implementação física do modelo descrito pela linguagem. O arquivo contendo a rede de ligações é a base de dados para a ferramenta que realiza o posicionamento e a interligação dos componentes, place and route. A saída da ferramenta de posicionamento e interligação é um arquivo contendo os dados necessários para confecção do circuito no dispositivo usado para a síntese.

Para um maior aprofundamento sobre o tema de síntese de circuitos por VHDL são sugeridas as bibliografias de d'Amore (2005) e Perry (2002).

Neste capítulo foram abordados os temas de hardware reconfigurável (FPGAs) e linguagem de descrição de hardware (VHDL), ambas ferramentas amplamente usadas na implementação do sistema de controle que será detalhado nos próximos capítulos.

## Capítulo 4

# CONTROLE APLICADO AO PÊNDULO

#### 4.1 Sistemas Automáticos

Uma definição de sistema pode ser dada como sendo todo conjunto de elementos interrelacionados, aonde o comportamento individual de cada elemento afeta o sistema como um todo. Observe que se faz referência a elementos, não a objetos ou peças, isso porque um sistema não tem que ser obrigatoriamente físico, tangível. Sistemas podem muito bem estarem conformados por unidades de informação, leis abstratas e vários outros "elementos" não físicos.

Todo sistema físico denomina-se genericamente de planta. Toda planta tem um determinado comportamento, isto é, executa uma determinada ação (Pazos, 2002). Genericamente, representa-se a planta, sua resposta (saída y(t)) e excitação (entrada u(t)) como no diagrama da figura 4.1.

Figura 4.1: Conceito de planta

Um exemplo de sistema físico pode ser o de uma simples alavanca, aonde existe uma relação entre o torque de saída e o torque de entrada, que depende do ponto de apoio na alavanca.

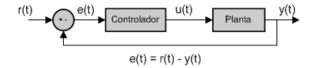

#### 4.2 Sistema de Controle em Malha Fechada

Os sistemas de controle em malha fechada, ou realimentados, são sistemas que utilizam como base o sinal de erro atuante, que é a diferença entre o sinal de realimentação (que pode ser o próprio sinal de saída ou uma função do sinal de saída e suas derivadas e/ou integrais) e o sinal de referência. O controlador objetiva minimizar o erro e ajustar a saída ao valor desejado informado no sinal de referência. O diagrama da figura 4.2 ilustra um sistema em malha fechada.

Figura 4.2: Diagrama de sistema de controle em malha fechada

Onde r(t) corresponde ao sinal de referência, u(t) o sinal de controle para a planta (sistema a ser controlado), y(t) a resposta do sistema com base no sinal de controle e e(t) o sinal de erro.

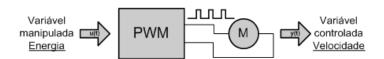

#### 4.3 Controle do Pêndulo

Na teoria de controle existem basicamente dois tipos de variáveis em um sistema, a variável controlada e a variável manipulada. A variável controlada é a grandeza ou a condição que é medida e controlada. A variável manipulada é a grandeza ou a condição modificada pelo controlador, de modo que afete o valor da variável controlada (Ogata, 2006). A figura 4.3 ilustra esse conceito mostrando o acionamento de um motor CC por PWM.

Figura 4.3: Acionamento por PWM

No sistema implementado neste trabalho o controle do pêndulo se dá através de alterações no fluxo de energia entregue a ele, que neste caso é a variável manipulada no sistema. O controle de energia resulta em ajustes na posição da haste do pêndulo, com base no comportamento do sistema dinâmico existente entra as variáveis controlada e manipulada. Dessa

maneira, a entrada do sistema (sinal de referência) é uma informação que indica a posição que a haste deve se manter, e o sistema de controle responde a essa entrada deslocando a haste até a posição especificada.

Uma abordagem mais aprofundada sobre a área de controle de sistemas dinâmicos pode ser vista em Ogata (2006) e Nise (2004).

### 4.4 Especificações Técnicas

Entende-se por especificações técnicas o conjunto de requerimentos ou exigências definidas pelo usuário do sistema com respeito ao seu comportamento, ou como ele quer que se comporte o sistema a controlar (Pazos, 2002). Em geral, uma primeira especificação técnica mínima exigida é que o sistema seja estável. Se o sistema não o for naturalmente, o controle deverá fazer com que se comporte como tal. Uma outra especificação pode ser o percentual de overshoot, ou relação entre o valor máximo da resposta sobre o seu valor final, e o seu valor final (valor quando  $t \to \infty$ ).

### 4.5 Pêndulo Amortecido

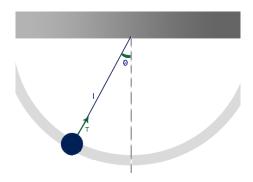

Em mecânica, um pêndulo simples é um instrumento ou uma montagem que consiste em um objeto que oscila em torno de um ponto fixo, realizando um movimento bidimensional no plano xy caracterizado por uma função seno. O braço ou haste executa movimentos alternados em torno da posição central, chamada posição de equilíbrio (figura 4.4).

Figura 4.4: Ilustração de pêndulo simples

O termo "amortecido" é dado ao sistema de movimento oscilatório cujo movimento sofre

resistência devido a uma força contrária de atrito, como é o caso do pêndulo como objeto mecânico real.

O pêndulo é um modelo clássico utilizado no estudo de juntas robóticas de sistema manipuladores e como excelente meio para testes de técnicas de controle avançadas para sistemas não lineares. O modelo matemático de movimento do pêndulo pode ser expresso pela equação 4.1.

$$ml^2\theta'' + kl^2\theta' + mgl\sin(\theta) = \tau \tag{4.1}$$

Sendo m a massa concentrada em seu centro de massa, g a aceleração da gravidade, k a viscosidade do meio e l o comprimento da haste do pêndulo.

### 4.6 Controlador Proporcional, Integral e Derivativo

Este tipo de controle consiste em uma estratégia onde é aplicada à planta um sinal de excitação proporcional ao erro, somado à sua função derivada e sua função integral.

O controle PID é a estratégia de controle mais genérica e provavelmente uma das mais utilizadas. Fornece resposta rápida, bom controle de estabilidade do sistema e baixo erro de regime permanente para sistemas de até segunda ordem. Tais vantagens acontecem porque o controle PID permite adaptar o sistema realimentado geral (sistema planta-controlador), quase que idealmente seja qual for o modelo da planta (Pazos, 2002).

O PID discreto pode ser implementado de diferentes formas. As estruturas PIDs discretas mais comuns são o controlador proporcional (equação 4.2), controlador Proporcional-Derivativo (equação 4.3), controlador proporcional Integral (equação 4.4) e controlador proporcional - integral - derivativo (equação 4.6).

$$u(n) = Kpe(n) \tag{4.2}$$

$$u(n) = \left[Kp + \frac{Kd}{Ts}\right]e(n) - \frac{Kd}{Ts}e(n-1)$$

(4.3)

$$u(n) = u(n-1) + \left[ Kp + \frac{KiTs}{2} \right] e(n) + \left[ -Kp + \frac{KiTs}{2} \right] e(n-1)$$

(4.4)

$$u(n) = u(n-1) + \left[ Kp + \frac{Kd}{Ts} + \frac{KiTs}{2} \right] e(n) + \left[ \frac{KiTs}{2} - Kp - 2\frac{Kd}{Ts} \right] e(n-1) + \frac{Kd}{Ts} e(n-2)$$

(4.5)

sendo Kp,Kd e Ki os ganhos proporcional, diferencial e integral, respectivamente. Ts é o tempo de amostragem e e(n) descreve o sinal de erro, dado por:

$$e(n) = r(t) - y(t) \tag{4.6}$$

onde r(t) é o sinal de referência e y(t) é a variável do sistema.

O desempenho do controlador PID é dependente da sintonia de seus parâmetros, que em alguns casos pode ser uma tarefa complicada devido à presença de comportamento não linear na planta.

### 4.7 Técnica Utilizada no Projeto dos Controladores

Os controladores implementados aqui (Kp e EHW) são fruto do trabalho de doutorado desenvolvido por Campos (2007) cujo um dos objetivos foi o de aplicar técnicas evolutivas no projeto de controladores para pêndulo amortecido.

A função de fitness, responsável por avaliar as soluções com base em seu comportamento, foi definida utilizando um índice de desempenho baseado na integral do erro quadrático ISE (*Integral of the Square Error*) Eq. 4.7 usada como critério de minimização dos controladores desenvolvidos naquele trabalho. Esse índice foi escolhido por penalizar fortemente valores altos na variável de erro, e por possuir um bom tratamento matemático (Campos, 2007).

$$fitness = f(J_{ISE}) = \frac{1}{1 + J_{ISE}} \tag{4.7}$$

O controlador proporcional Kp teve seu ganho sintonizado através de um algoritmo genético utilizando uma codificação binária tradicional (figura 4.5). No projeto do controlador evolutivo, apenas o critério funcional foi usado como elemento de projeto, ou seja, apenas as entradas e as saídas produzidas pelo sistema foram consideradas, numa abordagem chamada de caixa preta. A estrutura interna do circuito digital do controlador não foi considerada, desse modo apenas ações que produzem uma saída notável são cobertas pela função de fitness do AG

(Campos, 2007).

$$(K_P, K_D, K_I) = \underbrace{010...00}_{K_P} \underbrace{101...01}_{K_D} \underbrace{111...10}_{K_I}$$

Figura 4.5: Codificação dos ganhos do controlador

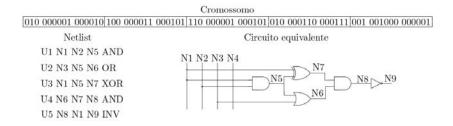

A codificação adotada para o controlador EHW consiste em um cromossomo binário formado por um conjunto de n segmentos, cada segmento representa uma porta lógica e é um nó do circuito digital formado pela função booleana, além de conter as informações sobre os nós que devem ser conectados às entradas da porta lógica por ele representada. Cada segmento é formado por uma palavra de 15 bits, sendo que os 3 primeiros bits designam o tipo de porta ou função do nó, seguido de um segmento de 6 bits que representa a conexão da primeira entrada e outro segmento de mesmo tamanho representando a conexão da segunda entrada. A biblioteca de portas suportada nos cromossomos é composta pela portas BUFFER, INV, AND, NAND, OR, NOR, XOR e XNOR.

A topologia é especificada por uma lista de tipos de componentes junto com seus nós terminais (PSPICE netlist). Os componentes não conectados são desconsiderados, o que possibilita ter um número de componentes variáveis em um circuito, embora o tamanho do cromossomo seja fixo. A figura 4.6 exibe uma ilustração do método de codificação para um circuito simples de 4 entradas.

Figura 4.6: Codificação netlist para controlador EHW

O primeiro passo na criação do circuito evolutivo é a geração de uma população inicial aleatório de cromossomos. Na evolução extrínseca os cromossomos são convertidos em um modelo simulado (SPICE) e são avaliados de acordo com as respostas geradas, por meio da função de fitness (Equação 4.7). Uma nova geração é então composta por novos indivíduos a partir de indivíduos selecionados na população anterior por uma técnica de seleção chamada de roleta com estratégia elitista. Para gerar novos cromossomos são aplicados os operadores de *crossover* e mutação (taxas de 100% e 5% respectivamente). O crossover de ponto único

recombina dois indivíduos a partir de uma posição escolhida aleatóriamente (chamado ponto de corte), trocando os bits das strings a partir deste ponto. Durante a operação de mutação os pontos são escolhidos, de acordo com a probabilidade de mutação, e os valores destes bits são invertidos. A partir daí uma nova geração de indivíduos foi criada e uma nova iteração pode ser criada. O processo repete-se até um circuito adequado seja encontrado ou até um número pré-determinado de iterações seja alcançado.

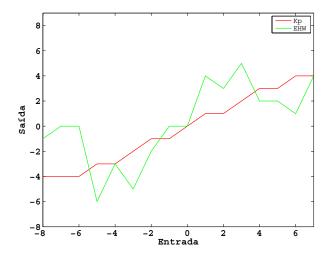

Como resultado deste processo, foram obtidos (dentre outros não abordados neste trabalho) um controlador Kp e um controlador EHW, ambos de 4 bits, para pêndulo não linear. A tabela 4.1 mostra o comportamento de ambos.

| Entrada | Saída Kp | Saída EHW |

|---------|----------|-----------|

| 0000    | 0000     | 0000      |

| 0001    | 0001     | 0100      |

| 0010    | 0001     | 0011      |

| 0011    | 0010     | 0101      |

| 0100    | 0011     | 0010      |

| 0101    | 0011     | 0011      |

| 0110    | 0100     | 0001      |

| 0111    | 0100     | 0100      |

| 1000    | 1100     | 1111      |

| 1001    | 1100     | 0000      |

| 1010    | 1100     | 0000      |

| 1011    | 1101     | 1010      |

| 1100    | 1101     | 1101      |

| 1101    | 1110     | 1011      |

| 1110    | 1111     | 1110      |

| 1111    | 1111     | 0000      |

Tabela 4.1: Tabela verdade Kp e EHW

A figura 4.7 exibe um gráfico comportamental onde é possível observar melhor a característica não-linear do controlador evolutivo. Isso decorre da característica do algoritmo genético em otimizar funções não-lineares através de buscas conduzidas por um aprendizado experimental. O controlador proporcional, cuja função está representada pela cor vermelha no gráfico da figura 4.7 exibe um comportamento linear em resposta a entrada dos sinais de erro. Dessa forma, um tratamento linear é aplicado a um problema com comportamento não-linear, e isso ocorre devido às características intrínsecas dos controladores PID e suas variações (Equação 4.2, 4.3, 4.4 e 4.6). No controlador evolutivo, representado pela cor verde, observa-se uma função não linear em resposta ao sinal de erro. Esse comportamento é reflexo da evolução do

circuito controlador, que provê alterações adaptativas no projeto do circuito com base em suas experiências de controle frente ao problema proposto.

Figura 4.7: Comportamento dos controladores Proporcional e EHW

A técnica de Hardware Evolutivo foi vista nesse capítulo como uma abordagem alternativa ao problema de controle de sistemas dinâmicos. O controlador evolutivo obtido possui uma abordagem caixa preta, cuja função de controle foi conseguida através de um processo heurístico por meio de um AG. No capítulo a seguir serão mostrados detalhes da aplicação dos controladores e os resultados experimentais dos testes realizados em bancada.

## Capítulo 5

# APLICAÇÃO E RESULTADOS EXPERIMENTAIS

### 5.1 Implementação Física do Sistema de Controle

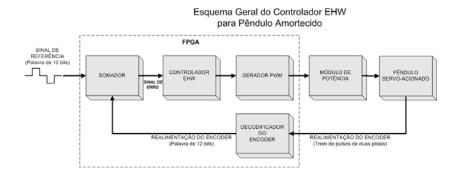

Como citado anteriormente, o objetivo deste trabalho é o de implementar fisicamente um modelo teórico de controle de pêndulo em malha fechada, obtido através da técnica de *hardware* evolutivo e sintonia de controlador proporcional por algoritmo genético (Campos, 2007).

Para criar um modelo físico com base no modelo simulado primeiramente é necessário estudar o modelo proveniente de simulação a fim de obter-se informações que serão usadas na escolha de quais componentes serão necessários, e conseqüentemente utilizados, no projeto físico do sistema de controle experimental. A figura 5.1 exibe um diagrama geral de todo o sistema experimental criado com base no modelo teórico proposto por Campos (2007).

Figura 5.1: Diagrama geral do controlador

#### 5.1.1 Pêndulo Servo Acionado

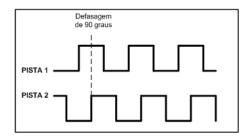

O objeto alvo do controle é um pêndulo mecânico desenvolvido no Laboratório de Sistemas Modulares Robóticos (LSMR) da FEEC - Unicamp e possui uma haste de 28,5 cm de comprimento e um conjunto de engrenagens de redução acionadas por um motor CC alimentado com 24 volts (figura 5.2). A este motor é acoplado um *encoder* óptico incremental marca HP modelo HEDS-6310 formando assim o sistema servo-motor. Este *encoder* possui 1000 pulsos de resolução e dois canais defasados em 90° cada, para informação do sentido de rotação.

Figura 5.2: Pêndulo servo-acionado

A haste do pêndulo move-se no sentido horário e anti-horário dependendo de como a polarização é aplicada nos terminais do motor CC. Como se trata de um motor de corrente contínua, a velocidade de rotação e conseqüentemente de deslocamento angular da haste são dependentes, dado o modelo dinâmico do pêndulo, do nível de corrente aplicada aos terminais do motor (no caso deste sistema, níveis entre 0 e 24 volts).

#### 5.1.2 Alimentação do Sistema

A responsabilidade do suprimento de energia para o sistema foi dividida entre duas fontes simétricas de tensão contínua. A primeira fonte, uma fonte variável da marca ICEL modelo PS5000D (figura 5.3) com saída variável de 0 a 30 Volts e fornecimento máximo de 6 Amperes de corrente contínua, foi usada para alimentar o circuito de potência acionador do pêndulo.

A segunda fonte é uma fonte simétrica chaveada padrão ATX usada na alimentação de microcomputadores arquitetura IBMPC e compatíveis (figura 5.4). Essa fonte é usada na alimentação do circuito analógico de bufferização que interconecta os vários sinais de controle do sistema.

Figura 5.3: Fonte do acionador do pêndulo

Figura 5.4: Fonte do circuito de interfaceamento

#### 5.1.3 Circuito de Interfaceamento