# **Paulo Augusto Dal Fabbro**

# PROJETO DE UM AMPLIFICADOR DE INSTRUMENTAÇÃO CMOS INTEGRADO

Dissertação apresentada à Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas, como requisito parcial à obtenção do título de **Mestre em Engenharia Elétrica**.

Área de Concentração: Microeletrônica

Orientador: Prof. Dr. Carlos Alberto dos Reis Filho

#### Banca Examinadora:

Prof. Dr. Carlos Alberto dos Reis Filho – DSIF/FEEC/UNICAMP

Prof. Dr. José Antenor Pomilio – DSCE/FEEC/UNICAMP

Dr. Saulo Finco – CenPRA/Campinas

Departamento de Semicondutores, Instrumentos e Fotônica Faculdade de Engenharia Elétrica e de Computação Universidade Estadual de Campinas Campinas, 29 de novembro de 2002.

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

D15p

Dal Fabbro, Paulo Augusto

Projeto de um amplificador de instrumentação CMOS integrado / Paulo Augusto Dal Fabbro.--Campinas, SP: [s.n.], 2002.

Orientador: Carlos Alberto dos Reis Filho. Dissertação (mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Circuitos eletrônicos - Projetos. 2. Circuitos integrados lineares. 3. Amplificadores eletrônicos. 4. Microeletrônica. I. Reis Filho, Carlos Alberto dos. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

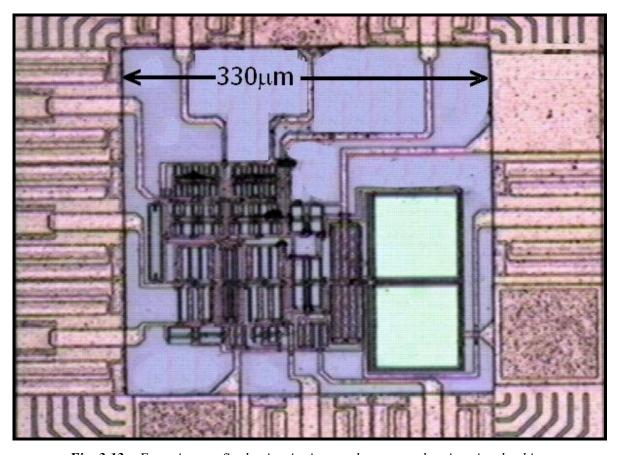

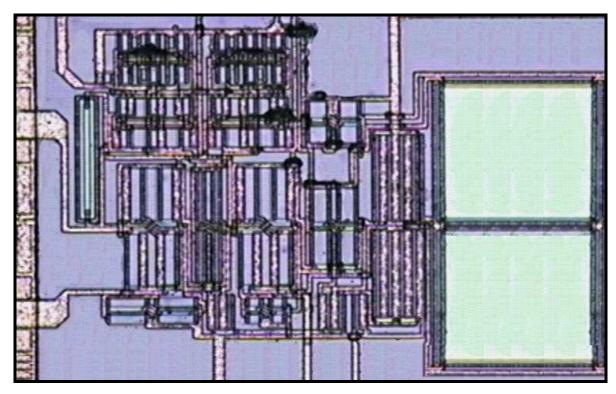

Este trabalho descreve o projeto de um amplificador de instrumentação integrado utilizando-se tecnologia CMOS 0,6μm. Os blocos básicos que compõem o circuito são descritos, explicitando-se o papel que cada um deles desempenha para garantir a performance desejada, cujo principal aspecto é uma alta rejeição de modo comum. São apresentados cálculos que levam ao dimensionamento dos dispositivos envolvidos. Algumas simulações são feitas com o intuito de validar esses cálculos, principalmente em relação ao comportamento do amplificador em freqüência. Segue, então, uma descrição dos cuidados tomados durante a fase de *layout* do circuito integrado (CI), na qual visou-se minimizar o efeito das imperfeições introduzidas pelo processo de fabricação do CI. Enfim, são apresentados os resultados experimentais obtidos para as amostras do circuito integrado fabricadas. Dentre eles, destaca-se uma CMRR (razão de rejeição de modo comum ou *Common Mode Rejection Ratio*) de 110dB medida para o amplificador de instrumentação operando com ganho 10 numa faixa de até 100kHz. Além disso, o amplificador de instrumentação ainda apresenta um produto ganho banda de aproximadamente 1MHz e consome 1,1mW de potência. O circuito ocupa uma área ativa de 0,061mm².

# **ABSTRACT**

This work deals with the design of an integrated instrumentation amplifier using a standard 0.6µm CMOS technology. The basic blocks that form the entire amplifier are studied and their roles in its overall performance are depicted. In order to validate the design, simulation is performed whenever necessary, mainly for verifying the frequency behavior of the amplifier. The layout of the integrated circuit (IC) is drawn for its best performance, obeying some cautions for minimizing the effect of possible imperfections introduced by the fabrication process. Finally, the experimental results obtained for the fabricated IC samples are presented. A CMRR of 110dB was attained for a gain of 10 up to a 100kHz bandwidth among other measured features like a gain-bandwidth product of 1MHz and 1.1mW power consumption. The circuit occupies an active area of 0.061mm<sup>2</sup>.

Aos meus queridos pais:

José Lélis e Maria Therezinha

e aos meus queridos irmãos:

Fabiana, Marcos, Alexandre,

Mateus e Luís Gustavo,

que tanto amo, dedico

este trabalho.

# **AGRADECIMENTOS**

Ao documentar este trabalho que demorou pouco mais de dois anos para ser concluído, gostaria de deixar documentada, também, minha gratidão aos que me ajudaram a fazê-lo. Deste modo, agradeço ao professor Carlos Alberto dos Reis Filho pela oportunidade a mim oferecida de cursar este mestrado e de partilhar de sua sabedoria em projetar e analisar circuitos eletrônicos.

Agradeço também aos professores José Mario de Martino e José Antenor Pomilio por ter podido contar sempre com eles durante minha graduação e pós-graduação na UNICAMP.

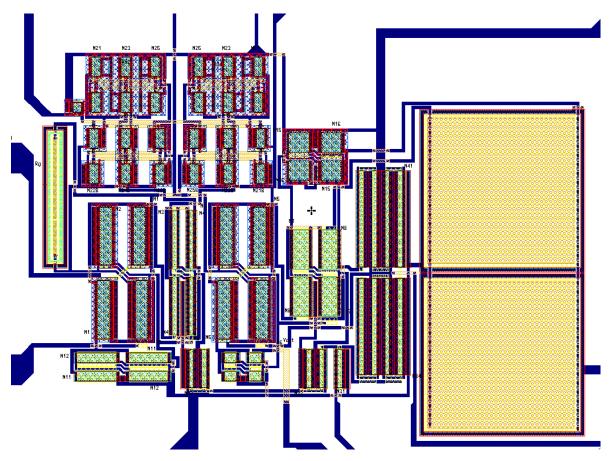

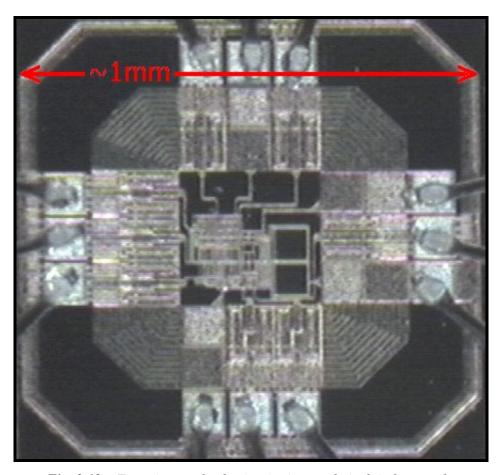

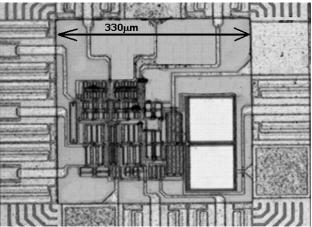

Agradeço ao CenPRA (antigo CTI) através de Saulo Finco, Carlos de Oliveira e Wellington R. de Melo pelas contribuições na etapa de desenvolvimento de *layout* do circuito integrado, pelo encapsulamento das amostras fornecidas e pelas fotomicrografias.

Agradeço ao Instituto de Pesquisas Eldorado pelo apoio financeiro.

Agradeço à Rose Meire da Silva, da Biblioteca da Área de Engenharia (BAE), por sua atenção e eficiência e a todos os funcionários da FEEC pelos serviços prestados.

Agradeço aos amigos do LPM2 pelo companheirismo e pelas discussões técnicas, estas últimas, principalmente ao Marcelo de Paula Campos e Marcos Maurício Pelícia.

Agradeço ao Murilo Pilon Pessatti, pela amizade de longa data, que correu do meu lado ao longo de todo este mestrado.

A todos meus demais amigos, que aqui não dei nomes, mas que com certeza estiveram em meu pensamento durante este trabalho.

Agradeço aos meus pais José Lélis e Maria Therezinha e meus irmãos Fabiana, Marcos, Alexandre, Mateus e Luís Gustavo pelo amor e pelo apoio incondicionais, aos meus sobrinhos Lorena e Ravi pela alegria de suas presenças e a todos meus demais familiares.

Finalmente, agradeço a Deus por me cercar de pessoas como estas e por me conceder dar mais este passo.

"Sempre que um homem de qualidades médias concentrar todas as suas faculdades num fim único, deverá atingi-lo".

Ferdinand Foch (1851-1929)

# NOTAÇÃO UTILIZADA

$W = \text{largura de canal do transistor MOS } [\mu \text{m}]$ L = comprimento de canal do transistor MOS [µm](W/L) = razão de aspecto do transistor MOS [µm/µm]  $v_{gs}$  = tensão porta-fonte incremental (gate-source voltage) do transistor MOS [V]  $v_{ds}$  = tensão dreno-fonte incremental (drain-source voltage) do transistor MOS [V]  $v_{bs}$  = tensão substrato-fonte incremental (body-source voltage) do transistor MOS [V]  $i_d$  = corrente de dreno incremental do transistor MOS [A]  $I_D$  = corrente de dreno quiescente do transistor MOS [A]  $V_{TN}$  = tensão de limiar para o transistor MOS canal-*n* (threshold voltage) [V]  $V_{TP}$  = tensão de limiar para o transistor MOS canal-p (threshold voltage) [V]  $\mu_N$  = mobilidade do elétron livre  $\mu_P$  = mobilidade da lacuna  $\chi$  = fator de efeito de corpo do transistor MOS  $\lambda$  = fator de modulação de canal do transistor MOS  $g_m$  = transcondutância do transistor MOS [A/V]  $g_{mb}$  = transcondutância de corpo do transistor MOS [A/V]  $r_o$  = resistência incremental de saída do transistor MOS [ $\Omega$ ]  $C_{gs}$  = capacitância porta-fonte do transistor MOS (gate-source capacitance) [F]  $C_{db}$  = capacitância dreno-substrato do transistor MOS (drain-body capacitance) [F]  $C_{gd}$  = capacitância porta-dreno do transistor MOS (gate-drain capacitance) [F] H = Transresistência [V/A]GM = Transcondutância [A/V] $A_{MC}$  = ganho de tensão de modo comum [V/V]  $A_{MD}$  = ganho de tensão de modo diferencial [V/V] SR = slew-rate [V/ $\mu$ s] ST = settling-time [s]

**THD** = distorção harmônica total (*Total Harmonic Distortion*) [%]

$V_{DS(sat)}$  = tensão dreno-fonte de saturação do transistor MOS [V]

$V_{OS}$  = Tensão de *offset* de entrada do amplificador de instrumentação [V]

**β**= ganho da malha de realimentação

$R_{\beta i}$  = resistência da malha de realimentação vista pela entrada do amplificador

$R_{\beta o}$  = resistência da malha de realimentação vista pela saída do amplificador

**GBW** = Produto Ganho-Banda (*Gain Band Width Product*)

# **SUMÁRIO**

| RESUMO/ABSTRACT                                                    | iii |

|--------------------------------------------------------------------|-----|

| AGRADECIMENTOS                                                     | v   |

| NOTAÇÃO UTILIZADA                                                  | vii |

| SUMÁRIO                                                            | ix  |

| INTRODUÇÃO GERAL                                                   | 1   |

| CAPÍTULO 1 – FUNDAMENTOS DE AMPLIFICADORES<br>DE INSTRUMENTAÇÃO    | 3   |

| 1.1. Introdução                                                    | 3   |

| 1.2. Princípios Básicos                                            | 3   |

| 1.3. Amplificador de Instrumentação com Op-Amps                    | 6   |

| 1.4. Técnica de Transferência de Corrente                          | 8   |

| 1.4.1. Amplificador de Instrumentação de Krabbe                    | 10  |

| 1.4.2. Amplificador de Instrumentação de Brokaw & Timko            | 11  |

| 1.4.3. Amplificador de Instrumentação de Martins, Selberherr e Vaz | 12  |

| 1.5. Conclusão                                                     | 15  |

| CAPÍTULO 2 - PROJETO DO AMPLIFICADOR DE INSTRUMENTAÇÃO             | 16  |

| 2.1. Introdução                                                    | 16  |

| 2.2. Tecnologia utilizada                                          | 16  |

| 2.3. O Circuito do Amplificador de Instrumentação                  | 17  |

| 2.3.1. Estágio Diferencial de Entrada                              | 19  |

| 2.3.1.1. Dimensionamento dos dispositivos envolvidos         | 23 |

|--------------------------------------------------------------|----|

| 2.3.2. Bloco de Transcondutância GM                          | 24 |

| 2.3.2.1. Dimensionamento dos dispositivos envolvidos         | 27 |

| 2.3.3. Estágio Diferencial de Saída                          | 27 |

| 2.3.3.1. Dimensionamento dos dispositivos envolvidos         | 30 |

| 2.3.4. Bloco Amplificador de Tensão AV                       | 30 |

| 2.3.4.1. Dimensionamento dos dispositivos envolvidos         | 34 |

| 2.3.5. Elemento de Transferência de Corrente                 | 35 |

| 2.3.5.1. Dimensionamento dos dispositivos envolvidos         | 39 |

| 2.4. Ajustes de Dimensionamento por Simulação                | 39 |

| 2.5. Análise em Freqüência                                   | 40 |

| 2.5.1. Circuito de Entrada (Amplificador de Transcondutância | 41 |

| 2.5.2. Circuito de Saída (Amplificador de Transresistência)  | 48 |

| 2.5.3. Simulação do Amplificador de Instrumentação Completo  | 55 |

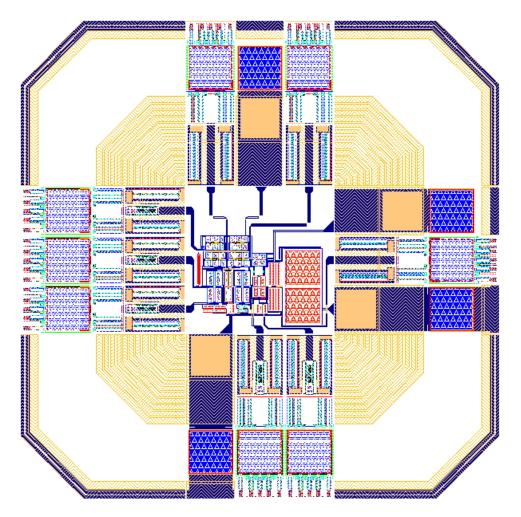

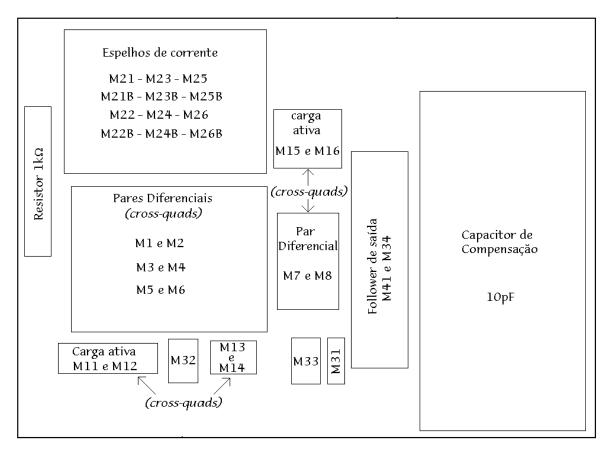

| 2.6. Layout do circuito integrado                            | 57 |

| 2.7. Conclusão                                               | 60 |

| CAPÍTULO 3 - RESULTADOS EXPERIMENTAIS                        | 62 |

| 3.1. Introdução                                              | 62 |

| 3.2. Instrumentos utilizados e cuidados tomados              | 62 |

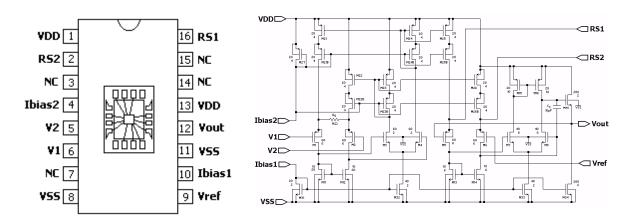

| 3.3. Diagrama de Pinos do Circuito Integrado                 | 63 |

| 3.4. Análise Estática                                        | 64 |

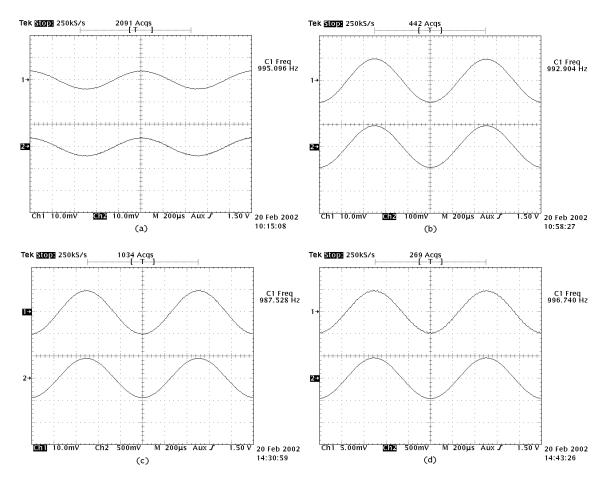

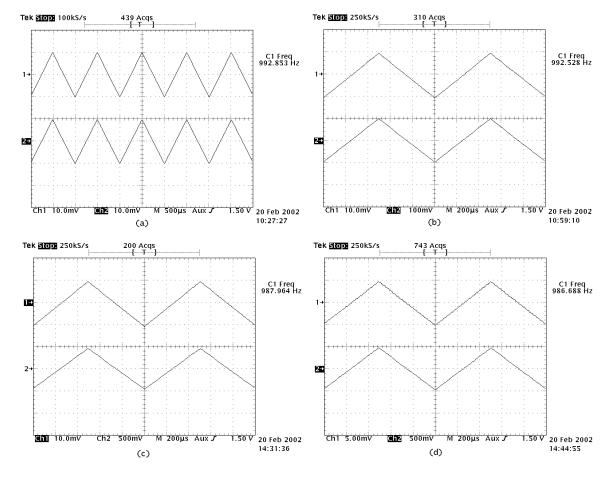

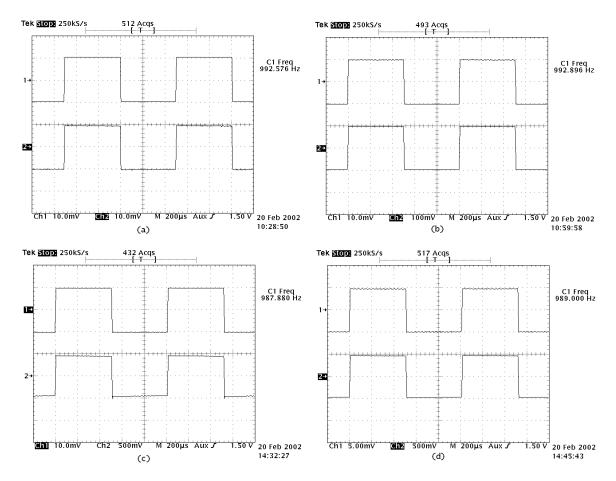

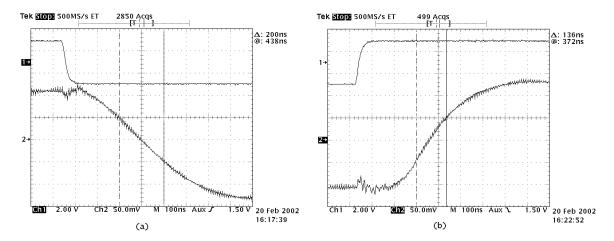

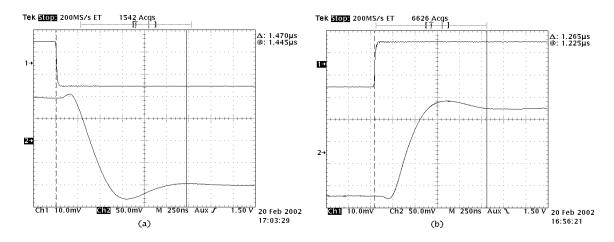

| 3.5. Análise no Tempo                                        | 64 |

| 3.6. Análise em Freqüência                                   | 70 |

| 3.7. Resumo dos Resultados                                   | 77 |

| 3.8. Comparações Pertinentes                                 | 77 |

| 3.9. Fotomicrografias                                        | 78 |

|                                                              |    |

| CONCLUSÃO GERAL                                                          | 81  |

|--------------------------------------------------------------------------|-----|

| APÊNCICE A – PROCESSO DE FABRICAÇÃO DE CIRCUITOS<br>INTEGRADOS UTILIZADO | 82  |

| A.1. Introdução                                                          | 82  |

| A.2. O Processo de Fabricação                                            | 82  |

| A.2.1. Parâmetros do Processo                                            | 83  |

| A.2.2. A Fabricação do Circuito Integrado                                | 84  |

| A.3. Conclusão                                                           | 85  |

| APÊNCICE B – ARQUIVO DE SAÍDA                                            | 86  |

| B.1. Introdução                                                          | 86  |

| B.2. Informações de Ponto de Operação                                    | 86  |

| B.3. Conclusão                                                           | 90  |

| APÊNCICE C – ARTIGO PUBLICADO                                            | 91  |

| REFERÊNCIAS                                                              | 97  |

| ÍNDICE REMISSIVO                                                         | 102 |

# INTRODUÇÃO GERAL

Um amplificador de instrumentação, também conhecido por *in-amp* (*instrumentation amplifier*) é um elemento essencial em qualquer sistema de aquisição de sinais de pequena amplitude. O que o difere de um amplificador operacional (*op-amp*) é que o amplificador de instrumentação deve ser capaz de rejeitar sinais de modo-comum a uma taxa de –90dB, aproximadamente. Outra diferença básica é que aos amplificadores operacionais, uma malha de realimentação deve ser incorporada para que eles operem de forma controlada, ao passo que os amplificadores de instrumentação já são estruturas intrinsecamente realimentadas.

São muitas as aplicações em que amplificadores de instrumentação podem ser empregados. Dentre elas, destaca-se a instrumentação biomédica, caso de sistemas de aquisição de sinais provenientes de eletroencefalogramas (EEG), além de condicionadores de sinais que, por exemplo, coletam sinais de termopares, pontes resistivas ou de algum outro tipo de sensor [1].

O projeto de um amplificador de instrumentação CMOS integrado foi escolhido como tema desta dissertação de mestrado pela oportunidade que oferece ao projetista de adotar soluções para os diversos problemas que normalmente surgem no desenvolvimento de um sistema analógico integrado. Além disso, é um dispositivo de grande utilidade como *front-end* de muitos sistemas em que o sinal a ser tratado é de amplitude muita baixa em relação aos sinais de modo-comum interferentes.

Neste trabalho, o amplificador de instrumentação desenvolvido deve apresentar, como principal característica, uma rejeição de modo-comum acima de 100dB, possibilitando que o sinal de saída amplificado sofra uma influência muito pequena dos sinais de modo comum presentes na entrada.

Para apresentar o trabalho desenvolvido, esta dissertação de mestrado foi estruturada da seguinte forma: no Capítulo 1 os princípios básicos de um amplificador de instrumentação são apresentados e faz-se uma breve exposição das principais configurações deste tipo de amplificador publicadas na literatura que influenciaram direta ou indiretamente este projeto. No Capítulo 2 o projeto do amplificador de instrumentação desenvolvido neste trabalho é detalhado, descrevendo-se as etapas seguidas até a sua

conclusão, o que inclui a configuração escolhida para a implementação do circuito; o projeto das diversas partes do amplificador, incluindo a análise em freqüência e o tipo de compensação utilizada; a simulação dos circuitos envolvidos; e, finalmente, o *layout* elaborado para o circuito integrado do amplificador de instrumentação. No Capítulo 3 apresentam-se os resultados experimentais obtidos, fazendo-se uma confrontação com os resultados esperados através dos cálculos e da simulação. Conclui-se esta dissertação com uma análise do projeto como um todo dentro da conjuntura de um trabalho de mestrado.

Este documento ainda inclui três apêndices: o Apêndice A traz os principais parâmetros de processo fornecidos pela *foundry* responsável pela fabricação do circuito integrado, assim como uma rápida descrição do processo utilizado em sua fabricação; o Apêndice B apresenta o arquivo de saída gerado pelo *software* de simulação dispondo em tabelas todos os parâmetros elétricos dos dispositivos envolvidos no circuito do amplificador de instrumentação; finalmente, o Apêndice C traz uma cópia do artigo resultante deste trabalho publicado numa conferência sobre circuitos integrados.

**CAPÍTULO**

1

Fundamentos de Amplificadores de Instrumentação

## 1.1. INTRODUÇÃO

Este capítulo descreve as principais características que um amplificador deve apresentar para ser classificado como um amplificador de instrumentação. Além disso, é feita uma breve cobertura sobre algumas configurações deste tipo de amplificador encontradas na literatura, a fim de se chegar à configuração adotada para o projeto do amplificador de instrumentação descrito neste documento.

#### 1.2. Princípios Básicos

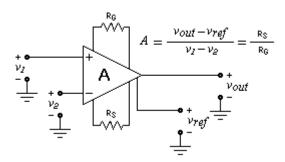

O termo "amplificador de instrumentação", segundo Derek F. Bowers em [2], parece ter surgido no fim da década de 60 denotando geralmente um amplificador que executava uma conversão de um sinal diferencial na entrada para um sinal de saída simples (single-ended) com um ganho precisamente definido. Desta maneira, um amplificador de instrumentação pode ser esquematizado como mostra o diagrama da Fig. 1.1 [3],

representando um circuito em cujas entradas se aplicam dois sinais de tensão ( $v_1$  e  $v_2$ ) e que disponibiliza em sua saída a diferença entre estes dois sinais ampliada por um ganho  $A \rightarrow v_{out} - v_{ref} = A(v_1 - v_2)$ . Este sinal de saída  $v_{out}$  pode ser tanto flutuante como referenciado ao terra, bastando neste caso apenas conectar o terminal  $v_{ref}$  ao terra do circuito.

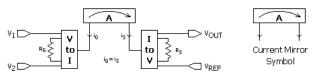

Fig. 1. 1 - Diagrama de um amplificador de instrumentação [3] e sua expressão de ganho.

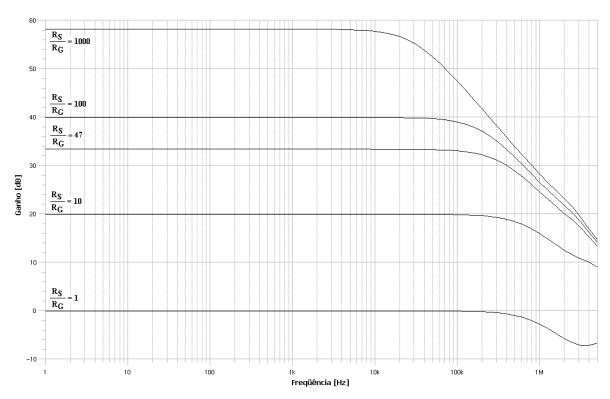

O ganho "precisamente definido" a que se referiu Bowers é geralmente dado pela razão entre duas resistências ( $R_S$  e  $R_G$ ). Outra característica do amplificador de instrumentação é que ele opera sempre em malha fechada e, portanto, não requer realimentação externa [4].

De modo a realizar uma perfeita conversão de entrada diferencial para saída simples, um amplificador de instrumentação ideal deve ter a habilidade de amplificar apenas sinais de modo diferencial, ou seja, amplificar somente a diferença entre os sinais presentes nas entradas  $v_I$  e  $v_2$ . Para tanto, a componente de modo comum aos sinais de entrada deve ser completamente rejeitada. Esta é a característica que, segundo Wolfenbuttel e Schekkerman em [5], um amplificador de instrumentação deve primar por apresentar, sendo conhecida como rejeição de modo comum. Assim, o termo Razão de Rejeição de Modo Comum, ou simplesmente CMRR (*Commom Mode Rejection Ratio*), descreve quantitativamente esta característica do amplificador. A CMRR é normalmente expressa em decibéis (dB) e é dada pela razão entre o ganho do amplificador para sinais diferenciais  $(A_{MD})$  e o ganho para sinais de modo comum  $(A_{MC})$ , como expresso a seguir em (1.1).

$$CMRR = \frac{A_{MD}}{A_{MC}}$$

$$CMRR_{dB} = 20 \cdot \log \left(\frac{A_{MD}}{A_{MC}}\right)$$

(1.1)

Entenda-se por ganho de modo comum, a razão entre a variação na tensão de saída pela variação na tensão de modo comum na entrada; e ganho de modo diferencial como a razão entre a variação na tensão de saída pela variação na tensão de modo diferencial na entrada. Portanto, quanto maior a CMRR, melhor é o amplificador de instrumentação.

Em geral, para ser definido como amplificador de instrumentação, um amplificador deve apresentar uma CMRR superior a 80dB [6], ou seja, um ganho para sinais diferenciais pelo menos 10 mil vezes o ganho para sinais de modo comum. Isto significa que na leitura de um sinal de amplitude de 1mV na presença de um sinal de modo comum com 1V de amplitude, um amplificador de instrumentação apresentando uma CMRR = 100dB, cometerá um erro de 1% na medida.

Deste modo, o projeto deste amplificador de instrumentação tem como principal objetivo alcançar um valor de CMRR elevado, não se atendo, portanto, a outras características também importantes como baixo ruído, alta rejeição a variações na fonte de alimentação (alta PSRR - *Power Supply Rejection Ratio*), baixa tensão de *offset* de entrada e baixa deriva térmica (*thermal drift*), visto que, na prática, é impossível otimizar todas as características no projeto de um amplificador [3].

Na história dos amplificadores de instrumentação, primeiro surgiram aqueles construídos a partir de amplificadores operacionais (*op-amps*) utilizando realimentação resistiva, como será visto na próxima seção e, enfim, os amplificadores de instrumentação desenvolvidos utilizando a técnica de transferência de corrente que será abordada na seção 1.4 e que incluem a configuração escolhida para implementar o amplificador projetado neste trabalho.

## 1.3. AMPLIFICADOR DE INSTRUMENTAÇÃO COM OP-AMPS

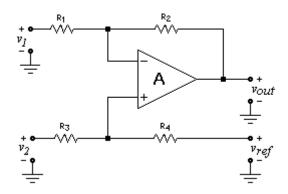

Um amplificador de instrumentação construído a partir de amplificadores operacionais é baseado numa estrutura conhecida como amplificador diferencial ou subtrator, mostrada na Fig. 1.2.

Fig. 1. 2 - Amplificador diferencial (subtrator).

Aplicando-se o teorema da superposição no circuito da Fig. 1.2, chega-se à seguinte expressão:

$$v_{out} - v_{ref} = -\frac{R_2}{R_1} \cdot v_1 + \frac{1 + R_2/R_1}{1 + R_3/R_4} \cdot v_2$$

(1.2)

Se  $R_1 = R_3 = R_G$  e  $R_2 = R_4 = R_S$ , então a expressão (1.1) reduz-se à:

$$\frac{v_{out} - v_{ref}}{v_2 - v_1} = \frac{R_2}{R_1} = \frac{R_S}{R_G}$$

(1.3)

Por (1.3) verifica-se que o ganho do subtrator é dado por uma razão de resistências e que se os sinais  $v_1$  e  $v_2$  forem iguais, a saída será nula. Porém, isto requer um casamento muito bom entre resistores  $R_1$  e  $R_3$  e entre  $R_2$  e  $R_4$ , nem sempre possível na prática. Outra imperfeição desta estrutura é que as entradas  $v_1$  e  $v_2$  apresentam impedâncias baixas e desiguais. Isto prejudica a rejeição de modo comum do circuito, visto que para

uma determinada tensão aplicada igualmente nas entradas, correntes diferentes fluirão por elas produzindo uma tensão não nula de saída [6].

Dessa forma, é necessário que as entradas de um amplificador de instrumentação apresentem impedâncias altas e casadas. Uma maneira de se implementar estas características, que se tornou uma configuração padrão para amplificadores de instrumentação é a clássica estrutura baseada em três amplificadores operacionais como mostrado na Fig. 1.3.

**Fig. 1. 3 –** Configuração clássica de um amplificador de instrumentação formado por três op-amps.

O circuito da Fig. 1.3 pode ser visto como apresentando dois estágios: o primeiro formado pelos amplificadores AI e A2 e pelas resistências  $R_2$  e  $R_G$ ; e o segundo que nada mais é do que o subtrator da Fig. 1.2 operando com ganho unitário para sinais de modo diferencial (todas as resistências são iguais). O estágio de entrada apresenta impedâncias altas e casadas em suas entradas, características estas conferidas pelos amplificadores AI e A2. Quando um sinal diferencial  $v_{id}$  é aplicado entre as entradas do circuito, a tensão  $v_{id}$  é imposta sobre a resistência  $R_G$  e, portanto, passa para o segundo estágio com um ganho dado pelo fator  $1+2\cdot R_2/R_G$ . Já para sinais de modo comum, as tensões nas extremidades de  $R_G$  serão iguais e não haverá corrente fluindo por  $R_G$ . Portanto, os op-amps disponibilizarão para o segundo estágio o sinal de entrada de modo comum com ganho unitário. Cabe ao segundo estágio rejeitar este sinal, passando para a saída somente sinais de modo diferencial.

Ainda assim, uma boa CMRR neste tipo de amplificador de instrumentação depende do casamento de resistores, o que torna este tipo de amplificador pouco atrativo para implementação monolítica. Além disso, em processos CMOS comumente utilizados, mecanismos eficientes de ajuste de resistores (de filmes finos), como ajuste por laser (*laser trimming*), são raramente utilizados.

Assim, uma configuração muito melhor e mais apropriada para implementação monolítica surgiu em 1971, proposta por Heinrich Krabbe [7]. Esta configuração, a ser abordada na seção seguinte, tornou-se padrão para amplificadores de instrumentação monolíticos, tendo sido adotada nos projetos realizados posteriormente.

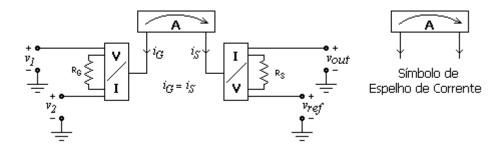

#### 1.4. TÉCNICA DE TRANSFERÊNCIA DE CORRENTE

A técnica introduzida por Krabbe consiste na transferência de corrente do estágio de entrada para saída e dispensa o uso de uma rede resistiva como acontecia com a configuração de três *op-amps*, eliminando, assim, o problema de casamento de resistores. Importantes contribuições foram dadas por Brokaw e Timko em [8], van de Plassche em [9] e mais recentemente por Martins, Selberherr e Vaz em [10] através do desenvolvimento de circuitos que implementam esta técnica de transferência de corrente.

Esta técnica foi chamada de "realimentação indireta de corrente" por van den Dool e Huijsing em [11], em que eles descrevem a implementação desta técnica com a característica adicional de estender a faixa de operação de modo comum até o limite negativo da fonte de alimentação. Porém, o termo por eles utilizado tem interpretações diversas, sendo algumas vezes alterado para "realimentação ativa" [2], o que pode levar a certas confusões desnecessárias. Preferiu-se, portanto, não utilizar nenhuma destas classificações encontradas na literatura, mas simplesmente indicar que funcionamento do amplificador depende de uma técnica de transferência de corrente. A Fig. 1.4 ilustra de modo simplificado o funcionamento desta técnica.

Fig. 1.4 – Diagrama ilustrativo da técnica de transferência de corrente utilizada.

Referindo-se à Fig. 1.4, na entrada, o sinal diferencial é convertido numa corrente  $i_G$ , (através do conversor V/I) que é transferida para o estágio de saída, normalmente com ganho unitário (A = 1). Na saída, esta corrente, denominada agora  $i_S$ , é convertida em tensão (através do conversor I/V) quando flui pelo resistor  $R_S$ , estabelecendo o ganho do amplificador. Referindo-se, ainda, à Fig. 1.4, as seguintes expressões se aplicam:

$$i_{G} = \frac{v_{1} - v_{2}}{R_{G}}$$

$$v_{out} - v_{ref} = R_{S} \cdot i_{S}$$

$$i_{G} = i_{S} \rightarrow \frac{v_{out} - v_{ref}}{v_{1} - v_{2}} = \frac{R_{S}}{R_{G}}$$

$$(1.4)$$

A razão dada por (1.4) entre a resistência  $R_S$  na saída e  $R_G$  na entrada estabelece o ganho esperado para um amplificador de instrumentação como mostrado na Fig. 1.1. Nota-se ainda pelo diagrama, que não há realimentação da saída para a entrada do circuito (realimentação global), facilitando a compensação em freqüência do amplificador. Outra característica importante é que a rejeição de modo comum e o ganho do amplificador não dependem de nenhum casamento entre resistores, mas simplesmente da transferência de corrente da entrada para a saída.

A seguir, faz-se um apanhado das principais configurações de amplificadores de instrumentação encontradas na literatura que utilizam esta mesma técnica de transferência de corrente e que influenciaram o projeto do amplificador de instrumentação aqui descrito.

## 1.4.1. Amplificador de Instrumentação de Krabbe

O primeiro amplificador de instrumentação totalmente monolítico publicado na literatura a empregar a técnica descrita no item anterior, como já dito, foi desenvolvido por Heinrich Krabbe em 1971 [7], [4] e implementado em tecnologia bipolar. O circuito simplificado deste amplificador é mostrado na Fig. 1.5 [12].

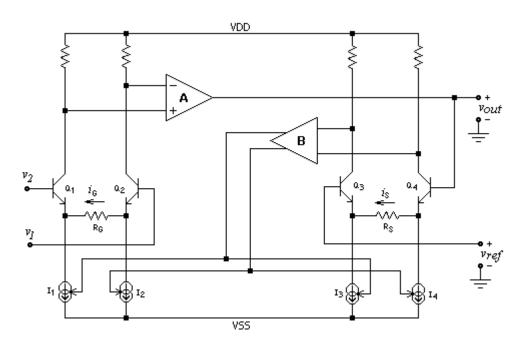

Fig. 1.5 – Circuito simplificado do amplificador de instrumentação desenvolvido por Krabbe.

O funcionamento deste circuito pode ser descrito brevemente da seguinte forma. Quando um sinal diferencial é aplicado entre as entradas  $v_1$  e  $v_2$ , o amplificador A, que monitora os potenciais nos coletores de  $Q_1$  e  $Q_2$ , impede que as correntes nos coletores de  $Q_1$  e  $Q_2$  se tornem desiguais. Para isto, ele atua de tal modo que as fontes de corrente  $I_1$  e  $I_2$  se ajustem para acomodar tanto as correntes de  $Q_1$  e  $Q_2$  como a componente  $i_G$ . Este ajuste é possível devido à ação do amplificador B que, da mesma forma que A, impede que as correntes nos coletores de  $Q_3$  e  $Q_4$  se tornem desiguais. Com as correntes nos pares diferencias mantidas iguais e, supondo um casamento perfeito entre os transistores  $Q_1$  e  $Q_2$  e entre  $Q_3$  e  $Q_4$ , as tensões base-emissor desses transistores devem satisfazer  $V_{BE1} = V_{BE2}$  e  $V_{BE3} = V_{BE4}$  e, portanto, a tensão sobre o resistor  $R_G$  torna-se igual à tensão aplicada na

entrada. A corrente  $i_G$  fluindo por ele, por sua vez, torna-se  $i_G = (v_1 - v_2)/R_G$ . Na saída, a tensão de saída torna-se  $v_{out} - v_{ref} = i_S \cdot R_S$ . Assim, se as fontes variáveis de corrente forem casadas de tal forma que  $I_1 - I_2 = I_3 - I_4$ , então a corrente  $i_S$  fluindo por  $R_S$  será igual a  $i_G$  e, portanto, o ganho do circuito será igual ao dado pela expressão (1.4). Para sinais de modo comum aplicados na entrada, a natureza balanceada do par diferencial faz com a corrente  $i_G$  seja nula e, por conseguinte, que a tensão de saída também seja nula. Desta forma, este circuito desempenha as funções requeridas para um amplificador de instrumentação. No entanto, para apresentar um funcionamento adequado ele depende do casamento das fontes de corrente variáveis.

#### 1.4.2. Amplificador de Instrumentação de Brokaw e Timko

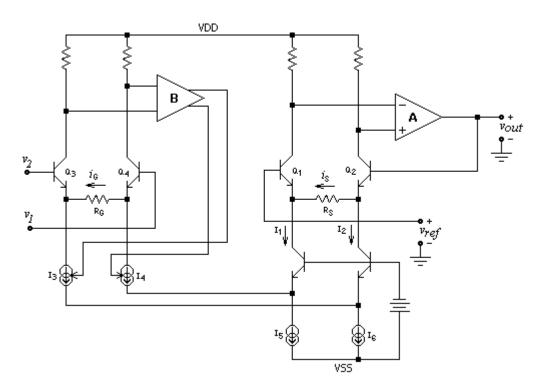

A fim de melhorar o circuito de Krabbe com relação à necessidade de um bom casamento entre fontes de corrente variáveis, uma nova configuração, também em tecnologia bipolar, foi proposta por Brokaw e Timko em [8], cujo circuito simplificado é mostrado na Fig. 1.6.

Fig. 1.6 – Circuito simplificado do amplificador de instrumentação desenvolvido em [8].

Nesta configuração o funcionamento do circuito é muito parecido com o do anterior, com a principal diferença de que para que  $i_S$  seja igual a  $i_G$ , é necessário apenas que as correntes  $I_5$  e  $I_6$  sejam iguais. Para esta condição,  $I_1 - I_2 = I_3 - I_4$  e, portanto,  $i_S = i_G$ . Assim sendo, o funcionamento adequado do amplificador de instrumentação depende do casamento entre as fontes fixas  $I_5$  e  $I_6$  e não mais do casamento entre fontes de correntes variáveis. Outras duas melhorias introduzidas com relação ao circuito de Krabbe são: melhor *settling time* do amplificador, visto que o amplificador B atua diretamente no par diferencial de entrada; e compensação em freqüência simplificada, uma vez que não existe mais um amplificador operando em malha fechada no caminho da realimentação do outro amplificador [8].

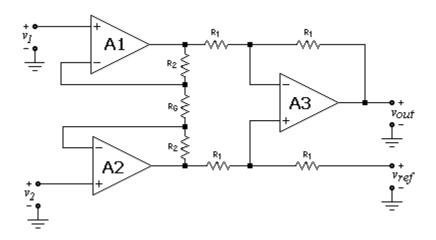

# 1.4.3. Amplificador de Instrumentação de Martins, Selberherr e Vaz

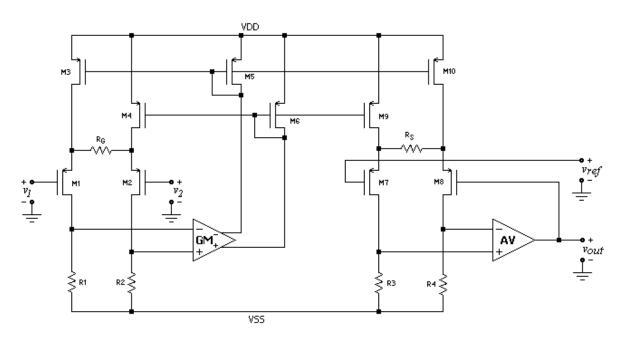

Uma versão CMOS da configuração proposta por Brokaw e Timko foi proposta em 1998 por Martins, Selberherr e Vaz em [10] cujo circuito simplificado é mostrado na Fig. 1.7. Nesta figura, algumas partes básicas do circuito podem ser identificadas: o estágio

de entrada é composto por um par diferencial implementado por transistores canal-p (M1 e M2) com cargas resistivas  $R_1$  e  $R_2$ ; um bloco de transcondutância GM e dois espelhos de corrente formados pelos transistores de canal-p M3–M5 e M4–M6. A corrente nos transistores M5 e M6, além de serem espelhadas para o par diferencial de entrada, também são espelhadas através dos transistores M10 e M9, respectivamente, para o outro par diferencial (M7 e M8) que compõe o estágio de saída juntamente com um bloco amplificador de tensão AV. Tanto o par diferencial de entrada como o de saída apresentam uma resistência ( $R_G$  e  $R_S$ , respectivamente) entre os terminais de fonte dos transistores que os compõem. Esta resistência permite uma conversão linear tensão-corrente (conversão V-I) da tensão presente entre os terminais de porta dos transistores de ambos os pares diferenciais.

Fig. 1.7 – Circuito simplificado do amplificador de instrumentação desenvolvido em [10].

Porém, para o funcionamento correto do circuito é necessário que haja uma conversão tensão-corrente adequada na entrada e uma conversão corrente-tensão adequada na saída. Para tanto, os blocos GM e AV devem apresentar valores razoáveis de transcondutância e de ganho de tensão (que serão vistos no Capítulo 2). Além disso, uma consideração feita anteriormente para que o ganho seja dado pela razão  $R_S/R_G$ , requer que os espelhos de corrente M3-M5-M10 e M4-M6-M9 sejam de boa qualidade, ou seja, que a

corrente em *M5* seja reproduzida de forma fiel em *M3* e *M10* e que o mesmo aconteça para *M4–M6–M9*.

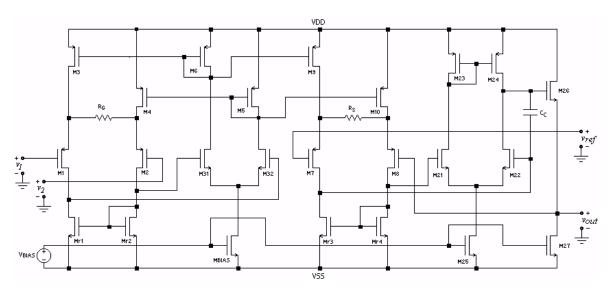

A Fig. 1.8 mostra o circuito completo do amplificador de instrumentação da Fig. 1.7. Os blocos GM e AV desta figura podem ser identificados como sendo o par diferencial M31-M32 e o amplificador M21-M22-M23-M24-M25-M26-M27, respectivamente. Além disso, os resistores R1, R2, R3 e R4 da Fig. 1.7 foram substituídos por cargas ativas Mr1-Mr2 e Mr3-Mr4. A compensação em freqüência do amplificador é feita através da colocação de um simples capacitor  $C_C$  no interior do bloco AV.

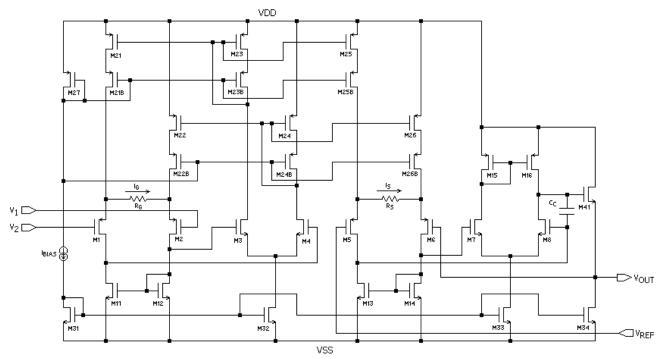

Fig. 1.8 – Circuito completo do amplificador de instrumentação desenvolvido em [3].

Existem ainda outras configurações de amplificadores de instrumentação ([9], [13], [14]) não descritas nesta dissertação, mas que utilizam alguma técnica de transferência de corrente. O fato de não serem apresentadas aqui não significa que elas sejam melhores ou piores; significa apenas que não estão diretamente ligadas ao projeto deste amplificador de instrumentação. Entretanto, elas devem ser levadas em consideração por quem está envolvido no projeto de um amplificador deste tipo, dependendo das necessidades e do tipo de aplicação a que este é destinado.

O amplificador de instrumentação desenvolvido e descrito neste trabalho de dissertação de mestrado utiliza a mesma configuração do amplificador proposto em [10], mostrado na Fig. 1.7 e na Fig. 1.8, diferindo apenas no espelho de corrente utilizado para

transferir a corrente da entrada para a saída. Com esta alteração teve-se o intuito de melhorar a acuidade desta transferência e ao mesmo tempo aumentar a rejeição de modo comum do amplificador, melhorias estas que serão discutidas no Capítulo 2.

#### 1.5. CONCLUSÃO

Neste capítulo foram apresentados os princípios básicos que regem o funcionamento de um amplificador de instrumentação, a fim de explicitar a característica priorizada neste projeto que é a rejeição de modo comum. Além disso, foram abordadas algumas configurações de amplificadores de instrumentação, desde um simples subtrator, passando pela configuração clássica de três *op-amps*, chegando, enfim, à classe dos amplificadores que utilizam o método de transferência de corrente, na qual se inclui a configuração em que se baseia o amplificador desenvolvido neste trabalho. O próximo capítulo abordará o projeto do amplificador de instrumentação enfocado nesta dissertação.

**CAPÍTULO**

2

PROJETO DO AMPLIFICADOR DE INSTRUMENTAÇÃO

## 2.1. Introdução

Este capítulo apresenta o projeto do amplificador de instrumentação em detalhe, identificando as principais estruturas que o compõem e suas respectivas características. Aborda-se inicialmente o processo utilizado para a fabricação do circuito integrado, descrevendo-se logo a seguir o funcionamento geral do circuito. Passa-se, então, para uma descrição funcional por blocos e pela análise em freqüência do amplificador de instrumentação. Resultados de simulações são apresentados, os quais são utilizados para validar os tópicos abordados, e a apresentação do *layout* do circuito integrado finaliza este capítulo.

#### 2.2. TECNOLOGIA UTILIZADA

A tecnologia utilizada neste projeto é a tecnologia Si CMOS 0,6µm da AMS (Austria Mikro Syteme International AG). Maiores detalhes sobre esta tecnologia, assim

como os principais parâmetros de processo fornecidos pela AMS, utilizados no decorrer deste capítulo, encontram-se no Apêndice A.

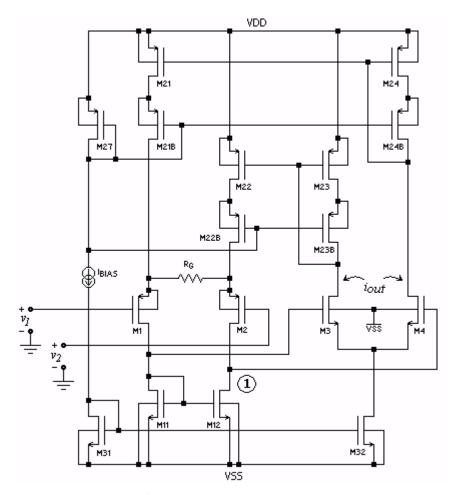

# 2.3. O CIRCUITO DO AMPLIFICADOR DE INSTRUMENTAÇÃO

Como explicado no capítulo anterior, o amplificador proposto neste trabalho utiliza a mesma configuração apresentada em [10], ilustrada pela Fig. 1.7 e pela Fig. 1.8 do Capítulo 1. Desta maneira, a Fig. 2.1 apresenta o circuito completo do amplificador de instrumentação aqui proposto, já incluindo as modificações introduzidas. Vale salientar que todos os componentes presentes no circuito são integrados com exceção feita apenas para a fonte de corrente  $I_{BIAS}$  e para a resistência  $R_S$ , que devem ser adicionadas externamente ao circuito. A colocação externa destes componentes permite mudar o valor da corrente de polarização para eventuais testes do circuito e também configurar o ganho do amplificador, ao alterar o valor da resistência  $R_S$ .

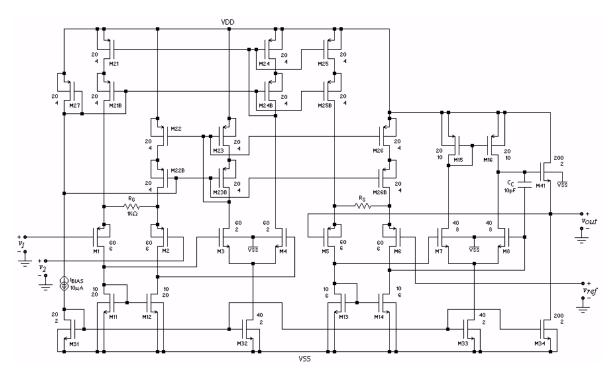

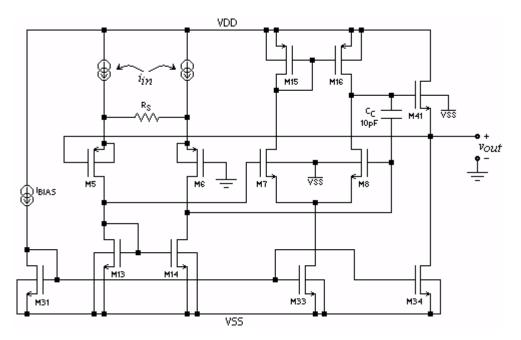

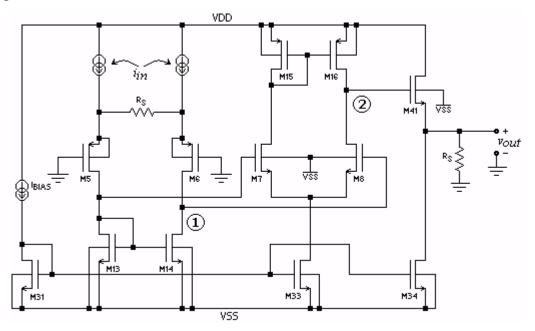

Fig. 2.1 – Circuito completo do amplificador de instrumentação.

Referindo-se à Fig. 2.1, quando um sinal diferencial  $(v_I - v_2)$  é aplicado entre as entradas do amplificador, uma corrente  $i_G$  flui por  $R_G$ , o que provoca um desbalanceamento entre as correntes nos drenos dos transistores MI e M2, que constituem o par diferencial de entrada. De forma a restabelecer o equilíbrio, condição imposta pelo espelho de corrente M11-M12, o par diferencial M3-M4 produz em seus ramos correntes cuja diferença é o dobro de  $i_G$ . Estas correntes são espelhadas para o par diferencial de entrada através dos transistores M21-M21B-M24-M24B e M22-M22B-M23-M23B garantindo o equilíbrio neste par. Quando isto ocorre e considerando que os transistores M1 e M2 sejam casados, o sinal de entrada aparece sobre o resistor  $R_G$  e, portanto, a corrente  $i_G$  torna-se igual a  $(v_I - v_2)/R_G$ .

Ainda, as correntes nos ramos do par diferencial M3-M4 são transferidas para os ramos do par diferencial de saída M5-M6 através dos espelhos de corrente M23-M23B-M26-M26B e M24-M24B-M25-M25B. Consequentemente, a diferença entre estas correntes é a mesma que a diferença entre as correntes nos ramos do par M1-M2, o que torna o par diferencial de saída desbalanceado. Porém, o amplificador AV formado pelos transistores M7-M8-M15-M16-M34-M41, cuja saída é realimentada para uma das entradas do par M5-M6, age no sentido de restabelecer o equilíbrio entre as correntes deste par, condição esta imposta pelo espelho M13-M14. Com as correntes balanceadas, a corrente pelo resistor  $R_S$  torna-se  $i_S = i_G$  e a queda causada por ela sobre  $R_S$  estabelece a tensão de saída do circuito  $(v_{out})$ . Assim, o ganho do amplificador é determinado pela razão entre os resistores  $R_S$  e  $R_G$  conforme a expressão apresentada na Fig. 1.1, repetida a seguir por conveniência:

$$\frac{v_{out} - v_{ref}}{v_1 - v_2} = \frac{R_S}{R_G}$$

(2.1)

O circuito da Fig. 2.1, como pode ser observado, é um circuito razoavelmente complexo, não tratando-se simplesmente de um amplificador operacional canônico, cujo projeto é abordado em diversos livros, tais como [15], [16], [17]. Dessa forma, não há qualquer tipo de roteiro a ser seguido para se chegar às especificações desejadas. Portanto, o projeto foi dirigido da seguinte forma: divisão do circuito em blocos funcionais, análise de cada um desses blocos e dimensionamento dos componentes de acordo com as

características desejadas e com algumas técnicas encontradas na literatura. Deste modo, nas subseções a seguir estes blocos são apresentados e discutidos.

#### 2.3.1. Estágio Diferencial de Entrada

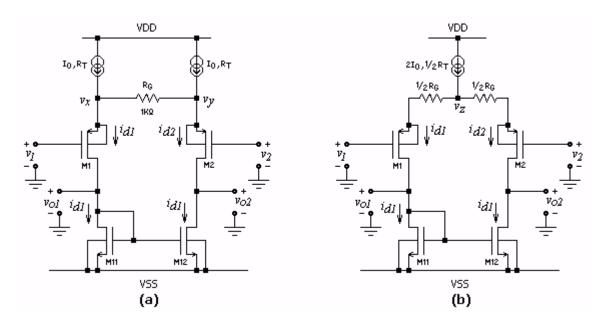

Neste estágio, mostrado na Fig. 2.2(a), um par diferencial degenerado pela resistência  $R_G$  é a estrutura básica. Os transistores M21, M21B, M22 e M22B da Fig. 2.1 foram substituídos por fontes de corrente  $I_0$  apresentando resistências de saída  $R_T$ . Este circuito pode ser analisado utilizando-se o seu equivalente mostrado na Fig. 2.2(b). Nesta figura, a resistência  $R_G$  foi dividida em duas, cada uma com a metade de seu valor. As duas fontes de corrente  $I_0$  foram substituídas por uma única fonte fornecendo uma corrente igual a  $2I_0$  e, portanto, com uma resistência de saída equivalente de valor  $\frac{1}{2}$   $R_T$  [3].

Fig. 2.2 – Dois circuitos equivalentes para o par diferencial de entrada.

Referindo-se à Fig. 2.2(b) pode-se fazer uma análise incremental do circuito. Quando um sinal diferencial ( $v_{id} = v_1 - v_2$ ) é aplicado entre as entradas do par diferencial, correntes incrementais  $i_{d1}$  e  $i_{d2}$  fluem pelos transistores M1 e M2, sendo que se a fonte de corrente  $2I_0$  for considerada ideal, então a condição  $i_{d1} + i_{d2} = 0$  deve ser satisfeita. Estas correntes estão relacionadas com o sinal de entrada conforme as seguintes expressões:

$$i_{d1} = \frac{v_z - v_1}{\frac{1}{g_{m1}} + \frac{R_G}{2}}$$

$$i_{d2} = \frac{v_z - v_2}{\frac{1}{g_{m2}} + \frac{R_G}{2}}$$

(2.2)

para as quais foram utilizados parâmetros de pequenos sinais dos modelos para transistores MOS canal-n e canal-p, encontrados fartamente na literatura [3], [18], [19]. Em (2.2),  $g_{m1}$  e  $g_{m2}$  designam as transcondutâncias dos transistores M1 e M2, respectivamente.

Se  $i_{d1} + i_{d2} = 0$  e considerando idênticos os transistores M1 e M2 de forma que  $g_{m1} = g_{m2}$ , então  $v_z = (v_1 + v_2)/2$  e, portanto, as correntes nos drenos de M1 e M2 podem ser reescritas como:

$$i_{d1} = -\frac{g_{m1} \cdot (v_1 - v_2)}{2 + g_{m1} \cdot R_G}$$

$$i_{d2} = \frac{g_{m1} \cdot (v_1 - v_2)}{2 + g_{m1} \cdot R_G}$$

(2.3)

Referindo-se ainda à Fig. 2.2(b), observa-se que o transistor M2 fornece uma corrente  $i_{d2}$  para o nó de saída 2, enquanto que o transistor M11 fornece uma corrente  $i_{d1}$  para este mesmo nó por ação do espelho de corrente formado por M11-M12. Como resultado, a tensão incremental no nó de saída 2 é dada por:

$$v_{o2} = (i_{d2} - i_{d1}) \cdot (r_{o1} / / r_{o11}) = \frac{2 \cdot g_{m1} \cdot (v_1 - v_2) \cdot (r_{o1} / / r_{o11})}{2 + g_{m1} \cdot R_G}$$

(2.4)

em que  $r_{o1}$  e  $r_{o11}$  são as resistências incrementais de saída de M1 e M11 respectivamente.

Já, no nó de saída 1, a tensão incremental praticamente não varia com a aplicação de um sinal diferencial de entrada, visto que a mesma corrente  $i_{d1}$  que entra neste

nó, também sai dele. Assim,  $v_{oI} \cong 0$  e, portanto, o ganho do par diferencial para sinais diferenciais é dado por:

$$A_{MD1} = \frac{(v_{o1} - v_{o2})}{(v_1 - v_2)} = -\frac{g_{m1} \cdot \{r_{o11} / [r_{o1} \cdot (2 + g_{m1} \cdot R_G)]\}}{1 + g_{m1} \cdot \frac{1}{2} R_G}$$

(2.5)

A fim de encontrar uma expressão para a CMRR do par diferencial de entrada, além do ganho de modo diferencial, o ganho de modo comum também deve ser conhecido. Para tanto, o conceito de meio-circuito (*half-circuit concept*) [3], [18] pode ser aplicado ao circuito da Fig. 2.2(a), resultando no equivalente de pequenos sinais da Fig. 2.3. Segundo Jiang, Tang e Mayaram em [20], isto é possível mesmo que a presença do espelho de corrente *M11-M12* como carga ativa dificulte a visualização da simetria existente no par diferencial para sinais de modo comum.

Fig. 2.3 – Equivalente de meio-circuito do par diferencial de entrada para sinais de modo comum (common-mode half-circuit).

Como mostra a Fig. 2.3, o circuito equivalente nada mais é do que um amplificador fonte-comum (common-source) degenerado pelas resistências  $\frac{1}{2}R_G$  e  $R_T$ , onde  $R_T$  ( $tail\ resistance$ ) corresponde à resistência de saída do espelho cascode de alta excursão (ver subseção 2.3.5) do qual os transistores M21 e M21B fazem parte. Assim, o ganho deste circuito é dado por:

$$\frac{v_{o1}}{v_1} = \frac{1}{g_{m11}} \cdot \frac{g_{m1}}{1 + g_{m1} \cdot \left(\frac{1}{2}R_G + R_T\right)}$$

(2.6)

onde  $g_{m11}$  é a transcondutância do transistor M11.

Além disso, sabe-se que o ganho de modo comum  $A_{MCI}$  é determinado pela seguinte relação [3], [18]:

$$A_{MC1} = \left(\frac{v_{o1} + v_{o2}}{2}\right) / \left(\frac{v_1 + v_2}{2}\right) \tag{2.7}$$

Então, substituindo-se (2.6) em (2.7) com  $v_{o1} = v_{o2}$  [20],  $v_1 = v_2$ , visto que se trata de uma análise de modo comum, e considerando idênticos entre si os pares de transistores M1-M2, M11-M12, M21-M22, M21B-M22B, a seguinte expressão para o ganho de modo comum resulta:

$$A_{MC1} = \frac{1}{g_{m11}} \cdot \frac{g_{m1}}{1 + g_{m1} \cdot \left(\frac{1}{2}R_G + R_T\right)}$$

(2.8)

Assumindo que  $R_T >> \frac{1}{2}R_G$  e que  $g_{ml}R_G >> 1$ , o que é bastante razoável num bom projeto, obtém-se:

$$A_{MC1} \cong \frac{1}{g_{m11} \cdot R_T} \tag{2.9}$$

Assim, a CMRR do par diferencial de entrada pode ser expressa por:

$$CMRR = \frac{A_{MD1}}{A_{MC1}} = \frac{g_{m1} \cdot g_{m11} \cdot R_T \cdot \left[r_{o11} // r_{o1} \cdot (2 + g_{m1} \cdot R_G)\right]}{1 + g_{m1} \cdot \frac{1}{2} R_G}$$

(2.10)

Como mostra a expressão (2.10), a rejeição de modo comum do par diferencial de entrada é prejudicada pela presença de  $R_G$ . Por outro lado, esta mesma rejeição é tanto melhor quanto maior for o valor da resistência associada às fontes de corrente  $I_0$  da Fig. 2.2(a). Portanto, maximizar o valor desta resistência foi uma das metas que guiou este projeto e que será tratada na subseção 2.3.5.

#### 2.3.1.1. Dimensionamento dos dispositivos envolvidos

Vale lembrar que o dimensionamento de transistores MOS não é uma tarefa simples visto que três graus de liberdade estão envolvidos: o comprimento de canal (L), a largura de canal (W) e a corrente de dreno  $(I_D)$ . Assim, mesmo estabelecendo algumas regras de projeto, alguns destes parâmetros devem ser escolhidos arbitrariamente (ao menos para um projeto sem especificações muito rígidas).

Para definir o valor da resistência  $R_G$  que degenera o par diferencial de entrada, levou-se em consideração o fato de que quanto maior seu valor, menor a CMRR deste par diferencial e, também, que área ocupada por resistores integrados limita o valor de  $R_G$ . Portanto, escolheu-se um valor de  $1k\Omega$ , igual ao utilizado em [10], permitindo ainda uma melhor comparação com o amplificador lá descrito.

O valor da corrente de polarização do par diferencial foi escolhido arbitrariamente como  $I_0 = 10\mu A$ . Ainda, segundo Martins *et al.* em [10], para minimizar ruído e *offset* num par diferencial, recomenda-se que os transistores do espelho de corrente, que forma a carga ativa, apresentem uma transcondutância de valor três vezes menor do que a transcondutância dos transistores do par diferencial. Assim, fixou-se:

$$(W/L)_{1,2} = 20 \cdot (W/L)_{11,12}$$

(2.11)

visto que as correntes de dreno destes transistores são iguais e que o fator de ganho  $(K_P)$  para transistores canal-p é aproximadamente três vezes menor que o fator de ganho  $(K_N)$  para transistores canal-n (ver Apêndice A).

Assim, segundo a expressão que define a transcondutância  $g_m$  para transistores MOS [3], [18],[19], suas razões de aspecto (W/L) devem seguir a expressão (2.11) acima.

Ao se determinar as dimensões de *M1* e *M2*, considerou-se, também, que quanto maior a dimensão do dispositivo, menor é o efeito das variações do processo de fabricação que leva ao descasamento entre dois transistores geometricamente idênticos [21], [15]. Desta forma, escolheu-se para *M1* e *M2* a seguinte razão de aspecto:

$$(W/L)_{12} = 60 \mu m/6 \mu m$$

(2.12)

E, segundo as expressões (2.11) e (2.12), as dimensões de *M11* e *M12* também puderam ser determinadas, fixando-se o comprimento de canal:

$$(W/L)_{1112} = 3\mu m/6 \,\mu m \tag{2.13}$$

#### 2.3.2. Bloco de Transcondutância GM

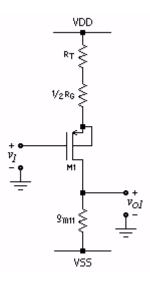

A Fig. 2.4 mostra de modo simplificado o par diferencial M3-M4 que desempenha o papel do bloco de transcondutância GM. Este bloco tem como objetivo monitorar a tensão de saída do par diferencial de entrada - tensões  $v_{o1}$  e  $v_{o2}$  - e transformar estes sinais incrementais de tensão em correntes que fluem pelos transistores M23-M23B e M24-M24B (ver Fig. 2.1), que foram substituídos na Fig. 2.4 por suas resistências equivalentes ( $R_{L2}$ ). Estes transistores fazem parte da cadeia de espelhos M21-M24-M25-M21B-M24B-M25B e M22-M23-M26-M22B-M23B-M26B. Através destes espelhos é feita uma realimentação para o par diferencial de entrada e também provoca-se um desbalanceamento no par diferencial de saída.

Fig. 2.4 – Representação simplificada do bloco GM.

Referindo-se à Fig. 2.4, as correntes  $i_{d3}$  e  $i_{d4}$  valem:

$$i_{d3} = g_{m3} \cdot (v_{o1} - v_x) - g_{mb3} \cdot v_x$$

$$i_{d4} = g_{m4} \cdot (v_{o2} - v_x) - g_{mb4} \cdot v_x$$

(2.14)

em que  $g_{m3}$  e  $g_{m4}$  são as transcondutâncias dos transistores M3 e M4, respectivamente e,  $g_{mb3}$  e  $g_{mb4}$  são as transcondutâncias de efeito de corpo destes transistores.

Analogamente ao par diferencial de entrada analisado na subseção anterior, as correntes pelos transistores M3 e M4 devem satisfazer  $i_{d3} + i_{d4} = 0$ . Nesta condição e, considerando idênticos os transistores M3 e M4 de forma que  $g_{m3} = g_{m4}$  e  $g_{mb3} = g_{mb4}$ , a tensão  $v_x$  pode ser escrita como:

$$v_{x} = \frac{g_{m3} \cdot (v_{o1} + v_{o2})}{2 \cdot (g_{m3} + g_{mb3})}$$

(2.15)

Substituindo (2.15) nas equações (2.14), obtém-se:

$$i_{d3} = \frac{g_{m3} \cdot (v_{o1} - v_{o2})}{2}$$

$$i_{d4} = -\frac{g_{m3} \cdot (v_{o1} - v_{o2})}{2}$$

(2.16)

Donde conclui-se que o efeito de corpo presente nos transistores M3 e M4, traduzido pelos parâmetros incrementais  $g_{mb3}$  e  $g_{mb4}$  nas equações (2.14), não exerce influência no valor das correntes em seus drenos quando em suas entradas é aplicado um sinal diferencial. Portanto, a transcondutância GM vale:

$$GM = \frac{i_{d3}}{\left(v_{o1} - v_{o2}\right)} = -\frac{i_{d4}}{\left(v_{o1} - v_{o2}\right)} = \frac{g_{m3}}{2}$$

(2.17)

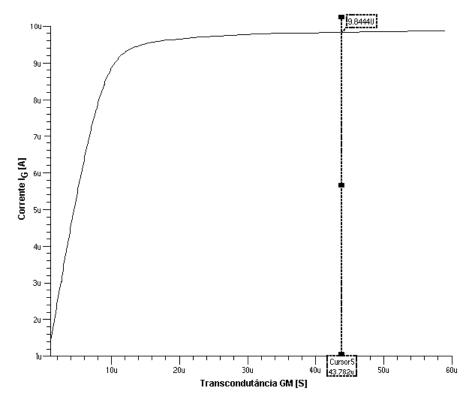

Para garantir uma conversão V-I adequada, o bloco GM deve apresentar uma transcondutância que resulte num erro de conversão menor que o máximo admissível. Para tanto, simulou-se o erro cometido para uma entrada diferencial de 10mV utilizando-se um bloco de transcondutância ideal. Como a resistência sobre a qual se dá a conversão é de  $1k\Omega$  e, tomando-se o gráfico resultante da simulação mostrado na Fig. 2.5, para um erro de aproximadamente 1%, o valor da corrente fluindo pelo resistor  $R_G$  deve ser de 9,9 $\mu$ A. O valor da transcondutância correspondente a esta corrente, segundo a Fig. 2.5, é  $GM = 43.8\mu$ A/V.

Fig. 2.5 – Simulação de erro na conversão V-I (valor ideal da corrente é 10μΑ).

#### 2.3.2.1. Dimensionamento dos dispositivos envolvidos

Para que GM seja igual a 43,8 $\mu$ A/V, segundo a expressão (2.17), o valor da transcondutância dos transistores M3 e M4 deve ser  $g_{m3} = g_{m4} = 87,6 \mu$ A/V. Assim, com uma corrente  $I_D = 10 \mu$ A fluindo por estes transistores, a razão de aspecto de M3 e M4 deve ser igual a 3,2. Dessa forma, definiu-se as seguintes dimensões para estes transistores:

$$(W/L)_{3,4} = 8\mu m/2\mu m \tag{2.18}$$

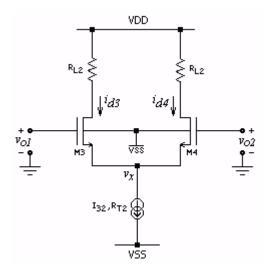

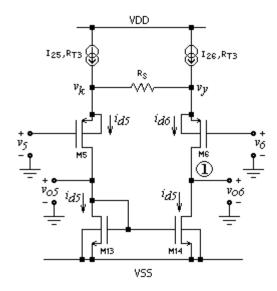

### 2.3.3. Estágio Diferencial de Saída

O estágio diferencial de saída, como mostra a Fig. 2.6, tem a mesma estrutura do estágio diferencial de entrada. A principal diferença é que para o estágio de saída, a variável de entrada é uma corrente (no caso, as correntes pelos transistores *M25-M25B* e

*M26-M26B*) e, portanto, o ganho do circuito é uma transresistência (visto que a saída é uma diferença de tensões).

Fig. 2.6 – Circuito do par diferencial de saída.

Observando-se a Fig. 2.6, percebe-se que os transistores M5 e M6 funcionam como amplificadores porta-comum (common-gate) para o sinal de entrada. Como é bem conhecido para este tipo de amplificador [3], [18], [22], o ganho de corrente é unitário e, portanto, o ganho da corrente de entrada para cada uma das tensões de saída é dado simplesmente pela resistência equivalente do nó de saída em questão. Como a resistência do nó de saída  $v_{o6}$  é muito mais alta do que a do nó de saída  $v_{o5}$ , a transresistência total deste estágio, ou seja, o ganho da corrente de entrada para a diferença entre as tensões de saída é dado praticamente pela resistência equivalente do nó da saída  $v_{o6}$ . Esta resistência, por sua vez, pode ser determinada utilizando-se o circuito equivalente de pequenos sinais mostrado na Fig. 2.7 e aplicando-se uma tensão de teste  $v_X$  no nó 1. Calculando-se a corrente resultante da aplicação desta tensão neste nó, determina-se sua resistência incremental equivalente.

Fig. 2.7 – Circuito para cálculo da resistência equivalente do nó 1 do par diferencial de saída.

Equacionando-se as correntes nos três nós da Fig. 2.7, a resistência equivalente encontrada para o nó 1 é:

$$r_{eq1} = \frac{v_x}{i_x} = r_{o14} / [r_{o6} \cdot (2 + gm_6 \cdot R_S)]$$

(2.19)

onde  $g_{m6}$  e  $r_{o6}$  são, respectivamente, a transcondutância e a resistência incremental de saída do transistor M6 (o mesmo valendo para M5);  $r_{o14}$  é a resistência incremental de saída de M14. Considerou-se neste cálculo  $r_{o5} = r_{o6}$ ,  $g_{m5} = g_{m6}$  e  $r_o >> 1/g_m$ .

Portanto, a transresistência deste estágio, chamada aqui de H, que é dada pela resistência equivalente do nó 1, vale:

$$H = r_{o14} / [r_{o6} \cdot (2 + gm_6 \cdot R_S)]$$

(2.20)

O resistor  $R_S$ , ao contrário de  $R_G$  no par diferencial de entrada, deve ser adicionado externamente ao circuito integrado. Isto se deve a duas razões: primeiro, ao valor possivelmente alto de  $R_S$  (para que o ganho do amplificador de instrumentação possa atingir valores próximos de 1000) que torna pouco atraente sua integração e, segundo, para que o ganho do amplificador de instrumentação possa ser configurado para o valor desejado segundo a relação explicitada em (2.1).

### 2.3.3.1. Dimensionamento dos dispositivos envolvidos

Para o dimensionamento dos transistores do par diferencial de saída utilizaramse as mesmas considerações feitas para o par diferencial de entrada. Portanto, as dimensões são as mesmas, exceto para os transistores do espelho que compõem a carga ativa. Para estes dispositivos, como este bloco não é o estágio de entrada do amplificador, suas dimensões não comprometem o comportamento do circuito quanto a ruído e à tensão de offset como considerado na subseção 2.3.1.1. Assim, arbitrou-se uma dimensão menor para M13 e M14, mantendo o comprimento de canal:

$$(W/L)_{13.14} = 10 \mu m/6 \mu m$$

(2.21)

E, mantendo-se as mesmas dimensões especificadas para o par diferencial de entrada, a razão de aspecto de *M5* e *M6* foi determinada como:

$$(W/L)_{5.6} = 60\mu m/6\mu m \tag{2.22}$$

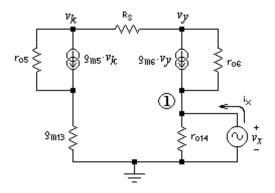

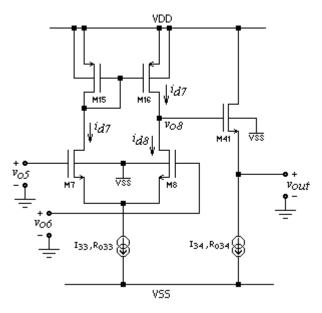

# 2.3.4. Bloco Amplificador de Tensão AV

O bloco AV, mostrado na Fig. 2.8, tem a função de amplificar a diferença de tensão na saída do par diferencial de saída formado pelos transistores M5 e M6 (tensões  $v_{o5}$  e  $v_{o6}$ ) de forma a prover uma realimentação para este par diferencial e corrigir o desbalanceamento nas correntes  $i_5$  e  $i_6$  causado através do bloco GM pela tensão diferencial de entrada aplicada.

Fig. 2.8 – Circuito que implementa o bloco AV.

Este bloco AV é composto por um par diferencial formado por transistores canal-n ( $M7 \, e \, M8$ ), com um espelho de corrente como carga ativa (transistores canal-p  $M15 \, e \, M16$ ) e um estágio de saída do tipo seguidor de fonte (source-follower) formado pelos transistores canal- $n \, M41 \, e \, M34$ , sendo que este último foi substituído na Fig. 2.8 pela fonte de corrente  $I_{34}$ .

O par diferencial *M7-M8* difere dos pares diferenciais de entrada e de saída por não apresentar resistência de degeneração de fonte e também por ter uma saída unilateral. No entanto, o procedimento para o cálculo do ganho é mesmo e está muito bem detalhado em [15]. Assim, tem-se:

$$A_{MD4} = \frac{v_{o8}}{v_{o5} - v_{o6}} = -g_{m7} \cdot (r_{o8} // r_{o16})$$

(2.23)

onde  $g_{m7}$  é a transcondutância do transistor M7 e  $r_{o8}$  e  $r_{o16}$  são as resistências incrementais de saída de M8 e M16, respectivamente.

Para chegar à expressão (2.23), considerou-se que M7 e M8 apresentam transcondutâncias  $g_m$  e resistências incrementais de saída  $r_o$  iguais, o mesmo valendo para os transistores M15 e M16. Além disso, considerou-se também que  $r_o >> 1/g_m$ .

Já o estágio de saída seguidor de fonte, em que o transistor M41 funciona como um amplificador dreno-comum (common-drain) cuja saída é o seu terminal de fonte, tem como características um alto ganho de corrente e baixa resistência de saída. Estas são qualidades desejadas para o estágio de saída de amplificadores operacionais, uma vez que o estágio de saída deve ser capaz de fornecer uma potência significativa para uma carga de baixa impedância [18]. Em contrapartida, esta estrutura sofre o efeito de corpo, o que provoca um aumento da tensão  $V_T$  do transistor canal-n M41 [22] quando a tensão de saída aumenta, prejudicando a faixa DC de saída do circuito [16]. Outra influência do efeito de corpo é a diminuição do ganho deste estágio, tornando-o menor que a unidade [3], [23].

Referindo-se ainda à Fig. 2.8, o ganho deste estágio pode ser facilmente determinado pelas equações a seguir [21].

$$A_{SF} = \frac{g_{m41}}{(1 + \chi_{41}) \cdot g_{m41} + \frac{1}{r_{o41}} + \frac{1}{r_{o34}}}$$

$$\chi_{41} = \frac{g_{mb41}}{g_{m41}}$$

(2.24)

em que  $g_{m41}$  é a transcondutância do transistor M41 e  $g_{mb41}$  sua transcondutância de efeito de corpo;  $r_{o34}$  e  $r_{o41}$  são as resistências incrementais de saída de M34 e M41, respectivamente.

Em (2.24), o fator  $\chi$ , conhecido como fator de efeito de corpo, é um parâmetro que indica a taxa em que a tensão de limiar  $V_T$  de um transistor MOS varia com a tensão de polarização de substrato em relação ao terminal de fonte [18]. O valor de  $\chi$  varia geralmente entre 0.1 e 0.3 [19].

Considerando que as resistências de saída  $r_{o41}$  e  $r_{o34}$  dos transistores M41 e M34 sejam bastante elevadas, então a expressão para o ganho  $A_{SF}$  pode ser aproximada por:

$$A_{SF} \cong \frac{1}{1 + \chi_{41}} \tag{2.25}$$

Esta última expressão corrobora o que foi dito anteriormente, mostrando que a presença do efeito de corpo deteriora o ganho do seguidor de fonte, reduzindo-o de 10% a aproximadamente 25% abaixo da unidade.

Desta forma, o ganho do bloco AV é determinado pelos ganhos do par diferencial *M7-M8* e do estágio seguidor de fonte, como indica a expressão seguinte.

$$AV = A_{MD4} \cdot A_{SF} = \frac{-g_{m7} \cdot (r_{o8} // r_{o_{16}})}{1 + \chi_{41}}$$

(2.26)

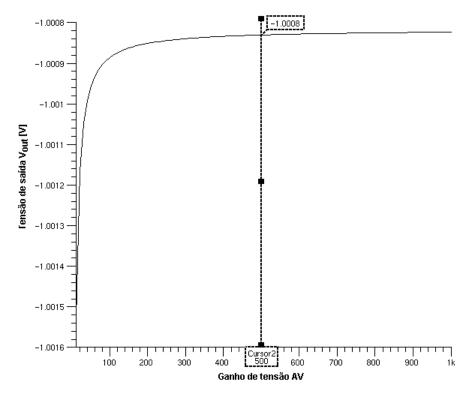

Para garantir que haja uma conversão I-V adequada na saída do amplificador, o que é fundamental para o funcionamento correto do amplificador de instrumentação, simulou-se o erro cometido nesta conversão em função do valor do ganho AV, utilizando-se um bloco amplificador ideal e uma resistência  $R_S = 100k\Omega$ . Por conseguinte, para uma corrente  $I_S = 10\mu A$  fluindo pelo resistor  $R_S$ , a tensão esperada na saída, admitindo-se um erro de 1%, é  $V_{OUT} = 1.01 \text{V}$ .

Portanto, tomando-se o gráfico resultante desta simulação, reproduzido na Fig. 2.9, o valor do ganho deve ser AV = 500. Dessa forma, com base no gráfico obtido, os transistores do par diferencial, da carga ativa e do estágio seguidor de fonte foram dimensionados para que o ganho AV desejado fosse atingido, como mostra-se a seguir.

Fig. 2.9 – Simulação de erro na conversão I-V (valor ideal da tensão de saída é 1V).

#### 2.3.4.1. Dimensionamento dos dispositivos envolvidos

Para que o ganho AV seja igual a 500, conforme indicado pela simulação de erro de conversão I-V, e respeitando-se a expressão (2.26), é possível definir as dimensões dos transistores envolvidos. Para tanto, algumas considerações devem ser feitas. Primeiramente, escolheu-se um comprimento de canal  $L=10\mu m$  para os transistores M8 e M16 de forma com que as resistências  $r_{o8}$  e  $r_{o16}$  fossem aproximadamente iguais a  $10 M\Omega$  (ver Apêndice A):

$$r_{o8} = r_{o16} = \frac{1}{\lambda \cdot I_D} = \frac{1}{0,009V^{-1} \cdot 10\mu A} = 11,2M\Omega$$

(2.27)

em que  $\lambda$  é o fator de modulação de canal e  $I_D$  é a corrente quiescente de dreno para transistores MOS.

Considerou-se também um valor mediano para o fator de efeito de corpo como  $\chi_{41} = 0.2$ . Assim, conforme (2.26), para um ganho AV = 500, a transcondutância do transistor M8 deve ser  $g_{m8} = 107\mu\text{A/V}$ . Para este valor, M8 deve apresentar uma razão de aspecto igual a 4,8, aproximadamente.

Assim, as seguintes dimensões foram determinadas para os transistores *M7*, *M8*, *M15* e *M16*:

$$(W/L)_{7,8} = 50 \mu m / 10 \mu m$$

$(W/L)_{15,16} = 20 \mu m / 10 \mu m$  (2.28)

### 2.3.5. Elemento de transferência de corrente

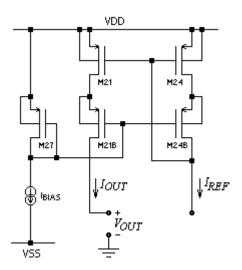

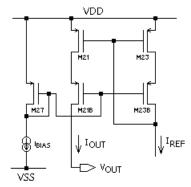

Como elemento de transferência de corrente entre os estágios de entrada e saída do amplificador de instrumentação descrito neste documento, no lugar dos espelhos simples utilizados em [10], foram utilizados espelhos do tipo *cascode* de alta excursão (*high-swing cascode*) [24], [25], [26], [27], cujo circuito é mostrado na Fig. 2.10. A razão para esta decisão de projeto foi aumentar a resistência de saída do espelho, característica comum às estruturas do tipo *cascode* [3], [15],[18], sem degradar a excursão DC do circuito todo [26], embora este último aspecto não tenha sido priorizado neste projeto. Entretanto, a resistência de saída do espelho de corrente é muito importante, visto que ela constitui a resistência de cauda  $R_T$  (*tail resistance*) do par diferencial de entrada, que, como visto na subseção 2.3.1, desempenha um papel fundamental na determinação da CMRR do amplificador [3]. Conseqüentemente, a característica mais importante de um amplificador de instrumentação, que, segundo Wolfenbuttel e Shekkerman em [5], é sua CMRR, pôde ser melhorada neste projeto.

Observando a Fig. 2.10, verifica-se que a resistência incremental de saída do espelho de corrente é a mesma de um espelho *cascode* regular, dada pela expressão seguinte [28]:

$$r_{out} \cong g_{m21B} \cdot r_{o21} \cdot r_{o21B} \tag{2.29}$$

em que  $g_{m21b}$  é a transcondutância do transistor M21B, enquanto  $r_{o21}$  e  $r_{o21b}$  são as resistências incrementais de saída dos transistores M21 e M21B, respectivamente.

Fig. 2.10 – Circuito do espelho de corrente do tipo cascode de alta excursão.

A resistência de saída definida em (2.29) é muito maior quando comparada com a de um espelho simples  $(r_o)$  e, portanto, deve contribuir para um melhor comportamento de modo comum do amplificador.

A resistência incremental de entrada deste tipo de espelho é, aproximadamente, metade da mesma resistência para um espelho *cascode* regular [24] e é dada por:

$$r_{in} \cong \frac{1}{g_{m24}} \tag{2.30}$$

onde  $g_{m24}$  é a transcondutância do transistor M24.

Ainda com referência à Fig 2.10, pode-se determinar a mínima tensão de saída do espelho necessária para seu funcionamento adequado, ou seja, mantendo todos os transistores operando na região de saturação  $(V_{DS} = V_{DS(sat)} > V_{GS} - V_T)$ .

$<sup>^{1}</sup>$   $V_{DS(sat)}$  = tensão dreno-fonte de saturação.

Para tanto, faz-se com que os transistores M21, M21B, M24 e M24B apresentem uma mesma razão de aspecto (W/L) e que M27 apresente (W/L)<sub>27</sub> =  $\frac{1}{4}$ (W/L) [25]. Dessa forma, as tensões  $V_{GS}$  de M21, M21B, M24 e M24B serão as mesmas ( $V_{GS} = V_{DS(sat)} + V_T$ ), visto que por todos eles fluem a mesma corrente. Já a tensão  $V_{GS27}$ , pela diferença na razão de aspecto e pelo fato do transistor M27 conduzir a mesma corrente, será  $2V_{DS(sat)} + V_T$ . Assim, seguindo o circuito, a tensão na porta de M21B será também  $2V_{DS(sat)} + V_T$  e em seu terminal de fonte será  $V_{DS(sat)}$  (colocando M21 em saturação). Desta forma, para que o transistor M21B também permaneça em saturação, a mínima tensão de saída deve ser  $V_{OUTmin} = 2V_{DS(sat)}$ . Este valor é menor que a tensão mínima de saída de um espelho cascode regular por  $V_T$  (tensão mínima de saída de um cascode regular é  $2V_{DS(sat)} + V_T$ ) e maior que o de um espelho simples por  $V_{DS(sat)}$  (tensão mínima de saída de um espelho simples é  $V_{DS(sat)}$ ), justificando o nome complementar dado a este espelho cascode de "cascode de alta excursão". Resta verificar se os demais transistores do espelho encontram-se em saturação. O transistor M27, por sua conexão em forma diodo apresenta  $V_{DS27} = V_{GS27} > V_{GS27} - V_T$  e, portanto, está saturado. Já o dreno de M24 deve apresentar uma tensão maior que  $V_{GS} - V_T$  e, assim, notando-se que o dreno de M24B está conectado com a porta de M24, então ambos estes transistores encontram-se em saturação já que a tensão entre dreno e fonte de M24B será igual  $V_{GS24} - V_{DS(sat)} = V_T$  (desde que  $V_{GS24} < 2V_T)^2.$

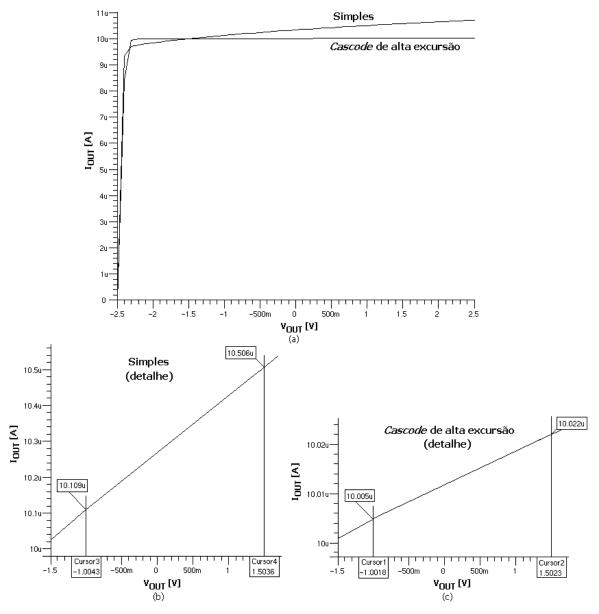

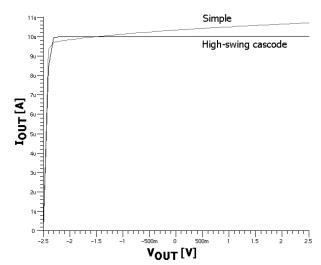

A Fig. 2.11(a) mostra uma simulação comparando as características de transferência DC do espelho de corrente de alta excursão e de um espelho de corrente simples de forma a comprovar as vantagens descritas até agora. Como se pode observar nesta figura, a resistência de saída do espelho *cascode* de alta excursão é, de fato, muito maior do que a resistência do espelho simples, enquanto que a excursão DC da tensão de saída de ambos é comparável. Quantitativamente, estas resistências foram calculadas com o auxílio da Fig. 2.11(b) e da Fig. 2.11(c), que mostram as curvas da Fig. 2.11(a) em maior detalhe. Os valores obtidos foram 6,32MΩ para o espelho simples e 147,6MΩ para o *cascode* de alta excursão, ou seja, uma resistência de saída aproximadamente 23 vezes maior para o *cascode* em relação ao espelho simples.

\_

<sup>&</sup>lt;sup>2</sup> Entre os ajustes feitos por simulação a serem vistos na seção seguinte, está o ajuste de  $V_{GS24}$  de forma que seu valor seja menor que  $2V_T$ , conforme requerido.

Vale mencionar que, para esta simulação, utilizaram-se correntes de referência e de polarização iguais ( $I_{REF} = I_{BIAS} = 10\mu\text{A}$ ), enquanto a tensão de saída foi variada entre as tensões de alimentação do amplificador (-2.5V a +2.5V). As razões de aspecto utilizadas foram de  $20\mu\text{m}/4\mu\text{m}$  para M21, M21B, M24 e M24B e  $5\mu\text{m}$  / $4\mu\text{m}$  para M27 (dimensões finais de projeto destes transistores – ver seção 2.4).

Fig. 2.11 – (a) Simulação comparativa entre as performances dos espelhos de corrente simples e cascode de alta excursão; (b) característica do espelho simples em maior detalhe; (c) característica do espelho cascode de alta excursão em maior detalhe.

#### 2.3.5.1. Dimensionamento dos dispositivos envolvidos

No circuito do amplificador de instrumentação existem quatro espelhos como o da Fig. 2.10, arranjados, no entanto, na forma de dois espelhos triplos (ver Fig 2.1). A corrente em *M24* e *M24B* é espelhada para *M21* e *M21B* e para *M25* e *M25B* formando um espelho triplo (*M21-M24-M25*). Já a corrente em *M23* e *M23B*, é espelhada para *M22* e *M22B* e para *M26* e *M26B* formando o segundo espelho triplo (*M22-M23-M26*). A corrente através dos drenos destes transistores é 10μA, visto que eles conduzem as correntes nos ramos dos pares diferenciais que constituem o estágio de entrada, o bloco GM e o estágio de saída.

Assim, todos estes transistores apresentam as mesmas dimensões e, considerando uma tensão dreno-fonte de saturação  $V_{DS(sat)}$  de aproximadamente 250mV, estas dimensões podem ser:

$$(W/L)_{21,21B,22,22B,23,23B,24,24B,25,25B,26,26B} = 16\mu m/4 \mu m$$

(2.31)

Já o transistor *M*27 da Fig. 2.10 é compartilhado entre os dois espelhos triplos. Sua dimensão, conforme demonstrado em [26], deve ser:

$$(W/L)_{27} = \frac{1}{4}(W/L)_{demais} = 4\mu m/4\mu m$$

(2.32)

## 2.4. AJUSTES DE DIMENSIONAMENTO POR SIMULAÇÃO

Determinadas todas as dimensões dos dispositivos utilizados, inúmeras simulações de ponto de operação e de pequenos sinais foram feitas a fim de verificar se o dimensionamento manual havia sido feito corretamente. Como algumas aproximações foram feitas, já era esperado que ajustes provavelmente seriam realizados através de simulação e que os cálculos manuais serviriam mais como um guia de projeto, para se ter noção do comportamento esperado para o circuito.

Após a análise das simulações, as dimensões dos dispositivos foram alteradas, algumas drasticamente, e a Tabela 2.1 apresenta as dimensões para os transistores

calculadas manualmente e as ajustadas por simulação. A seção seguinte, que explora a análise em freqüência do amplificador de instrumentação, já considera as dimensões ajustadas (dimensões finais) dos dispositivos.

**Tabela 2.1 –** Resumo das dimensões dos transistores MOS utilizados.

|            |       | CÁLCULO MANUAL            | APÓS SIMULAÇÃO   |

|------------|-------|---------------------------|------------------|

| Transistor | Canal | (W/L) em [μm/μm]          | (W/L) em [μm/μm] |

| M1 e M2    | P     | 60/6                      | 60/6             |

| M3 e M4    | N     | 8/2                       | 60/2             |

| M5 e M6    | P     | 60/6                      | 60/6             |

| M7 e M8    | N     | 50/10                     | 40/8             |

| M11 e M12  | N     | 3/6                       | 10/20            |

| M13 e M14  | N     | 10/6                      | 10/6             |

| M15 e M16  | P     | 20/10                     | 20/10            |

| M21-M26B   | P     | 16/4                      | 20/4             |

| M27        | P     | 4/4                       | 5/4              |

| M32 e M33  | N     | 40/2                      | 40/2             |

| M34 e M41  | N     | 200/2                     | 200/2            |

|            |       | Total de transistores: 32 |                  |

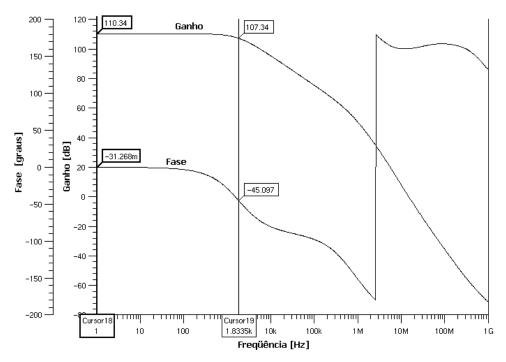

# 2.5. ANÁLISE EM FREQÜÊNCIA

O circuito do amplificador de instrumentação é um sistema um tanto quanto complexo por ser constituído de dois amplificadores distintos. Apesar de tal complexidade, estes amplificadores operam em malha fechada e são independentes entre si, visto que não há realimentação de um para o outro. Na verdade, o que ocorre é que o sinal de saída do amplificador na entrada do circuito alimenta o amplificador na saída do mesmo. Desta forma, estes amplificadores podem ser analisados separadamente, de forma que se saiba quais são as limitações em freqüência de cada um deles e, portanto, do amplificador de instrumentação.

Na entrada, pode-se identificar um amplificador de transcondutância, visto que a variável de saída é uma corrente que é proporcional à variável de entrada, que por sua vez

é uma tensão. Para este amplificador não houve necessidade de compensação em frequência conforme mostra a análise feita na subseção seguinte.

Na saída, o contrário do que acontece na entrada é observado, ou seja, a variável de saída é uma tensão proporcional à variável de entrada, que por sua vez é uma corrente, constituindo, portanto, um amplificador de transresistência. Neste amplificador, assim como feito em [10], utilizou-se um capacitor de compensação entre a entrada e a saída do par diferencial dentro do bloco AV, conforme indicado pela análise em freqüência feita na subseção 2.5.2.

### 2.5.1. Circuito de Entrada (Amplificador de Transcondutância)

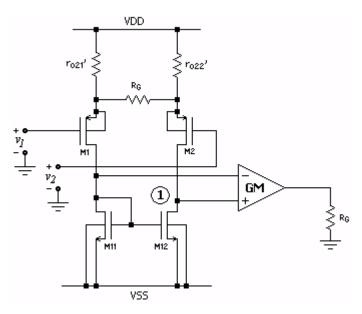

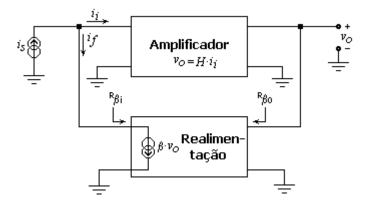

A Fig. 2.12 mostra o circuito do amplificador de transcondutância utilizado na entrada do amplificador de instrumentação. Este circuito é assim classificado por apresentar como variável de entrada uma tensão  $(v_I - v_2)$  e a corrente  $i_{out}$  como variável de saída [18], [19], [29].

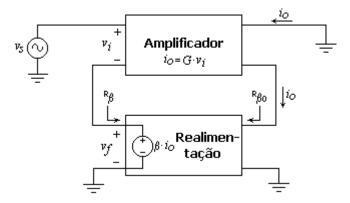

Reconhecendo-se que o tipo de realimentação empregada é tensão-corrente ou série-série (*series-series*) [29], como esquematizado na Fig. 2.13, resta identificar os elementos da Fig. 2.12 que desempenham os papéis daqueles da Fig. 2.13, para que o circuito possa ser melhor analisado. Para tanto, identifica-se, inicialmente, que a variável de entrada  $v_s$  é a própria tensão de entrada do amplificador de instrumentação  $(v_1 - v_2)$ . A variável de saída é a corrente  $i_{out}$  que flui pelos transistores M23 e M23B ou M24 e M24B. Já a tensão  $v_f$  é a tensão sobre o resistor  $R_G$ , dada por  $i_{out} \cdot R_G$ , como visto na seção 2.3. Portanto,  $\beta$  vale:

$$\beta = \frac{v_f}{i_{out}} = R_G \tag{2.33}$$

Fig. 2.12 - Circuito de entrada.

Sabendo-se quem desempenha o papel de  $\beta$ , pode-se determinar  $R_{\beta l}$  e  $R_{\beta o}$  como sendo ambos iguais a  $R_G$  a fim de se computar o efeito de carga da malha de realimentação ao se abrir a malha do amplificador. A Fig. 2.14 mostra então o circuito do amplificador de transcondutância em malha aberta.

Fig. 2.13 – Diagrama em blocos de um amplificador realimentado do tipo série-série.

Fig. 2.14 - Circuito de entrada em malha aberta.

Na Fig. 2.14, as resistências  $r_{o21}$ ' e  $r_{o22}$ ' representam as resistências de saída dos espelhos *cascode* do qual os transistores M21, M21B, M22 e M22B fazem parte. Referindose à Fig. 2.14, verifica-se que o nó de mais alta impedância é o nó 1, que, portanto, deve contribuir com um pólo dominante para o circuito de entrada. Os demais nós do circuito apresentam baixa impedância e devem contribuir com pólos em freqüências muito mais altas, não interessando, portanto, para esta análise simplificada. Dessa forma, computandose a resistência e a capacitância equivalentes deste nó a fim de calcular a constante de tempo associada ao mesmo, pode-se determinar a freqüência em que o pólo mais significativo de malha aberta ocorrerá.

No nó 1, a resistência equivalente pode ser calculada da mesma forma que na expressão (2.19), resultando em:

$$R_{eq1} = r_{o12} / [r_{o2} \cdot (2 + g_{m2} \cdot R_G)]$$

(2.34)

em que  $r_{o2}$  e  $r_{o12}$  são as resistências incrementais de saída dos transistores M2 e M12, respectivamente;  $g_{m2}$  é a transcondutância de M2.

Já, para computar a capacitância associada a este nó, devem ser consideradas todas as capacitâncias parasitas dos transistores MOS ligados a este nó, conforme mostra a seguinte expressão:

$$C_{eq1} = C_{db12} + C_{gd12} + C_{db2} + C_{gd2} + C_{gs4} + \left(1 + \frac{g_{m4}}{g_{m24}}\right) \cdot C_{gd4}$$

(2.35)<sup>3</sup>

onde  $C_{db2}$ ,  $C_{db12}$  são as capacitâncias dreno-substrato dos transistores M2 e M12, respectivamente;  $C_{gd2}$ ,  $C_{gd4}$  e  $C_{gd12}$  são as capacitâncias porta-dreno de M2, M4 e M12, respectivamente;  $C_{gs4}$  é a capacitância porta-fonte de M4.;  $g_{m4}$  e  $g_{m24}$  são as transcondutâncias de M4 e M24, respectivamente.

Assim, a frequência em que o pólo associado a este nó deve ocorrer, utilizandose os valores das transcondutâncias e capacitâncias dos transistores envolvidos, gerados como arquivo de saída (*output file*) pelo programa de simulação (ver Apêndice B), é:

$$\varpi_{1} = \frac{1}{R_{eq1} \cdot C_{eq1}} = \frac{1}{16,5M\Omega \cdot 0,304pF} = 199,63x10^{3} \, rad/s \quad (2.36)$$

ou

$$f_{1} = \frac{\omega_{1}}{2\pi} = 31,7kHz \quad (2.37)$$

No entanto, quando o amplificador de transcondutância é realimentado (e ele funciona sempre em malha fechada), a localização destes pólos no plano-s depende do ganho da malha de realimentação e, segundo Franklin, Powell e Emami-Naeini em [30], esta localização é dada por (considerando-se um sistema de primeira ordem, visto que há um único pólo):

$$s_1 = -\omega_1 \cdot (1 + \beta \cdot A_\alpha) \tag{2.38}$$

$<sup>^3</sup>$  Na expressão (2.35), a capacitância  $C_{gd4}$  aparece multiplicada pelo ganho de tensão do bloco GM devido ao efeito Miller.

em que  $A_o$  é o ganho de malha aberta do sistema para frequências médias, e para o amplificador de entrada é dado por (ver subseções 2.3.1 e 2.3.2 para as expressões de  $A_{MDI}$  e GM):

$$A_o = A_{MD1} \cdot GM = 1135 \cdot 84,05 \times 10^{-6} = 0,095 V / A$$

(2.39)

Desta forma, a frequência do pólo para o sistema realimentado dever ocorrer para a seguinte frequência:

$$s_1 = -199,6x10^3 \cdot (1+1000 \cdot 0,095) = -19,24x10^6 \, rad/s \text{ ou } -3,06\text{MHz}$$

(2.40)

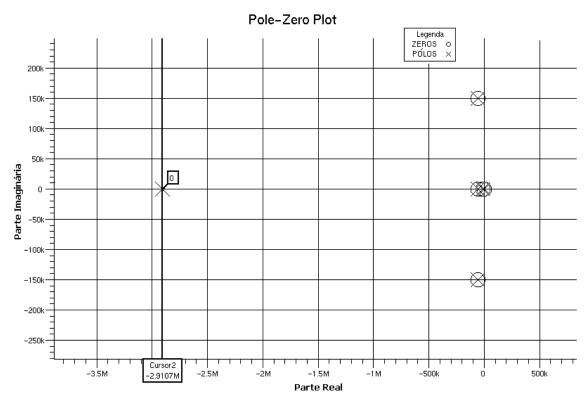

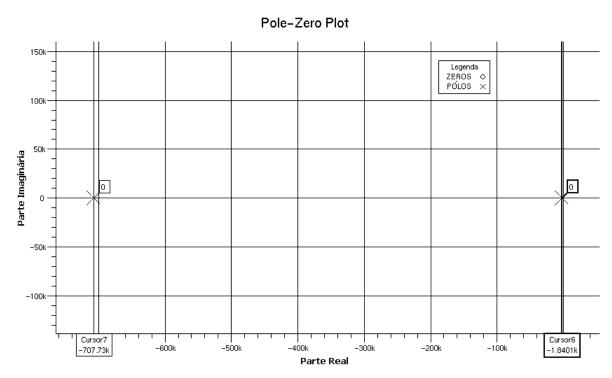

Por se tratar de um sistema com um único pólo, sua freqüência de -3dB (simbolizada por  $\omega_0$ ) corresponde à freqüência deste pólo. Frente a esses cálculos expostos para o amplificador de entrada, faz-se necessária uma simulação em freqüência para se averiguar se eles estão corretos. Desta forma, a Fig. 2.15 apresenta o resultado de uma simulação feita para o amplificador de transcondutância operando em malha fechada, mostrando o diagrama de pólos e zeros resultantes.

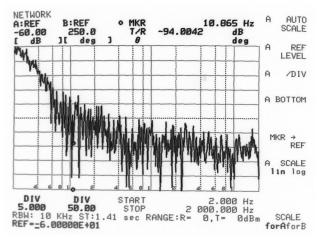

Fig. 2.15 – Diagrama de pólos e zeros para o amplficador de entrada em malha fechada (simulação).

Observando-se a Fig. 2.15, verifica-se que, realmente, existe apenas um pólo (os demais estão anulados por zeros ocorrendo na mesma freqüência) e que este pólo está localizado em –2,91MHz. Percebe-se, portanto, que o resultado está muito próximo do esperado pelos cálculos manuais (–3,06MHz), o que demonstra que o amplificador de entrada deve funcionar conforme previsto por eles.

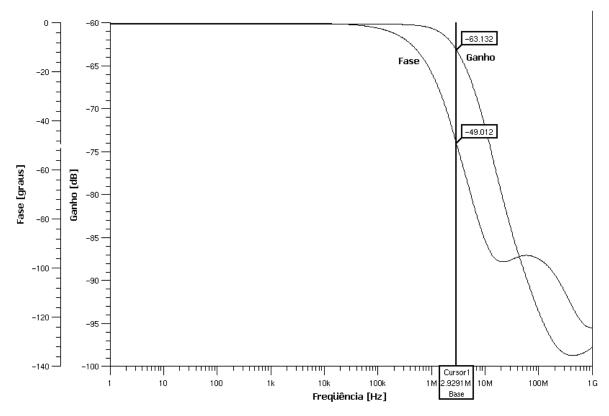

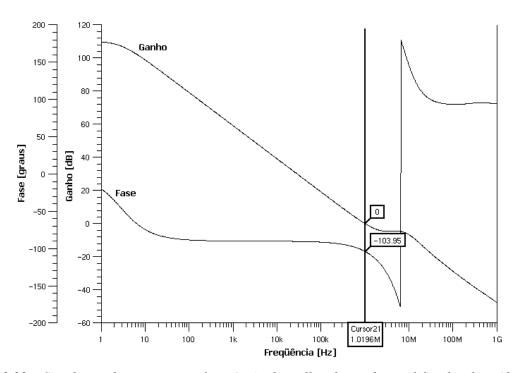

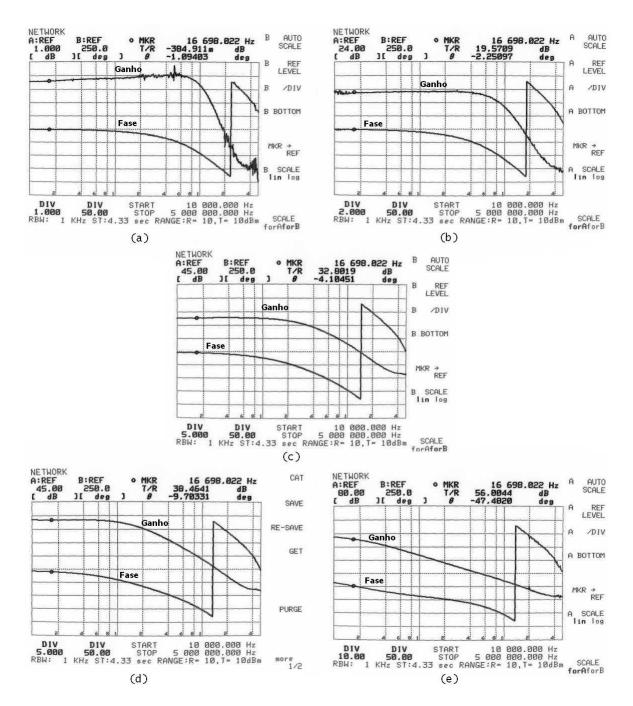

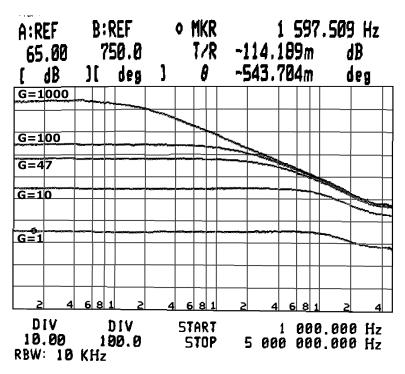

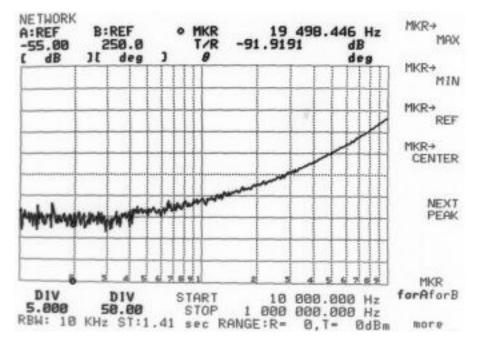

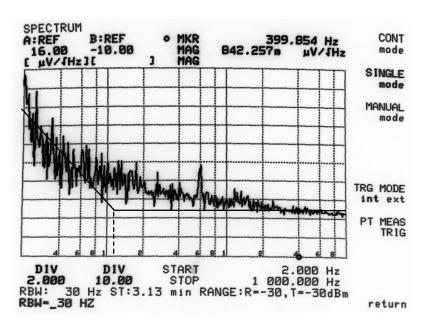

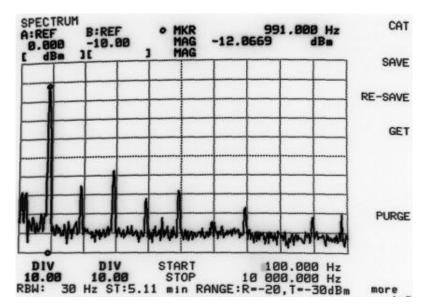

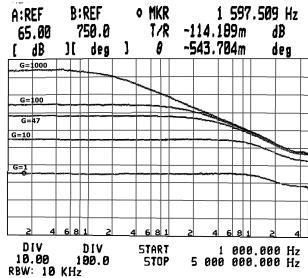

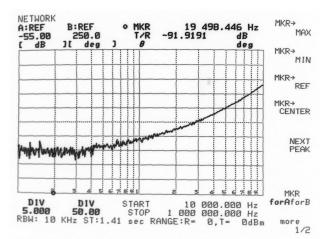

Uma outra simulação feita, ainda, para o amplificador de entrada, refere-se aos diagramas de Bode de ganho e fase. A Fig. 2.16 apresenta tais diagramas. Por esta figura, pode-se verificar que a freqüência de -3dB equivale à freqüência do único pólo do amplificador. As variações na fase após tal freqüência, devem-se provavelmente a zeros e pólos localizados em freqüências mais altas e desprezados nos cálculos manuais por conveniência. Vale observar ainda que a tensão AC aplicada na simulação foi de 1V. Assim, o ganho DC mostrado na Fig. 2.19 de -60dB, equivale a uma corrente de saída de 1mA, que corresponde à tensão de entrada dividida pelo resistor  $R_G$  de 1k $\Omega$ .

Fig. 2.16 – Simulação da resposta em freqüência de malha fechada do amplificador de entrada.

Assim, pode-se resumir o comportamento do amplificador de transcondutância nos parâmetros dispostos na Tabela 2.2. Como este amplificador não apresenta problemas de estabilidade por ser constituído de um único pólo, resta verificar a resposta em freqüência do amplificador de saída para se ter uma idéia do comportamento em freqüência do circuito completo do amplificador de instrumentação.

**Tabela 2.2 –** Resumo do comportamento em freqüência do amplificador de entrada.

| Ganho de realimentação                        | $\beta = 1000 \text{V/A} (R_G = 1 \text{k}\Omega)$                      |  |

|-----------------------------------------------|-------------------------------------------------------------------------|--|