#### Universidade Estadual de Campinas FEEC – Faculdade de Engenharia Elétrica e de Computação DSIF – Departamento de Semicondutores, Instrumentos e Fotônica

### Desenvolvimento de Receptor Óptico Integrado em Tecnologia HBT

Tese de mestrado apresentada à Faculdade de Engenharia Elétrica e Computação como parte dos requisitos para obtenção do título de Mestre em Engenharia Elétrica. Área de concentração: Eletrônica, Optoeletrônica e Microeletrônica.

Autor: Marcos Augusto de Goes Orientador: Jacobus Willibrordus Swart

#### Banca Examinadora:

Prof. Dr. Murilo Romero – USP/São Carlos

Prof. Dr. Everson Martins – UNESP/Guaratinguetá

Prof. Dr. José Alexandre Diniz – FEEC/UNICAMP

Campinas, SP Julho/2005

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

G554d

Goes, Marcos Augusto de

Desenvolvimento de receptor óptico integrado em tecnologia HBT / Marcos Augusto de Goes. -- Campinas, SP: [s.n.], 2005.

Orientador: Jacobus Willibrordus Swart Dissertação (Mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Transistores bipolares. 2. Fotodetectores. 3. Optoeletrônica. 4. Arseneto de Gálio. I. Swart, Jacobus Willibrordus. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

RMS-BAE

Development of integrated optic receiver in HBT technology Palavras-chave em Inglês: Bipolar transistors, Photodetectors, Optoelectronics e Gallium arsenide

Área de concentração: Eletrônica, Optoeletrônica e Microeletrônica

Titulação: Mestre em Engenharia Elétrica

Banca examinadora: Murilo Romero, Everson Martins e José Alexandre Diniz

Data da defesa: 29/07/2005

#### **RESUMO**

dissertação Esta de mestrado descreve o estudo, implementação de um receptor optoeletrônico integrado (OEIC) utilizando a tecnologia de transistores bipolares de heterojunção (HBT), fabricados a partir do material semicondutor arseneto de gálio. A grande vantagem deste transistor é o seu alto ganho e baixa resistência de base, o qual possibilita operações na faixa de gigahertz. A integração do estágio de fotodetecção, feita por um fotodiodo do tipo PIN, com o circuito de amplificação em um mesmo circuito integrado é possível, pois o fotodetector é construído com as camadas de base, coletor e subcoletor do transistor HBT. Com isso, as resistências, capacitâncias e indutâncias parasitas presentes na conexão entre estes dois estágios são minimizadas. Isto permite aos receptores monolíticos trabalharem em fregüências mais altas em relação aos receptores híbridos. O circuito fabricado opera com fontes de luz no comprimento de onda de 850 nm e pode ser utilizado em redes locais de curta distância (LAN).

## **ABSTRACT**

This master degree dissertation describes the study, project and implementation of an optoelectronic integrated circuit (OEIC) using the heterojunction bipolar transistors (HBT) technology over a gallium arsenide substrate. The major advantage of this transistor is its high gain and low base resistance, allowing operation at frequencies in the range of gigahertz. The integration of the photodetection stage, performed by a *PIN* photodetector, with the amplifier circuit in a single chip is possible because the photodetector is built from the base, collector and subcollector layers of the HBT transistor. Thus, the parasitic resistances, capacitances and inductances between the connection of these two stages are minimized. In this way, monolithic receivers can operate at higher frequencies than hybrid receivers. The fabricated circuit is intended to work with 850 nm light sources and can be used in local area networks (*LAN*).

Para meus pais, Orlando e Leonilda; meus irmãos Rafael e Henrique; meu grande amor, Daniella.

Este trabalho foi realizado com o apoio das seguintes entidades:

- ❖ FAPESP Auxílio Bolsa de Mestrado;

- ❖ AEB (Agência Espacial Brasileira);

- CCS/UNICAMP;

- DSIF/UNICAMP;

- ❖ IFGW/UNICAMP.

## **AGRADECIMENTOS**

Após a finalização desta importante etapa em minha vida, gostaria de agradecer todas as pessoas e instituições que me ajudaram na realização deste trabalho, dentre elas:

- meu orientador, Prof. Dr. Jacobus Willibrordus Swart pelo apoio, pela oportunidade e confiança em mim depositada,

- Dra. Maria Beny Zakia, Dr. Luiz Eugênio de Barros, Dr. Everson Martins e Dr. Augusto Redolfi, pelas valiosas discussões durante a fase de projeto,

- Dr. Ricardo Yoshioka, por me ensinar todas as etapas de fabricação em laboratório,

- todos os funcionários do CCS/UNICAMP e do LPD/IFGW, pela amizade e ajuda nos procedimentos de laboratório,

- > todos os amigos mestrandos e doutorandos do CCS, em especial Leonardo Breseghello Zoccal, por toda ajuda neste trabalho,

- Sr. Valentino Corso do CPqD, pela disponibilização dos equipamentos para a caracterização elétrica e óptica do circuito,

- Deus, por ter me dado a capacidade de realizar este trabalho.

## Sumário

| Capítulo 1 - Introdução                                                                       | 1        |

|-----------------------------------------------------------------------------------------------|----------|

| 1.1 - Histórico                                                                               | 1        |

| 1.2 - Objetivo da dissertação                                                                 | 2        |

| 1.3 - Organização da dissertação                                                              | 3        |

| Capítulo 2 - Circuitos Integrados Optoeletrônicos (OEIC)                                      | 5        |

| 2.1 - Introdução                                                                              | 5        |

| 2.1 - Introdução                                                                              | 6        |

| 2.2.1 - Fotodiodo                                                                             | 6        |

| 2.2.1 - Fotodiodo  2.2.1.1 - As bandas de energia                                             | 6        |

| 2.2.1.2 - Mecanismos de fotogeração                                                           | 7        |

| 2.2.1.3 - Fotodetectores                                                                      | 9        |

| 2.2.1.4 - Fotodiodo <i>PIN</i>                                                                | 13       |

| 2.2.1.5 - Corrente de escuro                                                                  | 15       |

| 2.2.1.6 - Escolha do material e resposta em frequência de um fotodetector <i>PIN</i>          | 15       |

| 2.2.2 - Transistores bipolares de heterojunção (HBT)                                          | 18       |

| 2.2.2.1 - Principio de funcionamento do transistor HB1                                        | 18       |

| 2.2.2.2 - Figuras de mérito da heterojunção                                                   | 19       |

| 2.2.2.3 - Operação com sinais AC                                                              | 20       |

| 2.2.2.4 - Modelagem e extração de parâmetros do transistor HBT                                | 22       |

| 2.2.3 - Resistores                                                                            | 39       |

| Capítulo 3 - Etapas de projeto do circuito integrado                                          | 43       |

| 3.1 - Introdução                                                                              | 43       |

| 3.2 - Fotodetectores                                                                          | 44       |

| 3.3 - Resistores                                                                              | 47       |

| 3.4 - Transistores bipolares de heterojunção                                                  | 48       |

| 3.5 - Estruturas TLM                                                                          | 50       |

| 3.5 - Estruturas TLM 3.6 - Circuito de transimpedância                                        | 51       |

| Capítulo 4 - Fabricação do circuito integrado                                                 | 63       |

| 4.1 - Introdução                                                                              | 63       |

| 4.1 - Introdução                                                                              | 63       |

| 4.3 - Etapas de processo                                                                      | 64       |

| 4.3.1 - Limpeza orgânica 4.3.2 - Fotolitografia para definição de contato de emissor          | 64       |

| 4.3.2 - Fotolitografía para definição de contato de emissor                                   | 65       |

| 4.3.3 - Metalização                                                                           | 6/       |

| 4.3.4 - Recozimento térmico do metal de contato                                               | 69       |

| 4.3.5 - Fotolitografia para definição da mesa de emissor                                      | 69       |

| 4.3.6 - Corrosão úmida para definição da mesa de emissor                                      |          |

| 4.3.7 - Fotolitografia e evaporação de contato de base                                        | 74       |

| 4.3.8 - Fotolitografía para definição da mesa de base e corrosão da camada                    | 77       |

| 4.3.9 - Fotolitografia para evaporação de contatos de subcoletor do HBT,                      |          |

| contatos N do <i>PIN</i> e contatos dos resistores                                            |          |

| 4.3.10 - Tratamento térmico: <i>Alloy</i>                                                     | 79       |

| 4.3.11 - Fotolitografia para isolação dos dispositivos                                        | 82       |

| 4.3.12 - Planarização dos dispositivos 4.3.13 - Fotogravação e corrosão para abertura de vias | 83       |

| 4.3.13 - rotogravação e corrosão para apertura de vias                                        | 84       |

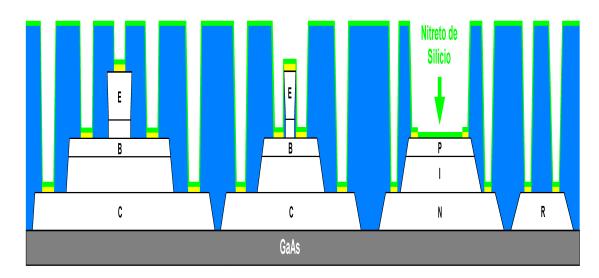

| 4.3.14 - Deposição de nitreto de silício (Si <sub>3</sub> N <sub>4</sub> )                    | 85       |

| 4.3.15 - Fotolitografia para abertura de vias                                                 | 86<br>87 |

| T IV - I VIVIII VETATIA VATA CVADVIACAV UV HICIAI UC HILCICVIICXAV                            | 0/       |

| Capítulo 5 - Caracterização do circuito integrado                | 95  |

|------------------------------------------------------------------|-----|

| 5.1 - Introdução                                                 | 9:  |

| 5.2 - Resultados DC                                              | 9:  |

| 5.2.1 - Resistores                                               | 9:  |

| 5.2.2 - Estruturas TLM                                           | 96  |

| 3.2.3 - Halisistoles fib i                                       | 9.  |

| 5.2.3.1 - Transistor HBT 20x06 µm² não auto-alinhado             | 97  |

| 5.2.3.2 - Transistor HBT 20x16 µm² não auto-alinhado             | 100 |

| 5.2.3.3 - Transistor HBT 20x06 µm² auto-alinhado                 | 102 |

| 5.2.3.4 - Transistor HBT 20x16 µm² auto-alinhado                 | 104 |

| 5.3 - Resultados AC                                              |     |

| 5.3.1 - Resistores                                               | 107 |

| 5.3.2 - Transistores HBT                                         | 108 |

| 5.3.2.1 - Transistor HBT 20x06 μm² não auto-alinhado             | 108 |

| 5.3.2.2 - Transistor HBT 20x16 µm² não auto-alinhado             | 110 |

| 5.3.2.3 - Resumo das medidas dos transistores não auto-alinhados | 111 |

| 5.3.2.4 - Transistor HBT 20x06 μm² auto-alinhado                 | 112 |

| 5.3.2.5 - Transistor HBT 20x16 µm² auto-alinhado                 |     |

| 5.3.2.6 - Resumo das medidas dos transistores auto-alinhados     | 114 |

| 5.3.3 - Circuito amplificador de transimpedância                 | 115 |

| 5.4 - Resultados das medidas ópticas                             | 12: |

| 5.4.1 - Medidas dos fotodetectores <i>PIN</i>                    | 124 |

| 5.4.2 - Medidas do circuito de transimpedância                   | 120 |

| Capítulo 6 - Conclusões e perspectivas                           | 129 |

| Bibliografia                                                     | 13: |

## Índice de Figuras

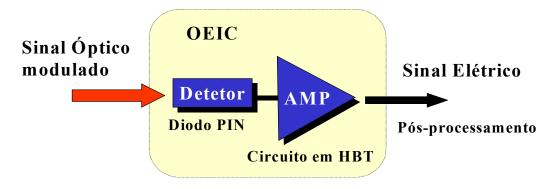

| Figura | 2.1 - Esquema do circuito optoeletrônico a ser integrado                                                                      | 5                |

|--------|-------------------------------------------------------------------------------------------------------------------------------|------------------|

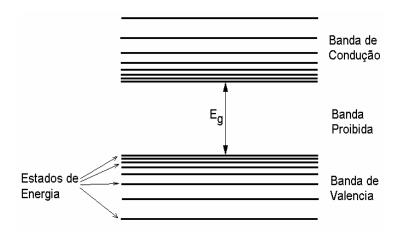

| Figura | 2.2 - Bandas de energia em um semicondutor intrínseco (sem impurezas)                                                         | 6                |

| Figura | 2.3 - Fotogeração por recombinação direta                                                                                     | 8                |

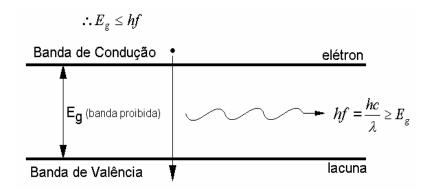

| Figura | 2.4 - Geração de pares elétron-lacuna por fotoionização                                                                       | 9                |

| Figura | 2.5 - Distribuição de carga, campo elétrico e potencial em uma                                                                |                  |

| j      | unção PN reversamente polarizada                                                                                              | 10               |

| Figura | 2.6 - Coeficiente de absorção de luz para diversos materiais                                                                  | _11              |

| Figura | 2.7 - Estrutura idealizada do fotodiodo <i>PIN</i>                                                                            | _12              |

| Figura | 2.8 - Circuito equivalente do fotodiodo PIN                                                                                   | _16              |

| Figura | 2.9 - Diagrama de bandas para um BJT e para um HBT                                                                            | _19              |

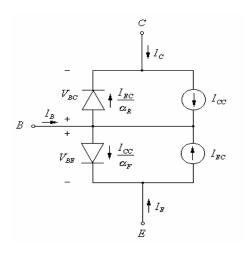

| Figura | 2.10 - Modelo Ebers-Moll                                                                                                      | _23              |

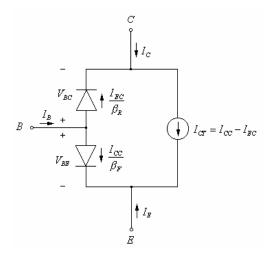

| Figura | 2.11 - Modelo Ebers-Moll modificado                                                                                           | _24              |

| Figura | 2.12 - Modelo Ebers-Moll com efeitos de primeira ordem (EM <sub>2</sub> )                                                     | _26              |

| Figura | 2.13 - Transistor bipolar com resistências parasitárias nos terminais                                                         | _26              |

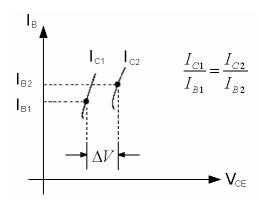

| Figura | 2.14 - Esquema elétrico para cálculo de r <sub>e</sub> ' e gráfico I <sub>B</sub> xV <sub>CE</sub>                            | _27              |

| Figura | 2.15 - Esquema elétrico para cálculo de r <sub>c</sub> ' e gráfico I <sub>B</sub> xV <sub>CE</sub> variando-se I <sub>C</sub> | _27              |

| Figura | 2.16 - Seção expandida das curvas para obtenção de ΔV                                                                         | _28              |

| Figura | 2.17 - Resistência de base distribuida                                                                                        | _29              |

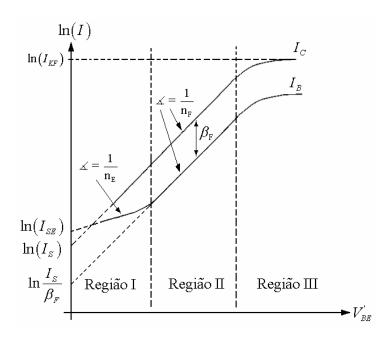

| Figura | 2.18 - Gummel-Plot                                                                                                            | _31              |

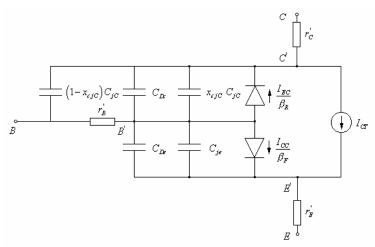

| Figura | 2.19 - Distribuição de C <sub>JC</sub> através de r <sub>b</sub> '                                                            | 34               |

| Figura | 2.20 - Modelo equivalente utilizado em altas frequências                                                                      | _35              |

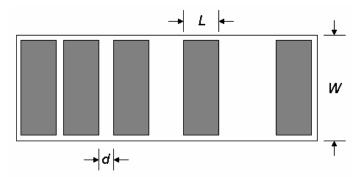

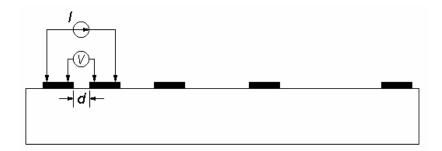

| Figura | 2.21 - Vista superior de uma estrutura TLM                                                                                    | 40               |

| Figura | 2.22 - Procedimento de medidas em TLM                                                                                         | _<br>40          |

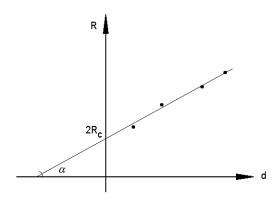

| Figura | 2.23 - Gráfico obtido da medida de uma estrutura TLM                                                                          | _41              |

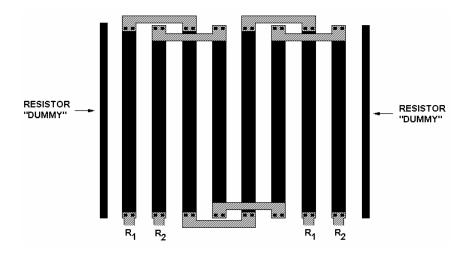

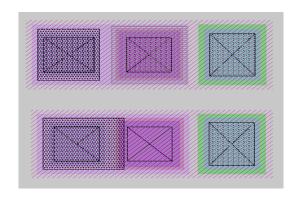

|        | 2.24 - Técnica de <i>layout</i> para obtenção de resistores casados                                                           | _<br>42          |

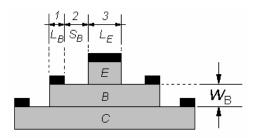

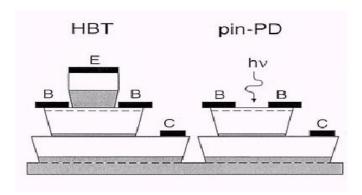

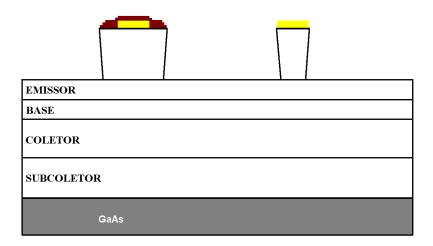

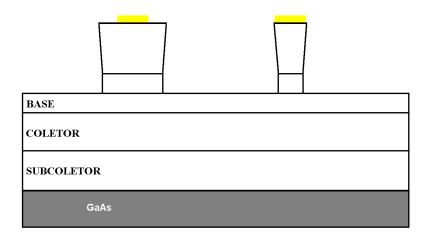

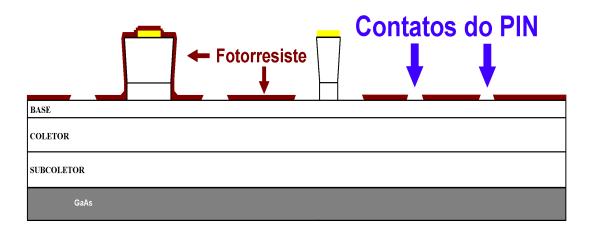

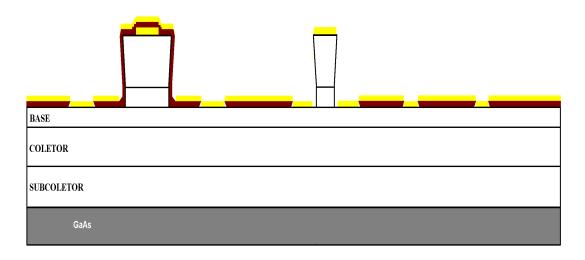

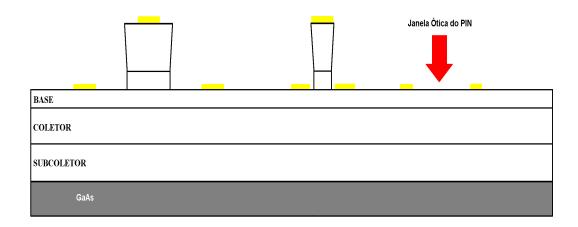

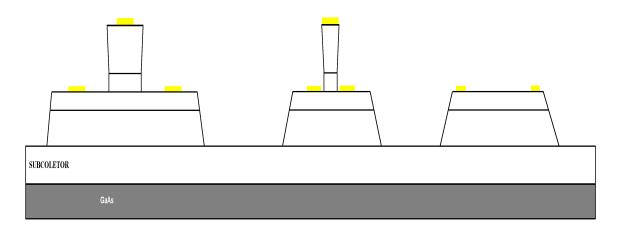

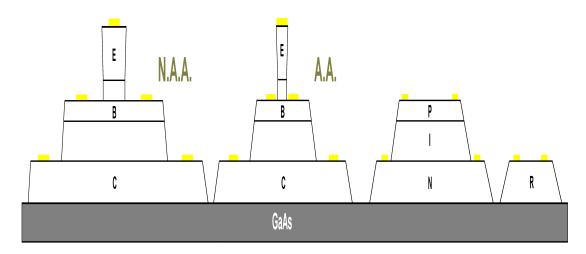

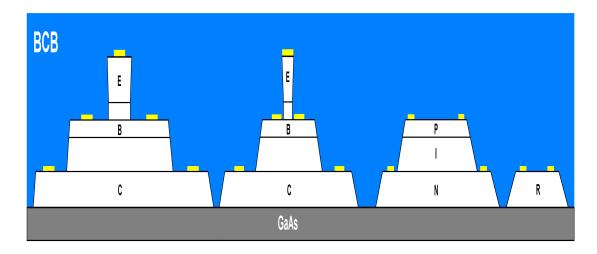

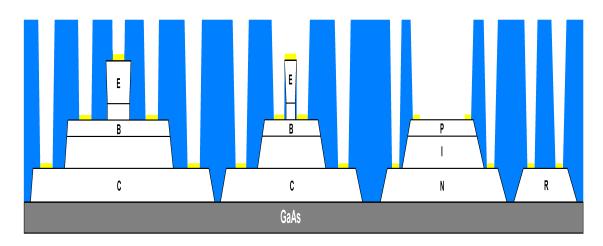

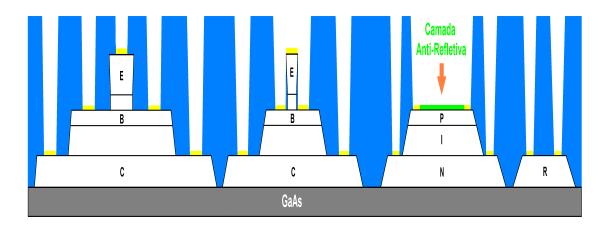

| Figura | 3.1 - Compatibilidade no processo de fabricação do fotodetector <i>PIN</i> e o transistor HBT                                 | _<br>44          |

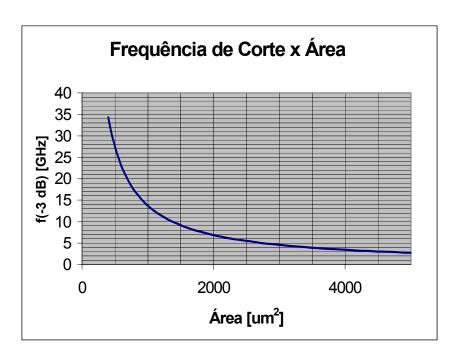

| Figura | 3.2 - Relação entre a frequência de corte do detector e sua área de iluminação                                                | 45               |

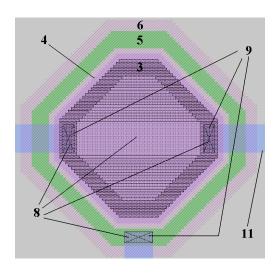

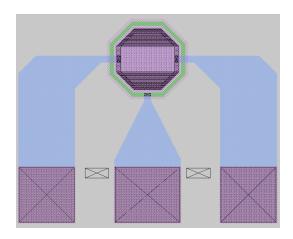

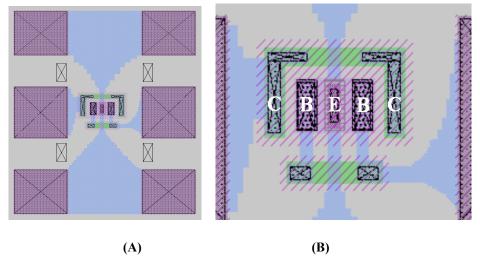

|        | 3.3 - <i>Layout</i> dos fotodetectores                                                                                        | _<br>46          |

| Figura | 3.4 - Fotodetector + pads GSG                                                                                                 | _<br>46          |

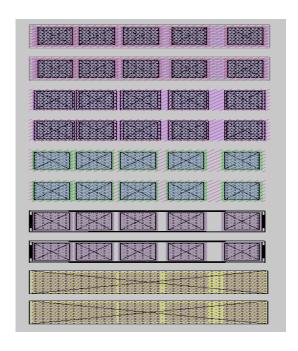

| Figura | 3.5 - <i>Layout</i> de um resistor integrado                                                                                  | _<br>47          |

| Figura | 3.6 - <i>Layout</i> dos resistores discretos: 50, 260, 300, 400 e 1000 Ω                                                      | 48               |

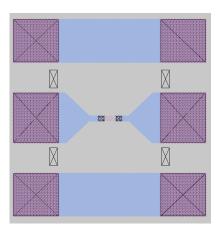

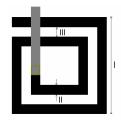

| Figura | 3.7 - Detalhes do l <i>ayout</i> do transistor HBT auto-alinhado de área 20x16 µm <sup>2</sup>                                | 48               |

| _      | 3.8 - Detalhes do l <i>ayout</i> do transistor HBT não auto-alinhado de área 20x06 µm <sup>2</sup>                            | _<br>49          |

|        | 3.9 - Estruturas em aberto e em curto, para a obtenção de parasitas                                                           | 49               |

|        | 3.10 - Layout dos transistores de área grande                                                                                 | _<br>50          |

|        | 3.11 - Layout das estruturas TLM                                                                                              | 50               |

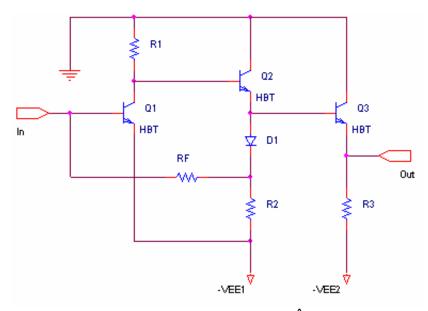

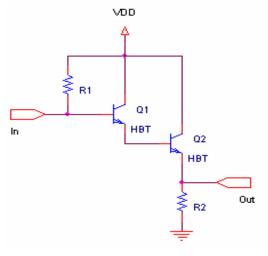

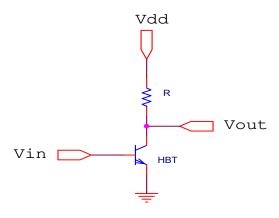

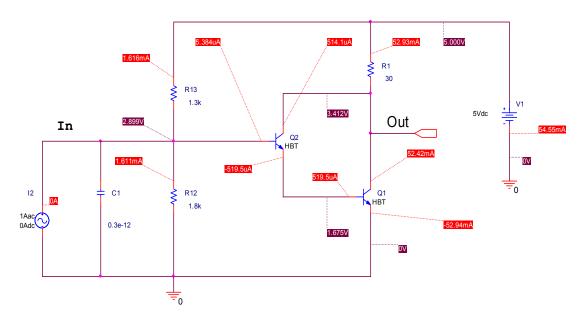

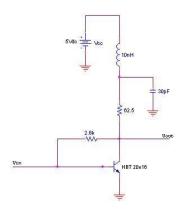

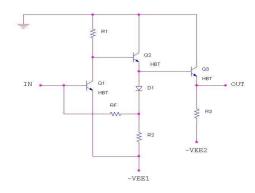

| -      | 3.12 - Circuito de transimpedância proposto                                                                                   | <sup>-</sup> 51  |

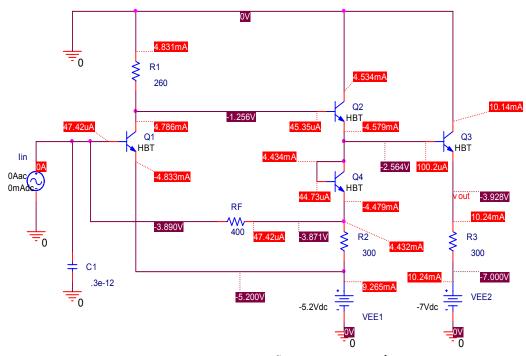

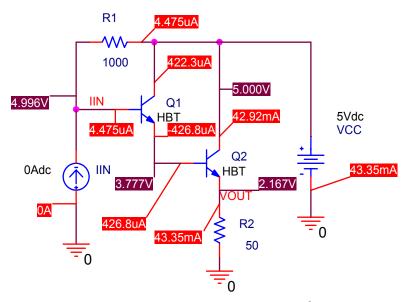

|        | 3.13 - Correntes e tensões nos diversos nós do circuito                                                                       | <sup>-</sup> 52  |

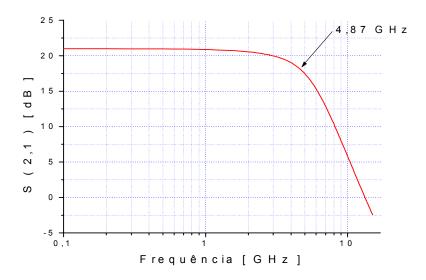

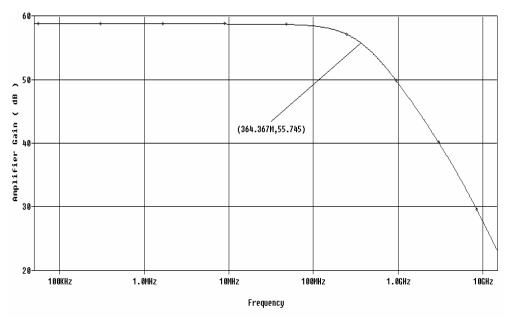

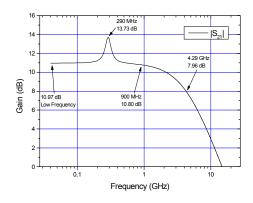

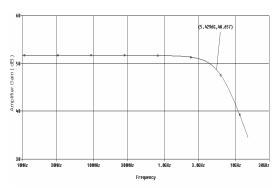

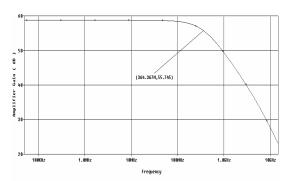

|        | 3.14 - Ganho simulado do circuito                                                                                             | _<br>53          |

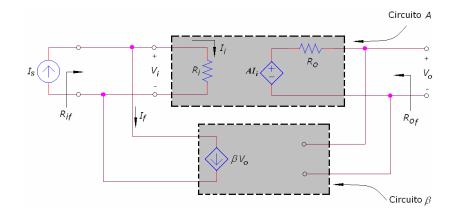

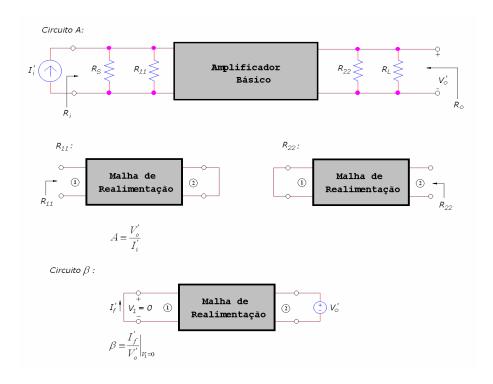

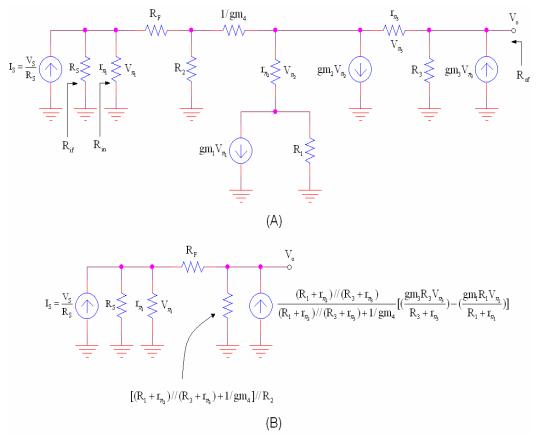

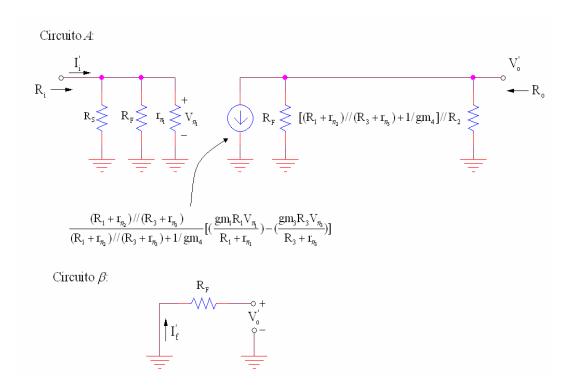

|        | 3.15 - Amostragem de tensão com comparação paralela (realimentação paralelo-paralelo)                                         | _<br>54          |

|        | 3.16 - Determinação dos valores de A e β                                                                                      | _<br>55          |

|        | 3.17 - Circuito utilizado para cálculo de resistência de entrada e saída com realimentação                                    | -56              |

| _      | 3.18 - Circuitos A e β utilizados para os cálculos das resistências de entrada e saída                                        | _57              |

|        | 3.19 - Perdas de retorno na entrada e saída do circuito                                                                       | $-\frac{57}{58}$ |

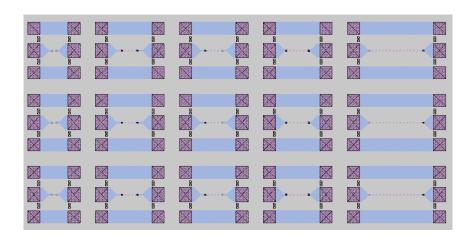

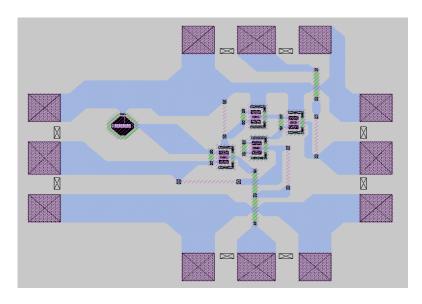

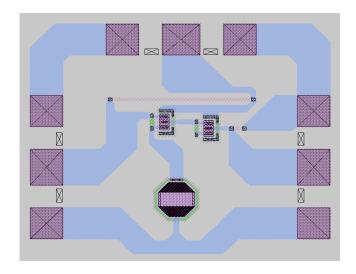

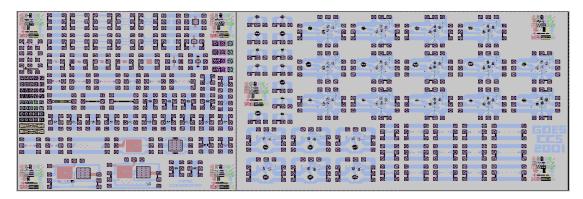

| _      | 3.20 - <i>Layout</i> final do circuito de transimpedância                                                                     | -50<br>59        |

|        | 3.21 - Circuito de transimpedância utilizando par Darlington                                                                  | -59              |

|        | 3.22 - Correntes e tensões em cada nó do circuito                                                                             | -60              |

|        | 3.23 - Resposta em frequência do circuito de transimpedância utilizando par Darlington                                        | $-\frac{60}{60}$ |

|        | 3.24 - Layout final do circuito de transimpedância na configuração Darlington                                                 | -61              |

| -      | 3.25 - <i>Layout</i> das marcas de alinhamento                                                                                | -61              |

|        | 4. 1 - Material semicondutor utilizado para fabricação do circuito integrado                                                  | -64              |

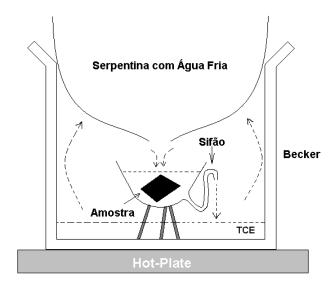

|        | 4. 2 - Sistema utilizado para limpeza orgânica da lâmina                                                                      | -64              |

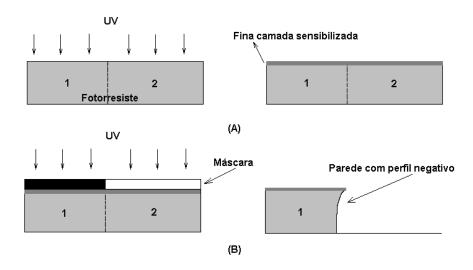

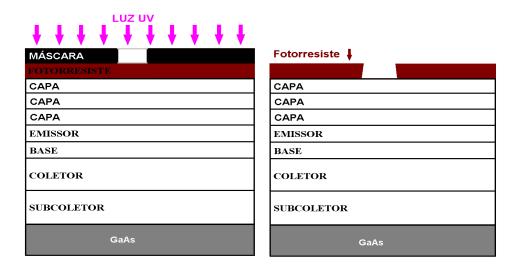

| _      | 4. 3 - Exposição litográfica do tipo <i>flood</i> e com máscara, para proceso <i>lift-off</i>                                 | -66              |

|        |                                                                                                                               |                  |

| Figura 4. 4 - Fotogravação para definição de contato de emissor                                          | 67                                       |

|----------------------------------------------------------------------------------------------------------|------------------------------------------|

| Figura 4. 5 - Metalização para obtenção do contato de emissor do transistor HBT                          | 68                                       |

| Figura 4. 6 - Contato de emissor após o <i>lift-off</i>                                                  | 69                                       |

| Figura 4. 7 - Fotolitografia para definição da mesa de emissor                                           | 70                                       |

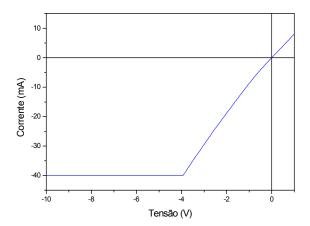

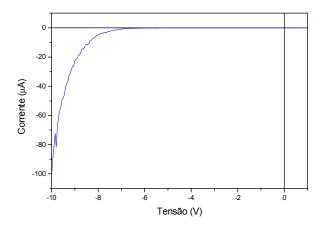

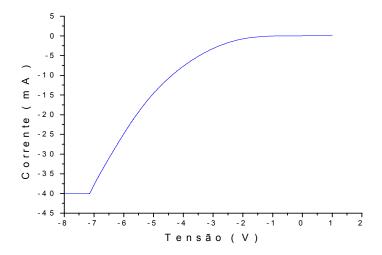

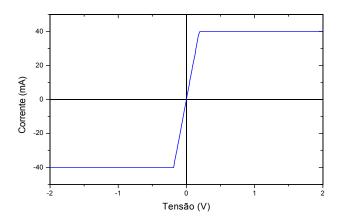

| Figura 4. 8 - Medidas de curva de diodo                                                                  | 71                                       |

| Figura 4. 9 - Curva de diodo para camada de capa                                                         | 71                                       |

| Figura 4. 10 - Curva de diodo para camada de emissor                                                     | 72                                       |

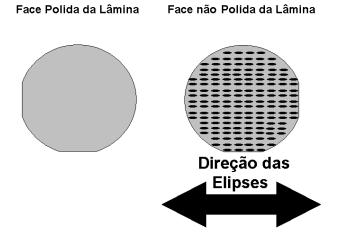

| Figura 4. 11 - Orientação da rede cristalina da lâmina                                                   | 72                                       |

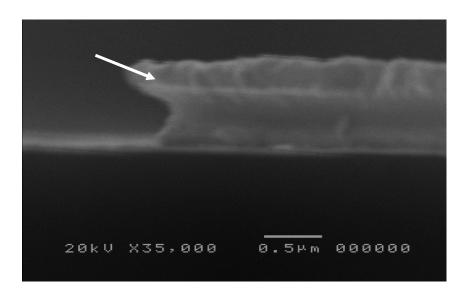

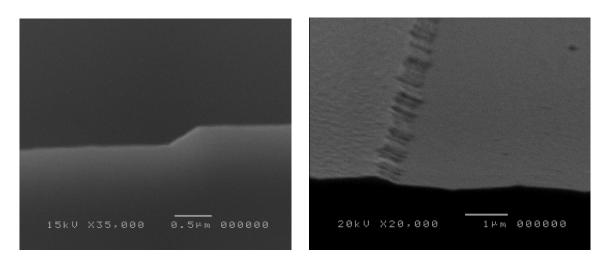

| Figura 4. 12 - Perfil negativo gerado na mesa de emissor pela corrosão por solução                       | $\overline{\text{de H}_2\text{SO}_4}$ 73 |

| Figura 4. 13 - Remoção das camadas de capa após o etching                                                | 72                                       |

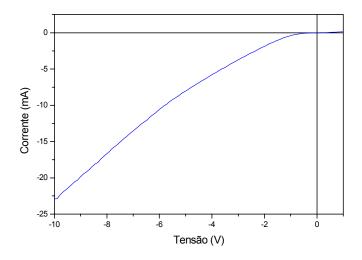

| Figura 4. 14 - Curva de corrente reversa para camada de base                                             | 74                                       |

| Figura 4. 15 - Remoção da camada de emissor com ácido clorídrico                                         | 74                                       |

| Figura 4. 16 - Fotolitografia para definição das regiões de contato de                                   |                                          |

| base do HBT e contato P do fotodetector PIN                                                              | 75                                       |

| Figura 4. 17 - Evaporação de Ti, Pt e Au                                                                 | 76                                       |

| Figura 4. 18 - Contatos formados após <i>lift-off</i> e limpeza plasma-barril B                          | 76                                       |

| Figura 4. 19 - Curva de diodo para a camada de subcoletor                                                | 77                                       |

| Figura 4. 20 - Região de subcoletor após a remoção das camadas de base e subcolet                        |                                          |

| Figura 4. 21 - Perfil positivo gerado pela corrosão úmida com solução de ácido fosf                      |                                          |

| Figura 4. 22 - Evaporação do terceiro contato do transistor HBT                                          | 79                                       |

| Figura 4. 23 - Curva característica I <sub>C</sub> xV <sub>CE</sub> para transistor não                  |                                          |

| auto-alinhado de área de emissor grande                                                                  | 80                                       |

| Figura 4. 24 - Gráfico <i>Gummel-Plot</i> para transistor não auto-alinhado                              |                                          |

| Figura 4. 25 - Curva característica ICxVCE para transistor                                               | 00                                       |

| auto-alinhado de área de emissor grande                                                                  | 81                                       |

| Figura 4. 26 - Gráfico <i>Gummel-Plot</i> para transistor auto-alinhado                                  |                                          |

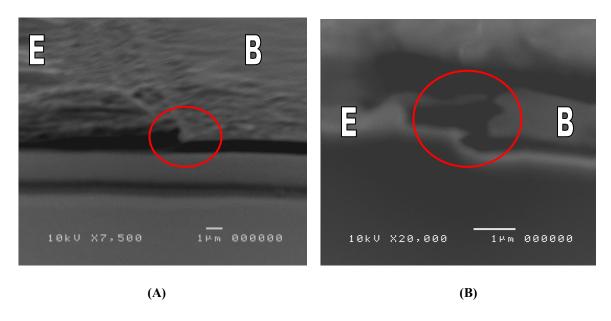

| Figure 4.27 Datalhas do parfil do maso do amissar                                                        | 92                                       |

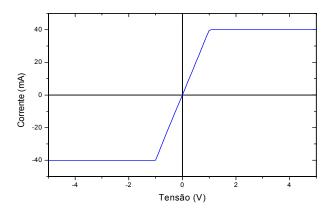

| Figura 4. 28 - Curva de corrente reversa para o substrato de GaAs                                        |                                          |

| Figure 4 20 Correção para isolação dos dispositivos                                                      | 92                                       |

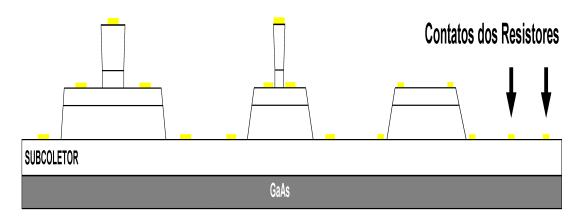

| Figura 4. 30 - Planarização dos dispositivos, pelo polímero BCB                                          |                                          |

| Figura 4. 31 - Verificação da abertura das vias                                                          |                                          |

| Figura 4. 32 - Abertura de vias para acesso aos contatos                                                 |                                          |

| Figura 4. 33 - Deposição de Si <sub>3</sub> N <sub>4</sub>                                               | 86                                       |

| Figura 4. 34 - Verificação da abertura das vias no nitreto de silício                                    |                                          |

| Figura 4. 35 - Abertura de vias pelo nitreto de silício                                                  | 87                                       |

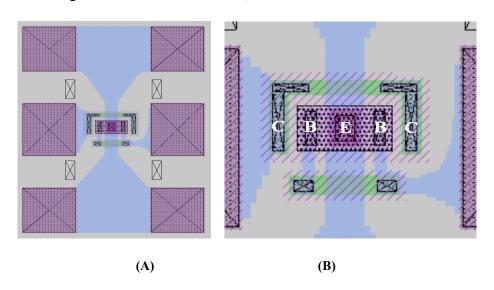

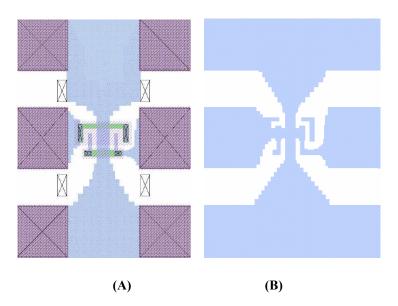

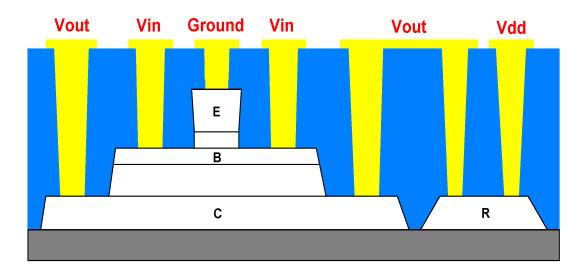

| Figura 4. 36 - Exemplo de integração de um circuito                                                      | 88                                       |

| Figura 4. 37 - Exemplo de integração de um circuito e ilustração das interconexões                       |                                          |

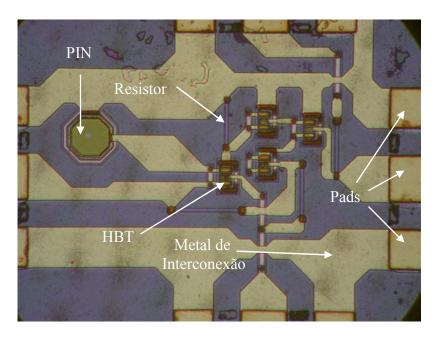

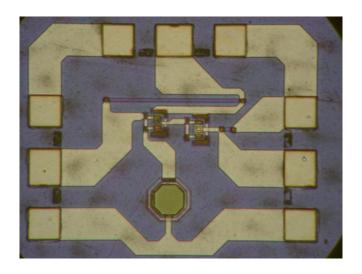

| Figura 4. 38 - OEIC fabricado                                                                            | 89                                       |

| Figura 4. 39 - OEIC na configuração Darlington                                                           | 89                                       |

|                                                                                                          |                                          |

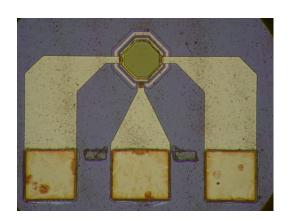

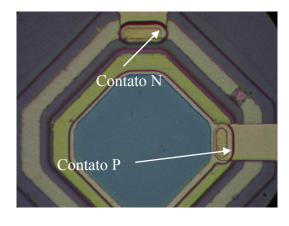

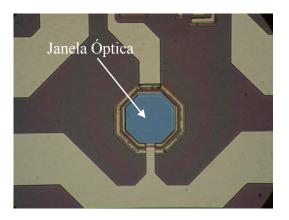

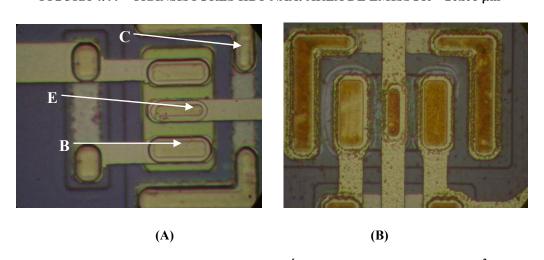

| Figure 4. 41 Petallac des fetaletatores <i>BIN</i>                                                       | 90                                       |

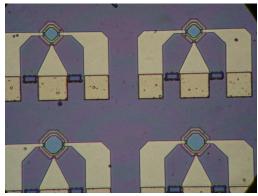

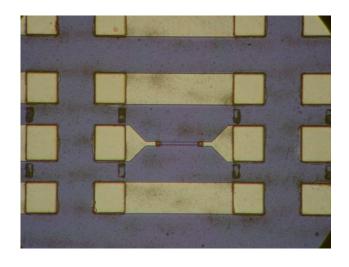

| Figure 4. 41 - Detalles dos fotodetectores PIN                                                           | 90                                       |

| Figure 4. 42 - Detalhes dos fotodetectores PIN                                                           | 90                                       |

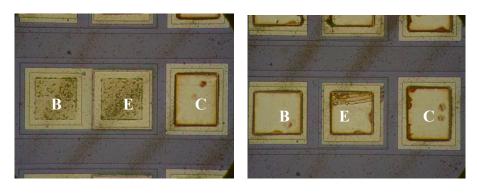

| Figura 4. 43 - Transistores de grande área                                                               |                                          |

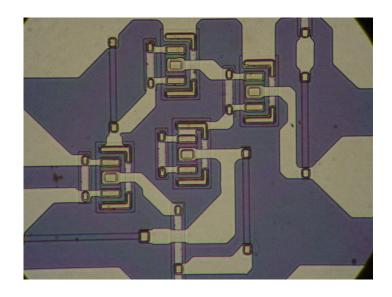

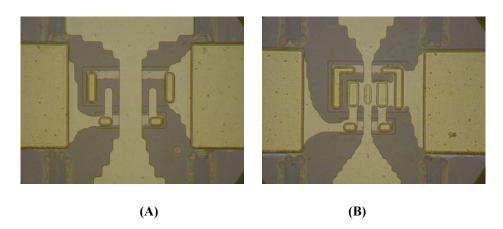

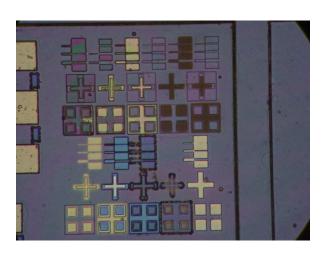

| Figure 4. 44 - Transistores HBT não auto-alinhados                                                       | 91                                       |

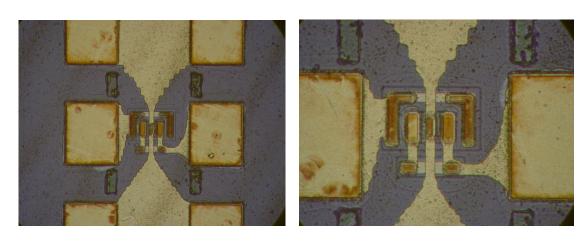

| Figura 4. 45 - HBT auto-alinhado e não auto-alinhado                                                     | 0.0                                      |

| Figura 4. 46 - HBT em aberto e em curto                                                                  | 92                                       |

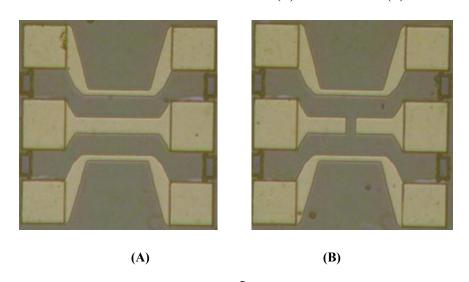

| Figura 4. 47 - Linha de transmissão em curto e em aberto                                                 |                                          |

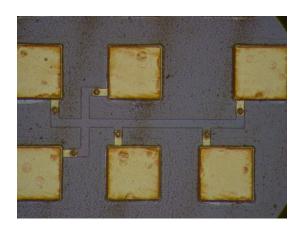

| Figura 4. 48 - Estruturas TLM                                                                            | 92                                       |

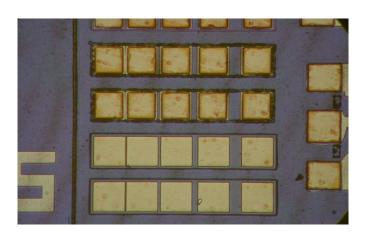

| Figura 4. 49 - Resistor feito com a camada de subcoletor                                                 | 93                                       |

| Figura 4. 50 - Marcas de alinhamento utilizadas durante o processo de fabricação _                       |                                          |

| Figura 4. 51 - Detalhe da cruz-grega                                                                     |                                          |

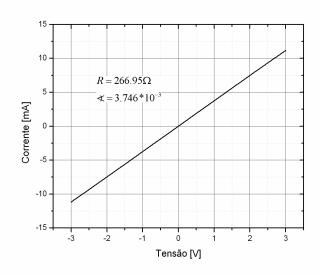

| Figura 5. 1 - Medida DC de um resistor de 260 Ω                                                          |                                          |

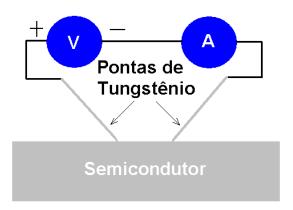

| Figura 5. 2 - Setup de medidas para obtenção do <i>Gummel-plot</i>                                       | 98                                       |

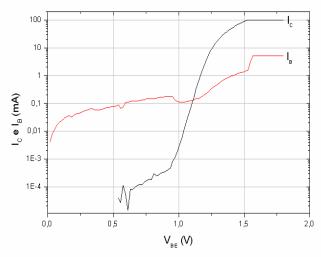

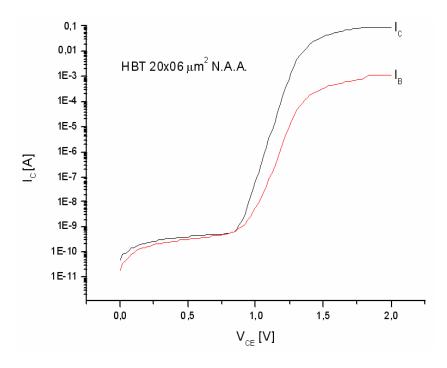

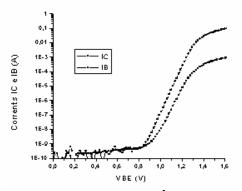

| Figura 5. 3 - Gummel-plot para HBT 20x06 μm <sup>2</sup> N.A.A.                                          | 98                                       |

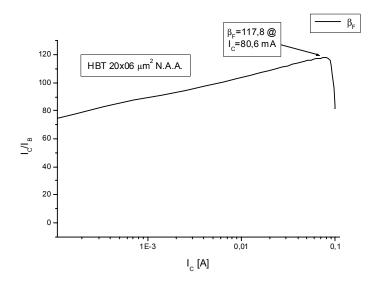

| Figura 5. 4 - Variação de $\beta_F$ com a corrente de coletor para HBT 20x06 $\mu m^2$ N.A.A             |                                          |

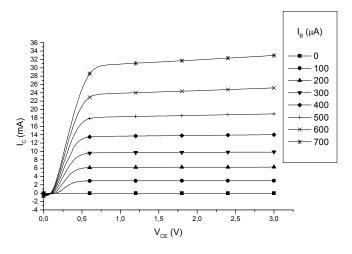

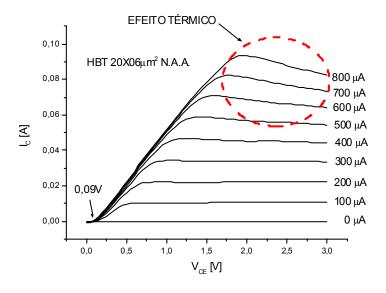

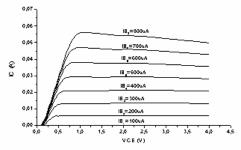

| Figura 5. 5 - Curva característica I <sub>C</sub> xV <sub>CE</sub> para HBT 20x06 μm <sup>2</sup> N.A.A. | 99                                       |

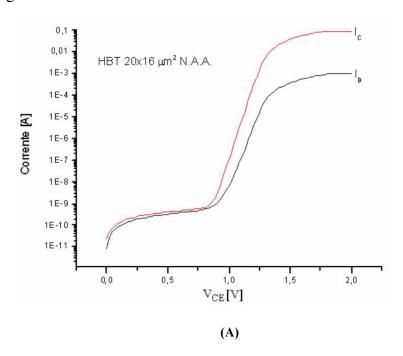

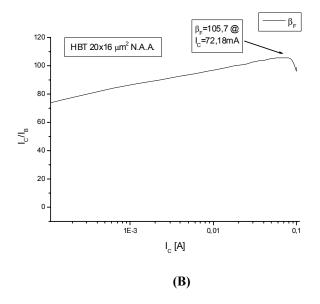

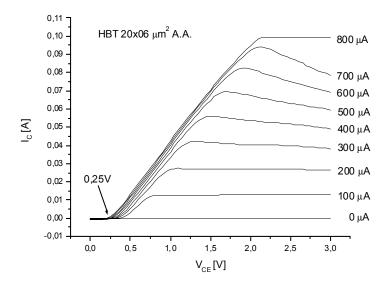

| Figura 5. 6 - Gummel-plot e ganho $\beta_F$          | para HBT 20x16 μm <sup>2</sup> N.A.A.                                           | 101 |

|------------------------------------------------------|---------------------------------------------------------------------------------|-----|

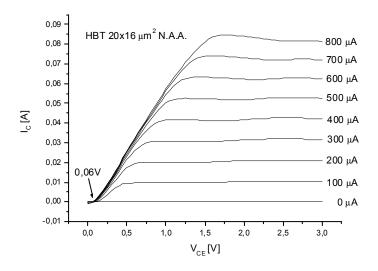

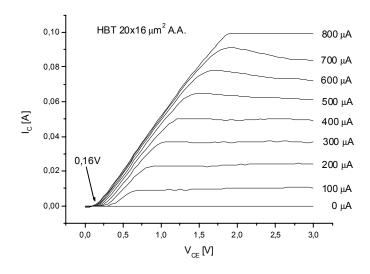

| Figura 5. 7 - Curva característica I <sub>C</sub> XV | $V_{\rm CE}$ para HBT 20x16 $\mu$ m <sup>2</sup> N.A.A.                         | 101 |

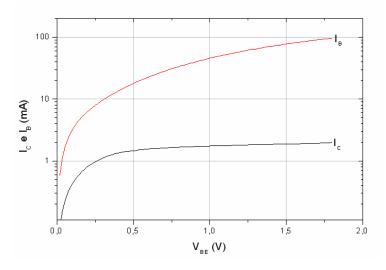

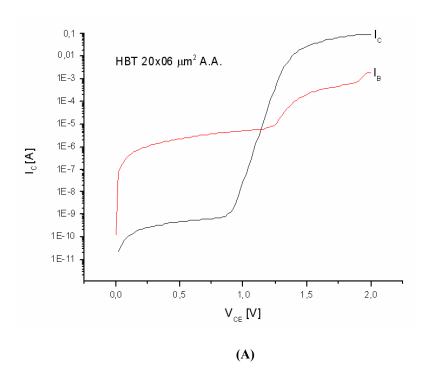

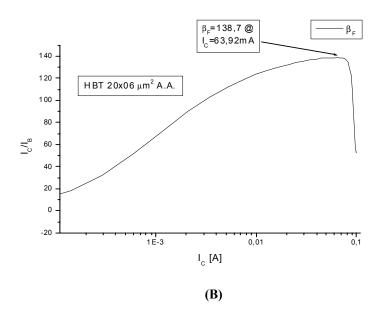

| Figura 5. 8 - Gummel-plot e ganho $\beta_F$          | para HBT $20x06 \mu m^2$ A.A.                                                   | 103 |

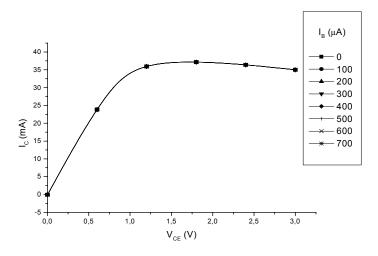

| Figura 5. 9 - Curva característica I <sub>C</sub> xV | $V_{\rm CE}$ para HBT 20x06 $\mu {\rm m}^2$ A.A.                                | 104 |

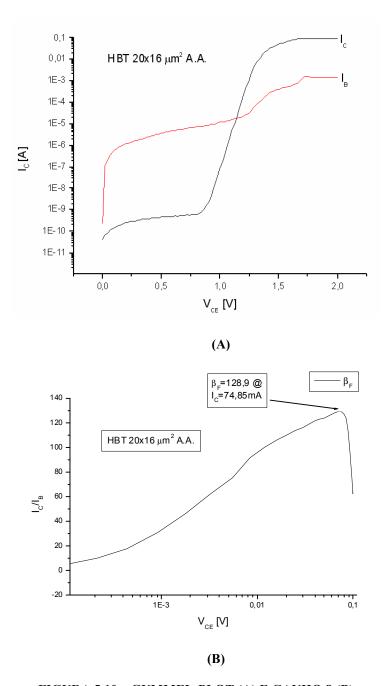

| Figura 5. 10 - Gummel-plot e ganho f                 | $_{\rm F}$ para HBT 20x16 $\mu {\rm m}^2$ A.A.                                  | 105 |

| Figura 5.11 - Curva característica I <sub>C</sub> x  |                                                                                 | 106 |

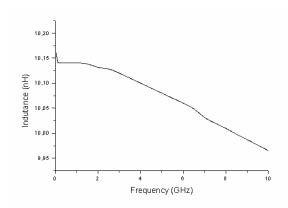

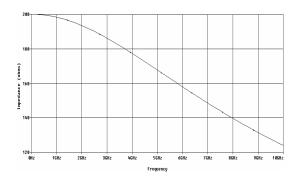

| Figura 5.12 - Medidas AC do resistor                 | de $260~\Omega$                                                                 | 107 |

| Figura 5.13 - Medidas AC do resistor                 | de $300~\Omega$                                                                 | 107 |

| Figura 5.14 - Medidas AC do resistor                 |                                                                                 | 108 |

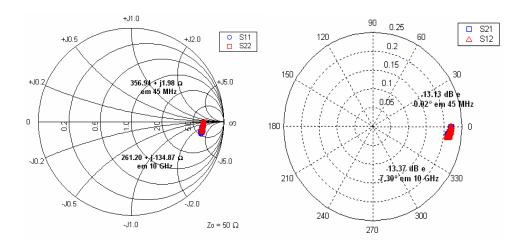

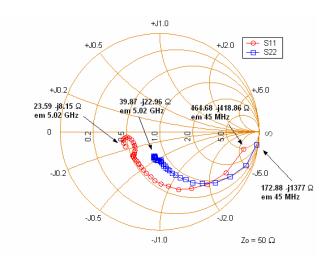

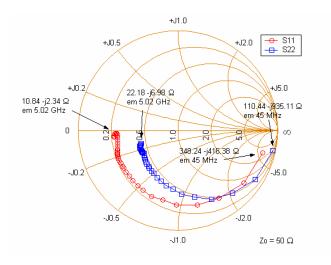

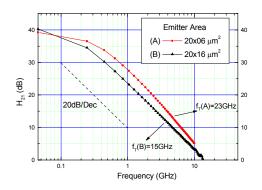

| Figura 5.15 - Módulo e fase de S <sub>12</sub> e S   | S <sub>21</sub> para HBT 20x06 μm <sup>2</sup> N.A.A.                           | 109 |

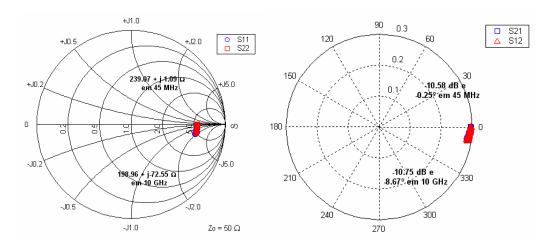

| Figura 5.16 - Reflexão na entrada (S <sub>1</sub>    | 1) e na saída (S <sub>22</sub> ) do HBT 20x06 μm <sup>2</sup> N.A.A.            | 109 |

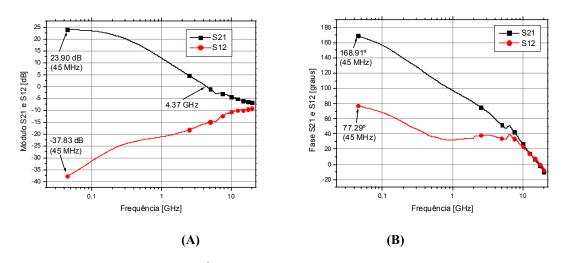

| Figura 5.17 - Módulo e fase de S <sub>12</sub> e S   | S <sub>21</sub> para HBT 20x16 μm <sup>2</sup> N.A.A.                           | 110 |

| Figura 5.18 - Reflexão na entrada (S <sub>1</sub>    | <sub>1</sub> ) e na saída (S <sub>22</sub> ) do HBT 20x16 μm <sup>2</sup> N.A.A | 111 |

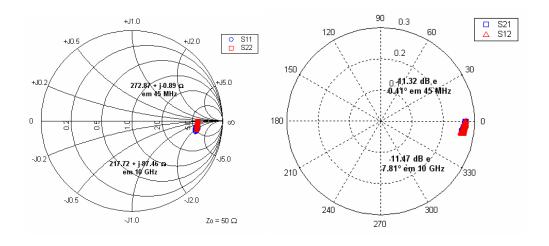

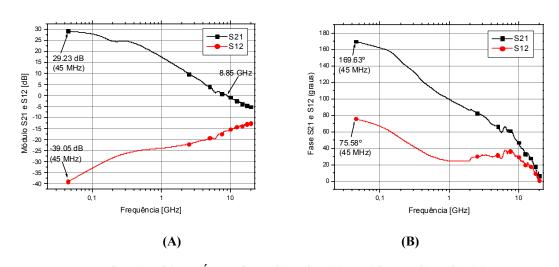

| Figura 5.19 - Módulo e fase de S <sub>12</sub> e S   | $S_{21}$ para HBT 20x06 $\mu$ m <sup>2</sup> A.A.                               | 112 |

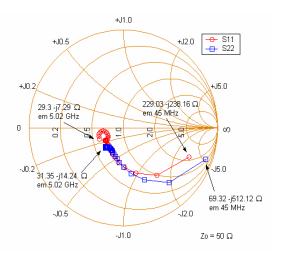

| Figura 5.20 - Reflexão na entrada (S <sub>1</sub>    | 1) e na saída (S <sub>22</sub> ) do HBT 20x06 μm <sup>2</sup> A.A.              | 113 |

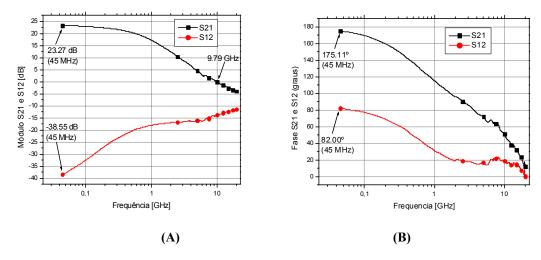

| Figura 5.21 - Módulo e fase de S <sub>12</sub> e S   | $S_{21}$ para HBT 20x16 $\mu$ m <sup>2</sup> A.A.                               | 113 |

| Figura 5.22 - Reflexão na entrada (S <sub>1</sub>    | 1) e na saída (S <sub>22</sub> ) do HBT 20x16 μm <sup>2</sup> A.A.              | 114 |

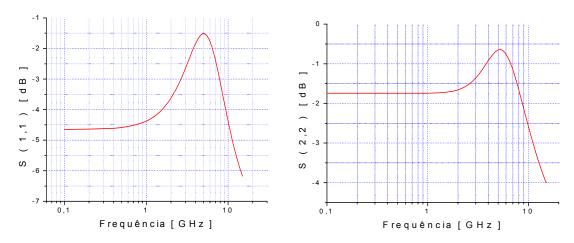

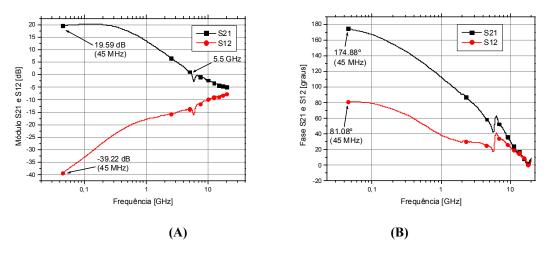

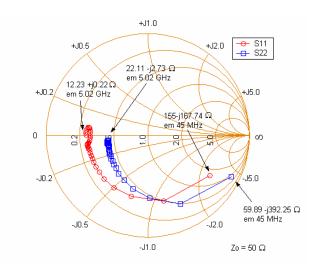

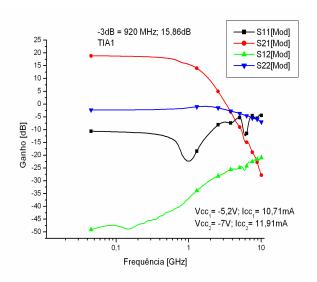

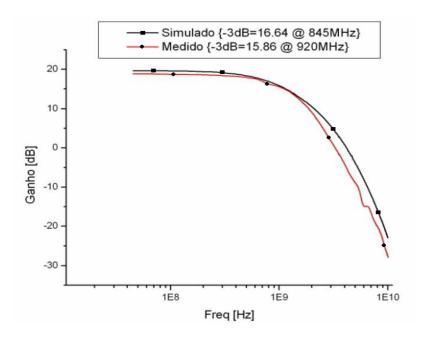

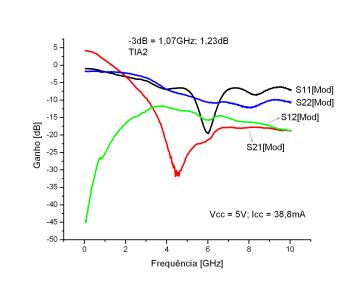

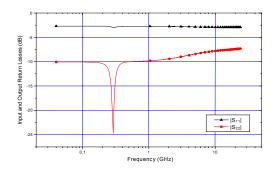

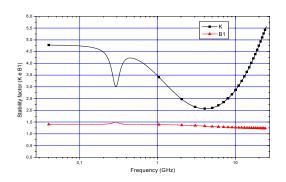

| Figura 5.23 - Ganho de potência e per                | das de retorno para circuito de transimpedância                                 | 116 |

| Figura 5.24 - Comparação entre o gar                 | nho e a banda do circuito medido e resimulado                                   | 118 |

| Figura 5.25 - Ganho de transimpedân                  | cia do circuito                                                                 | 119 |

| Figura 5.26 - Ganho de potência e per                | das de retorno para o circuito                                                  |     |

| de transimpedância utilizando p                      |                                                                                 | 119 |

| Figura 5.27 - Proposta para o novo cir               | cuito de transimpedância utilizando par Darlington                              | 120 |

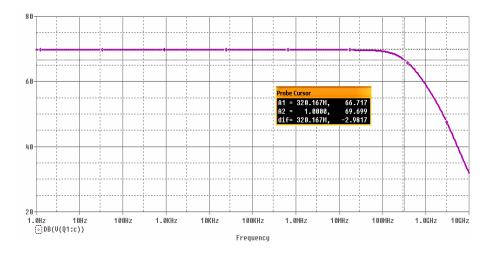

| Figura 5.28 - Resposta em frequência                 | para o circuito modificado                                                      | 120 |

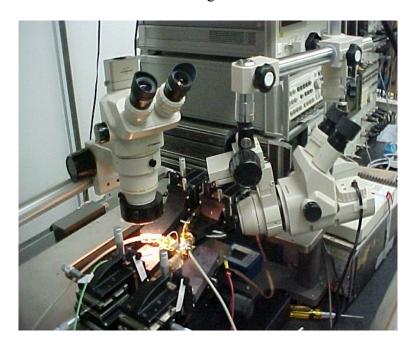

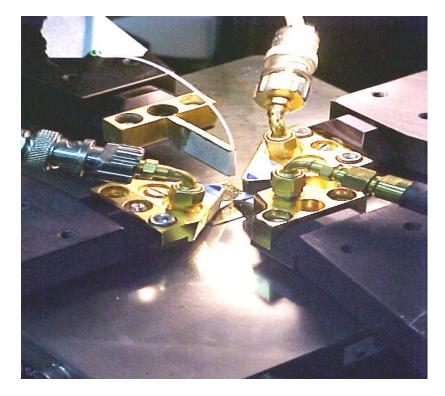

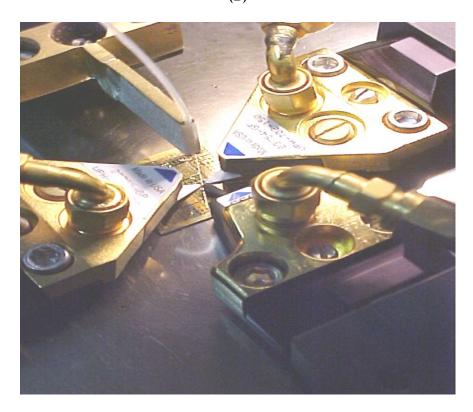

| Figura 5.29 - Montagem realizada par                 | ra medidas ópticas                                                              | 122 |

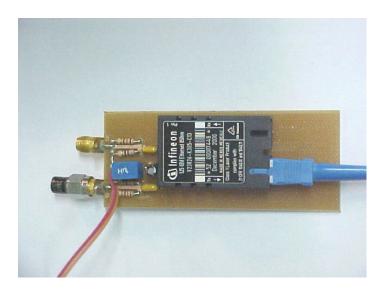

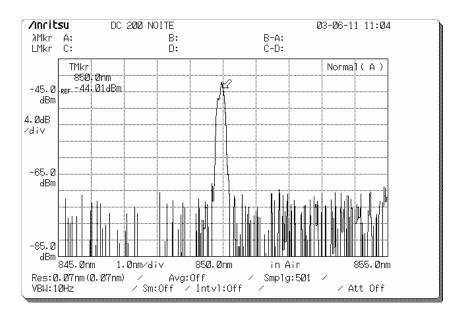

| Figura 5.30 - Fonte de luz em 850 nm                 | <u>.                                    </u>                                    | 123 |

| Figura 5.31 - Espectro de frequências                | da fonte de luz utilizada                                                       | 124 |

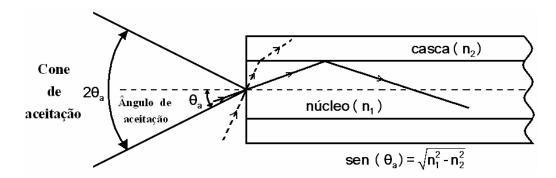

| Figura 5.32 - Abertura numérica de u                 | ma fibra óptica                                                                 | 124 |

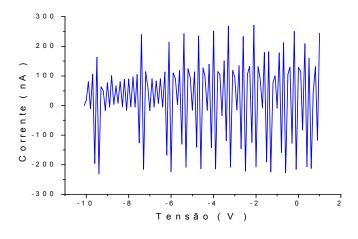

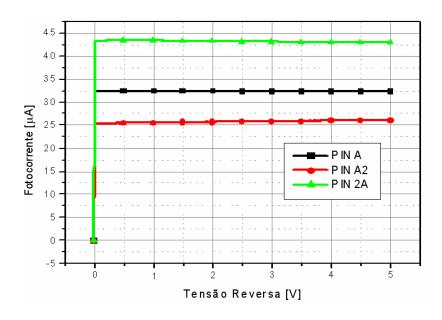

| Figura 5.33 - Fotocorrente gerada pel                | os detectores                                                                   | 125 |

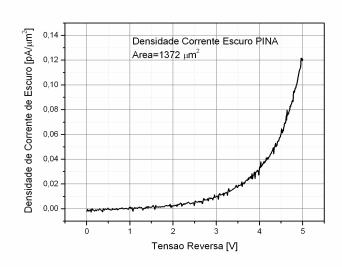

| Figura 5.34 - Densidade de corrente d                | e escuro para PINA                                                              | 126 |

| Figura 5.35 - Amplitude pico-pico da                 | onda quadrada na saída do gerador de                                            |     |

| sinais para 31 MHz, 350 MHz e                        | 1GHz                                                                            | 126 |

| Figura 5.36 - Resposta do circuito em                | relação ao pulso óptico na entrada para                                         |     |

| 31 MHz, 350 MHz e 1GHz                               |                                                                                 | 127 |

| Figura 5.37 - Amplitude do sinal eléti               | rico na saída do gerador e na saída do                                          |     |

| circuito de transimpedância                          |                                                                                 | 127 |

| Figura 5.38 - Diagrama de olho para s                | sinal NRZ em 1.8 Gbit/s                                                         | 128 |

## Índice de Tabelas

| Tabela 2.1 - Características de recombinação de portadores em materiais semicondutores      |     |

|---------------------------------------------------------------------------------------------|-----|

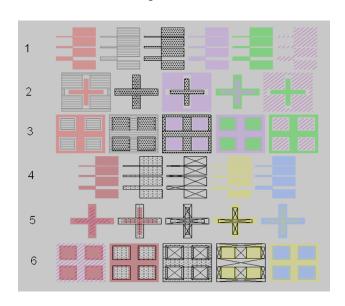

| Tabela 3.1 - Descrição das estapas de fotolitografia                                        | 43  |

| Tabela 3.2 - Parâmetros do transistor HBT utilizado nas simulações                          | 52  |

| Tabela 4.1 - Descrição das camadas epitaxiais do transistor HBT de InGaP/GaAs               | 63  |

| Tabela 4.2 - Metais que formam o contato de emissor                                         | 68  |

| Tabela 4.3 - Metais que formam o contato de base                                            | 75  |

| Tabela 4.4 - Metais que formam o contato de subcoletor                                      | 79  |

| Tabela 4.5 - Metais utilizados para interconexão dos dispositivos                           | 8   |

| Tabela 5.1 - Resumo das medidas DC dos resistores                                           | 90  |

| Tabela 5.2 - Medidas das estruturas TLM                                                     | 90  |

| Tabela 5.3 - Novos valores projetados para o resistor de $260 \Omega$                       | 9′  |

| Tabela 5.4 - Parâmetros DC do transistor HBT 20x06 μm <sup>2</sup> N.A.A.                   | 100 |

| Tabela 5.5 - Parâmetros DC do transistor HBT 20x16 μm <sup>2</sup> N.A.A.                   | 102 |

| Tabela 5.6 - Parâmetros DC do transistor HBT 20x06 μm <sup>2</sup> A.A.                     | 104 |

| Tabela 5.7 - Parâmetros DC do transistor HBT 20x16 μm <sup>2</sup> A.A.                     | 100 |

| Tabela 5.8 - Medidas AC de transistores N.A.A. realizadas em diversos pontos de polarização | 112 |

| Tabela 5.9 - Medidas AC de transistores A.A. realizadas em diversos pontos de polarização   | 11: |

| Tabela 5.10 - Parâmetros do modelo de pequenos sinais obtido                                | 117 |

## **CAPÍTULO 1**

## INTRODUÇÃO

#### 1.1 - HISTÓRICO

As comunicações ópticas surgiram na década de 60, com a realização prática do *laser* semicondutor e dos primeiros fotodiodos [1],[2]. Entretanto os meios de transmissão limitavam as comunicações de longas distâncias, dadas as elevadas perdas. O nível de impurezas presentes em fibras ópticas provocava perdas superiores a 20 dB/km, limite de viabilização do sistema na época. Desenvolvidas as técnicas de purificação de vidro na década de 70, surgem os primeiros sistemas de transmissão com fibras ópticas [3], operando com luz no comprimento de onda de 850 nm e atenuação em torno de 3 a 6 dB/km. A fibra óptica substitui então o par metálico e o cabo coaxial na transmissão de sinais, com inúmeras vantagens. Dentre elas [4]:

- Enorme banda passante e alta velocidade;

- Perdas extremamente baixas;

- Imunidade a interferências e ao ruído;

- Isolação elétrica;

- Baixíssimo peso, mesmo considerando-se o encapsulamento de proteção;

- Segurança da informação e do sistema;

- Flexibilidade na expansão da capacidade dos sistemas;

- Custos potencialmente baixos;

- Alta resistência a variações de temperatura.

A faixa em torno de 850 nm foi denominada  $I^a$  janela de transmissão, sendo as fontes de luz (lasers e LED's) fabricadas do material semicondutor arseneto de gálio (GaAs), fotodetectores PIN de silício e fibras do tipo multimodo. Foi utilizada em aplicações de curta distância, como por exemplo, no entroncamento de linhas telefônicas. Devido à simplicidade desta tecnologia e o baixo custo, ainda é utilizada em aplicações como redes locais (LAN's), interconexão de computadores e televisão a cabo.

A 2ª janela de transmissão surge logo após, no comprimento de onda de 1300 nm e fibras com perdas de 1 dB/km. O comprimento de onda de 1300 nm foi utilizado pois, associado às características de atenuação mínima, representa o ponto nulo de dispersão material através do guia de onda (fibra óptica), um dos fenômenos de limitação na capacidade de transmissão [5]. A tecnologia utilizada nas fontes de luz era de fosfeto de arsênio gálio e índio (InGaAsP), os fotodetectores eram do tipo PIN e APD e as fibras, do tipo monomodo. Apesar da tecnologia ser mais complexa e de maior custo, as perdas eram menores e a capacidade de transmissão de dados era maior (800 Mbps). Diminuía-se o número de repetidores e aumentava-se a distância entre os mesmos para algo em torno de 40 km.

Os esforços continuam no sentido de diminuir as perdas das fibras ópticas e no início dos anos 80, surgem as fibras com dispersão deslocada e perdas inferiores a 0,3 dB/km para 1550 nm, a 3ª janela de transmissão. Em 1550 nm têm-se a menor atenuação [5], outro fenômeno de limitação da capacidade de transmissão de sinais de luz através de uma fibra óptica, o qual define a distância máxima (alcance) entre um transmissor e um receptor óptico. Deslocando-se o ponto de dispersão mínima para este comprimento de onda, através de técnicas especiais de fabricação, obtém-se um desempenho maior. Surgem os sistemas de muito longo alcance (terrestres e submarinos), taxas de comunicação em GBit/s e maior distância entre os repetidores, utilizando-se o material Arseneto de Gálio e Índio (InGaAs) ou Fosfeto de Índio (InP). Progressos também são obtidos nas fontes de luz, com os diodos *lasers* de realimentação distribuída (DFB), que possuem menor largura espectral e maior potência.

Apesar de toda esta evolução, o desempenho é limitado pelos componentes eletrônicos utilizados no processamento dos sinais. Os receptores ópticos até então eram híbridos, ou seja, existia um estágio para a detecção da luz (fotodiodo) e outro para a préamplificação da fotocorrente gerada. A conexão entre ambos era feita por meio de fios ou microsoldas, gerando resistências, capacitâncias e indutâncias parasitárias indesejadas e consequentemente degradando o desempenho do receptor, além de aumentar seu custo. Para minimizar estes efeitos, os dois estágios deveriam ser construídos de forma monolítica, ou seja, no mesmo substrato semicondutor. Surgem os circuitos integrados optoeletrônicos (OEIC) [6]. Porém, devido aos problemas de crescimento de camadas epitaxiais com baixa densidade de defeitos, não foi possível a realização de tais circuitos na época com alto desempenho. Com o desenvolvimento de técnicas avançadas de crescimento, como MOCVD (Metalorganic Chemical Vapor Deposition), a partir da década de 90, os circuitos monolíticos superam os híbridos por possuírem maior funcionalidade, desempenho e menor custo. A possibilidade de integração dos receptores optoeletrônicos em conjunto com os lasers transmissores e posteriormente o desenvolvimento da fibra óptica amplificadora dopada a érbio (EDFA) [7] fazem surgir os sistemas multicanais, como o WDM (multiplexação por divisão em comprimento de onda) [8]. Esta técnica consiste em criar diversos canais em uma única fibra, com diferentes comprimentos de onda entre si e possibilitar também a transmissão nos dois sentidos. Deste modo, aproveita-se ainda mais a enorme banda passante das fibras ópticas.

O avanço nas telecomunicações foi muito grande, alcançando um mercado mundial de equipamentos e serviços em 2004 de 1.5 trilhões de dólares [9] e taxas de transmissão de 10 Tbit/s (256 canais de 42.7 GBit/s) [10]. Outras tecnologias estão sendo desenvolvidas, no sentido de diminuir a fração eletrônica da rede, por exemplo, as redes totalmente ópticas (ou redes fotônicas), incluindo chaves e amplificadores totalmente ópticos, aumentando-se ainda mais a capacidade de transmissão de informação.

#### 1.2 – OBJETIVO DA DISSERTAÇÃO

Este trabalho tem como objetivo utilizar a tecnologia de fabricação de transistores bipolares de heterojunção (HBT), desenvolvida pela Unicamp nos laboratórios de compostos III-V do Instituto de Física (LPD-IFGW) para projetar, fabricar e caracterizar um receptor optoeletrônico integrado (OEIC).

O comprimento de onda da luz utilizada é de 850 nm, ideal para redes de curta distância (LAN) e o material semicondutor utilizado na fabricação será o Arseneto de Gálio (GaAs), que possui maior mobilidade elétrica em relação ao silício, substrato semi-isolante, menor ruído em altas frequência, entre outras qualidades. Dentre as principais características dos transistores HBT, possuem alta transcondutância, alto ganho de corrente e elevada freguência de operação, sendo assim um ótimo candidato à fabricação do receptor. Transistores do tipo MESFET em GaAs ou HEMT (high electron mobility transistor) em AlGaAs/GaAs também podem ser usados para construir estes receptores [11],[12]. Porém, pelo fato da corrente elétrica fluir na horizontal por estes dispositivos, o tempo de transito será definido pela litografia do canal (distância entre dreno e fonte). Logo, a resolução litográfica do processo de fabricação utilizado deve ser alta. Transistores HBT são estruturas verticais, onde a corrente elétrica flui na vertical e o tempo de transito é definido pelas espessuras das camadas epitaxiais que compõe o dispositivo. Com isso, o processo de fabricação não necessita de resoluções mínimas tão pequenas quanto no caso dos dispositivos planares acima. Fotodetectores do tipo MSM (metal semicondutor metal), APD (avalanche photodiode) ou do tipo PIN são usados para fazer a detecção da luz e gerar um sinal de corrente elétrica a ser amplificado [13]. Os fotodetectores MSM são planares, constituídos de vários contatos interdigitados bem próximos uns dos outros. Necessitam de alta resolução litográfica para sua fabricação e apresentam moderadas correntes de fuga. Fotodetectores APD trabalham com tensões reversas de centenas de volts para provocar a avalanche na geração dos portadores elétricos, limitando sua utilização. Fotodetectores PIN são facilmente construídos, pois são formados das camadas de base, coletor e subcoletor dos transistores HBT, além de trabalharem com baixas tensões reversas. Por isto a combinação PIN+HBT será utilizada neste trabalho.

As diversas etapas para a obtenção do receptor optoeletrônico incluem a análise de modelos de projetos de componentes passivos (resistores, fotodetectores) e ativos (transistores), estudo de modelos elétricos dos mesmos, projeto e simulações do circuito, geração de um conjunto de máscaras litográficas e fabricação do receptor. Depois de fabricado, os dispositivos são medidos eletricamente (ac e dc) e um novo modelo elétrico é criado para representar os componentes do circuito. É feita então uma nova simulação do circuito para validação do projeto geral.

#### 1.3 – ORGANIZAÇÃO DA DISSERTAÇÃO

Este trabalho está divido em seis capítulos. O segundo capítulo apresenta teorias de geração de fotocorrente, o funcionamento de fotodetectores e de uma heterojunção, modelos elétricos de transistores bipolares e equações para projeto de resistores integrados. O terceiro capítulo descreve o projeto dos componentes discretos como resistores, fotodetectores e o circuito de transimpedância proposto. O *layout* destes componentes é feito e um conjunto de 11 máscaras litográficas é gerada para a etapa de fabricação em ambiente de salas limpas. Todas estas etapas de fabricação, dentre elas fotogravação, metalização, corrosão e limpeza são apresentadas no quarto capítulo. Depois de fabricado o circuito, medidas elétricas (dc, ac) e ópticas são realizadas. Modelos elétricos são gerados para os transistores HBT e resimulações do circuito proposto são feitas, mostradas no quinto capítulo. Por fim, no sexto capítulo as conclusões deste trabalho e algumas sugestões de melhoria são feitas.

Apêndices A e B incluem o arquivo de tecnologia utilizado para gerar o conjunto de máscaras litográficas e o artigo publicado no XVI congresso SBMicro – 2001 respectivamente.

## **CAPÍTULO 2**

# CIRCUITOS INTEGRADOS OPTOELETRÔNICOS (OEIC)

#### 2.1 - INTRODUÇÃO

Os circuitos integrados optoeletrônicos incluem em um mesmo bloco monolítico o fotodetector e o circuito eletrônico de processamento. Isto é possível devido às técnicas avançadas desenvolvidas para crescimento de camadas epitaxiais, dentre elas o MOCVD (*Metalorganic Chemical Vapor Deposition*). Com isso, as perdas na conversão optoeletrônica são pequenas, pois as indutâncias, capacitâncias e resistências parasitárias, que limitam a velocidade de operação dos circuitos híbridos, presentes na conexão entre o fotodetector e o circuito de amplificação, são minimizadas. Além disto, o consumo de energia é minimizado com a eliminação de circuitos de casamento de impedâncias entre os dois estágios. Conseqüentemente, aumenta-se a eficiência do dispositivo e reduz-se o custo de fabricação [14].

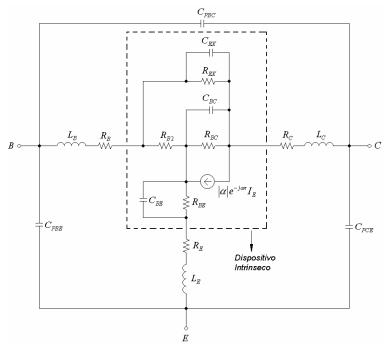

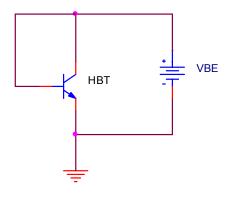

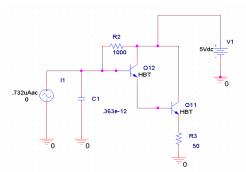

A figura 2.1 descreve o circuito optoeletrônico a ser integrado:

FIGURA 2.1 – ESQUEMA DO CIRCUITO OPTOELETRÔNICO A SER INTEGRADO

Nos circuitos optoeletrônicos integrados, os transistores HBT's podem ser utilizados [15]. Dentre suas principais características, possuem alta transcondutância e podem ser fabricados usando técnicas convencionais de fotolitografía. São compatíveis com os fotodiodos *PIN*, tornando a integração mais direta, simplificando os circuitos amplificadores, que serão mais confiáveis e de baixo consumo. OEIC's baseados na combinação *PIN*-HBT para aplicação em sistemas de comunicações ópticas operam a taxas de até 40 Gbit/s [16].

#### 2.2 - COMPONENTES QUE INTEGRAM UM OEIC

Os circuitos optoeletrônicos são constituídos de componentes passivos, como resistores, capacitores, indutores, fotodetectores e componentes ativos, como os transistores HBT, os quais serão apresentados a seguir.

#### **2.2.1 – FOTODIODO**

O fotodiodo é o dispositivo que faz a conversão óptica em elétrica. Ao ser excitado por luz em determinado comprimento de onda, gera o par elétron-lacuna. Devido ao intenso campo elétrico gerado pela tensão reversa na qual o dispositivo opera, estes portadores são coletados pelos terminais, gerando a fotocorrente. O princípio do mecanismo de fotogeração depende do material semicondutor e para a sua compreensão é necessária a análise da estrutura das bandas de energia permitidas para os elétrons [17], uma vez que os átomos destes materiais estão dispostos num arranjo de rede cristalina.

#### 2.2.1.1 – AS BANDAS DE ENERGIA

Em um semicondutor intrínseco, na temperatura de zero grau absoluto (0 °K), os átomos estão ligados entre si por ligações covalentes. Cada átomo consegue completar sua última camada eletrônica com os elétrons dos seus átomos vizinhos e todos os níveis de energia da banda de valência estarão preenchidos por elétrons. As demais bandas de energia estarão vazias. Estando os elétrons presos às ligações covalentes e estando estas totalmente ocupadas, não existe condução elétrica. Para esta temperatura, o material se comporta como isolante. Aumentando-se a temperatura, a disponibilidade de energia cinética faz com que alguns elétrons se libertem das ligações covalentes, ocupando estados de energia superiores, deixando vagos alguns estados na banda de valência. Define-se então a condutividade, que aumenta com a temperatura.

O diagrama básico das bandas de energia para um material semicondutor intrínseco é mostrado na figura 2.2. Acima da banda de valência existe um intervalo onde não são permi-.tidos estados de energia. Este intervalo é chamado de banda proibida (*band-gap*).

FIGURA 2.2 – BANDAS DE ENERGIA EM UM SEMICONDUTOR INTRÍNSECO (SEM IMPUREZAS)

O valor da largura da banda proibida para os principais materiais semicondutores utilizados é mostrado na tabela 2.1. Acima da banda proibida existe um contínuo de níveis permitidos de energia chamado de banda de condução. Na banda de condução os elétrons não estão presos a ligações covalentes, podendo se mover livremente pelos espaços da rede cristalina e serem acelerados por campos elétricos.

TABELA 2.1 - CARACTERÍSTICAS DE RECOMBINAÇÃO DE PORTADORES EM MATERIAIS SEMICONDUTORES

| Material | Tipo de<br>Recombinação | Largura da Banda<br>Proibida E <sub>g</sub> (eV) | Coeficiente de<br>Recombinação (cm3 . s <sup>-1</sup> ) |

|----------|-------------------------|--------------------------------------------------|---------------------------------------------------------|

| GaAs     | Direta                  | 1.43                                             | 7.21 x 10 <sup>-10</sup>                                |

| GaSb     |                         | 0.73                                             | 2.39 x 10 <sup>-10</sup>                                |

| InAs     |                         | 0.35                                             | 8.50 x 10 <sup>-11</sup>                                |

| InSb     |                         | 0.18                                             | 4.58 x 10 <sup>-11</sup>                                |

| Si       | Indireta                | 1.12                                             | 1.79 x 10 <sup>-15</sup>                                |

| Ge       |                         | 0.67                                             | 5.25 x 10 <sup>-14</sup>                                |

| GaP      |                         | 2.26                                             | 5.37 x 10 <sup>-14</sup>                                |

O parâmetro de rede típico numa estrutura cristalina semicondutora está em torno de meio nanômetro. Em camadas semicondutoras de espessura micrométrica existem, portanto milhares de átomos. Consequentemente, existem também milhares de níveis distintos de energia na banda de condução, fazendo com que esta se assemelhe a um contínuo.

Diversos mecanismos podem provocar a excitação de elétrons da banda de valência para a banda de condução. Os principais mecanismos são: a absorção de energia térmica, sempre presente em temperaturas não nulas, a absorção de fótons com energia maior que a largura da banda proibida, presente em fotodetectores e a injeção de elétrons, presente em fontes de luz. Ao deixar a banda de valência, o elétron deixa uma ligação covalente incompleta. Como essa ligação pode se mover pelos átomos da rede cristalina, ela constitui um portador virtual de carga positiva, denominada lacuna.

#### 2.2.1.2 - MECANISMOS DE FOTOGERAÇÃO

Quando perdem energia, os elétrons da banda de condução acabam retornando à banda de valência. Esse processo é chamado de recombinação, pois nele o elétron se "recombina" com uma lacuna, liberando energia. Essa energia pode ser liberada na forma de um fóton, logo a recombinação é um mecanismo de fotogeração. Este processo é mostrado na figura 2.3 e na realidade é o mecanismo básico da geração de luz nas fontes semicondutoras. Além disto, existente uma relação entre a freqüência da radiação emitida e a largura da banda proibida:

Recombinação: elétron + lacuna

$$\rightarrow$$

fóton (2.1) (espontânea)

FIGURA 2.3 – FOTOGERAÇÃO POR RECOMBINAÇÃO DIRETA, ONDE h É A CONSTANTE DE PLANCK, c É A VELOCIDADE DA LUZ, f E  $\lambda$  SÃO A FREQUÊNCIA E O COMPRIMENTO DE ONDA DA RADIAÇÃO EMITIDA RESPECTIVAMENTE. hf É A ENERGIA DO FÓTON.

Além de conservar a energia, a recombinação deve também conservar momento linear k. Como o momento do fóton é muito pequeno quando comparado com o momento dos elétrons e lacunas, isto significa que elétrons e lacunas devem ter momentos semelhantes para se recombinarem radiativamente, ou seja, com a emissão de um fóton. Se isso não acontecer, a recombinação exigirá a presença de uma terceira partícula capaz de ceder momento, denominada fonon. Fonons são vibrações quantizadas da rede cristalina. Como a necessidade de fonons torna a recombinação menos provável, o processo de geração de luz é mais eficiente quando se utiliza materiais onde eles não são necessários. Esses materiais são conhecidos como materiais de recombinação direta, ou banda proibida direta. A tabela 2.1 lista alguns materiais de banda direta e banda indireta.

A necessidade de recombinação direta em fontes de luz semicondutoras impede o uso do germânio e do silício. Materiais compostos são utilizados, como o arseneto de gálio (GaAs), o arseneto de gálio-alumínio (Ga<sub>x</sub>Al<sub>1-x</sub>As), o arseneto-fosfeto de gálio-índio (In<sub>x</sub>Ga<sub>1-x</sub>As<sub>y</sub>P<sub>1-y</sub>) e outros, nos quais a recombinação é direta. Estes materiais devem possuir poucos defeitos na estrutura cristalina, evitando assim um grande número de recombinações não-radiativas nestes locais, prejudicando a eficiência da fonte. Recombinações não-radiativas produzem calor, o que pode provocar degeneração dos defeitos, acentuando a perda de eficiência.

Além de ocorrer espontaneamente, conforme descrito na equação (2.1), a recombinação também pode ser estimulada pela presença de um fóton:

Recombinação: 1 elétron + 1 lacuna + 1 fóton

$$\rightarrow$$

2 fótons (2.2) (estimulada)

Para a recombinação estimulada, o novo fóton gerado é geralmente emitido com a mesma fase do fóton que a estimulou. Por isso, o predomínio da recombinação estimulada sobre a espontânea, que ocorre nos diodos *lasers*, está associado à produção de uma luz mais coerente. A recombinação estimulada produz ganho óptico, podendo ser utilizado em amplificadores ópticos e osciladores (*lasers*).

Os fótons gerados por recombinações podem ser reabsorvidos pelo material.

Deste modo, para que uma fonte seja eficiente na produção de luz, é necessário engendrar estruturas semicondutoras que produzam um grande número de recombinações concentradas em espaços limitados, o qual guiem de alguma forma os fótons resultantes para o exterior do dispositivo antes de sua perda por absorção. Essas estruturas são necessariamente heterogêneas, envolvendo diferenciais de dopagem (especialmente em junções pn) e materiais diferentes, crescidos epitaxialmente uns sobre os outros (heteroestruturas), para provocarem diferenciais nos níveis da banda proibida e dos índices de refração.

#### 2.2.1.3 - FOTODETECTORES

Para que um sistema de comunicação óptica tenha o maior alcance possível, é necessário que o fotodetector possa operar com sucesso nos menores níveis possíveis de potência óptica, convertendo-a em corrente com o mínimo de distorção e ruído. Seu desempenho deve ser medido em termos da resposta dinâmica e da geração de ruído.

A fotoionização é o mecanismo básico da conversão de luz em corrente elétrica pelo material semicondutor, pela qual a energia do fóton é usada para tirar o elétron da banda de valência, levando-o à banda de condução:

Fotoionização:

$$fóton + átomo \rightarrow elétron + lacuna$$

, (2.3)

O processo é mostrado na figura 2.4:

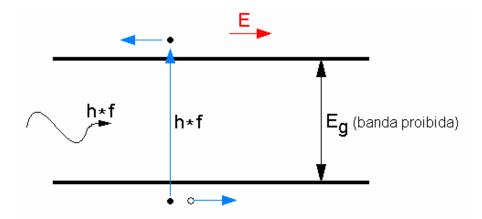

FIGURA 2.4 – GERAÇÃO DE PARES ELÉTRON-LACUNA POR FOTOIONIZAÇÃO, ONDE  $\boldsymbol{E}$  É UM CAMPO ELÉTRICO

No processo de fotoionização, os fótons geram portadores de carga. Para gerar corrente elétrica a partir deste momento, é necessária a presença de um campo elétrico para movimentar estes portadores antes que eles se recombinem no interior do dispositivo. Por isso, a estrutura semicondutora de um fotodetector deve concentrar a absorção de luz em regiões onde haja campo elétrico e poucos portadores com os quais os elétrons e lacunas geradas possam se recombinar.

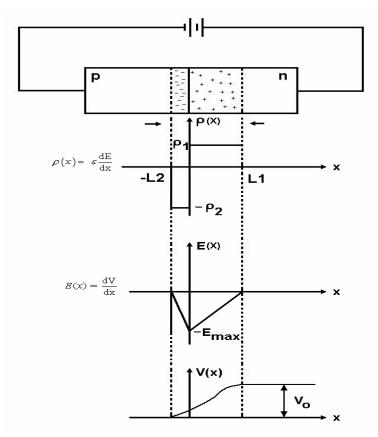

A junção *pn* polarizada reversamente constitui a estrutura básica de um fotodetector. A polarização reversa aumenta a barreira de potencial associada à junção *pn*, através do alargamento da região de depleção. A aplicação de tensão positiva no lado n em relação ao lado p atrai os elétrons do lado n e as lacunas do lado p (portadores majoritários) para longe da junção, alargando a região de depleção até que a barreira de potencial iguale à tensão aplicada, salvo pequenas quedas ôhmicas associadas à corrente de fuga e fotocorrente. A figura 2.5 ilustra as distribuições de carga resultantes (associada aos átomos de impurezas dopantes), campo elétrico e potencial elétrico na direção transversal à junção *pn* reversamente polarizada.

FIGURA 2.5 – DISTRIBUIÇÃO DE CARGA, CAMPO ELÉTRICO E POTENCIAL EM UMA JUNÇÃO PN REVERSAMENTE POLARIZADA: L1 E L2 DEFINEM OS LIMITES DA REGIÃO DE DEPLEÇÃO,  $\rho_1$  E  $\rho_2$  REPRESENTAM AS CONCENTRAÇÕES DE CARGAS, E E V SÃO O CAMPO ELÉTRICO E O POTENCIAL AO LONGO DA JUNÇÃO RESPECTIVAMENTE

Os elétrons e as lacunas geradas dentro da região de depleção são rapidamente separados, acelerados em sentidos opostos pelo campo elétrico da região de depleção e coletados, contribuindo assim para a fotocorrente. Os portadores gerados na região macroscópica (longe da região de depleção) não são acelerados e acabam se recombinado, na sua maioria, antes de chegarem por difusão à região onde existe campo elétrico, os quais poderiam ser coletados (dependendo da paridade da carga).

Os portadores gerados nas proximidades da região de depleção, até um comprimento médio de difusão, contribuem para a fotocorrente em sua maioria, porém com atraso em relação à sua geração. Esse tipo de fotoionização é inconveniente, pois degrada a resposta dinâmica do dispositivo.

Para que o dispositivo tenha alto rendimento e boa resposta dinâmica, é necessário que a luz seja absorvida apenas na região de depleção. Para isso, é necessário que a largura da região de depleção seja maior que  $\alpha^{-1}$  [18], onde  $\alpha$  é o coeficiente de absorção do material semicondutor. Se o silício é usado para absorver uma emissão *laser* de GaAs ( $\hbar\omega \approx 1.45 \text{ eV}$ ), o material deve ter espessura de 10-20  $\mu$ m. Por outro lado, um detector de Ge ou GaAs necessitaria apenas um comprimento de interação de apenas 1 $\mu$ m.

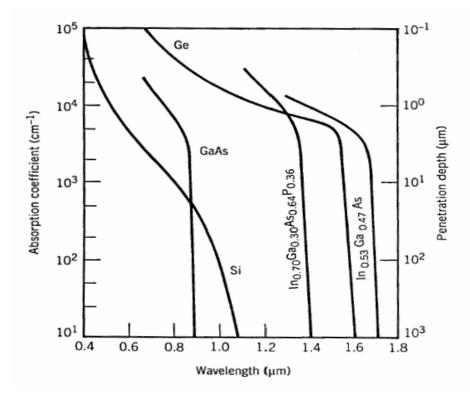

A figura 2.6 mostra a variação de α com a energia dos fótons incidentes para vários materiais empregados em fotodetectores.

FIGURA 2.6 [19] – COEFICIENTE DE ABSORÇÃO DA LUZ PARA DIVERSOS MATERIAIS, EM FUNÇÃO DA ENERGIA DOS FÓTONS INCIDENTES. OBSERVA-SE A EXISTÊNCIA DE ENERGIAS DE CORTE PARA A ABSORÇÃO DE LUZ, A PARTIR DOS QUAIS O MATERIAL TORNA-SE TRANSPARENTE. POR EXEMPLO, PARA GaAS SE O FÓTON TEM COMPRIMENTO DE ONDA MAIOR QUE 0,86µm, NÃO HAVERÁ GERAÇÃO DE FOTOCORRENTE.

Da figura 2.5, nota-se que o alargamento da região de depleção não exige tensões de polarização reversa altas. Se a estrutura do dispositivo impuser o desequilíbrio entre os níveis de dopagem nos lados p e n da junção, a região de depleção tende a um aumento proporcionalmente maior para o lado menos dopado.

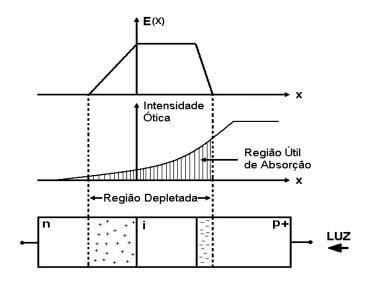

No limite, se a estrutura do fotodetector possuir entre os lados p e n, material não dopado (intrínseco), a região de depleção ocupará toda a camada intrínseca, onde o campo elétrico será constante, qualquer que seja a tensão reversa aplicada. Essa situação, mostrada na figura 2.7, representa idealmente o funcionamento do fotodiodo *pin* (p-intrínseco-n).

FIGURA 2.7 – ESTRUTURA IDEALIZADA DO FOTODIODO PIN

Como podemos observar através da figura 2.6, cada curva apresenta um comprimento de onda de corte do material semicondutor em questão, acima do qual não há geração de portadores de carga. Isso reflete simplesmente o fato dos fótons precisarem ter energia pelo menos equivalente à largura da banda proibida ( $E_{\rm g}$ ) do material, para viabilizar o salto energético dos elétrons entre as duas bandas permitidas:

$$\frac{hc}{\lambda} \rangle Eg$$

$$\therefore \lambda \langle \lambda_{cm} = \frac{hc}{Eg} = \left(\frac{1,24}{E_g (eV)}\right) \quad [\mu \text{m}]$$

(2.4)

onde  $\lambda_{cm}$  é o comprimento de onda de corte do material, h é a constante de Planck e c é a velocidade da luz. Para o arseneto de gálio, este comprimento de onda de corte está em torno de  $\lambda_{C}=0.867~\mu m$ . Na primeira janela de transmissão (800-900nm), o material comumente utilizado é o silício, que apresenta corte em 1060nm. Sua utilização é inviável nas janelas superiores, cujos comprimentos de onda se situam em torno de 1300nm (segunda janela) e 1550nm (terceira janela). Nessas janelas, os materiais disponíveis são o germânio e materiais compostos como o InGaAs.

#### **2.2.1.4 - FOTODIODO** *PIN*

A estrutura ideal de um fotodiodo *PIN* é ilustrada na figura 2.7. O uso de material intrínseco garante o alargamento da região de depleção por toda a sua extensão, mesmo com tensões de polarização reversa modestas, assegurando assim a absorção total ou quase total, da luz na região de depleção. Na prática, o uso de material puramente intrínseco não é possível nem necessário, pelos seguintes motivos:

- a) a presença de impurezas residuais dificulta a obtenção do material intrínseco;

- b) se a região intrínseca for larga demais, a velocidade do dispositivo começa a ficar prejudicada, pelo tempo de trânsito dos fotoportadores através da região de depleção, que naturalmente é proporcional à sua largura.

É aceitável que a camada intrínseca seja ocupada por material levemente dopado. No caso de fotodiodos de silício, faixas de 1GHz necessitam de larguras da região de depleção inferiores a 20µm. Como na faixa óptica de operação desses fotodiodos o coeficiente de absorção é da ordem de 10<sup>3</sup> cm<sup>-1</sup>, uma porção significativa da luz será absorvida fora da região de depleção, sem contribuir para a fotocorrente. Por isso, a eficiência quântica (relação entre a quantidade de pares elétrons-lacunas gerados e a quantidade de fótons incidentes) pode ficar abaixo de 80%.

Uma vez conhecido o coeficiente de absorção do semicondutor a ser usado, é necessário saber a taxa ao qual os pares elétrons-lacunas serão gerados. Para calcular a taxa da geração do par, considere um feixe óptico com intensidade  $P_{op}(0)$  incidindo sobre um semicondutor por unidade de área. A intensidade em um ponto x ( $0 \le x \le W$ , onde W é a largura da região de depleção), é dada por (intensidade  $[W/cm^2]$ ):

$$P_{op}(x) = P_{op}(0) \exp(-\alpha x)$$

(2.5)

A energia absorvida por segundo por unidade de área em uma região infinitesimal de espessura dx, entre os pontos dx e x+dx é:

$$P_{op}(x+dx) - P_{op}(x) = P_{op}(0)[\exp(-\alpha(x+dx)) - \exp(-\alpha x)]$$

=  $P_{op}(0)[\exp(-\alpha x)]\alpha dx$  (2.6)

Se a energia absorvida produz pares elétron-lacuna, a taxa de geração de portadores é  $G_L$  (taxa por unidade de volume):

$$G_{L} = \frac{\alpha P_{op}(x)}{\hbar \omega} = \alpha \Phi_{ph}(x)$$

(2.7)

onde  $\Phi_{ph}$  é a densidade de fluxo de fótons incidindo em um ponto x (fluxo tem unidades de cm<sup>-2</sup>s<sup>-1</sup>).

Quando a luz incide sobre o semicondutor e gera pares elétron-lacuna, o desempenho do detector depende da coleta destes portadores e portanto na mudança da condutividade do material. Na ausência de campo elétrico ou gradiente de concentração, os pares elétron-lacuna recombinam-se e não geram um sinal detectável. Uma propriedade importante do detector é dada pela sua responsividade, o qual fornece a corrente produzida por uma certa potência óptica. A responsividade R<sub>ph</sub> é definida por:

$$R_{ph} = \frac{I_L / A}{P_{op}} = \frac{J_L}{P_{op}}$$

(2.8)

onde  $I_L$  é a fotocorrente produzida em um dispositivo de área A e  $J_L$  é a densidade de fotocorrente. A eficiência quântica do detector é definida como:

$$\eta_{Q} = \frac{J_{L}/e}{P_{op}/\hbar\omega} = R_{ph} \frac{\hbar\omega}{e}$$

(2.9)

A eficiência quântica essencialmente nos diz quantos portadores são coletados para cada fóton incidindo no detector.

A responsividade de um detector tem uma dependência forte com o comprimento de onda dos fótons incidentes. Se o comprimento de onda está acima do comprimento de corte, os fótons não serão absorvidos e não será gerada fotocorrente. Quando o comprimento de onda é menor que  $\lambda_C$ , a energia do fóton será maior do que a energia de *bandgap* e a diferença será liberada em forma de calor. Com isto a responsividade começa a diminuir.

O fotodiodo pin explora o potencial interno (built-in) presente na junção juntamente com a polarização reversa aplicada para coletar os elétrons e as lacunas. Uma vez que o dispositivo está reversamente polarizado, a sua corrente de escuro é idealmente  $I_0$  e é independente da polarização aplicada. A fotocorrente  $I_L$  é devida essencialmente aos portadores gerados na região de depleção (região intrínseca) que são coletados. A região intrínseca estará inteiramente depletada e terá um forte campo elétrico.

A corrente máxima que pode ser coletada é (desprezando o processo de difusão):

$$I_L = eA \int_0^W G_L(x) dx$$

(2.10)

A taxa de geração descrita acima em um ponto x será dada por:

$$G_L = \alpha \Phi_{ph}(0) \exp(-\alpha x)$$

(2.11)

onde  $\Phi_{ph}(0)$  é o fluxo de fótons (número por cm² por segundo) em x = 0. A fotocorrente será então das equações (2.10) e (2.11):

$$I_L = eA\Phi_{ph}(0)[1 - exp(-\alpha W)]$$

(2.12)

Se R é a refletividade da superfície, a fração de fótons que realmente penetram o dispositivo é (1- R), então a fotocorrente será:

$$I_L = eA\Phi_{ph}(0)(1-R)[1-exp(-\alpha W)]$$

(2.13)

Uma medida da eficiência do detector é a razão da densidade de fotocorrente pelo fluxo incidente:

$$\eta_{\text{det}} = \frac{I_{\text{L}}}{A\Phi_{vh}(0)e} = (1-R)[1-\exp(-\alpha W)]$$

(2.14)

Para uma eficiência alta devemos ter um valor de R pequeno (usando camadas antirefletivas) e um W grande. Entretanto, se W é muito grande o tempo de trânsito que controla o dispositivo torna-se também grande, reduzindo a sua velocidade. Dispositivos de alta velocidade têm W em torno de 1 μm ou menos e podem operar a velocidades de 10 GHz ou mais.

#### 2.2.1.5 - CORRENTE DE ESCURO

Sendo causada pela energia térmica, a corrente de escuro tende a ser maior nos materiais em que a banda proibida é mais estreita. Fatores estruturais da rede cristalina também podem ser determinantes. Entre os materiais comumente utilizados, o silício tem a menor corrente de escuro: cerca de 10<sup>-7</sup> A/cm<sup>2</sup>. A área transversal do fotodetector deve ser a da fibra, que é de cerca de 10<sup>-6</sup> cm<sup>2</sup> no caso monomodo. Portanto, é possível fazer fotodiodos de silício com correntes de escuro da ordem de 0,1 pA. No caso do arseneto de gálio, esta corrente de escuro é da ordem de algumas dezenas de nanoampéres. Por isso, os sistemas da primeira janela são apenas marginalmente degradados pela corrente de escuro.

Nos comprimentos de onda superiores, é necessário usar materiais com banda proibida mais estreita, como o germânio e o InGaAs. O germânio apresenta corrente de escuro de  $10^{-3}~{\rm A/cm^2}$ , resultando em correntes de cerca de 1 nA sem luz sobre o fotodetector; esses níveis podem resultar em uma degradação sensível de desempenho. A corrente de escuro do InGaAs depende dos teores relativos do índio e do gálio, mas se situa em torno de  $10^{-5}~{\rm A/cm^2}$ , sendo este um dos motivos da superioridade do seu desempenho sobre o germânio.

# 2.2.1.6 – ESCOLHA DO MATERIAL E RESPOSTA EM FREQUÊNCIA DE UM FOTODETECTOR *PIN*

A questão mais importante no projeto de um fotodetector é trabalhar com um material que possua um coeficiente de absorção adequado para as freqüências a serem detectadas.

Para comunicações onde fontes de GaAs/AlGaAs são usadas (tipicamente usadas em redes locais LAN), fotodetectores de silício são usados, a menos que velocidades altas são desejadas. Para comprimentos de ondas maiores, fotodetectores de germânio e outros materiais podem ser usados. Um comprimento de onda importante é de 1.55 μm, usado para comunicações de longa distância onde a perda por propagação na fibra é mínima.

Uma vez escolhido o material, os pontos importantes no desenvolvimento do dispositivo são:

- 1. Minimização da reflexão na superfície: isto é feito geralmente aplicando camadas anti-refletivas as quais podem reduzir as perdas por reflexão de 40% para 2-3%;

- 2. Maximização da absorção na região de depleção: para detectores com alta eficiência, devemos ter grande absorção através da largura da região de depleção, como visto na equação (2.14). Entretanto, para a velocidade de operação, nem sempre aumentar a largura da região de depleção é aconselhável. Geralmente, espelhos podem ser usados para aumentar o comprimento de interação óptica do dispositivo fazendo com que um feixe de luz tenha maior probabilidade de ser absorvido;

- 3. Minimização da recombinação dos portadores: para aumentar a eficiência é necessário minimizar a recombinação de portadores na região de depleção. Isto requer o uso de materiais de alta pureza;

- 4. Minimização do tempo de trânsito: para o propósito de altas velocidades, o tempo de trânsito deve ser minimizado, o que significa que a região de depleção deve ser tão pequena quanto possível.

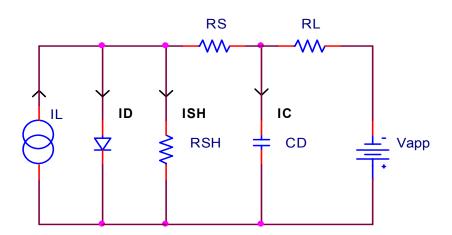

Em conjunto com estes critérios, a resposta do dispositivo é controlada pelo circuito equivalente do fotodiodo, mostrado na figura 2.8:

FIGURA 2.8 – CIRCUITO EQUIVALENTE DO FOTODIODO PIN. O DISPOSITIVO PODE SER REPRESENTADO POR UMA FONTE DE CORRENTE  $I_L$  ALIMENTANDO UM DIODO. AS CARACTERISTICAS INTERNAS DO DISPOSITIVO SÃO REPRESENTADAS POR UM RESISTOR SHUNT  $R_{sh}$  E UM CAPACITOR  $C_D$ .  $R_S$  É A RESISTÊNCIA SÉRIE DO DIODO [18]

Assume-se que a saída do fotodiodo é conectada a um amplificador. A capacitância do fotodiodo  $C_D$  é, para a polarização reversa:

$$C_D = \frac{\varepsilon A}{W}$$

(2.15)

A variável W representa a largura da região de depleção. O diodo tem uma resistência série R<sub>S</sub> e condutância G<sub>D</sub>. Para resposta em altas freqüências a capacitância e a resistência devem ser minimizadas, o qual significa reduzir a área A, sendo que se W é aumentado muito, o dispositivo é limitado por efeitos de tempo de trânsito. Se a capacitância e a resistência são otimizadas, o tempo de trânsito limita a resposta. Portanto existe um compromisso. O tempo de trânsito é controlado pela largura da região de depleção e a velocidade de saturação, que é dada por:

$$t_{tr} = \frac{\mathbf{W}}{\mathbf{v}_{S}} \tag{2.16}$$

Portanto, altas frequências requerem larguras da região de depleção pequenas.

A frequência de corte do fotodetector é dada por:

$$f_{-3dB} = \frac{1}{2\pi R_{\rm L} C_d}$$

(2.17)

onde R<sub>L</sub> e C<sub>d</sub> equivalem ao circuito equivalente da figura 2.8.

Se uma certa potência óptica incide sobre o fotodiodo, pode-se calcular a fotocorrente gerada:

$$\Phi_{ph} = \frac{P_{op}}{\hbar \omega}$$

(2.18)

onde  $\Phi_{ph}$  é o fluxo de fótons incidentes e  $P_{op}$  é a densidade de potência óptica.

Com isso, como na equação 2.13, a densidade de fotocorrente  $J_L$  é dada por:

$$J_L = e \Phi_{ph}(1-R) \{1-\exp(-\alpha w)\}$$

(2.19)

#### 2.2.2 – TRANSISTORES BIPOLARES DE HETEROJUNÇÃO (HBT)

Os transistores bipolares são preferidos em aplicações de alta frequência devido ao alto valor da frequência de transição  $(f_T)$  e da transcondutância  $(g_m)$ . Comparado aos transistores de efeito de campo, os bipolares conseguem manter valores altos de  $f_T$  e  $g_m$  para grandes dimensões laterais. Dispositivos grandes possuem melhor casamento no processo de fabricação, o qual é importante para o projeto de circuitos de RF. Os transistores BJT (Transistores Bipolares de Homojunção) são construídos a partir de um único material semicondutor, como o Silício. Possuem limitações que não permitem dispositivos com ganhos suficientemente elevados e baixos valores de resistência de base, o qual compromete a operação em altas frequências.

O transistor HBT foi proposto por *W. Shockley* [20] e aprimorado por H. Kroemer [57], na década de 50. A idéia era utilizar intencionalmente dois materiais semicondutores diferentes para a fabricação: um material com uma banda proibida maior no emissor e outro com banda proibida menor para a base. Porém as limitações no processo de fabricação na época não permitiam a construção do HBT, como por exemplo, o crescimento de camadas epitaxiais com poucos defeitos na estrutura cristalina.

#### 2.2.2.1 – PRINCÍPIO DE FUNCIONAMENTO DO TRANSISTOR HBT

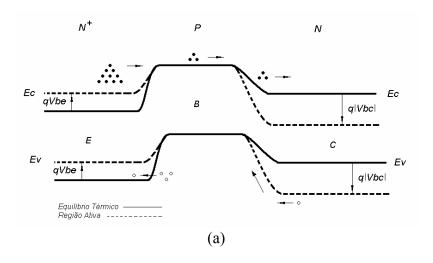

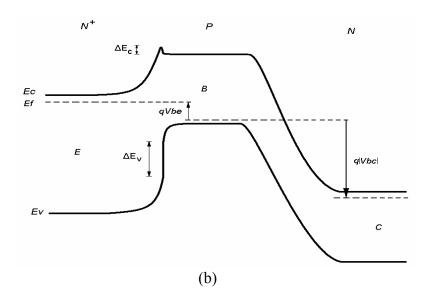

A técnica de variar a largura de banda proibida através do dispositivo faz com que elétrons e lacunas sofram forças elétricas diferentes: a heterojunção cria uma descontinuidade na banda de valência, ou seja, uma barreira de potencial que impede a injeção de cargas majoritárias da base (lacunas) para o emissor. Para um transistor HBT possuir máxima eficiência de injeção de cargas (pouca recombinação de lacunas da base para o emissor e portanto maior ganho de corrente), a altura desta descontinuidade deve ser a maior possível na banda de valência e mínima possível na banda de condução (facilitar a movimentação dos elétrons do emissor para o coletor). A figura 2.9 mostra o diagrama de bandas para um transistor BJT e para um HBT.

FIGURA 2.9 – DIAGRAMA DE BANDAS PARA UM BJT EM EQUILÍBRIO TERMODINÂMICO E POLARIZADO NA REGIÃO ATIVA (A) E PARA UM HBT NA REGIÃO ATIVA (B)

#### 2.2.2.2 – FIGURAS DE MÉRITO DA HETEROJUNÇÃO

Como podemos ver, o valor de  $E_g$  varia ao longo do dispositivo. A barreira de potencial  $\Delta E_V$  possibilita uma maior dopagem da região de base, diminuindo-se o valor da resistência intrínseca. O uso de um material com  $E_g$  maior na região de emissor também possibilita menor dopagem da região, diminuindo-se a capacitância de depleção. Estes fatores contribuem para a operação em altas frequências. As principais vantagens do HBT sobre o BJT são:

- 1. Maior eficiência de injeção do emissor devido à maior barreira de potencial para lacunas na banda de valência;

- 2. Menor resistência de base, por ser altamente dopada, sem degradar a eficiência de injeção de elétrons;

- 3. Menor efeito da corrente de *crowding* (queda de tensão causada pela corrente que atravessa a resistência de base tende a reduzir V<sub>BE</sub>', que é o V<sub>BE</sub> do transistor intrínseco, reduzindo a corrente de emissor até sua completa aniquilação);

- 4. Melhor resposta em frequência devido ao maior ganho de corrente e menor resistência de base;

- 5. Maior faixa de temperatura de operação, devido ao maior Eg.

A heterojunção InGaP/GaAs, utilizada neste estudo possui as características necessárias para a fabricação de circuitos optoeletrônicos [21].

O material possui uma grande descontinuidade na banda de valência (0,30 eV) com o GaAs, baixa recombinação superficial, alto valor de  $E_g$  na temperatura ambiente (1.87 eV) e alta seletividade de taxa de corrosão de região de emissor sobre a região de base [22].

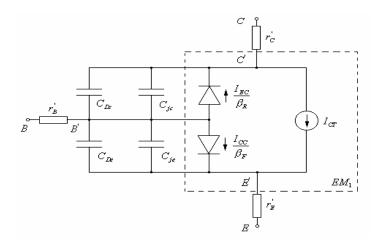

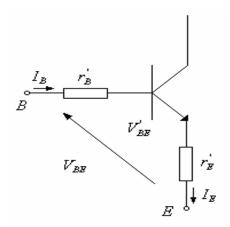

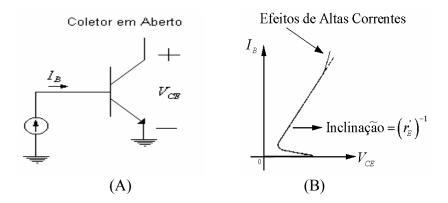

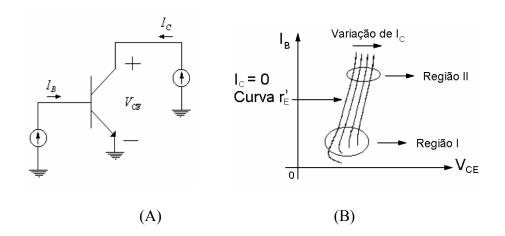

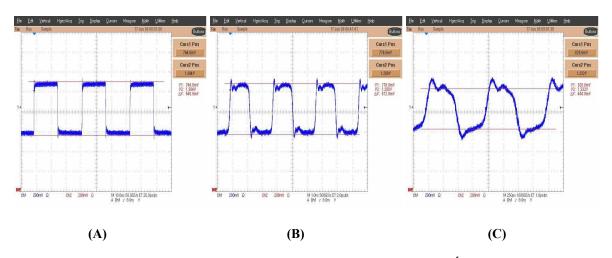

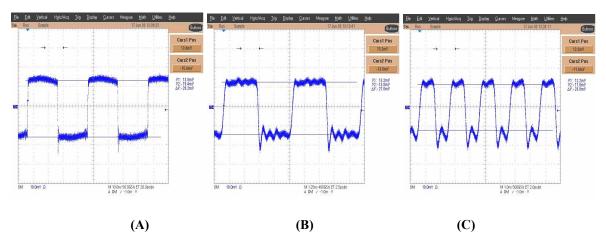

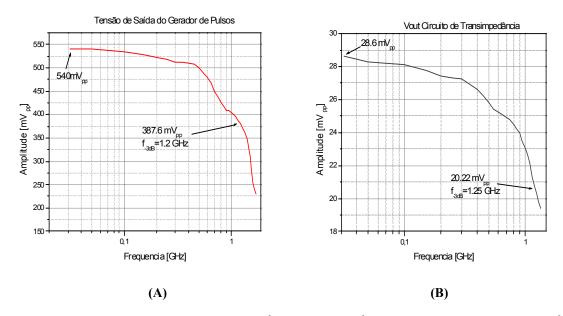

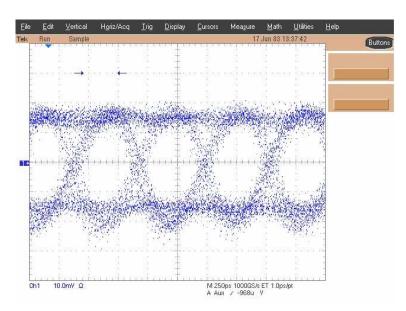

#### 2.2.2.3 – OPERAÇÃO COM SINAIS AC