### **CLEBER BIASOTTO**

# "PROCESSOS ALTERNATIVOS PARA MICRO E NANOTECNOLOGIA"

CAMPINAS 2012

## UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA ELÉTRICA E DE COMPUTAÇÃO

#### **CLEBER BIASOTTO**

## "PROCESSOS ALTERNATIVOS PARA MICRO E NANOTECNOLOGIA"

Tese de Doutorado apresentada à Faculdade de Engenharia Elétrica e Computação da Universidade Estadual de Campinas como parte dos requisitos exigidos para a obtenção do título de Doutor em Engenharia Elétrica, na área de Eletrônica, Microeletrônica e Optoeletrônica.

Orientador: Prof. Dr. José Alexandre Diniz

ESTE EXEMPLAR CORRESPONDE Á VERSÃO FINAL DA TESE DEFENDIDA PELO ALUNO CLEBER BIASOTTO, E ORIENTADA PELO PROF. DR. JOSÉ ALEXANDRE DINIZ.

CAMPINAS 2012

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA E ARQUITETURA - BAE - UNICAMP

Biasotto, Cleber

B47p

Processos alternativos para micro e nanotecnologia / Cleber Biasotto. --Campinas, SP: [s.n.], 2012.

Orientador: José Alexandre Diniz. Tese de Doutorado - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Microeletrônica. 2. Baixas temperaturas. 3. Laser. 4. Nanotecnologia. 5. Junções rasas. I. Diniz, José Alexandre, 1964-. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

Título em Inglês: Alternative processes for micro and nanotechnology Palavras-chave em Inglês: Microelectronics, Low temperatures, Laser, Nanotechnology, Shallow Junctions

Área de concentração: Eletrônica, Microeletrônica e Optoeletrônica

Titulação: Doutor em Engenharia Elétrica

Banca examinadora: José Alexandre Diniz, Leonardo Breseghello Zoccal, Henri Ivanov Boudinov, Ioshiaki Doi, Peter Jürgen Tatsch

Data da defesa: 22-11-2012

Programa de Pós Graduação: Engenharia Elétrica

#### COMISSÃO JULGADORA - TESE DE DOUTORADO

| Candidato: Cleber Biasotto                                           |

|----------------------------------------------------------------------|

| Data da Defesa: 22 de novembro de 2012                               |

| Título da Tese: "Processos Alternativos para Micro e Nanotecnologia" |

|                                                                      |

| Prof. Dr. José Alexandre Diniz (Presidente):                         |

| Prof. Dr. Leonardo Breseghelio Zoccal:                               |

| Prof. Dr. Henri Ivanov Boudinov: William                             |

| Prof. Dr. Joshiaki Doi Ashiralis & ?                                 |

| Prof. Dr. Peter Jürgen Tatsch: Rhis Juneau Polis.                    |

É com grande amor e gratidão que dedico este trabalho a minha filha Stephanie.

Dedico também a todos os alunos de mestrado e doutorado que trabalham fortemente no desenvolvimento científico e tecnológico deste país.

#### Este trabalho foi realizado com o apoio das seguintes entidades:

- Conselho Nacional de Desenvolvimento Científico e Tecnológico CNPq

- Faculdade de Engenharia Elétrica e de Computação FEEC/UNICAMP

- Departamento de Semicondutores, Instrumentos e Fotônica DSIF/UNICAMP

- Centro de Componentes Semicondutores CCS/UNICAMP

- Instituto de Física "Gleb Wataghin"- IFGW/UNICAMP

- Delft University of Technology TUDelft

- Delft Institute of Microsystems and Nanoelectronics Dimes

- Comunidade Européia (Sixth Framework FP6 project): "Disposable Dot Field Effect Transistor for High Speed Si Integrated Circuits"

#### **AGRADECIMENTOS**

- Primeiramente eu gostaria de expressar a minha gratidão a todos os que me deram a possibilidade de completar estes anos de pesquisa de Doutorado;

- Obrigado muito especial à minha filha Stephanie e Andrea. Elas sacrificaram parte de sua vida para me acompanhar, e eu não teria terminado este trabalho sem elas. Muito obrigado por todo o apoio, inspiração e compreensão que me manteve concentrado e motivado durante este tempo;

- Ao meu orientador, Prof. Dr. José Alexandre Diniz, pela oportunidade, confiança e amizade durante a realização deste trabalho;

- Ao Prof. Dr. Jacobus W. Swart pela colaboração acadêmica;

- Ao Prof. Dr. Stanislav Moshkalyov e André Daltrini pelas análises de plasma;

- Ao Antonio Celso Saragossa Ramos pela colaboração técnica prestada;

- A toda a parte técnica do Centro de Componentes Semicondutores (CCS), em especial ao Godoy, Regina e Eduardo;

- A Faculdade de Engenharia Elétrica e de Computação (FEEC/UNICAMP), Departamento de Semicondutores, Instrumentos e Fotônica (DSIF/UNICAMP), Centro de Componentes Semicondutores (CCS/ UNICAMP), Instituto de Física "Gleb Wataghin" (IFGW/UNICAMP), Laboratório de Pesquisa em Dispositivos (LPD/UNICAMP);

- A Delft University of Technology (TUDelft), Laboratory of Electronic Components Technology and Materials (ECTM) e Delft Institute of Microsystems and Nanoelectronics (Dimes);

- A comunidade européia por participar do projeto "Disposable Dot Field Effect Transistor for High Speed Si Integrated Circuits" (projeto D-DotFET), Sixth Framework Programme;

- A minha supervisora Profa. Dra. Lis Nanver por me dar a oportunidade de trabalhar na TUDelft no grupo de integração de dispositivos de silício, pelas críticas construtivas durante e incentivo durante todo o projeto, avaliação, pela supervisão diária e pelas várias discussões proveitosas;

- Gostaria de agradecer a Profa. Dra. Lina Sarro e Dr. Kees Beenakker por seu esforço na gestão de um excelente ambiente no Dimes;

- Agradeço a toda equipe técnica e administrativa do Dimes. Para Silvana Milosavljevic e Tom Scholtes meus especiais agradecimentos;

- Gostaria de agradecer a tosos meus amigos e colegas da TUDelft. Principalmente para Dr.

Vladimir Jovanovic, por sua ajuda e discussões durante o desenvolvimento do projeto;

- A todas Universidades envolvidas no projeto D-DotFET: Forschungszentrum Jülich (FZ Jülich Alemanha), Leibniz Institute for Solid State and Materials Research (IFW Dresden Alemanha), Johannes Kepler University (Linz Áustria), University of Milano (Bicocca- Itália), Technical University Wien (Áustria);

- A empresa STMicroelectronics (Grenoble França);

- Sou grato a meu amigo Fábio Cavarsan pelo apoio e amizade durante toda a pesquisa;

- Ao CNPq pelo apoio financeiro;

- Finalmente, gostaria de agradecer as inúmeras pessoas que de alguma forma contribuíram para que este trabalho pudesse ser realizado.

#### **RESUMO**

Atualmente para atender à necessidade de fabricação dos sensores, dispositivos eletrônicos e circuitos integrados com dimensões micro e nanométricas, novos processo de custos e de thermal budgets reduzidos são necessários. Este trabalho apresenta o desenvolvimento de alguns destes novos processos alternativos para aplicação nesta fabricação. O trabalho está dividido em quatro partes: a primeira parte apresenta a obtenção e a caracterização de filmes isolantes de nitreto de silício para aplicação em microsensores, tais como o sensor de pressão. Estes filmes foram obtidos sobre substratos de Si em baixa temperatura (20°C) utilizando-se um reator de plasma do tipo ECR-CVD (Electron Cyclotron Resonance - Chemical Vapor Deposition). Normalmente reatores do tipo Low Pressure Chemical Vapor Deposition (LPCVD) ou Plasma Enhanced - CVD (PECVD) em temperaturas maiores que 600°C e 250°C, respectivamente, são utilizados para essa aplicação. A caracterização dos plasmas ECR, que foram usados para as deposições dos nitretos, e a fabricação de membranas suspensas com estes filmes são apresentadas. A segunda parte apresenta a fabricação e a caracterização de diodos p+-n fabricados em camada de SiGe crescida por LPCVD sobre substrato de Si. Processo este alternativo em substituição aos executados em reatores epitaxiais de alto custo. Na terceira parte deste trabalho, é apresentado o desenvolvimento de processos em baixa temperatura para aplicação em diodos e tecnologia MOS (Metal-Oxide-Semiconductor). São apresentadas a fabricação e a caracterização elétrica dos capacitores MOS, utilizando as tecnologias ALD (Atomic Layer Deposition) e ICP (Inductively Coupled Plasma) para a obtenção em baixa temperatura dos dielétricos high-k de Al<sub>2</sub>O<sub>3</sub> e SiON de porta MOS, respectivamente. Na quarta parte, são apresentadas também, a fabricação e a caracterização elétrica de diodos n<sup>+</sup>p utilizando a tecnologia de recozimento a laser. O desenvolvimento de capacitores MOS e diodos possibilitou a fabricação (usando processos em baixa temperatura (≤400°C)) de n- e p-MISFETs (Metal-Insulator-Semiconductor Field Effect Transistors), como também a fabricação de um protótipo de transistor MOS de alta velocidade baseado em silício germânio chamado D-DotFET (Disposable Dot Field Effect Transistor). Os processos alternativos desenvolvidos nesta tese apresentam um enorme potencial para aplicação nas próximas gerações de dispositivos CMOS (Complementary Metal Oxide Semiconductor) de dimensões sub-22 nm.

Palavras-chave: Microeletrônica, Baixas temperaturas, Laser, Nanotecnologia, Junções rasas.

#### **ABSTRACT**

Nowadays, to attend the needs of the fabrication of sensors, electronic devices and integrated circuits with dimensions of micro and nanometrics, new processes of reduced costs and thermal budgets are needed. This work presents the development of some of these alternative processes for this fabrication. This work is divided in four parts: the first part presents the synthesis and characterization of insulating films of silicon nitride for application in microsensors, such as pressure sensors. These films were deposited on Si substrates at low temperature (20°C) using an ECR-CVD (Electron Cyclotron Resonance - Chemical Vapor Deposition) plasma reactor. Normally, Low Pressure Chemical Vapor Deposition (LPCVD) or Plasma Enhanced CVD - (PECVD) reactors are used for this application with high temperature process higher than 600°C and 250°C, respectively. The characterization of ECR plasmas, which were used to get the silicon nitrides, and the fabrication of suspended membranes based on these nitrides are presented. The second part presents the fabrication and the characterization of p+-n silicon germanium (SiGe) diodes fabricated on SiGe layers, which were grown by LPCVD on Si substrate. The grown of SiGe layers by LPCVD is an alternative process to replace the high cost of epitaxial reactors. In the third part of this work is presented the development of low-temperature processes for application in diodes and MOS (Metal-Oxide-Semiconductor) technology. The fabrication at low temperature and electrical characterization of MOS capacitors, using technologies as: ALD (Atomic Layer Deposition) and ICP (Inductively Coupled Plasma) to get the Al<sub>2</sub>O<sub>3</sub> and SiON high-k gate dielectrics of MOS capacitors are presented, respectively. In the four part, the fabrication and electrical characterization of n+-p diodes using the process of laser annealing are presented as well. The development of MOS capacitors and diodes have become feasible the fabrication (using processes at low temperature (≤ 400°C)) of n- and p-MISFETs (Metal- Insulator -Semiconductor Field Effect Transistors) and also the fabrication of a high speed MOS transistor prototype based on silicon germanium named D-DotFET (Disposable Dot Field Effect Transistor). In conclusion, the alternative processes developed in this thesis have shown to be a huge potential for application in next generations of CMOS (Complementary Metal Oxide Semiconductor) devices with sub- 22 nm dimensions.

**Keywords:** Microelectronics, Low temperatures, Laser, Nanotechnology, Shallow Junctions.

## **SUMÁRIO**

| CAPÍTULO 1- INTRODUÇÃO                                                                                          | 1  |

|-----------------------------------------------------------------------------------------------------------------|----|

| 1.1- Objetivo da Tese                                                                                           | 1  |

| 1.2 –Motivação para estudar os processos alternativos                                                           | 4  |

| 1.3- Composição da Tese                                                                                         | 6  |

| CAPÍTULO 2 - PROCESSOS ALTERNATIVOS PARA MICRO E                                                                |    |

| NANOTECNOLOGIA                                                                                                  | 9  |

| 2.1- O processo de deposição por ECR-CVD de $SiN_x$ para aplicação em sistemas                                  |    |

| microeletromecânicos                                                                                            | 9  |

| 2.1.1 - Sistemas microeletromecânicos                                                                           | 9  |

| 2.1.2- Nitreto de silício                                                                                       | 11 |

| 2.1.3- ECR-CVD                                                                                                  | 13 |

| 2.2- Os processos alternativos para a obtenção de dielétricos high-k de Al <sub>2</sub> O <sub>3</sub> e SiON e |    |

| de junçãos rasas para o desenvolvimento da tecnologia CMOS                                                      | 14 |

| 2.2.1 - O escalamento da tecnologia CMOS e a necessidade de novos materiais e                                   |    |

| de processos de fabricação                                                                                      | 15 |

| 2.2.2- Materiais dielétricos <i>High-k</i> utilizados neste trabalho                                            | 20 |

| 2.2.2.1- Oxinitreto de silício                                                                                  | 20 |

| 2.2.2.2- Óxido de alumínio                                                                                      | 21 |

| 2.2.3- Métodos alternativos (ALD e ICP) para obtenção de dielétricos High-k                                     |    |

| utilizados neste trabalho                                                                                       | 21 |

| 2.2.3.1- Deposição filmes por camada atômica                                                                    | 22 |

| 2.2.3.2- Plasma com acoplamento indutivo                                                                        | 26 |

| 2.2.4- Necessidade de junções rasas na região de fonte e dreno em transistores                                  |    |

| MOS                                                                                                             | 27 |

| 2.2.5- Processo alternativo de recozimento a laser para obtenção de junções                           |    |

|-------------------------------------------------------------------------------------------------------|----|

| rasas                                                                                                 | 29 |

| 2.3- O processo alternativo (LPCVD-vertical) de obtenção de camadas de SiGe para a                    | 21 |

| tecnologia de dispositivos de silício germânio                                                        | 31 |

|                                                                                                       |    |

| 2.3.2- Algumas aplicações dos filmes de SiGe                                                          |    |

| 2.3.3- Crescimento epitaxial                                                                          |    |

| 2.3.4- LPCVD-vertical para obtenção de camadas de SiGe                                                | 39 |

| 2.3.4.1- Obtenção das camadas de SiGe pelo sistema LPCVD-                                             |    |

| vertical                                                                                              | 41 |

|                                                                                                       |    |

|                                                                                                       |    |

| CAPÍTULO 3- PROCEDIMENTO EXPERIMENTAL                                                                 | 43 |

| 3.1- Deposição ECR-CVD em temperatura ambiente para obtenção de filmes de $\mathrm{Si}_3\mathrm{N}_4$ |    |

| para aplicação em tecnologia MEMS                                                                     | 43 |

| 3.2 – Deposição de filmes de SiGe em sistema LPCVD-vertical                                           | 45 |

| 3.2.1- Reator LPCVD-vertical                                                                          | 45 |

| 3.2.1.1- Limpeza da câmara LPCVD                                                                      | 46 |

| 3.2.2- Obtenção das camadas de SiGe                                                                   | 47 |

| $3.3$ - Deposição de filmes de $Al_2O_3$ por camada atômica (ALD) e oxinitretação do Si               |    |

| por plasma ICP em baixa temperatura para aplicação como dielétrico de porta de                        |    |

| dispositivos MOS                                                                                      | 48 |

| 3.3.1 – Fabricação de Capacitores Metal-Insulator-Semiconductor (MIS), tendo                          |    |

| como dielétricos de porta os filmes de SiON e de Al <sub>2</sub> O <sub>3</sub>                       | 48 |

| 3.3.1.1 - Processo de fabricação dos capacitores MIS                                                  | 48 |

| 3.4 - Recozimento a laser para obtenção de junções rasas em diodos e transistores                     |    |

| MOS                                                                                                   | 51 |

| 3.4.1 - Sistema de recozimento a laser                                                                | 51 |

| 3.4.1.1 - Camada refletiva para recozimento a laser                                                   | 51 |

| 3.4.2 - Transistores MIS com fonte e dreno recozidos a laser                                          | 52 |

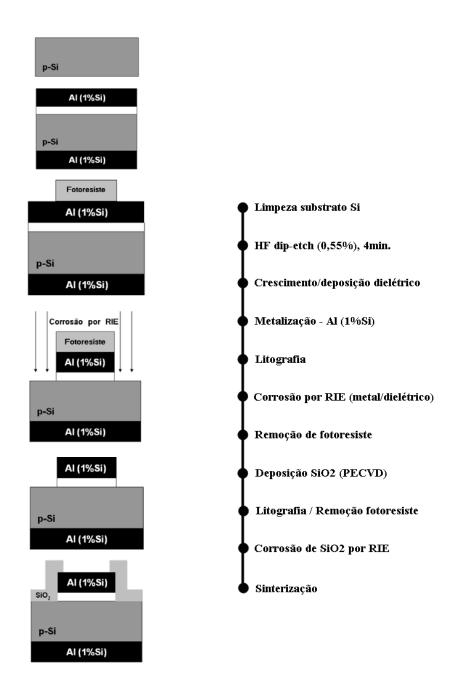

| 3.4.2.1 - Processo de fabricação dos MISFETs                                                          | 52 |

| CAPÍTULO 4- RESULTADOS EXPERIMENTAIS E DISCUSSÕES                                                       | 59  |

|---------------------------------------------------------------------------------------------------------|-----|

| 4.1- Deposição ECR-CVD em temperatura ambiente para obtenção de filmes o                                | de  |

| Si <sub>3</sub> N <sub>4</sub> para aplicação em tecnologia MEMS                                        | 59  |

| 4.1.1- Análise de plasma                                                                                | 59  |

| 4.1.2- Análise dos filmes e fabricação de estruturas suspensas                                          | 61  |

| 4.2- Deposição de filmes de SiGe em sistema LPCVD-vertical                                              | 66  |

| 4.2.1 - Caracterização física dos filmes de SiGe                                                        | 66  |

| 4.2.2 - Fabricação e caracterização elétrica dos diodos                                                 | 67  |

| 4.2.3 - Crescimento de SiGe com outros parâmetros                                                       | 72  |

| 4.3- Deposição de filmes de Al <sub>2</sub> O <sub>3</sub> por camada atômica (ALD) e oxinitretação do  | Si  |

| por plasma ICP em baixa temperatura para aplicação como dielétrico de porta o                           | de  |

| dispositivos MOS                                                                                        | 75  |

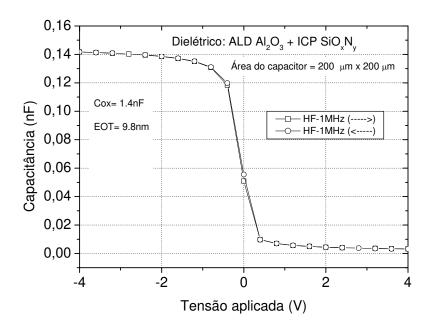

| 4.3.1- Caracterização elétrica dos capacitores MIS                                                      |     |

| 4.4 - Recozimento a laser para obtenção de junções rasas em diodos e transistor                         | es  |

| MOS                                                                                                     | 78  |

| 4.4.1- Integridade das máscaras refletivas de alumínio                                                  | 78  |

| 4.4.2- Fabricações de junções n <sup>+</sup> p auto-alinhadas                                           | 80  |

| 4.4.3 - Caracterização dos transistores MIS                                                             | 87  |

| 4.3.4- Caracterização elétrica dos transistores MIS                                                     | 87  |

| 4.3.5- Caracterização física dos transistores MIS                                                       | 95  |

|                                                                                                         |     |

|                                                                                                         |     |

| CAPÍTULO 5- CONCLUSÕES E PERSPECTIVAS FUTURAS                                                           | 101 |

| 5.1 - Deposição ECR-CVD em temperatura ambiente para obtenção de filmes o                               | de  |

| Si <sub>3</sub> N <sub>4</sub> para aplicação em tecnologia MEMS                                        | 101 |

| 5.2 - Deposição de filmes de SiGe em sistema LPCVD-vertical                                             |     |

| 5.3 - Deposição de filmes de Al <sub>2</sub> O <sub>3</sub> por camada atômica (ALD) e oxinitretação do |     |

| por plasma ICP em baixa temperatura para aplicação como dielétrico de porta o                           |     |

| dispositivos MOS                                                                                        |     |

| 5.4 - Recozimento a laser para obtenção de junções rasas em diodos e transistor                         |     |

| MOS                                                                                                     | 103 |

| 5.5 – Perspectivas futuras               | 107 |

|------------------------------------------|-----|

| Anexo A - FABRICAÇÃO DE MÁSCARAS         | 111 |

| Anexo B – LISTA DE PUBLICAÇÕES           | 112 |

| REFERÊNCIAS BIBLIOGRÁFICAS               | 115 |

| Referências bibliográficas do Capítulo 1 | 115 |

| Referências bibliográficas do Capítulo 2 | 116 |

| Referências bibliográficas do Capítulo 3 | 127 |

| Referências bibliográficas do Capítulo 4 | 131 |

| Referências bibliográficas do Capítulo 5 | 134 |

#### LISTA DE FIGURAS

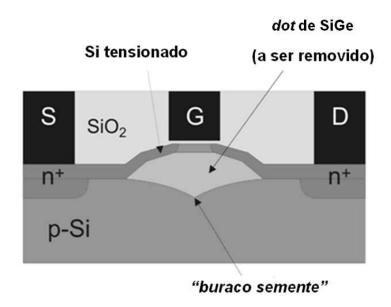

- Figura 1.1: Seção transversal do transistor D-DotFET com dot de SiGe utilizando "buraco semente" em substrato de silício. A região de porta é localizada sobre o dot de SiGe onde a tensão do filme de silício é alta. O dot pode ser removido em algum estágio do processamento.

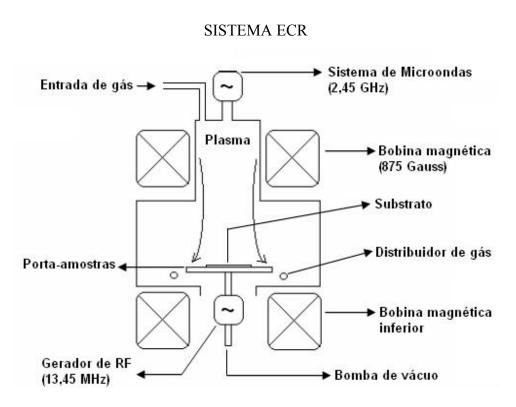

- Figura 2.1: Diagrama esquemático do sistema ECR.

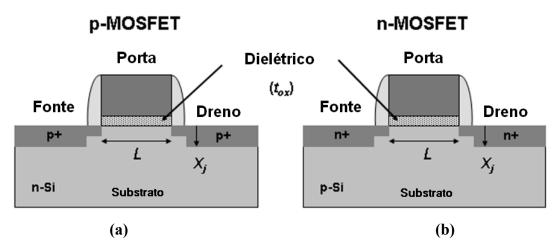

- Figure 2.2: Seção transversal de um dispositivo (a) n-MOSFET e (a) p-MOSFET.

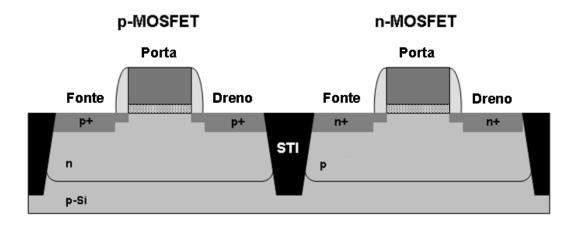

- Figure 2.3: Seção transversal de um dispositivo utilizando tecnologia CMOS onde MOS de canal p e canal n são fabricados em um mesmo substrato. Técnica de *Shallow Trench Insulation* é utilizada em atuais processos CMOS, isolando os dispositivos.

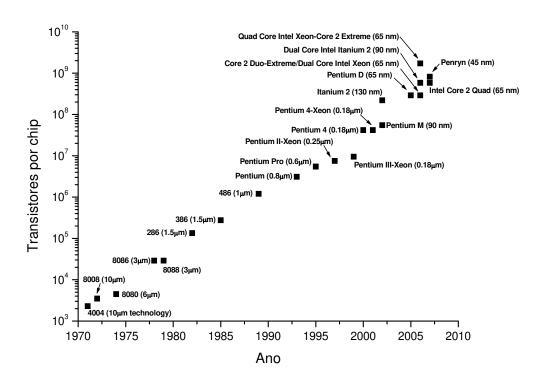

- Figura 2.4: A evolução dos processadores Intel<sup>®</sup> e a tecnologia associada exemplificando a lei de Moore [21].

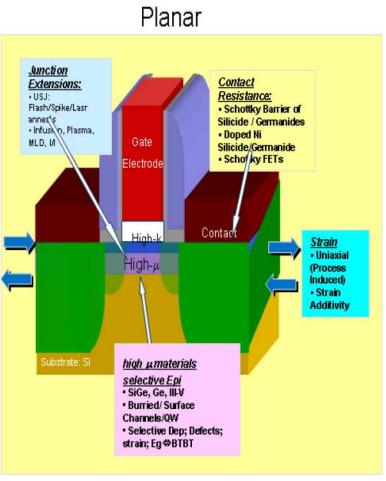

- Figura 2.5: Desafios para tecnologia planar de dispositivos MOSFET [24].

- Figura 2.6: Diagrama esquemático do sistema ALD.

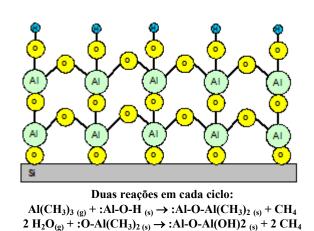

- Figura 2.7: Esquemático de um ciclo de deposição.

- Figura 2.8: Reações químicas (das letras a até g) durante o processo de deposição de Al<sub>2</sub>O<sub>3</sub>

por ALD em substrato de Si. Adaptado de [54].

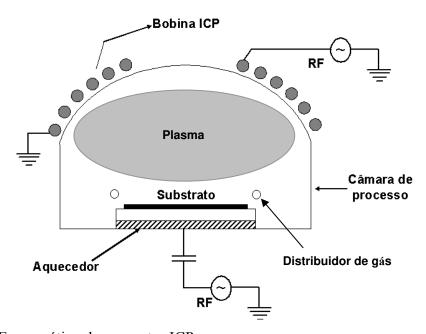

- Figura 2.9: Esquemático de um reator ICP.

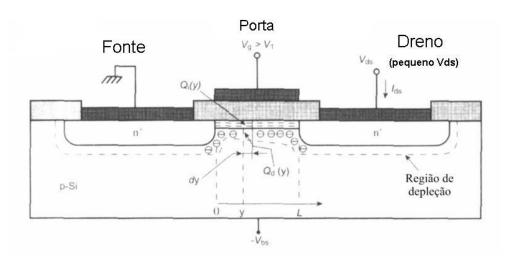

- Figura 2.10: Regiões de depleção de fonte e de dreno de um transistor n-MOS [59].

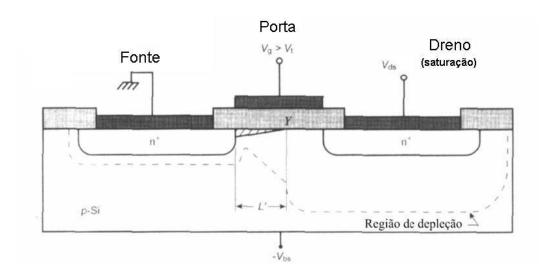

- Figura 2.11: Aumento da região de depleção de dreno devido ao aumento do potencial aplicado no dreno [59].

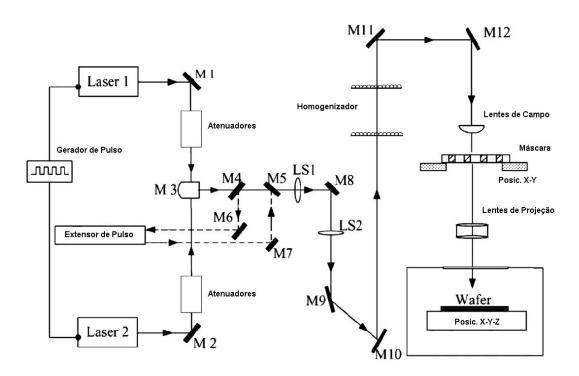

- Figura 2.12: Esquemático do sistema de laser Exitech M8000V, onde M1-M12 são espelhos e LS1-LS2 são lentes [72].

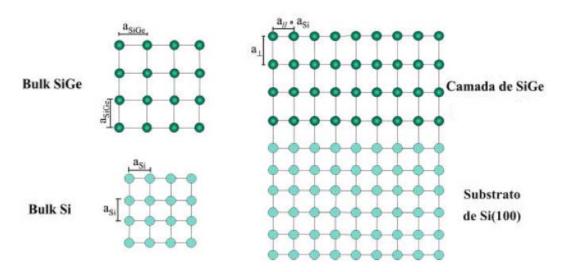

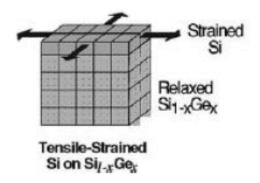

- Figura 2.13: Estrutura do Si, do Ge e da estrutura de SiGe epitaxial crescida sobre o substrato de Si [80].

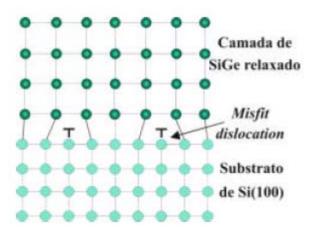

- Figura 2.14: Discordância tipo *misfit* na interface Si/ SiGe [80].

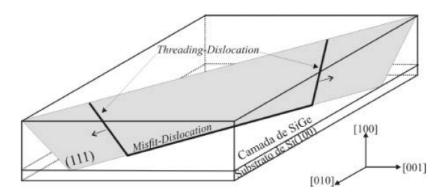

- Figura 2.15: Discordância tipo *threading* na camada de SiGe [80].

- Figura 2.16: Camada de Si tensionada sobre SiGe relaxado [80].

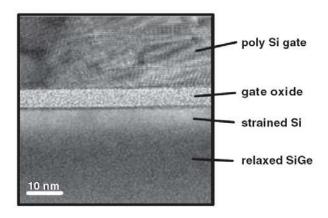

- Figura 2.17: Imagem TEM de dispositivo MOS utilizando Si/SiGe [80].

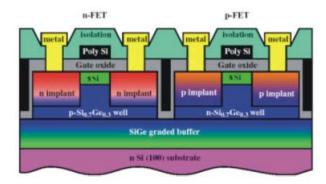

- Figura 2.18: Estrutura de um dispositivo CMOS onde é utilizado o Si tensionado na região de canal [88].

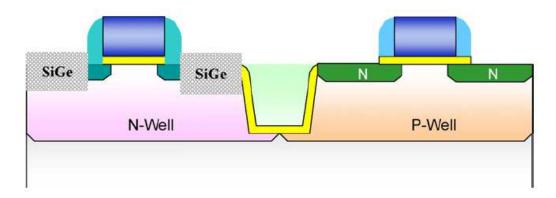

- Figura 2.19: Estrutura de dispositivo CMOS utilizando SiGe epitaxial na fonte e dreno de transistor p-MOS [89].

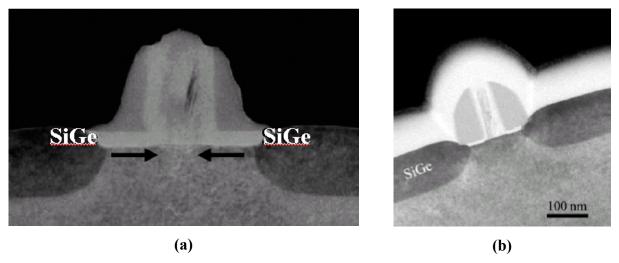

- Figura 2.20: Imagem SEM de um transistor p-MOS com SiGe na região de fonte e dreno crescido por epitaxia. O SiGe utilizado na região de fonte e dreno provoca um estresse compressivo no canal do transistor que melhora a mobilidade do portador (a) [89] e (b) [88].

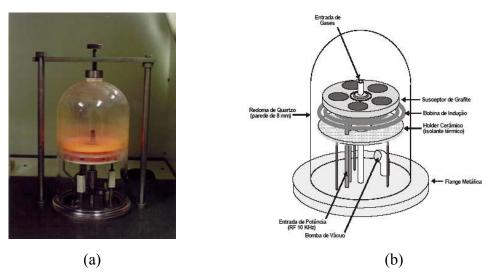

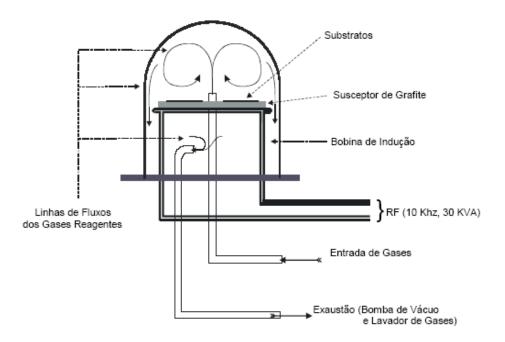

- Figura 2.21: Câmara do reator Epitaxial Vertical (a) Foto do Reator em funcionamento (b) Esquema interno da câmara de reação [97].

- Figura 2.22: Sistema de fluxo de gases na câmara do reator [98].

- Figura 3.1: Amostra com SiGe-epi por LPCVD vertical.

- Figura 3.2: Fluxograma básico do processo de fabricação dos capacitores.

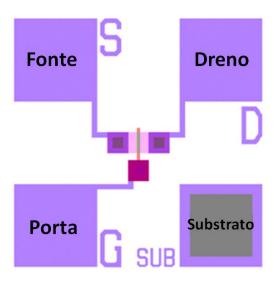

- Figura 3.3: *Layout* do transistor MIS a ser fabricado.

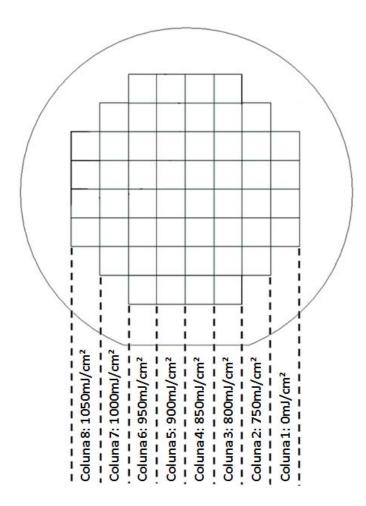

- Figura 3.4: Configuração de energia da radiação de laser aplicada no recozimento de fonte e dreno dos dispositivos MISFETs.

- Figura 3.5: Principais etapas do processo de fabricação dos dispositivos n-MISFETs.

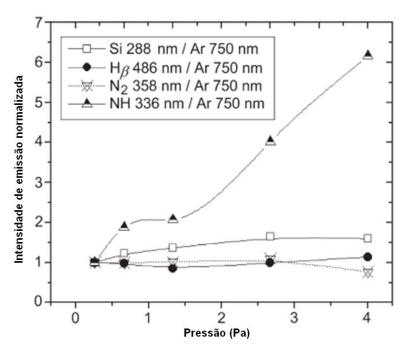

- Figura 4.1: Intensidade de espectros normalizados para espécies Si, H, NH e N<sub>2</sub> a diferentes pressões.

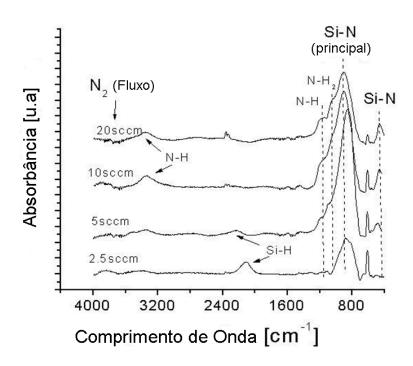

- Figura 4.2: Espectro FTIR dos filmes de nitreto de silício para diferentes fluxos de N<sub>2</sub>.

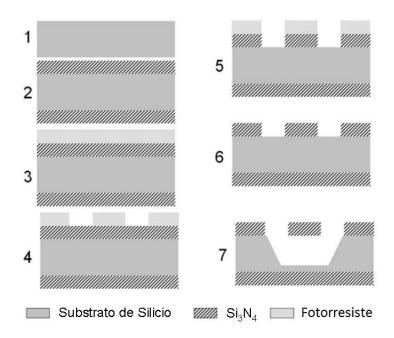

- Figura 4.3: Fluxograma para fabricação das membranas suspensas. (1) limpeza do substrato de Si pelo processo RCA, (2) deposição dos filmes de SiN por ECR-CVD, (3) aplicação de fotorresiste, (4) litografía, (5) corrosão do SiN por RIE, (6) remoção do fotorresiste, (7) corrosão do Si em solução de KOH.

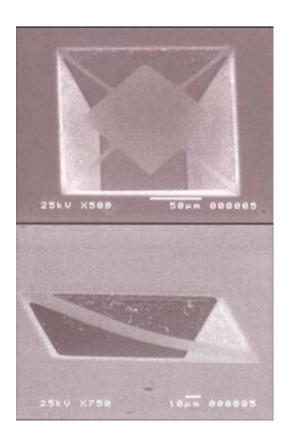

- Figura 4.4: Imagens SEM das membranas suspensas com filmes de nitreto de silício fabricadas em substratos de Si utilizando 0,67 Pa, 5W RF, e 5 sccm de N<sub>2</sub>.

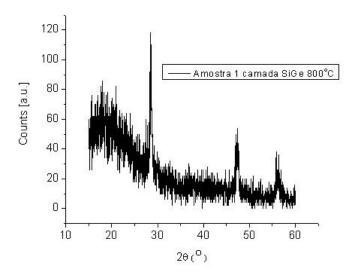

- Figura 4.5: Estrutura Poli-Cristalina No eixo 2θ, os ângulos 28°, 47° e 57° são correspondentes às orientações (111), (220) e (311), respectivamente.

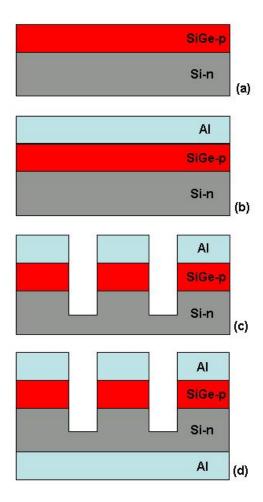

- Figura 4.6: Processo de fabricação dos diodos. (a) crescimento da camada de SiGe, implantação de boro, recozimento por RTA, (b) deposição de Al, litografia, corrosão por RIE, (c) deposição de Al na parte inferior da lâmina de Si.

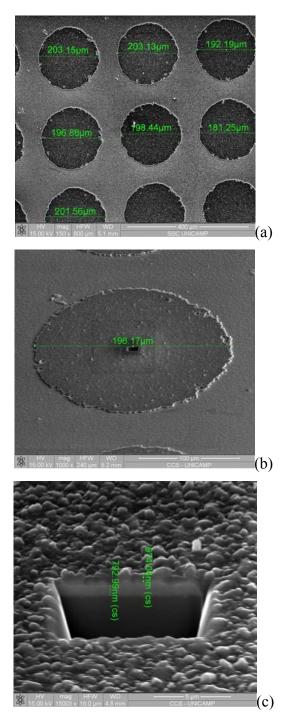

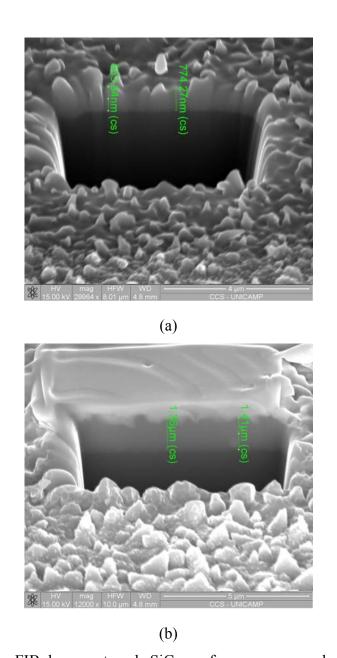

- Figura 4.7: (a) Diodos de SiGe fabricados, (b) diodo escolhido para análise e corrosão realizada por FIB, (c) análise de espessura das camadas: 792,99nm de SiGe e 674,04nm de Al.

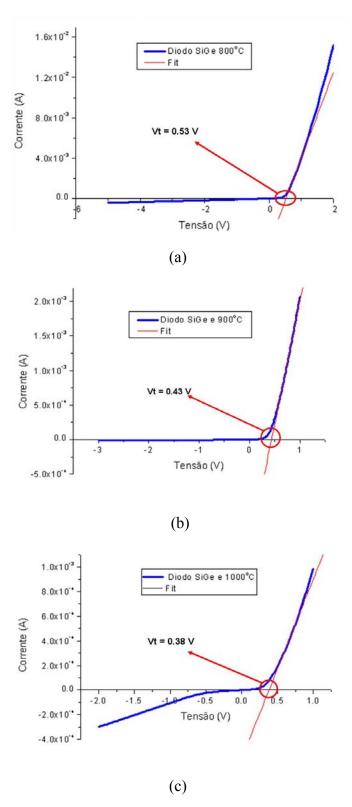

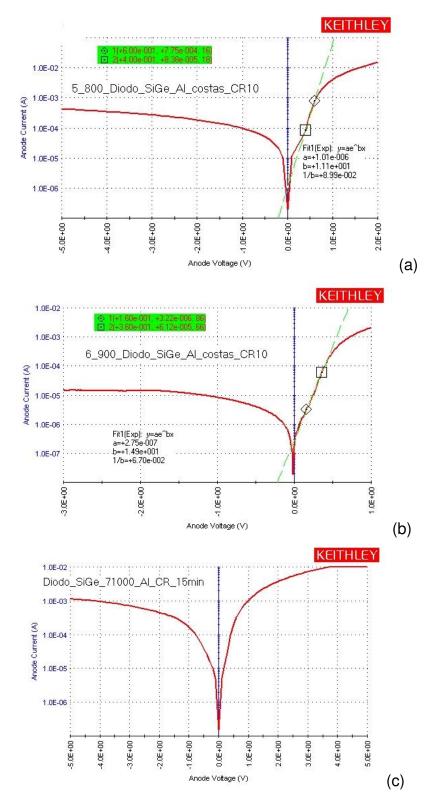

- Figura 4.8: Curva I-V dos diodos fabricados com camada de SiGe crescida a (a) 800oC, (b) 900°C e (c) 1000°C.

- Figura 4.9: Gráficos I-V dos diodos fabricados com camada de SiGe crescida a (a) 800oC,

(b) 900°C e (c) 1000°C.

- Figura 4.10: Imagem FIB das amostras de SiGe conforme processos da (a) Tabela 4.2 e (b) Tabela 4.3.

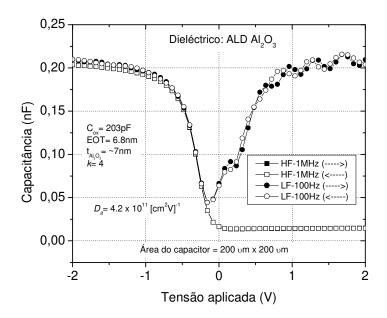

- Figura 4.11: Característica C-V do capacitor com dielétrico de Al2O3 depositado por ALD a 300oC. Capacitores de 200 μm × 200 μm de área.

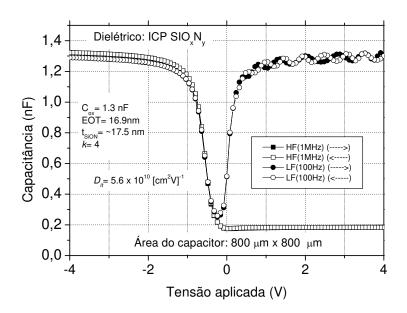

- Figure 4.12: Característica C-V de capacitor com dielétrico de SiON crescidos por ICP a 250oC. Capacitores de 800 μm × 800 μm de área.

- Figure 4.13: Característica C-V do capacitor com dielétricos SiON crescidos por ICP a 250°C e ALD Al<sub>2</sub>O<sub>3</sub> depositado a 300°C. Capacitores de 200 μm × 200 μm de área.

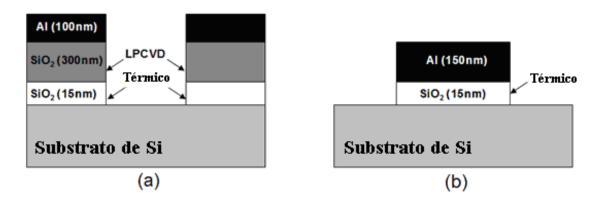

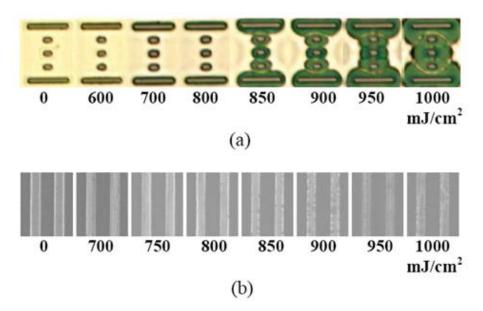

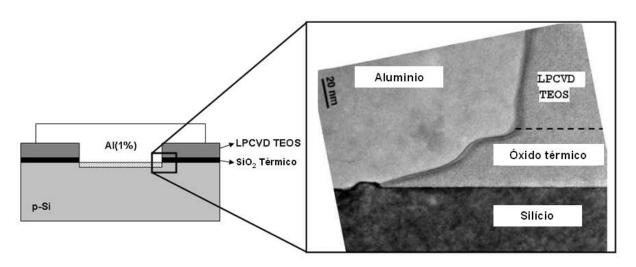

- Figura 4.14: Estruturas fabricadas para teste de Al como máscara refletiva. Estrutura (a) 100nm Al / 300 nm SiO<sub>2</sub> LPCVD / 30 nm SiO<sub>2</sub> térmico e estrutura (b) 150 nm Al / 15 nm SiO<sub>2</sub> térmico.

- Figura 4.15: Imagens da camada refletiva de Al sob várias energias de laser. Evaporação de

Al ocorre nas bordas das estruturas devido ao óxido espesso. Evaporação de borda é

aumentada conforme a energia do laser aumenta (a) [17]. Imagem SEM de linhas de Al

150nm sobre 15nm de óxido térmico após o recozimento. Nenhuma evaporação de Al é

observada (b) [18].

- Figura 4.16: Processo de fabricação de diodos p<sup>+</sup>n e n<sup>+</sup>p.

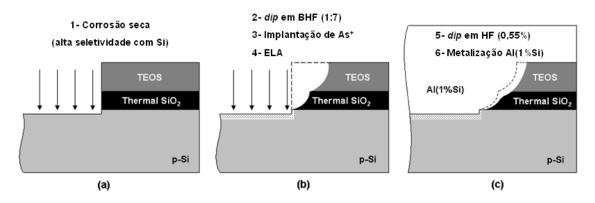

- Figura 4.17: Processo de corrosão da janela de contato (canto direito) durante o processo de fabricação. (a) janela de contato após a corrosão seca (alta seletividade com Si), (b) corrosão em BHF (1:7), implantação e recozimento a laser. Primeiro alargamento da janela de contato na direção lateral, (c) imersão em HF (0,55%) e metalização. Segundo o alargamento da janela de contato na direção lateral.

- Figura 4.18: Imagem TEM do lado direito da janela de contato dos diodos fabricados.

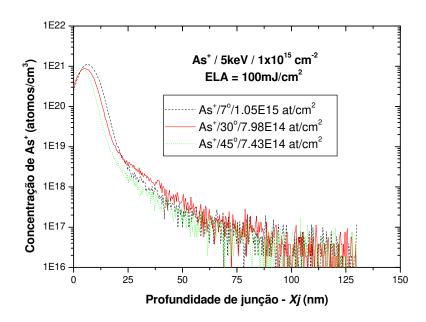

- Figura 4.19: Perfil SIMS das regiões implantadas e recozidas a 100mJ/cm² em três ângulos diferentes: 7°, 30° e 45°. Maior inclinação ângulos reduz a profundidade da junção, a um custo de perda de dose de implantação (devido a uma maior refexão na superfície).

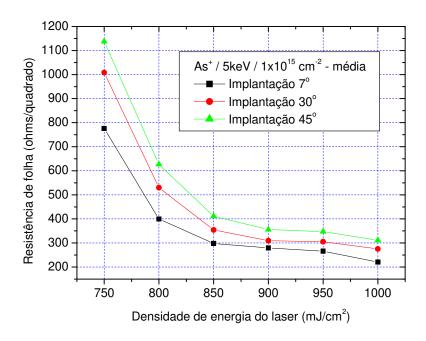

- Figura 4.20: Média da resistência de folha de uma amostra recozida a laser e implantadas a 5keV, 10<sup>15</sup> cm<sup>-2</sup>, ângulos de implantação: 7°, 30° e 45° versus a densidade de energia do laser.

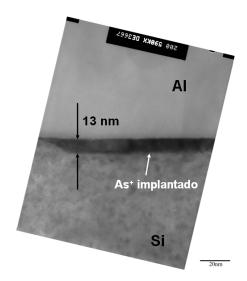

- Figura 4.21: Imagem TEM de uma junção n<sup>+</sup>p recozida a laser a uma energia de 1000mJ/cm<sup>2</sup> e implantação de As a um ângulo de 45°. Profundidade de junção de 13nm pode ser observada.

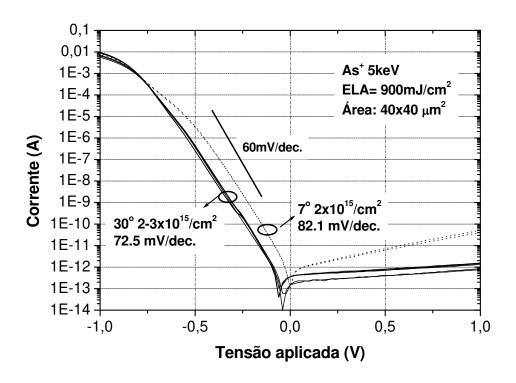

- Figura 4.22: Características I-V de diodos n<sup>+</sup>p auto-alinhados e recozidos a lazer a 900mJ/cm<sup>2</sup>.

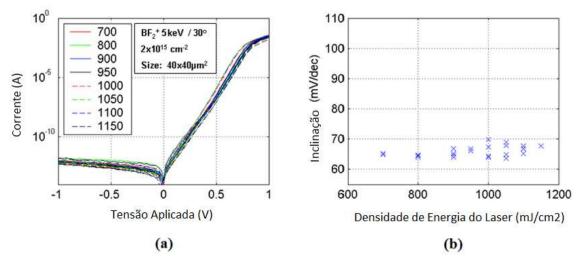

- Figura 4.23: (a) Características I-V dos diodos p<sup>+</sup>n auto-alinhados (40 x 40μm<sup>2</sup>) recozidos a laser em diferentes energias. (b) Inclinação das curvas em polarização direta versus energia do laser [21].

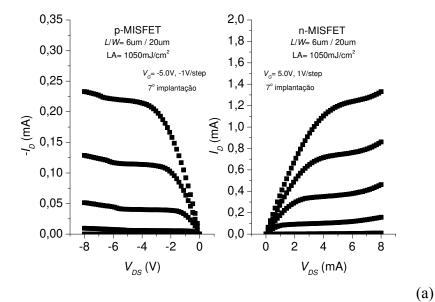

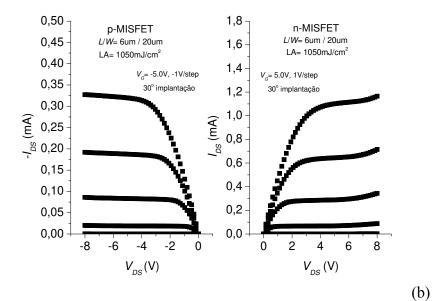

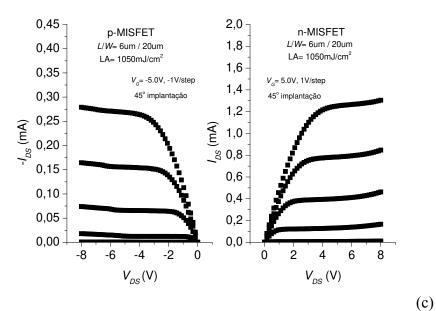

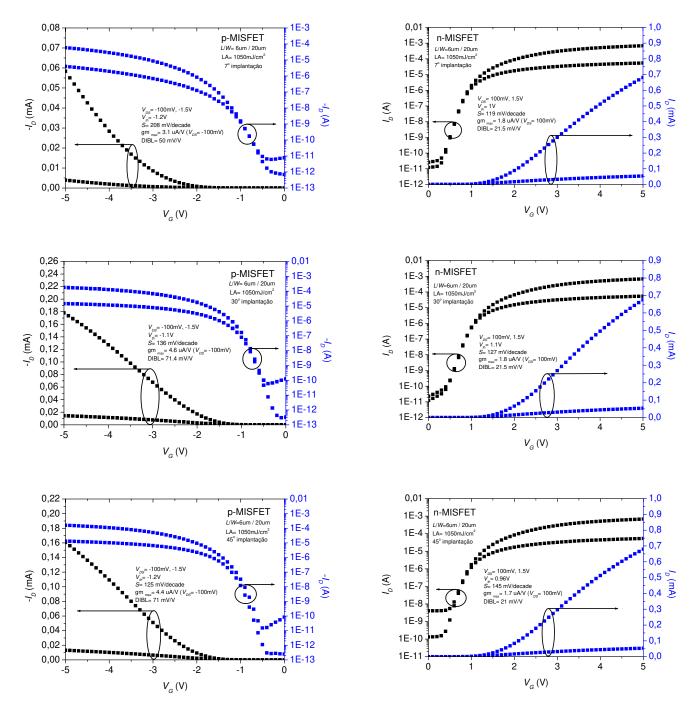

- Figure 4.24: Curvas da característica de saída  $I_D$  versus  $V_{DS}$  dos dispositivos n and p-MISFETs com comprimento de porta de 6µm com fonte e dreno recozidos a laser a  $1050 \text{mJ/cm}^2$  e implantados a (a)  $7^\circ$ , (b)  $30^\circ$  e (c)  $45^\circ$ . A largura de porta foi fixada em  $20 \mu\text{m}$ .

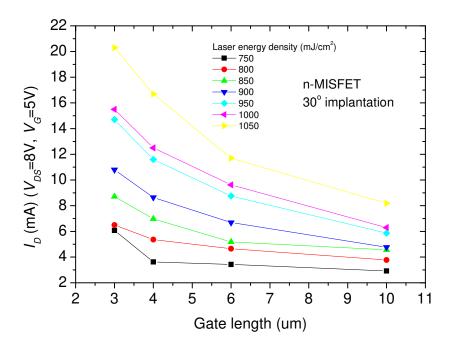

- Figura 4.25:  $I_D$  versus o comprimento de canal para transistores n-MISFETs com implantação de 30° e recozimento a laser variando entre 750 mJ/cm<sup>2</sup> e 1050 mJ/cm<sup>2</sup>.

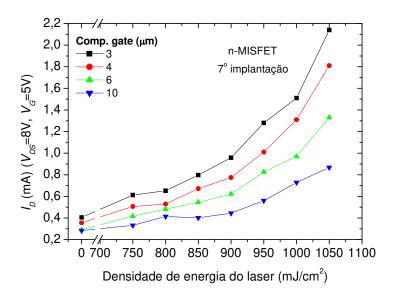

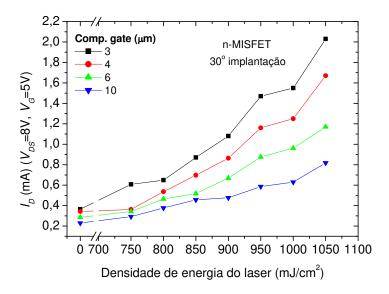

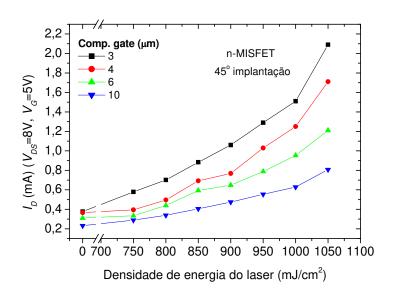

- Figure 4.26: Curva  $I_D$  versus densidade de energia do laser para dispositivos n-MISFETs com valor fixos de  $V_G$ = 5V e  $V_{DS}$ = 8V implantados a (a)7°, (b) 30° e (c) 45°.

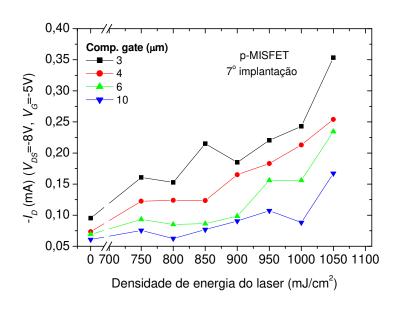

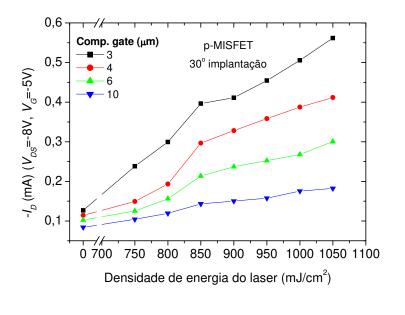

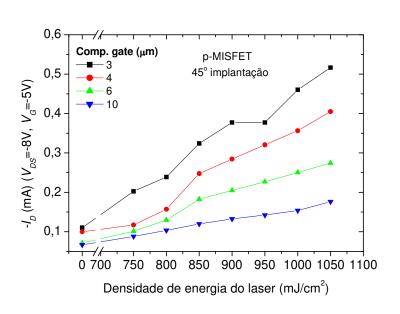

- Figure 4.27: Curva ID versus densidade de energia do laser para dispositivos p-MISFETs com valor fixos de  $V_G$ = -5V e  $V_{DS}$ = -8V implantados a (a)  $7^{\circ}$ , (b)  $30^{\circ}$  e (c)  $45^{\circ}$ .

- Figure 4.28:  $I_D$  versus  $V_{GS}$  e log  $I_D$  versus  $V_{GS}$  de n e p-MISFETs com comprimento de porta de 6 $\mu$ m, com fonte e dreno recozidos a laser a 1050mJ/cm<sup>2</sup> implantados a 7°, 30° and 45°. A largura de porta foi fixada em 20 $\mu$ m.

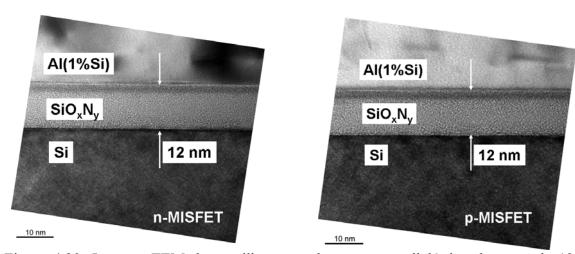

- Figura 4.29: Imagem TEM do empilhamento de porta com dielétrico de porta de 12nm ICP-SiON.

- Figura 4.30: Imagem TEM da região de junção de fonte e dreno (*Xj*).

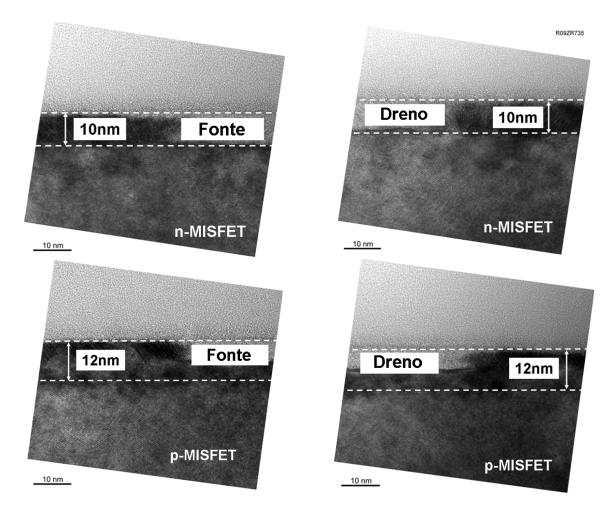

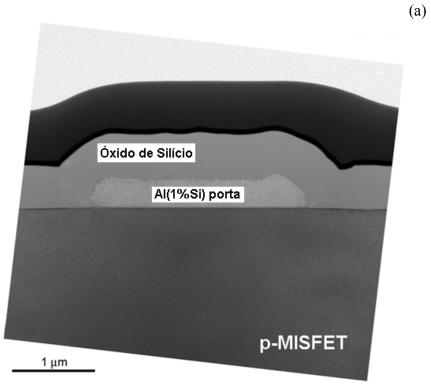

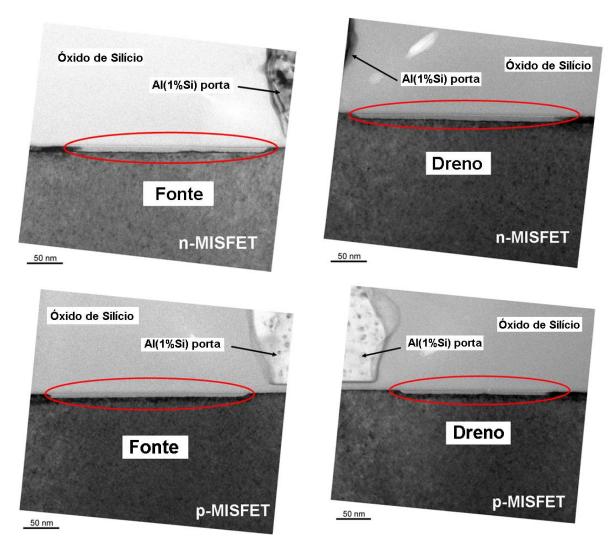

- Figura 4.31: Seção transversal dos dispositivos (a) n-MISFET e (b) p-MISFET, L= 3μm e

W= 20μm. Região de fonte e dreno foram recozidos a laser em uma densidade de energia de 1000mJ/cm<sup>2</sup>.

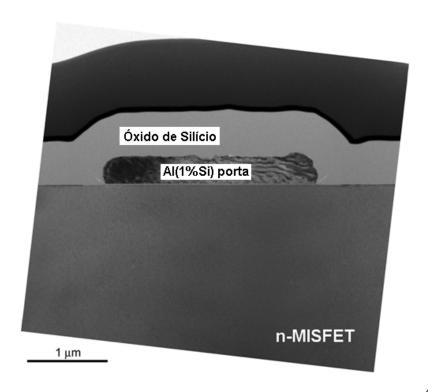

- Figura 4.32: Imagens TEM dos dispositivos n e p-MISFETs (*L*= 3μm) recozidos em densidade de energia de laser de 1000 mJ/cm². Al (metal de porta) continua presente e sem danos após o recozimento a laser. Uma incompleta recristalização pode ser verificada próxima ao empilhamento de porta (regiões marcadas).

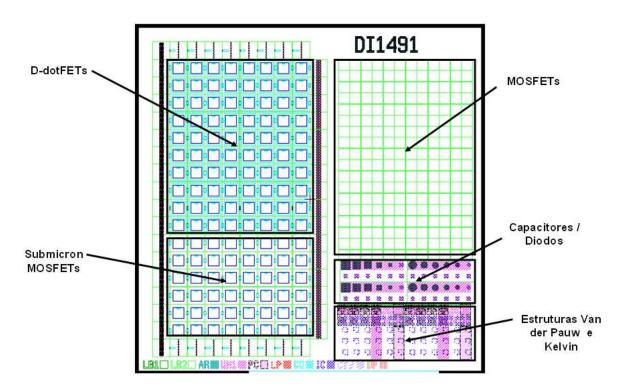

- Figura A1: Layout das máscaras projetadas para a fabricação dos dispositivos.

#### LISTA DE TABELAS

- Tabela 2.1: Parâmetros dos dispositivos CMOS citados no International Technology Roadmap for Semiconductors 2009 [22].

- Tabela 2.2: Propriedades de possíveis dielétricos de porta com alta constante dielétrica em substituição ao SiO<sub>2</sub> [29].

- Tabela 2.3: Vantagens e desvantagens dos reatores VPE, LPE, MBE e MOVPE.

- Tabela 3.1: Parâmetros e valores na deposição dos filmes de nitreto de silício.

- Tabela 3.2: Processo de limpeza da câmara do Reator e preparação da lâmina de Si.

- Tabela 3.3: Parâmetros para crescimento de silício germânio Reator Epitaxial CVD. [15].

- Tabela 3.4: Fluxo de processo detalhado para fabricação de n e p-MISFETs.

- Tabela 4.1: Medidas elipsométricas dos filmes de nitreto de silício depositados a diferentes parâmetros de processo.

- Tabela 4.2: Parâmetros para crescimento de silício germânio Reator Epitaxial CVD com pressão do processo de 5 Torr, fluxo de GeH<sub>4</sub> de 4 sccm e SiH<sub>4</sub> 20 sccm.

- Tabela 4.3: Parâmetros para crescimento de silício germânio Reator Epitaxial CVD com pressão do processo de 10 Torr, fluxo de GeH<sub>4</sub> de 8 sccm e SiH<sub>4</sub> 40 sccm.

- Tabela 4.4: Parâmetros extraídos pelas medidas C-V e I-V.

- Tabela 4.5: Resumo das implantações de arsênico em baixa energia. A média dos resultados de resistência de folha é apresentada.

- Tabela 4.6: Resumo das medidas e cálculos realizados em dispositivos MISFETs (média).

## LISTA DE SÍMBOLOS, SIGLAS E ABREVIATURAS

Al - Alumínio

Al<sub>2</sub>O<sub>3</sub> - Alumina

ALD - Atomic Layer Deposition

ALE - Atomic Layer Epitaxy

AlN - Nitreto de Alumínio

Ar - Argônio

BF<sub>2</sub> - Diflureto de Boro

BHF - Ácido Fluorídrico Tamponado

CI's - Circuitos Integrados

CMOS - Complementary Metal-Oxide-Semiconductor

C-V - Corrente versus Tensão

CVD - Chemical Vapor Deposition

DIBL - Drain Induced Barrier Lowering

Dimes - Delft Institute of Microsystems and Nanoelectronics

Dit - Interface Trap Level Density

ECR- CVD - Electron Cyclotron Resonance - Chemical Vapor Deposition

ELA – Excimer Laser Annealing

**EOT** - Equivalent Oxide Thickness

FIB - Focused Ion Beam

FTIR - Fourier Transform Infrared

FWHM - Full Width at Half Maximum

GaAs - Arseneto de Gálio

Ge - Germânio

GeH<sub>4</sub>- Germana

gm - Transcondutância

H - Hidrogênio

HBT - Heterojunction Bipolar Transistor

HCl - Ácido Clorídrico

HF - Ácido Fluorídrico

HfO2 - Dióxido de Háfnio

ICP - Inductively Coupled Plasma

I<sub>D</sub> - Corrente de Dreno

InGaAs – Arseneto de Gálio e Índio

Ion/Ioff - Taxa de Corrente

ITRS - International Technology Roadmap for Semiconductors

I-V - Corrente versus Tensão

KOH - Hidróxido de Potássio

L - Comprimento de Canal

LOCOS - Local Oxidation of Silicon

LPCVD - Low Pressure Chemical Vapor Deposition

LPE - Liquid Phase Epitaxy

MBE - Molecular Beam Epitaxy

MEMS - Micro Electro Mechanical Systems

MIS - Metal-Insulator-Semiconductor

MOCVD - Metal Organic Chemical Vapor Deposition

MOS - Metal - Oxide - Semiconductor

MOSFETs - Metal-Oxide Semiconductor Field Effect Transistors

MOVPE - Metal Organic Vapour Phase Epitaxy

NEMS - Nano Electro mechanical Systems

NF<sub>3</sub> - Trifluoreto de Nitrogênio

NH<sub>3</sub> - Amônia

N<sub>2</sub> - Nitrogênio

**OES - Optical Emission Spectroscopy**

PECVD - Plasma Enhancement Chemical Vapor Deposition

RF - Rádio Frequência

RIE - Reactive Ion Etching

RLC - Resistivo-Indutivo-Capacitivo

Rs - Resistência de Folha

RTA - Rapid Thermal Annealing

S - Inclinação da Curva do Transistor na Região Sublimiar

SEM - Scanning Electron Microscopy

SF<sub>6</sub> - Hexafluoreto de Enxofre

Si - Silício

Si<sub>3</sub>N<sub>4</sub> – Nitreto de Silício

SiCl<sub>2</sub>H<sub>2</sub> - Dicloro Silana

SiGe - Silício Germânio

SiH<sub>4</sub> - Silana

SIMS - Secondary Ion Mass Spectrometry

SiO<sub>2</sub> - Dióxido de Silício

SiON - Oxinitreto de Silício

SON - Silicon on Nothing

Si-Poli – Silício Policristalino

STI - Shallow Tranch Insulator

TEM - Transmission Electron Microscopy

TaN - Nitreto de Tântalo

TiN - Nitreto de Titânio

TiO<sub>2</sub> - Dióxido de Titânio

TMA -Trimetilalumínio

TUDelft - Delft University of Technology

UHV - Ultra-High-Vacuum

USJ - Ultra Shallow Junction

V<sub>DS</sub> - Tensão Dreno/Fonte

V<sub>G</sub> - Tensão de Porta

V<sub>GS</sub> - Tensão Porta/Fonte

**VPE** - Vapor-Phase Epitaxy

Vt - Tensão de Limiar

W - Largura de Canal

Xj - Profundidade de Junção

XRD - X-Ray Diffraction

η - Índice de Refração

λ - Comprimento de Onda

### **CAPÍTULO 1**

## INTRODUÇÃO

#### 1.1- Objetivos da tese

Os objetivos desta tese são desenvolver processos alternativos executados em sistemas de mais baixo custo (tais como, o custo de reatores *Low Pressure - Chemical Vapor Deposition* (LPCVD) quando comparado com o alto custo de reatores epitaxiais) ou em sistemas com *thermal budget* reduzidos para aplicação em micro e nanotecnologia sobre substratos de Si. São considerados processos com pacotes térmicos reduzidos aqueles que são executados em baixas temperaturas, menores que 400°C, ou em altas temperaturas, mas com tempo reduzido (menor que 1 minuto). Vale salientar que processos executados com pacotes térmicos reduzidos são primordiais para a continuação do escalamento da tecnologia *Complementary Metal-Oxide-Semiconductor* (CMOS) para atingir nós tecnológicos com dimensões sub-22 nm e para tornar a tecnologia *Micro Electrical-Mechanical System* (MEMS) em *Nano Electrical-Mechanical System* (NEMS). Estes processos são:

## 1) Deposição ECR-CVD em temperatura ambiente para obtenção de filmes de $Si_3N_4$ para aplicação em tecnologia MEMS.

Filmes de nitreto de silício (Si<sub>3</sub>N<sub>4</sub>) para aplicação em sistemas microeletromecânicos são normalmente depositados por LPCVD ou *Plasma Enhanced - CVD* (PECVD) em temperaturas maiores que 600°C e 250°C, respectivamente [1-3]. Para essa aplicação, esta tese apresenta a obtenção de filmes de nitreto de silicio em baixa temperatura, de 20°C, utilizando um reator de plasma do tipo *Electron Cyclotron Resonance – CVD* (ECR-CVD). As composições dos plasmas utilizados nas deposições dos filmes de Si<sub>3</sub>N<sub>4</sub> foram obtidas utilizando-se a espectroscopia por emissão óptica (*Optical Emission Spectroscopy* (OES)). A caracterização dos filmes de Si<sub>3</sub>N<sub>4</sub> foi obtida utilizando-se as seguintes técnicas: a

elipsometria, que determina a espessura, a uniformidade, a taxa de deposição/corrosão e o índice de refração dos filmes; a perfilometria, que determina a espessura, a uniformidade, a taxa de deposição e as taxas de corrosão em soluções de hidróxido de potássio (KOH) e de ácido fluorídrico (*buffered* HF (BHF)); e a espectroscopia no infravermelho por transformada de Fourier (*Fourier Transform Infrared* (FTIR)), que analisa as ligações químicas e a incorporação de hidrogênio. Para estudar a viabilidade destes filmes em tecnologia MEMS foram fabricadas estruturas suspensas de Si<sub>3</sub>N<sub>4</sub>, que foram analisadas pela técnica de microscopia eletrônica de varredura (*Scanning Electron Microscopy* (SEM)). Os resultados sobre as composições dos plasmas, as características físicas dos filmes e as estruturas suspensas fabricadas foram relacionados e permitem entender a dinâmica do processo de deposição ECR-CVD em temperatura de 20°C.

#### 2) Deposição de filmes de SiGe em sistema LPCVD vertical.

Normalmente, para o crescimento de filmes de silício germânio (SiGe) sobre substrato de Si utilizam-se reatores epitaxiais de alto custo e baixa produtividade. A proposta é desenvolver um processo simples de obtenção de camadas de SiGe em reator do tipo LPCVD vertical de baixo custo e de maior produtividade do que os reatores epitaxiais. Os filmes de SiGe obtidos foram caracterizados por difração de raio-x (X-Ray Diffraction (XRD)), que é uma técnica para a análise qualitativa e quantitativa dos materiais cristalinos. Estruturas formadas por SiGe/Si foram introduzidas em um sistema de feixes de elétrons, usado para microscopia SEM, e de íons de gálio focalizados (Focused Ion Beam (FIB)), usado para remover a camada de SiGe até alcançar o substrato de Si. Com a análise SEM, nesta região de camada removida, foi possível visualizar a interface entre o filme de SiGe e o substrato de Si, a espessura e a superfície do filme de SiGe. Para verificar a viabilidade destes filmes para aplicações em células solares e em regiões de fonte/dreno de transistores Metal-Oxide-Semiconductor (MOS), foram fabricados diodos de junções p<sup>+</sup> (de SiGe)/n (substrato de Si). Todos os diodos foram caracterizados eletricamente por medidas de corrente-tensão (I-V). Os resultados provenientes das análises de XRD, SEM e I-V foram relacionados para verificar a viabilidade do uso deste processo em tecnologia CMOS e de célula solar.

## 3) Deposição de filmes de Al<sub>2</sub>O<sub>3</sub> por camada atômica (ALD) e oxinitretação do Si por plasma ICP em baixa temperatura para aplicação como dielétrico de porta de dispositivos MOS.

A deposição por camada atômica (*Atomic Layer Deposition* (ALD)) vem sendo empregada para obtenção de filmes de óxido de alumínio (Al<sub>2</sub>O<sub>3</sub>) para aplicação como dielétrico de porta em tecnologia CMOS baseada em Si ou em dispositivos n-MOS baseada em arseneto de gálio e índio (InGaAs) [4-6]. A oxinitretação do Si por plasma *Inductive Coupled Plasma* (ICP), executada em baixa temperatura (250°C), para obtenção de filmes de oxinitreto de silício (SiON) para aplicação como dielétrico de porta de dispositivos MOS é um processo pouco estudado [7,8]. Neste contexto, esta tese apresenta um processo de deposição de filmes de Al<sub>2</sub>O<sub>3</sub> por ALD em temperatura ≤ 400°C e oxinitretação de Si por ICP que serão utilizados como dielétricos na fabricação de capacitores MOS. Os Capacitores fabricados foram caracterizados por medidas de capacitância-tensão (C-V), sendo extraídas as densidades de carga efetiva e de interface, a constante dielétrica, a espessura dos filmes e, por medidas de I-V, sendo extraída a corrente de fuga pelo dielétrico. A tensão de ruptura não foi analisada. Os resultados provenientes das análises C-V e I-V foram relacionados para verificar a viabilidade do uso deste processo em tecnologia CMOS.

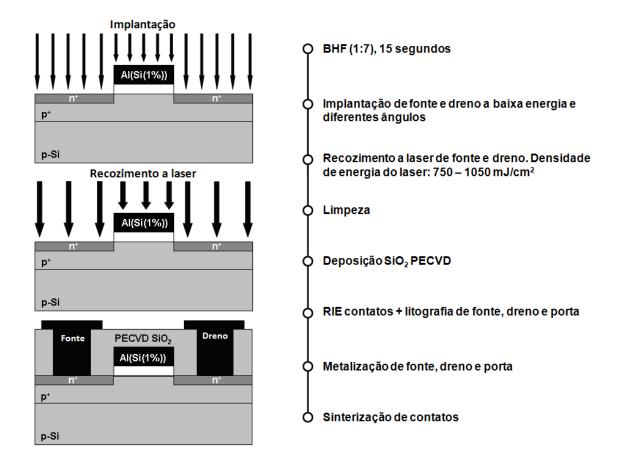

#### 4) Recozimento a laser para obtenção de junções rasas em diodos e transistores MOS.

Nos últimos anos, processos a laser estão sendo muito utilizados para a obtenção de junções ultra-rasas para tecnologias sub-45 nm CMOS e é uma técnica promissora na fabricação de dispositivos nanoeletrônicos em substituição aos atuais processos térmicos rápidos [9]. As junções obtidas com o recozimento a laser (*Excimer Laser Annealing* (ELA)) foram caracterizadas fisicamente utilizando *Secondary Ion Mass Spectrometry* (SIMS), para verificar a profundidade de junção e concentração de dopantes, e as imagens de *Scanning* (SEM) e *Transmission* (TEM) *Electron Microscopy*, para verificar a superfície e a estrutura cristalina das junções, respectivamente. Medidas I-V em diodos e transistores fabricados com estas junções foram extraídas, obtendo-se alguns importantes parâmetros elétricos, tais

como corrente de fuga e fator de idealidade. Os resultados provenientes das análises SIMS, SEM, TEM, C-V e I-V foram relacionados para verificar a viabilidade do uso deste processo em tecnologia CMOS.

#### 1.2 – Motivação para estudar os processos alternativos

Esta tese de doutorado teve início em 2005 com a continuação dos trabalhos desenvolvidos durante o Mestrado (Dissertação de Título "Obtenção e Caracterização de Filmes Finos de Óxido, Nitreto e Oxinitreto de Silício por Deposição ECR-CVD") na obtenção e caracterização de filmes de nitreto de silício utilizando reator ECR-CVD para aplicação em MEMS em substituição aos reatores normalmente utilizados para este tipo de aplicação como reatores do tipo LPCVD ou PECVD que utilizam temperaturas maiores que 600°C e 250°C, respectivamente. Além de filmes de nitreto de silício depositados por ECR-CVD, iniciou-se também a obtenção de filmes de silício germânio para fabricação de dispositivos microeletrônicos por LPCVD do tipo vertical. Normalmente, filmes de SiGe são crescidos por reatores epitaxiais de alto custo. No ano de 2007 os trabalhos foram continuados na Delft University of Technology (TUDelft) participando de um projeto da Comunidade Européia de nome "Disposable Dot Field Effect Transistor for High Speed Si Integrated Circuits", referido como o projeto D-DotFET. A participação neste projeto teve como objetivo desenvolver processos alternativos em baixa temperatura (≤ 400°C) na solicitação de aumentar a mobilidade de portadores no canal de transistores MOS utilizando silício tensionado por dots de silício germânio localizados logo abaixo da região do canal (Figura 1.1). O enorme sucesso dos dispositivos MOS utilizando silício tensionado e o grande interesse das indústrias em novas tecnologias realçam o desenvolvimento destes dispositivos em escala industrial. Assim, no primeiro ano do projeto D-DotFET em Delft, o trabalho foi concentrado no estabelecimento de um fluxograma compatível com a indústria microeletrônica. Este trabalho também recebeu o apoio da STMicroelectronics-França, colaborador ativo do projeto, onde o processo Silicon-on-Nothing (SON) foi inventado e continua em desenvolvimento, e de outras universidades da Comunidade Européia. O fluxograma do processo de fabricação do D-DotFET estão muito relacionados com os dipositivos SON fabricados na indústria. Este projeto necessitou o desenvolvimento de técnicas de processamento de circuitos integrados compatíveis com o projeto solicitado.

Como o desenvolvimento do projeto D-DotFET envolveu muitas etapas de fabricação e muitos equipamentos, neste caso muitas universidades foram envolvidas. Globalmente o trabalho foi dividido da seguinte forma:

- Forschungszentrum (FZ Jülich Alemanha): crescimento epitaxial dos *dots* de SiGe e silício (Si) tensionado por *Molecular Beam Epitaxy* (MBE) e *CVD*, e litografía por feixe de elétrons,

- Leibniz Institute for Solid State and Materials Research (IFW Dresden Alemanha): crescimento epitaxial dos *dots* de SiGe e Si tensionado por MBE e CVD,

- **Johannes Kepler University** (Linz Austria): crescimento epitaxial dos *dots* de SiGe e Si tensionado por MBE e CVD, e análise dos *dots* de SiGe,

- University of Milano (Bicocca Italia): modelamento teórico dos *dots* de SiGe e Si tensionado,

- Technical University Wien (Austria): Simulações do dispositivo,

- **STMicroelectronics** (Grenoble França): consultor tecnológico, experts em tecnologia SON,

- Delft University of Technology (Delft Institute of Microsystems and Nanoelectronics –

Dimes / Holanda): desenvolver fluxograma de processo, fabricação de máscaras (ver

Anexo A), fabricação do dispositivo, caracterização física dos materiais envolvidos no

processo e caracterização elétrica dos dispositivos fabricados.

Nesta tese serão apresentados os processos de fabricação MOS em baixa temperatura que levaram ao sucesso do desenvolvimento de transistors DotFETs. No desenvolvimento destes transistores, foram utilizados *dots* de silício germânio juntamente com silício tensionado (*strained silicon*) para se aumentar a mobilidade de portadores na região de canal. O *dot* pode ser removido em algum estágio do processamento para melhorar a dissipação térmica do dispositivo. O processo de fabricação, caracterização física e elétrica do dispositivo DotFET está publicado no livro " *DotFETs: MOSFETs Strained by a Single SiGe Dot in a Low-Temperature ELA*

*Technology*" – tese de doutorado apresentada na TUDelft-Holanda em Outubro de 2011. Uma lista de publicações esta apresentada no Anexo B.

Figura 1.1: Seção transversal do transistor D-DotFET com *dot* de SiGe utilizando "buraco semente" em substrato de silício. A região de porta é localizada sobre o *dot* de SiGe onde a tensão do filme de silício é alta. O *dot* pode ser removido em algum estágio do processamento.

### 1.3- Composição da Tese

Esta tese de doutorado foi dividida em cinco capítulos. A seguir apresenta-se uma descrição sumária dos capítulos que a compõe.

**O CAPÍTULO 1 - INTRODUÇÃO** apresenta os objetivos do trabalho e a motivação para o desenvolvimento de processos alternativos (ECR-CVD, LPCVD-vertical, ALD, oxinitretação do Si por plasma ICP e recozimento por ELA);

O CAPÍTULO 2 - PROCESSOS ALTERNATIVOS PARA MICRO e NANOTECNOLOGIA apresenta brevemente os sistemas microeletromecânicos, a utilização de filmes de nitreto de silício nestes sistemas depositados por plasma ECR-CVD em temperatura ambiente, necessidades futuras para o escalamento dos dispositivos CMOS e desempenho, dispositivos de silício-germânio para tecnologias futuras e método alternativo para obtenção de filmes de SiGe, materiais dielétricos de alta constante dielétrica (*high-k*), processos alternativos para obtenção de materiais dielétricos de *high-k*, métodos alternativos para obtenção de junções rasas, necessidade de junções rasas na região de fonte e dreno em transistores MOS;

O CAPÍTULO 3 - PROCEDIMENTO EXPERIMENTAL apresenta as condições de preparação da amostra e os parâmetros de processo para a obtenção dos filmes de nitreto de silício por ECR-CVD e silício-germânio por LPCVD, processo de fabricação de capacitores *Metal-Insulator-Semiconductor* (MIS) utilizando *Atomic Layer Deposition* e/ou *Inductively Coupled Plasma*, fabricação de diodos utilizando as técnicas de implantação iônica em baixa energia e recozimento a laser, caracterização física e elétrica, fabricação de transistores n-MOS e p-MOS utilizando processos em baixa temperatura (≤400°C). Na fabricação dos transistores MOS filmes de SiON crescidos por ICP foram utilizados como dielétricos de porta. Recozimento a laser foi utilizado para ativação de dopantes na região de fonte e dreno e obtenção junções rasas. Caracterizações físicas e elétricas foram realizadas;

O CAPÍTULO 4 - RESULTADOS EXPERIMENTAIS E DISCUSSÕES apresenta os resultados e discussões da caracterização dos filmes de nitreto e de silício-germânio. A caracterização de diodos, capacitores e transistores MIS utilizando os processos alternativos;

O CAPÍTULO 5 - CONCLUSÕES E PERSPECTIVAS FUTURAS apresenta as conclusões dos resultados de caracterização dos filmes e dispositivos fabricados por processos alternativos e as perspectivas futuras.

### **CAPÍTULO 2**

# PROCESSOS ALTERNATIVOS EM MICRO E NANOTECNOLOGIA

Neste capítulo serão apresentadas as tecnologias baseadas em micro e nanofabricação de sistemas microeletromecânicos, estruturas CMOS, dispositivos de SiGe, e os processos alternativos (ECR-CVD para deposição de SiN<sub>x</sub>, oxinitretação do Si por plasma ICP para obtenção do SiON, ALD para deposição de Al<sub>2</sub>O<sub>3</sub>, recozimento a laser para formação de junções rasas e LPCVD-vertical para obtenção de camadas de SiGe) empregados neste trabalho para o desenvolvimento destas tecnologias.

## 2.1- O processo de deposição por ECR-CVD de $SiN_x$ para aplicação em sistemas microeletromecânicos

Esta parte da tese trata do processo alternativo ECR-CVD para a obtenção de nitreto de silício, que será usado para a fabricação de microestruturas suspensas, que são à base da tecnologia de MEMS. Assim, nos três próximos sub-itens serão introduzidos os temas sobre os sistemas microeletromecânicos, os filmes de SiN<sub>x</sub> e o sistema ECR-CVD.

### 2.1.1 - Sistemas microeletromecânicos [1,2-4]

O crescente interesse de pesquisadores e indústrias sobre os microsistemas integrados, nesses últimos anos, tem sido justificado pelos inúmeros dispositivos e aplicações potenciais nas mais diversas áreas emergentes das telecomunicações, automobilística, médica, biomédica, entre outras. O desenvolvimento de técnicas de fabricação de microestruturas suspensas tem motivado a construção de novos sensores e atuadores miniaturizados, fabricados sobre lâminas de Si. O avanço nos processos de fabricação de CI's permite hoje a construção de microestruturas mecânicas (suspensas), móveis ou não, que podem ser exploradas como sensores e/ou atuadores em sistemas miniaturizados. Certamente inúmeras são as áreas de interesse e aplicações

potenciais para estas microestruturas, então, o principal esforço mundial hoje está na miniaturização e na integração dos sensores e atuadores, uma vez que o desenvolvimento dos circuitos eletrônicos, tanto digitais quanto analógicos, apresenta-se bastante avançados.

O microsistema final pode ser implementado de forma híbrida ou monolítica. Híbrida quando este é composto por mais de um chip, geralmente quando a eletrônica é separada das estruturas microusinadas (mecânicas). Monolítica no caso da integração do sistema completo dentro de um único chip. É geralmente preferencial a implementação de forma monolítica devido à redução dos problemas de interface entre os chips (confiabilidade e desempenho) e aumento do rendimento de fabricação em grande escala de produção. Podemos definir essas microestruturas como sendo sistemas microeletromecânicos.

Assim como ocorre nos Circuitos Integrados (CI's), o silício é o material mais usado para a construção dos microsistemas integrados principalmente pelo seu custo e pelo avançado estado de desenvolvimento das tecnologias disponíveis. O grande desafio consiste em fabricar microsensores e microatuadores sobre um substrato antes utilizado apenas para a construção de componentes eletrônicos (transistores, diodos, resistores, capacitores). Estes dispositivos têm sido construídos principalmente através do uso de microestruturas suspensas ou microusinadas. As estruturas comumente encontradas são pontes, vigas e membranas, embora outras geometrias podem também ser realizadas para as mais diversas aplicações.

Podemos dividir as técnicas de fabricação de microestruturas em dois grandes grupos: processos específicos para microsistemas e processos compatíveis com a microeletrônica. Os processos específicos para a construção de microsistemas geralmente comprometem a integração da eletrônica e, por consequência, apenas microssistemas híbridos podem ser realizadas. As técnicas compatíveis com os processos de fabricação de circuitos integrados (microeletrônica), por sua vez, poderiam ainda ser classificadas segundo as regiões ou camadas que são removidas (corroídas) para a liberação das estruturas suspensas:

- remoção do substrato pela face inferir ou posterior (back-side bulk micromachining);

- remoção do substrato pela face superir ou anterior (front-side bulk micromachining);

- remoção de camadas sacrificiais da superfície do substrato (surface micromachining).

A construção de tais estruturas é geralmente feita após a fabricação dos circuitos eletrônicos devido à complexidade dos processos de microeletrônica, enquanto que muitas vezes uma simples etapa de corrosão é suficiente para a liberação das estruturas suspensas.

Microestruturas suspensas são facilmente construídas a partir da corrosão da face anterior e/ou posterior do substrato (micro-usinagem em volume), front e back-side etching, respectivamente. As diferenças entre essas duas técnicas de micro-usinagem são bastante acentuadas tanto no processo de fabricação quanto no tipo de estrutura desejada. No caso da usinagem pela face anterior, a suspensão da estrutura deve-se principalmente ao processo de corrosão lateral (under-etching). A usinagem pela face posterior do substrato, por sua vez, é bastante utilizada para a realização de membranas. O objetivo principal é a realização de uma corrosão profunda e praticamente sem corrosão lateral significativa. A usinagem de superfície refere-se exatamente aos processos de construção de microestruturas suspensas a partir da remoção ou corrosão de camadas presentes na superfície do substrato.

As soluções químicas utilizadas na corrosão do substrato podem ser tanto úmidas (líquidas) quanto secas (gases, plasma). As soluções úmidas têm sido preferidas por sua simplicidade e facilidade de aplicação. Características importantes da corrosão úmida são a sua anisotropia, quando às direções de ataque do material são preferenciais segundo a disposição de seus planos cristalográficos, e a seletividade do ataque entre diferentes materiais. Os três tipos de técnicas apresentadas (*back-side bulk micromachining*, *front-side bulk micromachining e surface micromachining*), são compatíveis com os processos de fabricação de circuitos integrados.

#### 2.1.2- Nitreto de silício

O nitreto de silício é geralmente usado na fabricação de microcircuitos e de microsensores. Este material passiva circuitos eletrônicos CMOS, pois funciona como barreira de difusão de íons móveis, particularmente de Na<sup>+</sup> (íons de sódio). Possui alta seletividade (maior que 2) em relação ao Si e ao dióxido de silício (SiO<sub>2</sub>), funcionando como camada protetora (máscara) em processos de corrosão úmida. Nos processos de oxidação local (*Local Oxidation of Silicon* (LOCOS), barra a oxidação do Si sobre regiões ativas durante a fabricação dos dispositivos MOS, pois é um material que não oxida. Outras aplicações do nitreto de silício são: guias de onda óptica, isolante de porta MOS, máscara em processos de implantação de íons e

barreira contra a perda do arsênio de substratos de arseneto de gálio (GaAs) durante etapas de recozimento [5,6].

Podem-se obter filmes de Si<sub>3</sub>N<sub>4</sub> por técnicas de deposição química a partir da fase vapor, que é um processo pelo qual os gases ou vapores reagem quimicamente, levando à formação de uma camada sólida sobre o substrato. Normalmente, na formação do Si<sub>3</sub>N<sub>4</sub>, utilizam-se as seguintes misturas gasosas com as suas respectivas reações químicas [5,7]:

Diclorosilana + Amônia =

$$3SiCl_2H_2 + 4NH_3 \rightarrow SiN_x + 6HCl + 6H_2$$

Silana + Amônia =  $SiH_4 + 4NH_3 \rightarrow SiN_x + 12H_2$  ou  $Si_x N_y H_z + H_2$

Esta técnica incorpora hidrogênio (H) nos filmes depositados. Quanto maior a concentração de H, menor a densidade. Menor densidade, maior porosidade, maiores taxas de corrosão em soluções de hidróxido de potássio e de ácido fluorídrico (HF). Esta incorporação é proveniente dos gases amônia (NH<sub>3</sub>), silana (SiH<sub>4</sub>) e diclorosilana (SiCl<sub>2</sub>H<sub>2</sub>). Para reduzir essa quantidade de hidrogênio incorporado utiliza-se nitrogênio em substituição da amônia, em processos auxiliados por plasmas de alta densidade [8]. O nitreto nestas condições é formado pela reação química abaixo [1]:

Silana + Nitrogênio =

$$SiH_4 + 2N_2 \rightarrow SiN_x + 6H_2$$

A composição do filme de nitreto pode ser controlada variando-se alguns parâmetros de deposição, tais como os fluxos de gases, pressão e temperatura. O índice de refração e a constante dielétrica relativa dos filmes podem variar entre 1,8 e 2,5 e de 6 a 9, respectivamente, dependendo da sua composição. Obtêm-se densidades entre 2,4 e 3,2 g/cm³ [5,7]. A taxa de corrosão dos filmes de SiN<sub>x</sub> depositados por processo LPCVD está entre 0,5 e 1nm/minuto A taxa de corrosão para esses filmes em solução de KOH é muito baixa, menor que 0,5 nm/minuto [9,10].

### 2.1.3- ECR-CVD [1,11,12,13-19]

Um importante desenvolvimento em processamentos por plasma de alta densidade e de baixa pressão é a descarga de ressonância ciclotrônica de elétrons. Este tipo de plasma é produzido através de uma excitação por microondas (2,54 GHz) gerada por um mágnetron e injetada na câmara do ECR através de um guia de onda (ver Figura 2.1), e um campo magnético aplicado através de bobinas magnéticas (875 Gauss). Os elétrons do plasma giram em volta de linhas de campo magnético em trajetórias helicoidais e com frequência que depende da velocidade do campo. Em condições de ressonância entre a frequência de giro e a frequência de microondas incidente, os elétrons absorvem energia criando um plasma de alta densidade. Fora da zona de campo magnético uniforme, a interação da microonda com o plasma é relativamente fraca. Os elétrons produzidos na zona de plasma denso se difundem ao longo das linhas de campo magnético (indo para a área inferior onde se localiza a câmara de processo) mais rápido que os íons, criando um campo elétrico que promove sua extração. A condição de ressonância resulta em um plasma intenso de alta densidade, que pode ser mantido em baixa pressão geralmente entre  $10^{-5}$  e  $10^{-2}$  Torr.

O sistema ECR com plasma remoto reduz o bombardeamento da amostra por íons com alta energia (os íons são extraídos da região de plasma por um campo levemente divergente e difundem até a amostra), minimizando a quantidade de defeitos produzidos nas superfícies do substrato semicondutor por radiação, produz alta densidade de espécies reativas, permite taxas de deposição maiores que 10 nm/minuto e possibilita a deposição de filmes até em temperatura ambiente. Além disso, se o sistema ECR estiver equipado com uma fonte de rádio frequência (RF) (frequência de 13,56 MHz) acoplada ao porta-amostra, onde se localiza o substrato, pode-se controlar a energia de bombardeamento da amostra por íons provenientes da região do plasma. A potência de RF é diretamente proporcional ao bombardeamento iônico.

O equipamento ECR permite combinar processos de deposição ou corrosão, e permite também operar com pressões mais baixas do que as utilizadas em processos de plasma convencionais. Os parâmetros de processo que influenciam nas propriedades físicas e na composição química dos filmes são os gases reagentes, a temperatura do substrato, a pressão e os fluxos dos gases, as potências de microondas e de RF, o tempo de deposição, e outros fatores como a limpeza das paredes da câmara, que podem gerar impurezas que se incorporam na

estrutura do filme, degradando a sua qualidade. Normalmente, antes das deposições, executam-se etapas sequenciais de limpeza in-situ com plasmas de gases reativos, como o hexafluoreto de enxofre (SF<sub>6</sub>), trifluoreto de nitrogênio (NF<sub>3</sub>) e o hidrogênio, que remove as camadas depositadas nas paredes das câmaras, e de argônio (Ar), que remove o resíduo. Este sistema foi utilizado para obtenção de filmes de SiN<sub>x</sub> em temperatura ambiente para aplicação em dispositivos MEMS.

Figura 2.1: Diagrama esquemático do sistema ECR.

## 2.2- Os processos alternativos para a obtenção de dielétricos high-k de $Al_2O_3$ e SiON e de junçãos rasas para o desenvolvimento da tecnologia CMOS

Esta parte da tese trata dos processos alternativos (ALD, ICP e ELA, respectivamente) para a obtenção de dielétricos *high-k* de Al<sub>2</sub>O<sub>3</sub> e SiON e de junçãos rasas para o desenvolvimento da tecnologia CMOS. Assim, nos próximos sub-itens serão introduzidos os temas sobre a tecnologia CMOS, dielétricos *high-k*, filmes *high-k* de SiON e de Al<sub>2</sub>O<sub>3</sub>, processos alternativos

(ICP e ALD) para obtenção de SiON e de Al<sub>2</sub>O<sub>3</sub>, a necessidade das junções rasas e o recozimento a laser para obtenção destas junções.

## 2.2.1 – O escalamento da tecnologia CMOS e a necessidade de novos materiais e de processos de fabricação

A estrutura básica dos tradicionais disposivos *Metal-Oxide-Semiconductor Field Effect Transistor* (MOSFETs): n-MOSFET e p-MOSFET é dada na Figura 2.2. Em ambos, p- e n-MOSFETs em um circuito complementar é demontrado na Figura 2.3 [20]. A tecnologia CMOS é uma tecnologia usada para uma ampla variedade de circuitos analógicos e digitais. *Shallow Trench Isolation* (STI) é geralmente utilizado em uma nova tecnologia CMOS de processamento para isolar os dispositivos em substituição à oxidação local. A Figura 2.3 apresenta a seção transversal da tecnologia CMOS em que os dispositivos p- e n-MOS são fabricados sobre o mesmo substrato.

Figure 2.2: Seção transversal de um dispositivo (a) n-MOSFET e (a) p-MOSFET.

Figure 2.3: Seção transversal de um dispositivo utilizando tecnologia CMOS onde MOS de canal p e canal n são fabricados em um mesmo substrato. Técnica de *Shallow Trench Insulation* é utilizada em atuais processos CMOS, isolando os dispositivos.

Figura 2.4: A evolução dos processadores Intel<sup>®</sup> e a tecnologia associada exemplificando a lei de Moore [21].

Tabela 2.1: Parâmetros dos dispositivos CMOS citados no *International Technology Roadmap* for Semiconductors 2009 [22].

| Ano de Produção                    | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 |

|------------------------------------|------|------|------|------|------|------|------|

| Comprimento de porta físico (nm)   | 27   | 24   | 22   | 20   | 18   | 17   | 15   |

| Equivalent Oxide Thickness         | 1    | 0.95 | 0.88 | 0.75 | 0.65 | 0.55 | 0.53 |

| (EOT) físico (nm)                  |      |      |      |      |      |      |      |

| Junção de contato - <i>Xj</i> (nm) | 35.2 | 32   | 29   | 26.7 | 24.7 | 22   | 19.8 |

| Extensão de dreno - <i>Xj</i> (nm) | 13   | 12   | 10.5 | 10   | 9.5  | 8.7  | 8    |

O *International Technology Roadmap for Semiconductors* (ITRS), desenvolvido pela indústria de semicondutores, reflete claramente o forte desejo de que a indústria continue o escalamento dos dispositivos CMOS no futuro de acordo com a Lei de Moore, que em 1965 previu que o número de transistores em um chip dobraria a cada dois anos [23]. Esta tendência é vista na Figura 2.4, que exibe a evolução para os processadores Intel® e a tecnologia associada.

Até hoje, o escalamento dos dispositivos ainda é a forma mais importante para atingir um melhor desempenho, devido as dificuldades tecnológicas está se tornando extremamente desafiador. Por exemplo, a ITRS de 2009 previa um comprimento de canal de 15 nm em 2015 e profundidade de junção (*Xj*) de 19,8 nm, conforme demonstrado na Tabela 2.1. No entanto, para satisfazer as especificações do ITRS e continuar o escalamento dos dispositivos CMOS, fica evidente que novos materiais e novas tecnologias devem ser introduzidas, como mostra a Figura 2.5 [24]. Para o escalamento dos dispositivos MOSFET em dimensões nanométrica (sub-45 nm), novos conceitos e novos materiais precisam ser considerados:

- o dióxido de silício tem sido utilizado há décadas como dielétrico de porta, mas para dielétricos finos de SiO<sub>2</sub> (< 2 nm) a corrente de tunelamento se torna excessiva (> 1 mA). Neste caso, novos materiais precisam ser estudados com as seguintes características: alta constante dielétrica, interfaces de boa qualidade com o Si, alta estabilidade térmica e química, a fim de manter o escalamento e evitar o efeito de tunelamento. Oxinitreto de silício demonstrou que consegue a redução da corrente de fuga, e supressão de segregação de boro [25-28], e foi usado nos nós tecnológicos de 90 nm e 65 nm. Um dielétrico de porta com maior constante dielétrica (superior ao valor de 3,9 do SiO<sub>2</sub>), tais como o dióxido de háfnio (HfO<sub>2</sub>) que tem uma constante dielétrica

de 25 (Tabela 2.2), pode com esta característica reduzir o efeito da corrente de fuga por tunelamento em até quatro ordens de grandeza. A Tabela 2.2 fornece uma lista de dielétricos de porta em substituição ao SiO<sub>2</sub> e suas propriedades relevantes. Os nós tecnológicos atuais de 32 nm e 45 nm e o futuro 22 nm usam como dielétrico de porta o óxido de háfnio. Nesta tese, as técnicas alternativas ALD e ICP de obtenção de dielétricos de porta de Al<sub>2</sub>O<sub>3</sub> e de SiON, respectivamente, foram usadas neste trabalho.

- junções rasas são obrigatórias para as extensões de fonte e dreno, a fim de suprimir efeitos de canal curto. Neste trabalho, a técnica de recozimento a laser dos íons implantados é empregada e estudada para a formação de junções ultra rasas (*Ultra-Shallow Junctions* (USJ));

- redução de dissipação de potência;

- desenvolvimento do processo de litografía.

Tabela 2.2: Propriedades de possíveis dielétricos de porta com alta constante dielétrica em substituição ao SiO<sub>2</sub> [29].

| Material                       | Constante Dielétrica (k) | Band gap E <sub>G</sub> (eV) | Banda de Condução offset ( $\Delta Ec$ ) (eV) |

|--------------------------------|--------------------------|------------------------------|-----------------------------------------------|

| SiO <sub>2</sub>               | 3.9                      | 8.9                          | 3.2                                           |

| SiNx                           | 7.0                      | 5.1                          | 2                                             |

| $Al_2O_3$                      | 9.0                      | 8.7                          | 2.8                                           |

| HfO <sub>2</sub>               | 25                       | 5.7                          | 1.5                                           |

| ZrO <sub>2</sub>               | 25                       | 7.8                          | 1.4                                           |

| La <sub>2</sub> O <sub>3</sub> | 30                       | 4.3                          | 2.3                                           |

| $Ta_2O_5$                      | 26                       | 4.5                          | 1-1.5                                         |

Onde:  $E_G$  é a variação de energia entre os níveis de energia dos extremos mínimo da banda de condução e máximo da banda de valência (denominado band gap) e  $\Delta Ec$  é a variação de energia entre os níveis de energia dos extremos mínimos das bandas de condução do dielétrico e do semicondutor (denominado de *offset conduction bands*).

Como mostra a Figura 2.5, novos materiais e tecnologias de processamento de circuitos integrados estão sendo cada vez mais estudadas no intuito de continuar o escalamento e aumento

de desempenho dos dispositivos MOSFET. Novos materiais como dielétricos de porta MOS com alta constante dielétrica (Tabela 2.2), eletrodos metálicos de nitreto de tântalo (TaN) ou de nitreto de titânio (TiN) de porta MOS, dielétricos entre níveis metálicos com baixa constante dielétrica (filmes de SiO<sub>2</sub> com incorporação de fluor e/ou carbono) [30] e também novos substratos têm sido utilizados, a fim de melhorar o desempenho dos circuitos. Durante os últimos anos, para aumentar a mobilidade de portadores (elétrons ou lacunas) nos transistores MOS, vem sendo usado o silício tensionado na região do canal. Atualmente estão sendo estudados também substratos semicondutores alternativose, tais como Ge e InGaAs, em substituição aos de Si, por apresentarem mais altas mobilidades de lacunas e elétrons.

Figura 2.5: Desafios para tecnologia planar de dispositivos MOSFET [24].

#### 2.2.2- Materiais dielétricos High-k utilizados neste trabalho

### **2.2.2.1- Oxinitreto de silício [31-34]**

O melhor isolante para a microeletrônica que se pode obter é o díóxido de silício por ser composto natural do silício, por ser um ótimo dielétrico de porta em transistores MOS, por ser uma eficiente barreira de difusão de impurezas e por apresentar excelentes características de interface, o que permitiu o desenvolvimento da tecnologia planar e o rápido aumento da escala de integração. Os filmes de oxinitreto de silício são filmes que podem ser obtidos com características entre nitreto e dióxido de silício, dependendo da concentração de nitrogênio e oxigênio no filme. Podem-se obter diferentes composições de SiON. As mesmas técnicas de obtenção do dióxido e nitreto de silicio são usadas para o oxinitreto. Portanto, é um material compatível com os processos de micro e nanofabricação. A variação química durante o processo de obtenção dos filmes de SiON produz mudanças em suas propriedades elétricas (constante e ruptura dielétricas), mecânicas (estresse e porosidade) e ópticas (indice de refração - η). Por exemplo, controlando-se a concentração de nitrogênio e oxigênio nos filmes de SiON, pode-se obter um índice de refração variável, entre 1,46 (índice de refração dos filmes de SiO<sub>2</sub>) e 2,0 (índice de refração dos filmes de nitreto de silício e constantes dielétricas variando entre 3,9 e 7, aproximadamente, o dobro da constante elétrica do SiO<sub>2</sub>. Por esses motivos os filmes de SiON substituiram os filmes de SiO<sub>2</sub> como dielétrico de porta nos recentes nós tecnológicos de 65 nm e 90 nm [35,36]. Atualmente, o dióxido de háfnio vem sendo usado como material de alta constante dielétrica em substituição dos filmes de SiO<sub>2</sub>. Entretanto, os filmes de SiON vêm sendo usados como camada interfacial entre o dielétrico de HfO<sub>2</sub> e o semicondutor de Si nas portas de MOSFETs, pois apresentam menos defeitos do que os filmes de HfO<sub>2</sub> diretamente depositados sobre Si. E nesta tese, os filmes de SiON, usados como dielétricos de porta, foram obtidos pela técnica alternativa de oxinitretação do Si por plasma ICP.

### 2.2.2. Óxido de alumínio

Muitas pesquisas vêm sendo realizadas tanto na indústria de semicondutores como na área acadêmica para encontrar materiais com alta constante dielétrica e que sejam compatíveis com os processos de micro e nanofabricação para substituir os filmes de SiO<sub>2</sub> [37-42]. O Al<sub>2</sub>O<sub>3</sub>, também chamado de alumina, vem sendo estudado [43,44] para esta aplicação devido a sua alta constante dielétrica (Tabela 2.2) e outras propriedades, tais como a baixa permeabilidade de íons alcalinos e outras impurezas, resistência às altas intensidades de radiações ionizantes e alta condutividade térmica. O óxido de alumínio possui (veja a Tabela 2.2): valor de *bang gap* (E<sub>G</sub>) similar ao do óxido de silício e constante dielétrica com valor maior que duas vezes a do SiO<sub>2</sub>. Como descrito anteriormente, outros materias como o HfO<sub>2</sub> também esta sendo muito pesquisado como material de alta constante dielétrica em substituição dos filmes de SiO<sub>2</sub> [45-47]. Vale salientar que estes dispositivos são fabricados em substratos de Si. Para dispositivos MOSFETs fabricados em substratos semicondutores de mais altas mobilidades de lacunas e elétrons, como os de Ge e de InGaAs, respectivamente, que substituirão o Si nas próximas tecnologias sub-22 nm, o Al<sub>2</sub>O<sub>3</sub> vem sendo o dielétrico mais compatível, com menos defeitos de interface do que o HfO<sub>2</sub>. Neste trabalho o Al<sub>2</sub>O<sub>3</sub> é obtido por processo ALD, como será visto posteriormente.

### 2.2.3- Métodos alternativos (ALD e ICP) para obtenção de dielétricos *High-k* utilizados neste trabalho

Com a necessidade de substituição de SiO<sub>2</sub> por outros dielétricos, como o Al<sub>2</sub>O<sub>3</sub> e o SiON, nas gerações futuras dos dispositivos CMOS, também serão necessários novos métodos, tais como o ALD e a oxinitretação por plasma ICP, respectivamente, para a deposição ou crescimento desses filmes. Métodos similares a estes são usados, tais como:

- Excelente qualidade de filmes de SiON crescidos por oxinitretação por plasma ECR em baixa temperatura (20°C) vêm sendo usados como dielétricos de porta em capacitores MOS [35,36];

-Para os filmes de Al<sub>2</sub>O<sub>3</sub> diferentes métodos têm sido utilizados para o crescimento, dentre eles podemos citar o MBE, CVD, deposição química a vapor a partir de metal-orgânico

(*Metal Organic Chemical Vapor Deposition* (MOCVD)) e principalmente a técnica de ALD ou também chamada de epitaxia de camada atômica (*Atomic Layer Epitaxy* (ALE)) [48].

Nos próximos sub-itens serão apresentados os métodos ALD e ICP usados neste trabalho.

#### 2.2.3.1- Deposição filmes por camada atômica

Esse método de deposição de filmes finos foi criado por Tuomo Suntola em 1974 na Finlândia [49]. A vantagem de utilizar a técnica ALD sobre as outras técnicas de deposição de filmes finos são [50-53]:

- filmes livres de *pin-holes* (pequenos buracos);

- excelente uniformidade e conformação;

- excelente repetibilidade;

- exelente cobertura de degrau;

- possível deposição em baixa temperatura (<300°C);

- controle da composição e estequiometria dos filmes depositados.

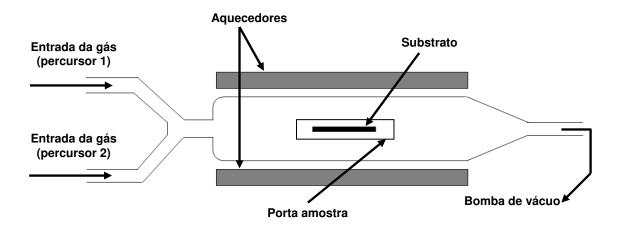

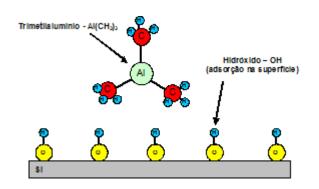

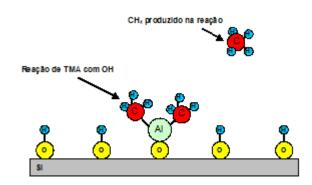

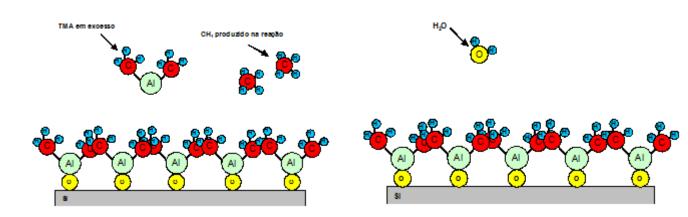

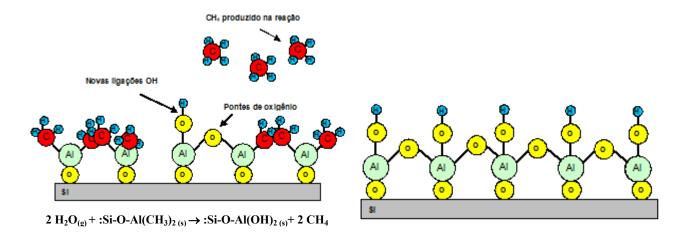

Nessa técnica as reações químicas acontecem na superfície do substrato, utilizando precursores na fase gasosa, e depositando filmes ultra-finos. Esses precursores reagem com a superfície da lâmina, um de cada vez, sequencialmente. Como exemplo, vamos explicar a deposição de Al<sub>2</sub>O<sub>3</sub> em lâminas de silício. Para esse tipo de filme que queremos obter, precisamos de gases precursores de alumínio (Al) e de oxigênio. O precursor fonte de alumínio é o trimetilalumínio (TMA) e a fonte de oxigênio é o vapor de água. O esquemático do reator ALD utilizado nesse trabalho pode ser visto na Figura 2.6.

Figura 2.6: Diagrama esquemático do sistema ALD.

As reações, nesse tipo de equipamento, ocorrem de forma cíclica em que se pode considerar um único ciclo sendo:

- a- exposição do substrato ao primeiro precursor;

- b- purga com nitrogênio;

- c- exposição do substrato ao segundo precursor;

- d- purga com nitrogênio.

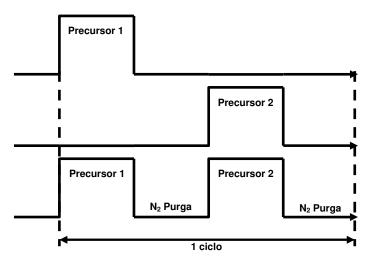

A Figura 2.7 apresenta um ciclo de deposição.

Figura 2.7: Esquemático de um ciclo de deposição.

Após completar este ciclo de quatro passos um novo cíclo é iniciado. A espessura do filme depositado depende da quantidade de ciclos utilizada. Dependendo dos parâmetros utilizados durante o crescimento das camadas atômicas é possivel obter filmes de espessura menores de 0,9nm. A Figura 2.8 apresenta as reações químicas envolvidas em um ciclo de deposição de filme de óxido de alumínio em substrato de silício.

$Al(CH_3)_{3(g)} + :Si-O-H_{(s)} \rightarrow :Si-O-Al(CH_3)_{2(s)} + CH_4$

- (a) Adsorção de vapor de água na superfície da (b) TMA reage com OH produzindo CH<sub>4</sub>. lâmina de Si e primeiro pulso do primeiro precursor (TMA) na câmara de reação.

- (c) TMA não reage com ela mesma apenas com (d) Primeiro pulso do segundo precursor (H<sub>2</sub>O). as ligações OH, TMA em excesso e CH4 são bombeados para fora da câmara de reação.