Dep. de Eng. de Computação e Automação Industrial Faculdade de Engenharia Elétrica e Computação, Universidade Estadual de Campinas.

# CO-PROCESSADOR PARA ALGORITMOS DE CRIPTOGRAFIA ASSIMÉTRICA

Autor: Maurício Araújo Dias

Orientador: Prof. Dr. José Raimundo de Oliveira

### Banca:

Prof. Dr. José Raimundo de Oliveira - Presidente

Profa. Dra. Alice M. H. Tokarnia

Prof. Dr. Marco Aurélio Amaral Henriques

Prof. Dr. Ricardo Dahab

Dissertação apresentada como requisito parcial à obtenção do grau de Mestre em Engenharia Elétrica.

Campinas, fevereiro de 2002

U N I C A M P BIBLIOTECA CENTRAL SEÇÃO CIRCULANTE

| INIDADE (T) E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O CHAMADA TIVNICAMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D5430                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CX COMMON CONTRACTOR C |

| DM80 BC/ 51071                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ROC 16.837/02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DΧ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RECO PRS 11,00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ATA 28/09/02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1 CPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

CMO0174443-5

1B 1D 259179

### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

D543c

Dias, Maurício Araújo

Co-processador para algoritmos de criptografia assimétrica / Maurício Araújo Dias.--Campinas, SP: [s.n.], 2002.

Orientador: José Raimundo de Oliveira. Dissertação (mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Criptografia. 2. Criptografia de dados (Computação). 3. Curvas elípticas. 4. Hardware. 5. Circuitos integrados. 6.VHDL (Linguagem descritiva de hardware). 1. Oliveira, José Raimundo de. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

### Resumo

Este trabalho tem como objetivo o desenvolvimento de um co-processador para algoritmos de criptografía assimétrica. Trata-se de um co-processador que pode servir de base para a implementação de algoritmos de criptografía assimétrica, não apenas de um dispositivo dedicado a um único algoritmo criptográfico. Para tanto, ele dispõe de uma biblioteca de módulos de circuitos que implementam rotinas básicas úteis a vários desses algoritmos. A implementação é feita em um dispositivo do tipo FPGA. Para testar o funcionamento do co-processador foi escolhido o algoritmo de criptografía assimétrica, baseado no problema do logaritmo discreto sobre curvas elípticas. Os testes práticos do co-processador apóiam-se no uso de curvas elípticas distintas e de diferentes pontos pertencentes a cada uma dessas mesmas curvas.

### **Abstract**

This work has as main objective the development of a co-processor for asymmetric cryptography algorithms. It is a co-processor that can serve for the implementation of asymmetric cryptography algorithms. It isn't a device dedicated to only a cryptographic algorithm. So, it uses a library of *hardware* modules that implement basic routines useful to several of these algorithms. The implementation is made in a FPGA device. In order to test the operation of this co-processor, we choose the asymmetric cryptography algorithm based on the elliptic curve discrete logarithm problem. The practical tests of the co-processor are based on the use of distinct elliptical curves and different points over these same curves.

| · |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# Índice

| Abstract                                                                                | iii |

|-----------------------------------------------------------------------------------------|-----|

| Glossário                                                                               | vi  |

| Capítulo 1 Introdução                                                                   | 1   |

| 1.1 M1 – Um co-processador para algoritmos de criptografía assimétrica                  | 1   |

| 1.2 Considerações iniciais                                                              | 1   |

| 1.3 Exemplos de trabalhos relacionados.                                                 | 4   |

| 1.3.1 Sistema criptográfico baseado em curvas elípticas em DSP                          | 5   |

| 1.3.2 Sistemas criptográficos baseados em curvas elípticas para <i>smart cards</i>      | 6   |

| 1.3.3 Co-processador criptográfico baseado em curvas elípticas sobre F(2 <sup>m</sup> ) | 7   |

| 1.3.4 Processador de alta performance para sistemas criptográficos baseados es          |     |

| curvas elípticas sobre GF(2 <sup>m</sup> )                                              | 8   |

| 1.4 Organização deste Trabalho                                                          | 10  |

| Capítulo 2 O Co-processador Criptográfico M1                                            | 13  |

| 2.1 Ponto de Partida do Trabalho                                                        | 13  |

| 2.2 M1: Um Co-processador Voltado para Algoritmos de Criptografia Assimétrica           | 13  |

| 2.3 Características do Projeto do Co-processador M1                                     |     |

| 2.4 Custos do Projeto em Relação a ASICs                                                | 15  |

| 2.5 Aplicação do Co-processador M1                                                      | 16  |

| 2.6 Comentários                                                                         | 17  |

| Capítulo 3 A Estrutura Interna do M1                                                    |     |

| 3.1 Visão Geral da Estrutura Interna do Co-processador M1                               | 19  |

| 3.2 Unidade de Controle                                                                 |     |

| 3.3 PSW (Program Status Word)                                                           | 24  |

| 3.4 Registradores                                                                       | 26  |

| 3.5 Unidade Lógico-Aritmética                                                           | 28  |

| 3.6 Contadores                                                                          | 34  |

| 3.7 Registrador Acumulador                                                              | 36  |

| 3.8 Registrador Temporário                                                              | 39  |

| 3.9 Comentários                                                                         | 39  |

| Capítulo 4 Dispositivo Usado para a Implementação do Co-processador M1: FPGA            | 41  |

| 4.1 A Família APEX 20K                                                                  | 41  |

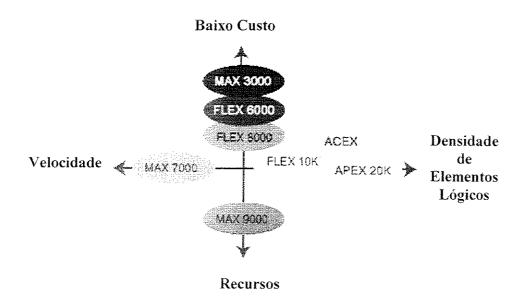

| 4.2 Outras famílias de dispositivos FPGAs da Altera                                     | 42  |

| 4.3 Comentários                                                                         | 45  |

| Capítulo 5 Implementação de um Algoritmo de Criptografia Assimétrica no Co-             |     |

| processador M1                                                                          | 47  |

| 5.1 O algoritmo de ECC                                                                  | 47  |

| 5.2 Comentários                                                                         |     |

| Capítulo 6 Resultados                                                                   | 51  |

| 6.1 Resultados da Simulação                                                             | 51  |

| 6.2 Resultados das Compilações                                                          |     |

| 6.3 Comentários                                                                         | 56  |

| Capítulo 7 Considerações Finais                                                         |     |

| 7.1 Comentários                      |    |

|--------------------------------------|----|

| 7.2 Conclusão                        | 57 |

| 7.3 Sugestões para Trabalhos Futuros | 58 |

| Referências Bibliográficas           |    |

### Glossário

**ACC** (*Accumulator*) – registrador acumulador.

ALU (Arithmetic and Logic Unit) – unidade lógico-aritmético.

ASIC (Application-Specific Integrated Circuit) – um chip que pode ser projetado para implementar uma função digital.

AU (Arithmetic Unit) - unidade aritmética.

AUC (Arithmetic Unit Controler) – controlador da unidade aritmética.

BSR (Bit Status Register) – registrador do estado do bit.

Carry look ahead – Técnica digital utilizada para acelerar as operações de soma pela previsão da propagação ou geração de "vai-um" entre os dois operandos.

CHES (Cryptographic Hardware and Embedded Systems) – workshop que apresenta o estado da arte em sistemas criptográficos implementados em hardware.

**CPU** (*Central Processing Unit*) – unidade central de processamento.

**DSP** (Digital Signal Processor) – processador digital de sinais.

ECC (Elliptic Curve Cryptography) – criptografia baseada em curvas elípticas.

ECP (Elliptic Curve Processor) – processador para curvas elípticas.

**EEPROM** (*Eletrically Erasable Programmable Read-Only Memory*) – memória somente para leitura, que podia ser desgravada e regravada eletricamente muitas vezes.

**EPROM** (*Erasable Programmable Read-Only Memory*) – memória somente para leitura, que podia ser desgravada através da exposição do *chip* a raios ultra-violeta. Em seguida, ela podia ser regravada.

**FPGA** (*Field Programmable Gate Array*) – é um tipo de dispositivo programável, isto é, uma classe de *chips* com propósito geral que podem ser configurados por uma variedade de aplicações.

HDL (Hardware Description Language) – linguagem de descrição de hardware.

LSI (Large Scale Integration) – integração em larga escala.

Mainframe – computador de grande porte

MC (Main Controler) – controlador principal.

PC (Personal Computer) – computador pessoal.

PLD (*Programmable Logic Device*) – arquitetura base para a implementação de circuitos diversos, através da programação lógica criada pelo próprio usuário final.

**PROM** (*Programmable Read-Only Memory*) – memória somente para leitura, que é programável pelo usuário final somente uma única vez.

PSW (*Program Status Word*) – palavra de estado do programa.

RAM (Randomic Access Memory) – memória de acesso randômico.

**ROM** (*Read-Only Memory*) – memória somente para leitura.

RSA (Rivest-Shamir-Adleman) – um algoritmo de criptografia assimétrica.

Smart-card – Dispositivo no formato de um cartão de crédito que têm embutido um circuito de processamento e de armazenamento. Candidato a substituir os cartões magnéticos de créditos.

**TEMP** (*Temporary*) – registrador temporário.

Verilog – Linguagem de descrição de hardware

VHDL (Very High Speed Integrated Circuit Hardware Description Language) – uma linguagem de descrição de hardware.

VLSI (Very Large Scale Integration) – integração em escala muito larga.

### Capítulo 1 Introdução

## 1.1 M1 – Um co-processador para algoritmos de criptografia assimétrica.

O presente trabalho descreve o projeto e desenvolvimento de um co-processador para algoritmos de criptografia assimétrica. A este projeto foi dado o nome de Co-processador M1. Não se trata de um dispositivo dedicado a um único algoritmo criptográfico. Pelo contrário, ele propõe uma arquitetura básica e uma biblioteca de módulos de circuitos, descritos em sua maior parte em VHDL (Very High Speed Integrated Circuit Hardware Description Language), que implementam rotinas básicas úteis a vários desses algoritmos.

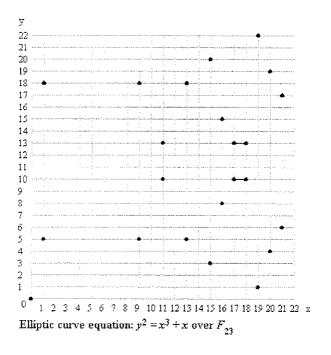

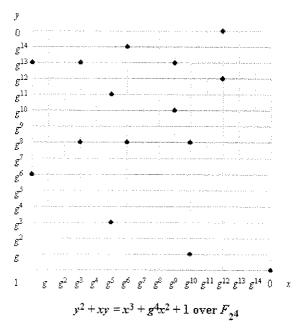

O algoritmo de criptografía assimétrica, baseado no problema do logaritmo discreto sobre curvas elípticas (vide [6], [7], [10], [11] e [12]), também conhecido como algoritmo de ECC (*Elliptic Curve Cryptography*), foi escolhido para demonstrar as operações que podem ser realizadas pelo co-processador M1. As simulações do co-processador M1 são baseadas no uso de curvas elípticas distintas e de diferentes pontos dispostos sobre essas mesmas curvas.

Ele foi compilado de modo a dar prioridade para uma menor área em detrimento a uma maior velocidade. A implementação do co-processador M1 é feita em um dispositivo do tipo FPGA (*Field Programmable Gate Array*) (vide [20]), da família APEX20K da Altera (vide [2], [3], [4] e [5]). O co-processador M1 foi inteiramente compilado, sintetizado e programado utilizando-se o software Quartus II (vide [1]), também da Altera.

#### 1.2 Considerações iniciais

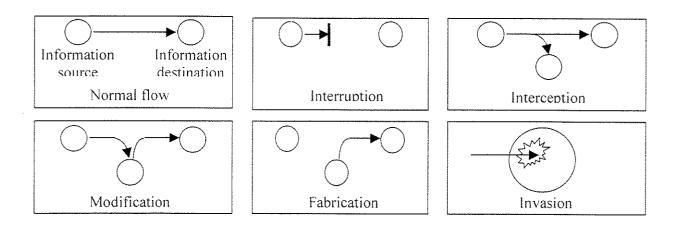

Atualmente, milhões de computadores encontram-se interligados através de redes de computadores. Por esses meios, circulam inúmeros tipos de informações: desde simples mensagens de correio eletrônico entre namorados, arquivos de jogos e de músicas até informações altamente confidenciais, como números de cartões de crédito, transações bancárias, declarações de imposto de renda, projetos secretos de empresas, etc. As informações que apresentam caráter sigiloso demandam a presença de mecanismos capazes

1

de prover segurança contra espionagem, adulteração ou mesmo desvio das mesmas. Segundo Willian Stallings, em [17]: "Segurança em um ambiente de rede depende da aplicação prática de um conjunto de princípios fundamentais de segurança. As ferramentas básicas de segurança em redes procuram garantir a proteção do conteúdo das informações durante as transmissões, assegurar a autenticidade das partes envolvidas em uma interação e impedir que intrusos utilizem as redes para tentar danificar sistemas". Tais ferramentas empregam os chamados algoritmos de criptografía. Esses algoritmos procuram dificultar a ação mal-intencionada de pessoas que visam ter acesso às mensagens sigilosas. Entretanto, de tempos em tempos, uma dessas ações é bem sucedida, o que coloca em dúvida a eficiência do algoritmo. Por esse motivo, esses mecanismos de segurança em redes de computadores sofrem constantes aprimoramentos.

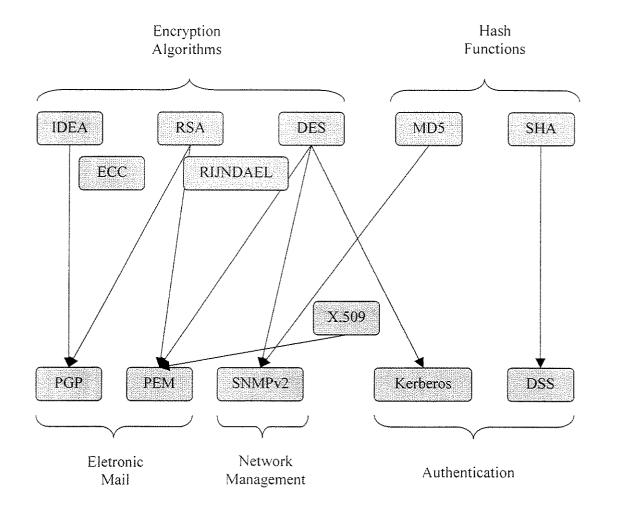

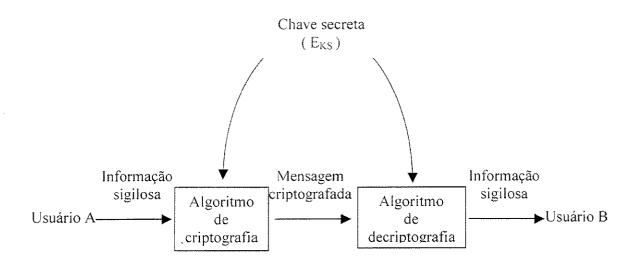

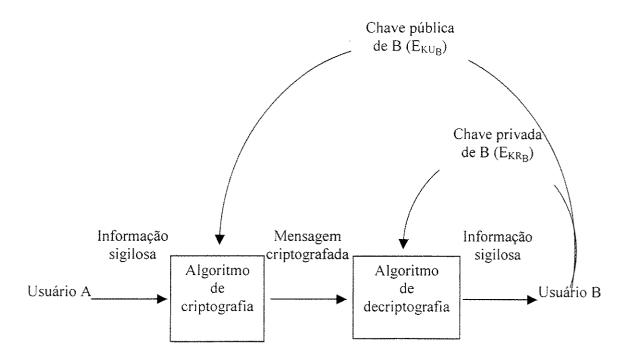

De uma forma geral, a transmissão segura de informações por meio de uma rede de computadores depende da codificação das mesmas através do emprego de representantes de uma classe de algoritmos de criptografia, conhecidos como algoritmos de criptografia simétrica (vide [17]). Tais algoritmos empregam uma chave secreta, a qual é um código binário compartilhado entre o transmissor e o receptor da informação codificada. Este código é o único segredo capaz de ser usado para decodificar tal informação e torná-la novamente inteligível. Entretanto, para que essa chave possa ser compartilhada entre as partes envolvidas na comunicação, de maneira realmente secreta, é necessário o emprego de representantes de uma segunda classe de algoritmos de criptografia, chamados de algoritmos de criptografia assimétrica. Os algoritmos pertencentes a essas duas classes são apresentados em detalhes no apêndice A.

Para alcançarem êxito em suas funções, os algoritmos de criptografia assimétrica necessitam empregar chaves com muitos bits. O RSA (Rivest-Shamir-Adleman) (vide [17]), por exemplo, emprega chaves com pelo menos 1024 bits. Já o algoritmo baseado em ECC, quando usa uma chave de 160 bits, alcança o mesmo grau de segurança do RSA, quando este último usa uma chave de 1024 bits. Embora ambos empreguem chaves com muitos bits, existe uma diferença significativa entre o número de bits das chaves do RSA e do algoritmo baseado em ECC, para um mesmo nível de segurança. É justamente esse menor número de bits que está chamando a atenção dos pesquisadores para ECC.

O grande número de bits das chaves usadas por esses algoritmos faz com que a implementação deles em *software* gere sistemas de segurança relativamente lentos, quando comparados aos mesmos implementados diretamente por *hardware*. Isso ocorre porque esses programas são geralmente executados sobre um processador de propósito geral (vide [16]) de 64 bits, o que significa que eles manipulam as chaves em fatias de 64. Como os processadores não conseguem lidar com uma chave inteira de uma só vez, eles são obrigados a realizar uma mesma operação aritmética ou lógica diversas vezes sobre diferentes porções da mesma chave, a fim de completar toda a operação. Implementações em *hardware*, por outro lado, permitem trabalhar com o tamanho integral das chaves, agilizando o processo de execução do algoritmo.

Atualmente as implementações em *hardware* são feitas, em sua grande maioria, de duas formas: através de desenvolvimento de circuitos dedicados, em geral, nos chamados ASICs (*Application Specific Integrated Circuits*, vide [9]), ou através dos circuitos FPGA.

As implementações em ASICs, por sua vez, embora apresentem um desempenho superior às implementações em *software*, por trabalharem com mais bits, empregam sempre um único algoritmo de criptografia. Se for necessário fazer uma atualização de um mesmo algoritmo, por exemplo, para que ele possa trabalhar com uma chave maior, o que é necessário de tempos em tempos, ou mesmo se for desejado usar um outro algoritmo de criptografia, um novo ASIC precisa ser adquirido, pois não é possível alterar seu conteúdo. Neste sentido, as implementações em FPGAs são mais flexíveis, uma vez que é possível programá-las novamente com a atualização de um mesmo algoritmo ou para substituir um algoritmo por outro.

Segundo Christof Paar [14], "Dispositivos re-configuráveis, como as FPGAs, apresentam grandes oportunidades para a implementação de sistemas criptográficos. Em particular, a rápida substituição de algoritmos criptográficos em *hardware* é possível em FPGAs, enquanto é muito difícil nos tradicionais ASICs".

Grande parte dos algoritmos de criptografía assimétrica é empregada em sistemas de segurança principalmente através do uso de rotinas desenvolvidas em linguagens de alto nível, como a linguagem C. Contudo, os pesquisadores têm começado a voltar a sua

atenção às implementações realizadas por meio de circuitos integrados de aplicação específica, do tipo ASICs e às potencialidades das FPGAs, que estão sendo cada vez mais usadas para receber as implementações desses algoritmos (vide [14]).

Hoje, é possível encontrar, sobretudo através da Internet, diversos artigos descrevendo implementações relacionadas direta ou indiretamente com este trabalho de pesquisa. Entretanto, trabalhos envolvendo *hardware* para criptografia são tão recentes, que o primeiro *workshop* sobre o assunto, o *Cryptographic Hardware and Embedded Systems* (CHES) (vide [14]), foi realizado pela primeira vez em 1999, nos Estados Unidos. O CHES apresenta o estado da arte em sistemas criptográficos implementados em *hardware*.

Esse workshop tem como objetivo apresentar todos os aspectos envolvendo criptografía e segurança em sistemas embutidos (vide [9]) e em hardware em geral. Através dele, tanto a comunidade científica como a indústria pode mostrar os resultados de suas mais recentes pesquisas. Um interesse maior é dado para software de alta performance e para novas maneiras de realizar implementações eficientes em hardware, especialmente para sistemas criptográficos voltados para uso em smart cards (vide [8]), microprocessadores, DSPs (vide [11]), etc.

Essa tendência de pesquisa é comentada por Christof Paar em [14]: "Historicamente, as redes de computadores consistiram principalmente de computadores tradicionais, isto é, servidores ou *mainframes* junto com clientes do tipo PC. Entretanto, é largamente esperado que a próxima geração de dispositivos para redes também consistirá de vários tipos de aplicações embutidas. Tais aplicações podem incluir telefones sem fio, carros com acesso à lnternet, dispositivos domésticos, sensores de infra-estrutura, dispositivos médicos, etc".

### 1.3 Exemplos de trabalhos relacionados.

A seguir são apresentados, de forma resumida, quatro trabalhos que têm alguma relação com este. Desses, o primeiro foi muito importante para este trabalho, pela proximidade e facilidade de interação. Trata-se do trabalho desenvolvido no DCA-FEEC-UNICAMP pelo grupo de pesquisa REGRA\_C, dirigido pelo professor Dr. Marco Aurélio Amaral Henriques (vide [11]). O segundo trabalho apresenta um exemplo de aplicação de algoritmos de criptografía em *smart-cards* (vide [8]). Os dois últimos são exemplos

similares a este trabalho e foram publicados em anais do workshop Cryptographic Hardware and Embedded Systems (CHES) (vide [13] e [19]).

### 1.3.1 Sistema criptográfico baseado em curvas elípticas em DSP

Macedo e os membros do grupo REGRA\_C, em 2001, apresentaram um trabalho (vide [11]), no qual é possível encontrar a descrição de uma implementação de sistema criptográfico baseado em curvas elípticas para ambientes computacionalmente restritos.

A arquitetura base para a implementação desse sistema criptográfico foi o processador digital de sinais (DSP (*Digital Signal Processor*)) da família TMS320C54x da Texas Instruments (vide [11]). Mais especificamente, o dispositivo DSP usado na implementação do código e na obtenção dos resultados foi o TMS320VC5402, que possui 32Kbytes de RAM, 8Kbytes de ROM e trabalha a uma freqüência de 100MHz. A escolha desse dispositivo foi motivada pelo aumento de aplicações que usam microprocessadores DSP. Essas aplicações variam desde equipamentos de áudio digital até radares militares sendo que os DSPs estão tendo um uso crescente em produtos de comunicação sem fio, sobretudo telefones celulares.

Aplicações voltadas para os DSPs da Texas podem ser desenvolvidas com o auxílio do Code Composer Studio (vide [11]) da Texas Instruments. Este ambiente suporta todo o ciclo de desenvolvimento de programas em sistema embutidos: codificação, depuração e análise em tempo real. Para a implementação em questão, a codificação foi feita em linguagem C.

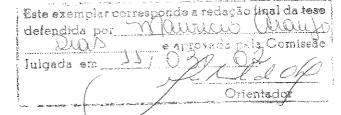

O código foi dividido em camadas e foram implementadas as funções das camadas 1, 2 e 3, representadas na figura 1.1 (fonte: [11]).

Figura 1.1: Implementação de software de criptografía em camadas.

# 1.3.2 Sistemas criptográficos baseados em curvas elípticas para *smart* cards

O Certicom Research Group, em 2000, apresentou um trabalho (vide [8]), no qual é possível encontrar um relato a respeito de sistemas criptográficos baseados em curvas elípticas para smart cards, os quais são dispositivos pequenos, portáteis e que possuem capacidade de armazenamento e processamento de dados. Eles são empregados em diversas áreas, como por exemplo, comércio eletrônico e identificação pessoal, dentre tantas outras aplicações. Muitos desses usos requerem serviços de criptografia, como por exemplo, assinaturas digitais e trocas de chaves. Um smart card é um ambiente propício para a implementação de sistemas criptográficos porque ele contém várias características de segurança, as quais melhoram a proteção das informações sigilosas, tanto durante o armazenamento, quanto durante o processamento das mesmas.

Ao mesmo tempo, algumas das características dos *smart cards* fazem a implementação de algoritmos de criptografia assimétrica sobre esses dispositivos tornar-se um desafio. A pouca memória disponível e a baixa capacidade de processamento são apenas dois exemplos de fatores limitantes para a implementação de sistemas criptográficos nesse ambiente.

Os *smart cards* oferecidos atualmente no mercado possuem uns poucos Kbytes de memórias RAM, ROM e EEPROM, além de uma CPU de 8 bits trabalhando a uma freqüência relativamente baixa (pouco superior a 3 MHz). Qualquer incremento de memória e CPU provoca um aumento significativo nos preços dos *smart cards*. O problema é que, para serem largamente utilizados, eles precisam ser baratos. Sistemas criptográficos baseados em curvas elípticas, por ocuparem menos memória que os outros sistemas, são bons candidatos para serem implementados nesses ambientes restritos.

### 1.3.3 Co-processador criptográfico baseado em curvas elípticas sobre F(2<sup>m</sup>)

Torii e outros pesquisadores, em 2000, apresentaram um trabalho (vide [19]), no qual é possível encontrar a descrição da implementação LSI de um co-processador criptográfico baseado em curvas elípticas sobre Galois Field GF(2<sup>m</sup>) em uma FPGA e em um ASIC, assim como os resultados de suas implementações e testes. Ele realiza a multiplicação escalar para curvas pseudo-randômicas (vide [12]) e curvas de Koblitz (vide [12]), independentemente do tamanho do corpo finito.

A tecnologia usada como base para a primeira implementação foi uma FPGA da Altera, a EPF10K250AGC599-2 (vide [5]). O co-processador opera a 3 MHz e era composto por um multiplicador de 82 bits x 4 bits. Para uma multiplicação escalar envolvendo chaves de 163 bits, ele obtém o resultado em 80ms para curvas pseudorandômicas e em 45ms para uma curva de Koblitz.

A segunda implementação usou como arquitetura base um ASIC da FUJITSU [19] de 0.25 um. O co-processador operou a 66MHz, usando um multiplicador de 288 bits x 8 bits, implementado sobre 165.000 portas lógicas. Para uma multiplicação escalar envolvendo chaves de 163 bits, ele obteve o resultado em 1,1ms para curvas pseudo-randômicas e em 0,65ms para uma curva de Koblitz. Para chaves de 571 bits, os resultados foram obtidos em 22ms e 13ms respectivamente para as mesmas curvas.

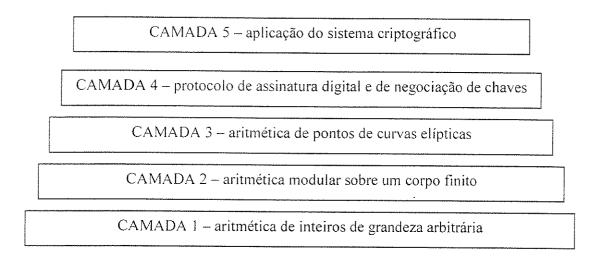

O co-processador foi descrito através da HDL (Hardware Description Language) Verilog (vide [9]). O diagrama básico do co-processador é mostrado na figura 1.2 (fonte: [19]). Ele é composto de quatro blocos funcionais:

Figura 1.2: Diagrama básico do co-processador de ECC.

- I Interface block, responsável pelo controle da comunicação entre o servidor e o coprocessador;

- 2 Operation block, que contém o multiplicador citado anteriormente;

- 3 Storage block, o qual memoriza as entradas, as saídas e os valores intermediários;

- 4 *Control block*, responsável por controlar o bloco de operação para que este realize a multiplicação escalar.

# 1.3.4 Processador de alta performance para sistemas criptográficos baseados em curvas elípticas sobre GF(2<sup>m</sup>)

Orlando e outros pesquisadores, em 2000, apresentaram um trabalho (vide [13]), no qual é possível encontrar a descrição de um processador de alta performance para sistemas criptográficos baseados em curvas elípticas sobre GF(2<sup>m</sup>), implementado em uma FPGA.

A tecnologia usada como base para a implementação do co-processador foi uma FPGA da Xilinx, a XCV400E-8-BG432 (Virtex E). O projeto foi codificado em VHDL (vide [15]) e sintetizado através das ferramentas FPGA Express 3.0 da Synopsis e Design Manager M2.1i da Xilinx (vide [13]).

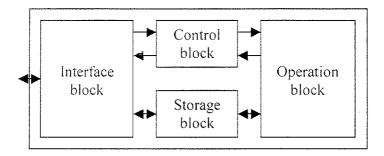

A estrutura interna do processador chamado de ECP (*Elliptic Curve Processor*), é mostrada na figura 1.3 (fonte: [13]).

Figura 1.3: Arquitetura de um processador para curvas elípticas.

Ele possui três componentes principais: o MC (Main Controler), o AUC (Arithmetic Unit Controler) e o AU (Arithmetic Unit).

O MC controla a realização de operação kP, onde k é um inteiro e P um ponto na forma (Xp, Yp), pertencente a uma curva elíptica. Ele controla a execução do *Double\_and\_Add* e da multiplicação Montgomery (vide [11]). O MC também comanda a comunicação com o servidor do sistema. Como o próprio nome já diz, a AUC controla a AU, comandando as operações de adição de pontos, duplicação de ponto e conversão de coordenadas. A AU realiza adições, multiplicações, divisões e inversões para F2<sup>m</sup>, sob controle da AUC.

A implementação usou: um MC de 16 bits com uma memória de 256 palavras de programa; uma AUC de 24 bits com uma memória de 512 palavras de programa; 128 registradores de 167 bits cada; uma interface de entrada e saída de 32 bits para comunicação com o servidor do sistema. O multiplicador foi implementado com os tamanhos 4, 8 e 16 para seus dígitos, não simultaneamente, para avaliar a escalabilidade do ECP.

O processador suporta mudança de algoritmos e curvas elípticas para atualização do sistema criptográfico, a fim de conservar a segurança desse mesmo sistema onde ele está

sendo usado. Trabalhando a uma freqüência de 76,7MHz e com um multiplicador de 16 dígitos, o processador consegue obter o resultado de uma multiplicação de pontos em 0,21ms.

### 1.4 Organização deste Trabalho

Seguem neste trabalho sete capítulos e cinco apêndices. Nos capítulos é apresentado o projeto desde os seus aspectos mais globais até os seus detalhes de construção. Os capítulos ainda discutem os resultados obtidos a partir da simulação do projeto e comparam estes resultados com aqueles descritos por outros trabalhos similares. Os apêndices apresentam informações importantes relacionadas a este trabalho. A seguir é feito um breve resumo de cada um dos capítulos e apêndices deste trabalho.

O Capítulo 2 apresenta algumas considerações preliminares do projeto, procurando analisar as questões de custo, limitações e aplicação do co-processador M1.

O Capítulo 3 descreve a estrutura interna do co-processador M1, revelando, em detalhes, como cada um dos seus componentes foi projetado e como eles são integrados de modo a garantir o funcionamento adequado do co-processador M1.

O Capítulo 4 descreve as características do dispositivo usado para a implementação do co-processador M1: uma FPGA, da família APEX20K, da Altera. Outras famílias de dispositivos FPGAs da Altera, que poderiam ser usadas na implementação do projeto, também são apresentadas nesse mesmo capítulo.

O Capítulo 5 revela como o algoritmo de criptografia assimétrica, baseado no problema do logaritmo discreto sobre curvas elípticas, foi implementado no co-processador M1 com intuito de demonstrar as operações que podem ser ali realizadas.

O Capítulo 6 apresenta os resultados obtidos por simulação, assim como comparações do co-processador M1 com outras implementações em *hardware*.

O Capítulo 7 apresenta as considerações finais a respeito do trabalho, incluindo comentários, conclusão e sugestões para trabalhos futuros.

Após o Capítulo 7 apresentam-se as referências bibliográficas.

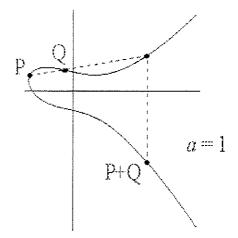

O apêndice A faz uma breve introdução à segurança em redes de computadores, criptografias simétrica e assimétrica, autenticação, assinaturas digitais, curvas elípticas e o problema do logaritmo discreto sobre curvas elípticas.

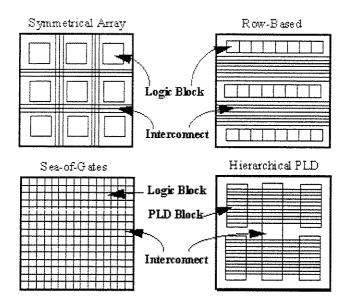

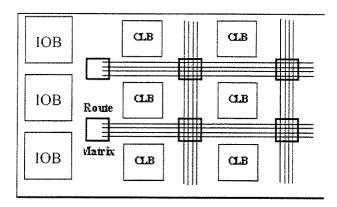

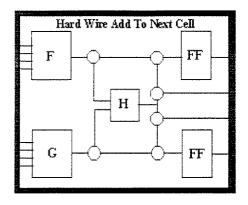

O apêndice B apresenta uma breve introdução às características comuns às FPGAs existentes atualmente no mercado, incluindo comentários a respeito de seus elementos internos.

O apêndice C apresenta uma lista contendo todos os sinais de controle usados pelo co-processador M1, incluindo o número e a função de cada um deles.

O apêndice D permite conhecer as principais características da linguagem de descrição de *hardware*, VHDL, usada no projeto do co-processador M1.

O apêndice E permite conhecer as principais características da ferramenta de engenharia auxiliada por computador, o Quartus II, usada no projeto do co-processador M1.

Os apêndices A e B representam a base fundamental deste trabalho e, ao mesmo tempo, constituem um importante material complementar para o entendimento mais aprofundado dos assuntos relacionados com este trabalho.

| 1 | 7 |

|---|---|

|---|---|

# Capítulo 2 O Co-processador Criptográfico M1

Um co-processador é um dispositivo que tem como finalidade auxiliar o processador principal a realizar funções complementares. O tipo mais conhecido é o co-processador numérico ou matemático que trata operações numéricas em ponto flutuante. Além deste, existem outros tipos de co-processadores com funções bastante específicas projetados para realizarem operações com maior precisão ou velocidade do que o processador principal. Pode-se citar como exemplos, co-processadores gráficos ou de gerência de entrada e saída.

Neste capítulo, é apresentado o projeto de um co-processador voltado ao tratamento de algoritmos criptográficos. A este co-processador foi dado o nome de M1.

### 2.1 Ponto de Partida do Trabalho

O desenvolvimento do co-processador M1 iniciou-se com a observação e a análise das características de muitos programas e algoritmos de criptografía assimétrica. Nesta análise, a necessidade de se trabalhar com uma grande quantidade de bits dentro dos algoritmos chamou a atenção. Isto obriga os programadores a desenvolver programas cujas funções manipulam enormes vetores numéricos. Essas funções apresentam encadeamentos de vários comandos IF, o que torna a execução do programa muito demorada. Uma das maneiras de se aumentar o desempenho desses algoritmos é construir um *hardware* composto por unidades capazes de trabalhar com longos vetores de bits. Em outras palavras, a existência de um dispositivo dotado de registradores de 512 bits, por exemplo, e uma unidade lógico-aritmética capaz de realizar de uma só vez operações aritméticas com o conteúdo desses registradores, eliminaria a necessidade do uso de grandes quantidades de laços dentro dos programas de criptografía assimétrica.

# 2.2 M1: Um Co-processador Voltado para Algoritmos de Criptografia Assimétrica

O dispositivo apresentado neste capítulo é um co-processador criptográfico. Pretende-se com a proposta deste dispositivo criar uma arquitetura básica e uma série de módulos

descritos em VHDL que poderão ser combinados para a implementação de algoritmos de criptografia assimétrica. Não se trata de um dispositivo dedicado a um único algoritmo criptográfico. O co-processador M1 representa uma espécie de "esqueleto" para a implementação de algoritmos de criptografia assimétrica em *hardware*, possuindo a estrutura básica para suportar a implementação desses algoritmos. É importante deixar claro que cada implementação do M1 trabalha com apenas um algoritmo. Assim sendo, o chamado "esqueleto" facilita muito o trabalho do projetista, durante o desenvolvimento do *hardware*.

O co-processador M1 apresenta uma estrutura tal que poderá ser facilmente adaptada a diferentes algoritmos de criptografia assimétrica, em função de todos eles possuírem características similares entre si. Uma dessas semelhanças é que esses algoritmos costumam ser baseados em funções matemáticas do tipo mão-única (*one way functions*) (vide [17]) - as quais funcionam como uma armadilha-, isto é, aplicadas em uma "direção", elas podem servir para criptografar dados, porém, é impossível usá-las na "direção contrária", para tentar decriptografar os mesmos dados. Essas diferentes funções podem até ser resolvidas matematicamente de formas distintas, mas, sendo todas elas funções matemáticas, podem usar uma mesma unidade lógico-aritmética para serem resolvidas, bastando, talvez, fazer algumas pequenas modificações no *hardware*. Por ter sido desenvolvido sobre uma FPGA, o co-processador M1 é bastante flexível para aceitar alterações.

### 2.3 Características do Projeto do Co-processador M1

O co-processador M1 foi desenvolvido parte em VHDL, parte em esquemático. A porção em VHDL compreende toda a micro-memória, incluindo o algoritmo de criptografia assimétrica. A porção em esquemático compreende todo o restante do co-processador M1, isto é, registradores, contadores, unidade lógico-aritmética, barramentos, etc.

A maior complexidade do nosso projeto está na rotina do algoritmo criptográfico, escrita em VHDL. Na verdade, a micro-memória por completa é bastante complexa e está sujeita a possíveis alterações (caso uma substituição de algoritmos seja desejada). Dessa forma ela foi desenvolvida inteiramente em VHDL, para facilitar o trabalho do projetista. Além de o projetista ter que entender a função matemática apresentada pelo algoritmo, e

como ela será empregada na criptografia, ele ainda tem que se preocupar em como transformar tudo isso em *hardware*. Descrever a rotina de criptografia em VHDL é seguramente mais simples do que projetar através de esquemático. Por isso, esse componente do co-processador MI foi escrito nessa linguagem.

O restante do co-processador M1, isto é, registradores, contadores, unidade lógico-aritmética, barramentos, foi desenvolvido em esquemático, porque é provável que esta porção do hardware não sofra muitas alterações, quando se desejar substituir um algoritmo de criptografia por outro. Esses componentes devem ser mantidos dessa forma, porque o projeto em esquemático produz melhores resultados nas FPGAs em termos de área e desempenho, quando comparados com projetos em VHDL.

### 2.4 Custos do Projeto em Relação a ASICs

Implementações em ASICs costumam apresentar baixos custos porque, neste caso, um projeto é feito uma única vez e é gravado em série – linha de produção-, nos chips. Porém, como o co-processador M1 deve poder trabalhar com vários algoritmos de criptografia assimétrica, seria necessário um ASIC para cada tipo de algoritmo, para se ter a mesma funcionalidade. É possível pensar ainda que cada um desses algoritmos, dependendo da maneira como o co-processador M1 foi projetado, teria diferentes padrões de tamanhos de chaves, cada um implementado em um *chip* distinto. Dessa forma, seriam necessários muitos *chips* para implementar o projeto como um todo, elevando seu custo.

No caso deste trabalho, apenas um único chip é suficiente para dar suporte aos algoritmos de criptografia assimétrica. Os algoritmos serão desenvolvidos uma única vez e poderão ser implementados sobre a FPGA apropriada. Quando houver necessidade de trocar um algoritmo, por exemplo, por outro mais seguro, basta apenas adquirir o novo algoritmo e re-programar a FPGA. Não é preciso comprar um novo chip toda vez que se desejar efetuar a troca de um algoritmo. Isso facilita muito o trabalho do projetista, durante o desenvolvimento do *hardware*.

O co-processador M1 pode ser mudado de 128 para 160, 512 bits ou qualquer outra quantidade de bits facilmente, pois basta alterar os valores de algumas constantes do projeto. Para trabalhar com essas grandes porções de bits, é necessário empregar os

dispositivos EP20K600E, EP20K1000E e EP20K1500E. Para fazer a compilação desses dispositivos foi usado um processador Intel Pentium 4, de 1,5GHz de freqüência, com 1024Mbytes de memória RAM e 30Gbytes de HD. A tabela 2.1 (fonte: [1]) mostra o tamanho mínimo exigido para a memória RAM e para o *swap* no HD necessários para simular projetos de *hardware* sobre dispositivos APEX da Altera.

Tabela 2-1 Tamanho mínimo de RAM e de "swap" para simular projetos sobre o APEX.

| Dispositivos APEX                                    | Tamanho mínimo exigido para a memória RAM | Tamanho mínimo exigido<br>para Swap no HD |

|------------------------------------------------------|-------------------------------------------|-------------------------------------------|

| EP20K60E, EP20K100/100E,<br>EP20K160E, EP20K200/200E | 256 MB                                    | 256 MB                                    |

| EP20K300E, EP20K400/400E,<br>EP20K600E               | 512 MB                                    | 512 MB                                    |

| EP20K1000E                                           | 1024 MB                                   | 1024 MB                                   |

| EP20K1500E                                           | 1024 MB                                   | 1024 MB                                   |

### 2.5 Aplicação do Co-processador M1

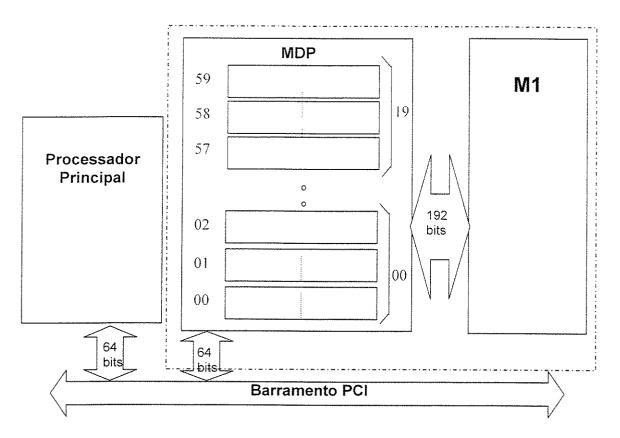

Apresenta-se aqui o exemplo de uso do M1 como um co-processador para um microcomputador compatível com IBM-PC com um barramento PCI. O M1 está instalado numa placa adaptadora com uma unidade de memória de dupla porta, compartilhada pelo barramento PCI e pelo M1. Considere ainda que o M1 deste exemplo está configurado para operar inteiros de 192 bits e para isto utiliza 20 registradores de 192 bits. O barramento PCI em sua versão 2.1 permite a transferência de palavras de 64 bits a uma velocidade de 66MHz (vide[21]).

A figura 2.1 ilustra o exemplo acima. Nela destaca-se a memória de dupla porta MDP que pode ser acessada pelo barramento PCI e pelo M1. O barramento PCI enxerga a MDP como composta por 60 palavras de 64 bits (480 *bytes*). O M1 enxerga a mesma MDP como organizada em 20 palavras de 192 bits.

O processamento criptográfico começa com o processador principal do barramento PCI escrevendo na MDP dados em unidades de 3 palavras de 64 bits, usando para isto 3 ciclos de acesso. O M1 acessa cada uma destas unidades como uma única palavra de 192 bits através de um único ciclo. Após tratar os dados, o M1 coloca os resultados de suas operações de volta em MDP, para que sejam acessados pelo barramento.

Figura 2.1: Exemplo de esquema da comunicação entre o M1 e uma CPU através de uma memória compartilhada.

### 2.6 Comentários

O desenvolvimento do co-processador M1 é resumido nesse capítulo. Aqui foram considerados aspectos gerais de desenvolvimento e esboçado um possível circuito de aplicação num barramento PCI.

Nos demais capítulos a seguir, é possível aprofundar na descrição deste projeto.

### Capítulo 3 A Estrutura Interna do M1

Este capítulo descreve a estrutura interna do co-processador M1, revelando, em detalhes, como cada um dos seus componentes foi projetado e como eles são integrados de modo a garantir o funcionamento adequado do co-processador M1. Para agilizar e facilitar a descrição, este capítulo foi ilustrado com o exemplo de uma implementação do co-processador M1 com somente 8 bits.

### 3.1 Visão Geral da Estrutura Interna do Co-processador M1

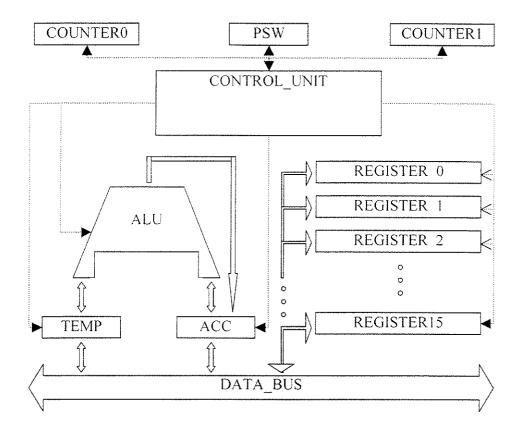

Conforme pode ser visto na figura 3.1, o co-processador M1 é composto, basicamente, por uma unidade de controle, uma unidade lógico-aritmética, vários registradores auxiliares de uso geral, um registrador acumulador (ACC) e um registrador temporário (TEMP), além de algumas outras unidades menores, como contadores e PSW.

O número de elementos que compõem o co-processador M1 pode variar de implementação para implementação, dependendo das exigências impostas pelo algoritmo de criptografía que estiver sendo usado.

A implementação feita para este trabalho exigiu que o co-processador M1 fosse dotado de uma unidade de controle, uma unidade lógico-aritmética, 18 registradores, sendo 16 deles, registradores de uso geral, um registrador acumulador e um registrador temporário. Também foram necessários dois contadores e uma PSW.

Embora praticamente todos os elementos do co-processador M1 sejam aptos a manipular longos vetores de bits de uma só vez, o co-processador M1 descrito neste capítulo trabalha com apenas 8 bits, apenas por uma questão de facilitar a representação das figuras mostradas mais à diante. Em outras palavras, todos os registradores do co-processador M1, assim como a unidade lógico-aritmética, serão mostrados com tamanho igual a 8 bits.

Figura 3.1: Visão geral da estrutura interna do co-processador M1.

Na verdade, outras implementações do M1 podem vir a apresentar elementos com tamanhos variando de 2 bits até n bits. O valor de "n" é limitado pela capacidade da FPGA que é usada para implementar o circuito do M1.

Um buffer (a MDP), que não faz parte da estrutura interna do co-processador M1 e por isso não aparece na figura 3.1, alimenta o barramento de dados (DATA\_BUS) com as informações que serão processadas pelo M1. Todos os registradores têm acesso ao DATA\_BUS. A unidade lógico-aritmética também tem acesso ao DATA\_BUS, mas de forma indireta, por intermédio do ACC e do TEMP. Sendo assim, este barramento representa um dos principais meios de comunicação entre os elementos que compõem o M1. Por ele, circulam todas as informações que são processadas pelo co-processador M1 durante a execução do algoritmo de criptografia.

Outro meio de comunicação importante, presente dentro do M1, é o barramento de controle, o qual permite que a unidade de controle mantenha comunicação com os demais

elementos do M1. As linhas tracejadas da figura 3.1 representam sinais de controle que chegam e saem da unidade de controle. Eles são responsáveis por comandar todos os elementos presentes no M1. Esse trabalho integrado entre os elementos é que permite que o M1 execute suas tarefas com sucesso. Esses elementos foram desenvolvidos através de esquemático e serão apresentados em detalhes nas próximas seções deste mesmo capítulo.

Além desses elementos, o M1 dispõe de uma biblioteca de módulos de circuitos que implementam rotinas básicas úteis a vários algoritmos de criptografia assimétrica, como por exemplo, o módulo capaz de realizar multiplicação de números da ordem de algumas centenas de bits. Outros módulos, que também podem manipular longos vetores de bits de uma só vez, são capazes de realizar operações como divisão, multiplicação, entre outras.

#### 3.2 Unidade de Controle

A unidade de controle é responsável pelo controle de todas as atividades do co-processador M1. Ela comanda os passos necessários para a busca de dados no buffer, assim como a execução do algoritmo e a colocação do resultado final de volta no buffer.

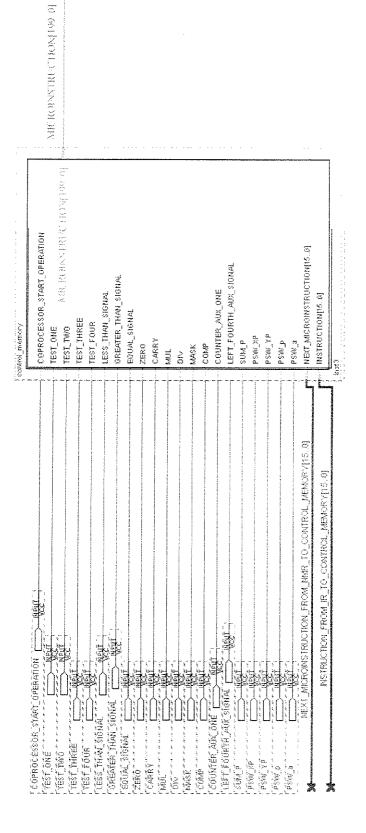

A figura 3.2 mostra a representação do circuito da unidade de controle. Todas as entradas, com exceção de INSTRUCTION e NEXT\_MICROINSTRUCTION, representam sinais provenientes da PSW. Esses sinais impõem condições à execução do algoritmo de criptografia, determinando a seqüência do fluxo de execução do mesmo. Essa seqüência aparece em INSTRUCTION e em NEXT\_MICROINSTRUCTION, na forma de endereços de 16 bits. Os sinais de controle gerados pela unidade de controle são colocados na saída MICROINSTRUCTION. Esta unidade gera até duzentos sinais de controle diferentes. O apêndice C mostra a lista contendo todos os sinais de controle usados nesta implementação.

Na verdade, a unidade de controle é descrita em VHDL, como pode ser visto na figura 3.3. Através dela, é possível notar as declarações de todas as entradas comentadas anteriormente, assim como a saída **MICROINSTRUCTION**, para os duzentos sinais de controle. As demais linhas representam uma pequena parte do algoritmo (vide capítulo 5), o qual emprega os módulos de circuitos da biblioteca, comentados na seção anterior.

Figura 3.2: Visão geral do circuito da unidade de controle.

```

(a)

std_logic_vector( 15 downto 0 );

std_logic_vector( 199 downto 0 )

std_logic;

std_logic;

std_logic;

std_logic;

std_logic;

std_logic;

std_logic;

44444

architecture CONTROL MEMORYBehave of CONTROL MEMORY is

entity COMTROL_MENORY is port( COPROCESSOR_START_OPERATION, TEST_ONE

TEST TWO, TEST THREE, TEST FOUR

LESS THAN SIGNAL, GREATER THAN SIGNAL

EQUAL SIGNAL, ZERO, CARRY, MUL, DIV

NASK, COMP, COUNTER AUX ONE

LEFT FOURTH AUX SIGNAL, SUM P

PSW XP, PSW YP, PSW p, PSW B

NEXT MICROIMSTRUCTION, INSTRUCTION

99744552111987754321098765421098765465666 000000

ASSESSIVE EXTREMENTABLE PROPERTY OF THE PROPER

MICROINSTRUCTION

use ieee.std_logic_1164.all;

MICROINSTRUCTION <=

end CONTROL MEMORY;

OPERATION ( O - KP ;

library ieee;

begin

```

Figura 3.3: Descrição da unidade de controle em VHDL.

### 3.3 PSW (Program Status Word)

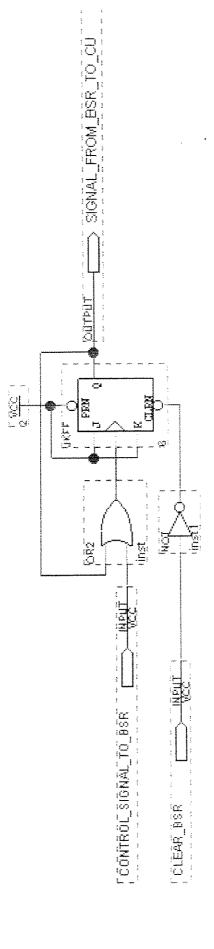

O circuito PSW (*Program Status Word*) é composto por vários registradores BSR (Bit Status Register) de 1bit, independentes uns dos outros. Dentro da PSW, cada BSR armazena o estado de um determinado elemento do co-processador M1 ou registra a condição de uma dada operação, durante a execução do algoritmo de criptografia. Por exemplo, a PSW possui um BSR para registrar se a contagem realizada pelo contador COUNTERO foi reinicializada ou não; o mesmo acontece para o contador COUNTER1.

O circuito apresentado pela figura 3.4 é o BSR, responsável pelo armazenamento de um único bit. Ele é composto, quase que exclusivamente, por um flip-flop JK. O sinal de entrada control\_signal\_to\_bsr é responsável por permitir o armazenamento de um novo valor no registrador. clear\_bsr é um sinal de entrada que muda o estado do registrador para zero. O sinal de saída signal\_from\_bsr\_to\_cu tem como função informar a unidade de controle a respeito do valor armazenado pelo registrador BSR.

A realimentação da entrada com o sinal da saída serve para que o registrador BSR conserve indefinidamente o seu valor, mesmo que haja alterações de valores no sinal de entrada. Em outras palavras, se o registrador estiver armazenando o valor 0 e receber um sinal com valor 1 em sua entrada, ele passará a registrar o valor 1. O valor armazenado no registrador não vai mudar, independentemente da variação de valores do sinal de entrada, graças a essa realimentação. O registrador somente voltará a armazenar o valor 0, se receber um sinal de *clear*.

A PSW possui outros BSRs importantes, a saber: um BSR para registrar o *carry-out* de uma operação de adição; um BSR para registrar se o resultado de uma comparação resultou em igualdade; um BSR para registrar se o resultado de uma comparação resultou em um número maior que o outro; um BSR para registrar se o resultado de uma comparação resultou em um número menor que o outro.

Em suma, a PSW registra o estado da execução do algoritmo de criptografia, para um dado momento.

Figura 3.4: Estrutura interna da PSW (registrador BSR).

# 3.4 Registradores

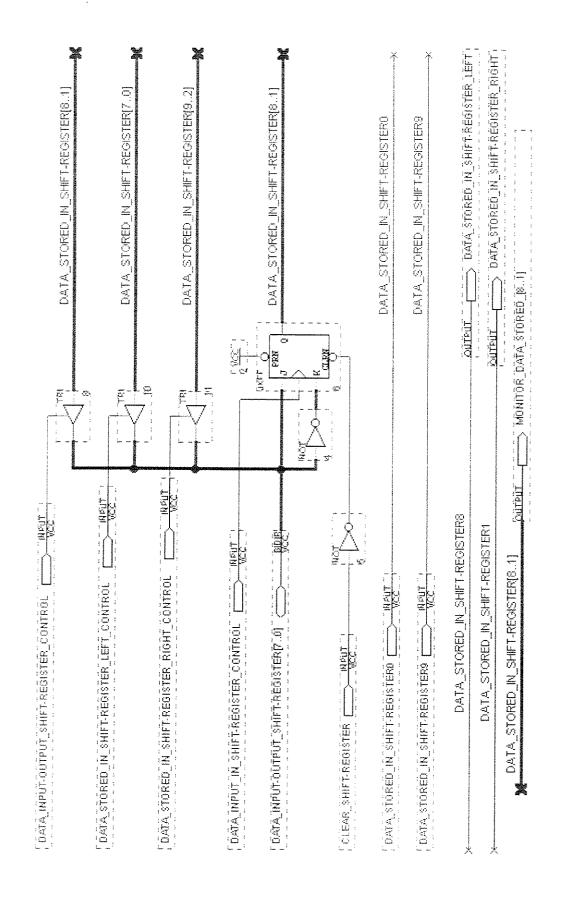

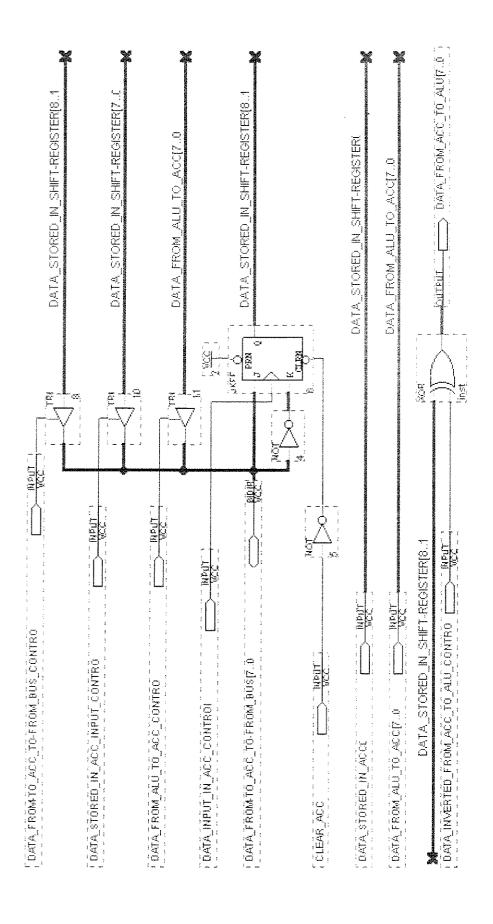

Cada um dos dezesseis registradores auxiliares de uso geral do co-processador M1 possui 8 bits de tamanho. A maioria funciona como registrador auxiliar, usado pelo co-processador M1 para guardar dados. Todos eles podem ser usados para realizar deslocamentos à direita ou à esquerda.

A estrutura interna de um desses registradores é apresentada em detalhes pela figura 3.5. Através dela é possível notar que o registrador é dotado de oito flip-flops JK e possui diversas entradas para sinais de controle e para dados.

Para que um novo valor possa ser armazenado no registrador, basta alimentar data\_input-output\_shift\_register[7..0], através do DATA\_BUS, com o valor desejado. Quando data\_input\_in\_shift\_register\_control mudar seu valor de 0 para 1, o registrador armazenará o novo valor.

Se for desejado saber o valor presente no registrador, em um dado instante de tempo, basta mudar o valor de DATA\_INPUT-OUTPUT\_SHIFT\_REGISTER\_CONTROL de 0 para 1 e o conteúdo do registrador será apresentado no DATA\_BUS, por meio do DATA\_INPUT-OUTPUT\_SHIFT\_REGISTER[7..0].

As entradas data\_stored\_in\_shift-register\_left\_control e data\_stored\_in\_shift-register\_right\_control recebem os sinais de controle, respectivamente, para as operações de deslocamento à esquerda e de deslocamento à direita. Quando ocorre um deslocamento à esquerda, o bit 8 (bit excedente) do registrador é colocado na saída data\_stored\_in\_shift-register\_left e o novo bit 0 é introduzido no registrador através da entrada data\_stored\_in\_shift-register0. Quando ocorre um deslocamento à direita, o bit excedente do registrador é colocado na saída data\_stored\_in\_shift-register\_right e o novo bit é introduzido no registrador através da entrada data\_stored\_in\_shift-register9.

As operações de deslocamento à esquerda e de deslocamento à direita são importantes, dentre outras coisas, para a realização das operações aritméticas de multiplicação e de divisão.

O sinal clear\_shift\_register obriga o registrador a armazenar o valor 0.

Fígura 3.5: Estrutura interna de um registrador.

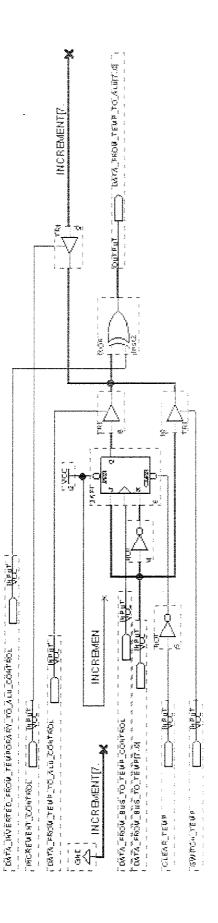

# 3.5 Unidade Lógico-Aritmética

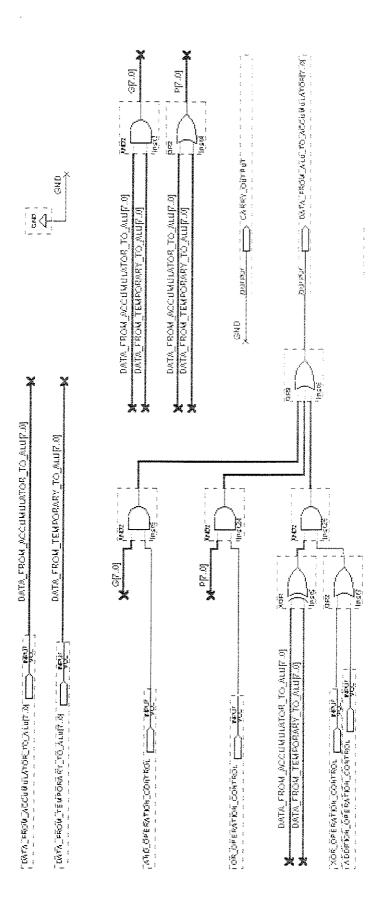

A unidade lógico-aritmética (ALU) é capaz de realizar operações aritméticas (soma, subtração, multiplicação e divisão) e operações lógicas (AND, OR, NOT e XOR), além de comparações (maior que, menor que e igual a) tanto para números inteiros como para polinômios.

Enquanto unidades lógico-aritméticas tradicionalmente realizam operações em dados de 16, 32 ou 64 bits, a unidade lógico-aritmética do co-processador M1 é capaz de realizar qualquer uma das operações anteriores em dados com até algumas centenas de bits, de uma só vez. Essa característica elimina a necessidade de se fazer programas nos quais grandes inteiros são tratados como vetores de inteiros menores, operados separadamente uns dos outros com o auxílio de vários laços aninhados.

A figura 3.6a revela que as entradas data\_from\_accumulator\_to\_alu e data\_from\_temporary\_to\_alu recebem as informações que serão processadas pela ALU, respectivamente, do ACC e do TEMP. O resultado das operações realizadas pela ALU é colocado na saída data\_from\_alu\_to\_accumulator, para ser posteriormente armazenado pelo ACC. A mesma figura 3.6a mostra o conjunto de portas lógicas responsáveis por realizarem as operações lógicas AND, OR, NOT e XOR. Essas operações são ativadas, respectivamente, pelos sinais de controle and\_operation\_control, or\_operation\_control e xor\_operation\_control, para as duas últimas operações. Os circuitos necessários para as operações de soma e subtração foram omitidos por não serem necessários para este projeto, por isso não aparecem na figura 3.6a.

Um outro circuito que também não aparece, mas poderia estar presente internamente na unidade lógico-aritmética, em implementações de outros algoritmos, e, por isso, merece ser comentado, é o circuito *carry look ahead* 512 bits. Tal circuito aumenta em muito a velocidade das operações aritméticas, uma vez que o carry não precisa se propagar através de 512 somadores de Ibit. Na verdade o *carry* se propagará por apenas 16 unidades de *carry look ahead* de 32 bits cada uma, possibilitando maior velocidade nas operações aritméticas. O último *carry* é propagado através da saída carry output.

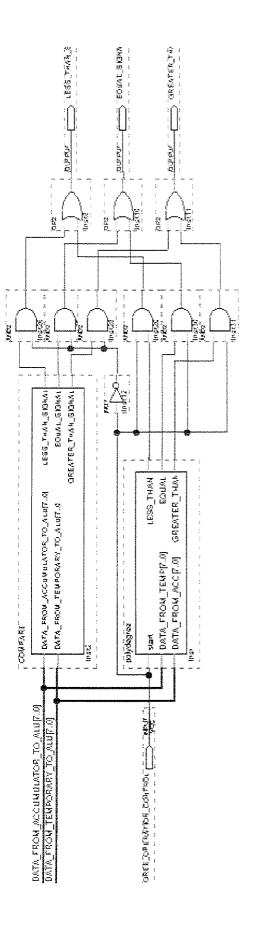

A unidade lógico-aritmética possui um circuito chamado compare, mostrado na figura 3.6b. Esse circuito é responsável por realizar a operação de comparação entre números inteiros. A figura 3.7 mostra a descrição desse circuito em VHDL. A figura 3.7 mostra que suas entradas data\_from\_accumulator\_to\_alu e data\_from\_temporary\_to\_alu são alimentadas, respectivamente, com o valor do inteiro armazenado em TEMP e com o valor do inteiro armazenado em ACC. Se o resultado de uma comparação resulta em igualdade, a saída equal\_signal assume o valor 1; se o valor do inteiro vindo do ACC é maior que o valor do inteiro vindo do TEMP, a saída greater\_than\_signal assume o valor 1; se o valor do inteiro vindo do TEMP, a saída less\_than\_signal assume o valor 1.

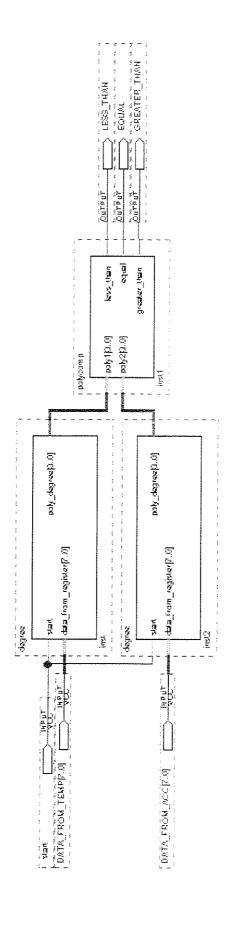

A mesma unidade lógico-aritmética possui um circuito chamado polydegree, mostrado na figura 3.6b. Esse circuito é responsável por realizar a operação de comparação entre polinômios. A figura 3.8 mostra a estrutura interna desse circuito em detalhes. Ele realiza sua função sempre que o sinal **START** assume um valor igual a 1. O circuito polydegree é composto por três outros circuitos: dois circuitos chamados degree e um circuito chamado polycomp.

O degree é responsável por calcular o grau de um polinômio. Dentro de polydegree, existem dois circuitos degree porque um deles serve para calcular o grau do polinômio armazenado em ACC, enquanto o outro serve para calcular o grau do polinômio armazenado em TEMP. Esses dois polinômios entram em polydegree, respectivamente, através das entradas DATA\_FROM\_ACC e DATA\_FROM\_TEMP, cada uma com 8 bits.

O polycomp é responsável por comparar os graus de dois polinômios. A figura 3.8 mostra que ele compara os graus gerados na saída dos dois circuitos degree, comentados anteriormente. Em outras palavras, suas entradas poly1 e poly2 são alimentadas, respectivamente, com o grau do polinômio armazenado em TEMP e com o grau do polinômio armazenado em ACC. Se o resultado de uma comparação resulta em igualdade, a saída EQUAL assume o valor 1; se o grau do polinômio vindo do ACC é maior que o grau do polinômio vindo do TEMP, a saída GREATER\_THAN assume o valor 1; se o grau do polinômio vindo do ACC é menor que o grau do polinômio vindo do TEMP, a saída LESS\_THAN assume o valor 1.

Figura 3.6a: Estrutura interna da ALU.

Figura 3.6b: Estrutura interna da ALU.

```

bit_vector(7 DownTo 0);

LESS THAN SIGNAL <= '1' WHEN DATA FROM ACCUMULATOR TO ALU<DATA FROM TEMPORARY TO ALU ELSE '0';

EQUAL SIGNAL <= '1' WHEN DATA FROM ACCUMULATOR TO ALU=DATA FROM TEMPORARY TO ALU ELSE '0';

GREATER THAN SIGNAL<='1' WHEN DATA FROM ACCUMULATOR TO ALU>DATA FROM TEMPORARY TO ALU ELSE '0';

PORT (DATA FROM ACCUMULATOR TO ALU, DATA FROM TEMPORARY TO ALU : IN LESS THAN SIGNAL, EQUAL SIGNAL, GREATER THAN SIGNAL : OUT bit

ARCHITECTURE compare bby OF compare IS

END compare bby;

EMD compare;

BEGIM

```

ENTITY compare IS

Figura 3.7: Descrição do circuito compare em VHDL.

Figura 3.8: Estrutura interna do polydegree.

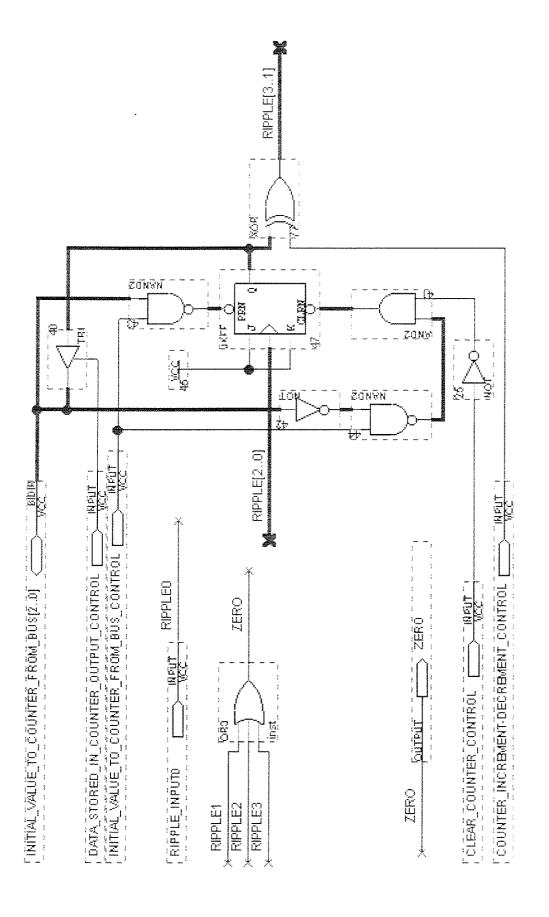

#### 3.6 Contadores

Contadores são circuitos que possibilitam ao co-processador M1 saber o número de vezes que uma certa operação está sendo realizada, durante a execução do algoritmo de criptografía.