Universidade Estadual de Campinas

Faculdade de Engenharia Elétrica e de Computação

Departamento de Semicondutores, Instrumentação e Fotônica

## COMPENSAÇÃO EM FREQÜÊNCIA DE AMPLIFICADORES CMOS DE DOIS E TRÊS ESTÁGIOS

## Autor André Luís Fortunato

Dissertação submetida à Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas, como requisito parcial à obtenção do título de Mestre em Engenharia Elétrica, sob orientação do Prof. Dr. Carlos Alberto dos Reis Filho.

#### Banca Examinadora:

Prof. Dr. Carlos Alberto dos Reis Filho – FEEC/UNICAMP

Prof. Dr. Rafael Santos Mendes – FEEC/UNICAMP

Dr. Richard Titov Lara Saez – MOTOROLA/JAGUARIÚNA

Campinas, 8 de julho de 2004

### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

F779c

Fortunato, André Luís

Compensação em frequência de amplificadores CMOS de dois e três estágios / André Luís Fortunato. -- Campinas, SP: [s.n.], 2004.

Orientador: Carlos Alberto dos Reis Filho. Dissertação (mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Amplificadores eletrônicos. 2. Amplificadores operacionais. 3. Curvas de frequência. I. Reis Filho, Carlos Alberto dos. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

#### RESUMO

Este trabalho analisa os critérios e técnicas de projeto para compensação em freqüência de amplificadores operacionais em tecnologia CMOS. Foram projetados 10 amplificadores operacionais (amp-ops), incluindo amplificadores de dois e de três estágios de ganho. Serão usados os parâmetros de consumo, freqüência de ganho unitário e estabilidade na comparação do desempenho e uso de determinado método de compensação em freqüência. Mostraremos, também, como ocorre a movimentação dos pólos no circuito. Em especial, para o amplificador de dois estágios, foram relacionados os parâmetros que influenciam nessa movimentação.

Ao projetar estes amplificadores foram estabelecidas as seguintes especificações: no caso dos amplificadores de dois estágios, a tensão de alimentação é simétrica ( $\pm 2V$ ), carga composta de um resistor de  $100\,\mathrm{k}\Omega$  em paralelo com um capacitor de  $50\,\mathrm{pF}$ , ganho DC mínimo de  $60\,\mathrm{dB}$ , freqüência de ganho unitário de 1MHz. Para os amplificadores de três estágios , a tensão de alimentação é de  $\pm 1,5\,\mathrm{V}$ , carga composta de um resistor de  $25\,\mathrm{k}\Omega$  em paralelo com um capacitor de  $50\,\mathrm{pF}$ , ganho DC mínimo de  $100\,\mathrm{dB}$  e freqüência de ganho unitário de  $100\,\mathrm{dB}$ .

#### ABSTRACT

This dissertation analyzes the project techniques used in frequency compensation of CMOS operational amplifiers (op-amps). A collection of 10 op-amps, including two and three stages amplifiers was fabricated for test. Power consumption, unity gain frequency and stability were aimed for performance comparison. Poles movement analysis was extensively exploited in circuits understanding. Specially, for the two-stage amplifier, poles movement condition was obtained.

Two distinct specifications were focused. For two stage amplifiers, specifications included nominal power supply of  $\pm\,2\,V$  , an external load of  $100\,k\Omega$

in parallel with 50 pF, a minimum open-loop gain of 60 dB and a unity gain frequency of 1MHz. A more rigorous specification were aimed for three stage amplifiers:  $\pm$  1,5 V power supply, minimum DC gain of 100 dB and 1MHz unity gain frequency driving an external load of 25 k $\Omega$  in parallel with 50 pF.

Agradeço aos meus pais pelo imenso apoio durante este meu pequeno passo.

Agradeço ao meu orientador pela oportunidade, confiança e pelo apoio.

Agradeço ao Cenpra, especialmente a Carlos Oliveira, pelas fotomicrografias, a Wellington por verificar os *chips* e a Saulo Finco por ter cedido o espaço.

## **SUMÁRIO**

| Índice de Figuras e Tabelas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | xiii   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Notação Utilizada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xxiii  |

| 1 Introdução                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1      |

| 2 Amplificador Operacional de Transcondutância                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5      |

| 2.1 Amplificador Operacional de Dois Estágios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5<br>7 |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11     |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14     |

| 2.1.4 Análise dos Resultados Obtidos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25     |

| Notação Utilizada xxi  1 Introdução  2 Amplificador Operacional de Transcondutância  2.1 Amplificador Operacional de Dois Estágios  2.1.1 Polarização  2.1.2 Ganho em Baixa Freqüência 1  2.1.3 Ganho em Alta Freqüência 2  2.1.4 Análise dos Resultados Obtidos 2  2.2 Amplificador Operacional de Três Estágios 2  2.2.1 Polarização 2  2.2.2 Ganho em Baixa Freqüência 3  2.2.3 Ganho em Alta Freqüência 3  3 Compensação em Freqüência para Amplificadores de Dois Estágios 5  3.1 Compensação em Freqüência Tipo Miller 5  3.1.1 Critério de Estabilidade para Compensação Miller 6  3.2 Compensação em Freqüência Tipo Miller com Cancelamento de Zero por Resistor 7  3.3 Compensação em Freqüência Tipo Miller com Cancelamento de Zero por Multi-Caminho 8  3.4 Compensação em Freqüência Tipo Miller com Cancelamento do Segundo Pólo por Multi-Caminho 8 | 27     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34     |

| 2.2.3 Ganho em Alta Freqüência                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 39     |

| 3 Compensação em Freqüência para Amplificadores de Dois Estágios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53     |

| 3.1 Compensação em Freqüência Tipo Miller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53     |

| 3.1.1 Critério de Estabilidade para Compensação Miller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83     |

| 3.5 Efeito de g <sub>MII</sub> no Amplificador de Transcondutância de Dois Estágios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87     |

| 4 | Compensação em Freqüência para Amplificadores de Três Estágios                                            | 91               |

|---|-----------------------------------------------------------------------------------------------------------|------------------|

|   |                                                                                                           |                  |

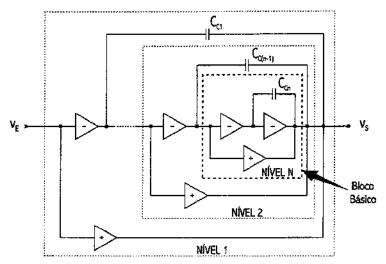

|   | 4.1 Compensação em Frequência Tipo Miller Aninhada                                                        | 91               |

|   | 4.1.1 Critério de Estabilidade para Compensação Miller Aninhada                                           | 104              |

|   | 4.2 Compensação em Frequência Tipo Miller Aninhada com<br>Cancelamento de Zero por Resistor               | 110              |

|   | 4.3 Compensação em Freqüência Tipo Miller Aninhada com Multi-<br>Caminho                                  | 118              |

|   | 4.3.1 Critério de Estabilidade para Compensação Tipo Miller Aninhada com Multi-Caminho                    | 122              |

|   | 4.4 Compensação em Freqüência Tipo g <sub>м</sub> − C Aninhada                                            | 127              |

|   | 4.4.1 Critério de Estabilidade para Compensação g <sub>м</sub> − C Anihada                                | 129              |

|   | 4.5 Compensação em Freqüência Tipo Miller Aninhada com Antecipação                                        | 133              |

|   | 4.5.1 Critério de Estabilidade para Compensação Miller Aninhada com<br>Antecipação                        | 136              |

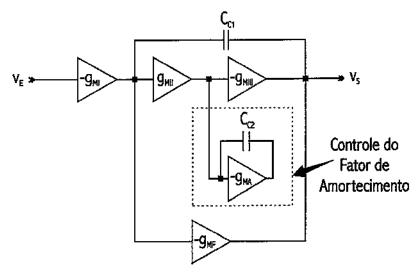

|   | 4.6 Compensação em Freqüência com Controle do Fator de<br>Amortecimento                                   | 138              |

|   | 4.6.1 Critério de Estabilidade para Compensação com Controle do Fator de Amortecimento                    | 1 <del>4</del> 8 |

| 5 | i Implementação e Resultados Experimentais                                                                | 155              |

|   |                                                                                                           |                  |

|   | 5.1 Implementação                                                                                         | 155              |

|   | 5.2 Resultados Experimentais                                                                              | 158              |

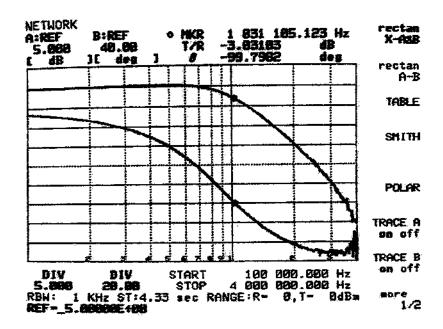

|   | 5.2.1 Compensação em Frequência Tipo Miller (MC)                                                          | 160              |

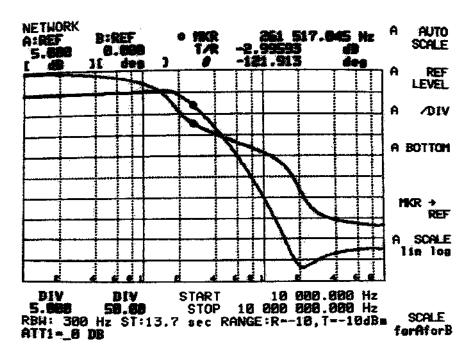

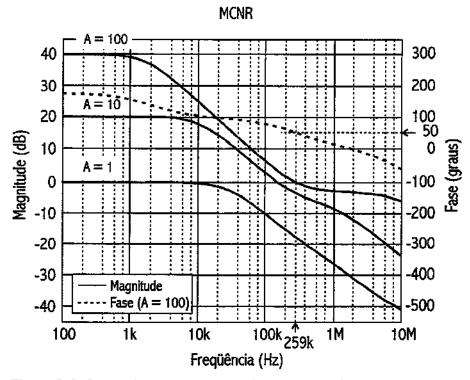

|   | 5.2.2 Compensação em Freqüência Tipo Miller com Cancelamento de<br>Zero por Resistor (MCNR)               | 161              |

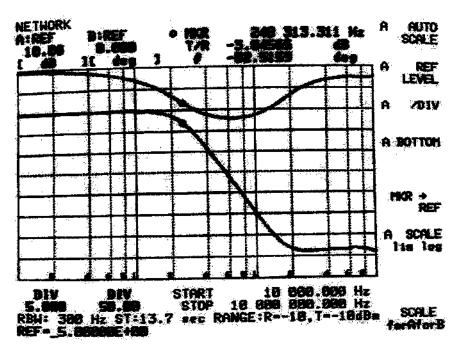

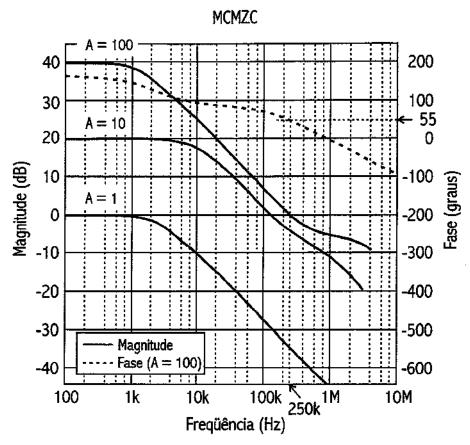

|   | 5.2.3 Compensação em Freqüência Tipo Miller com Cancelamento de<br>Zero por Multi-Caminho (MCMZC)         | 163              |

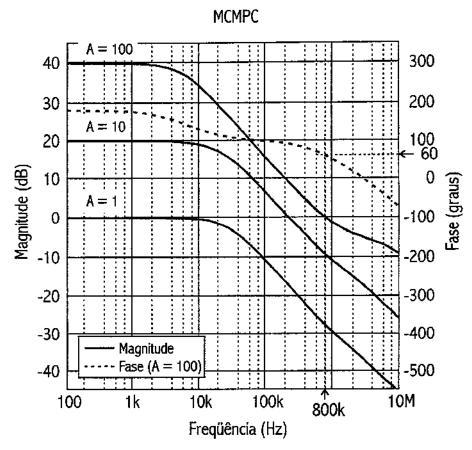

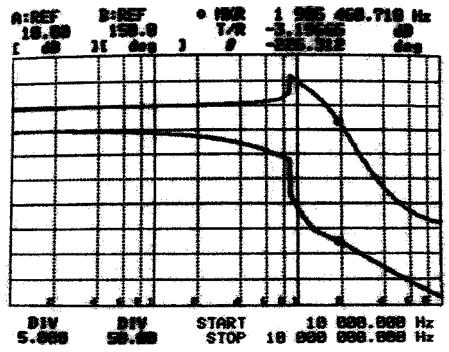

|   | 5.2.4 Compensação em Freqüência Tipo Miller com Cancelamento do<br>Segundo Pólo por Multi Caminho (MCMPC) | 165              |

|   | 5.2.5 Compensação em Freqüência Tipo Miller Aninhada (NMC)                                                | 167              |

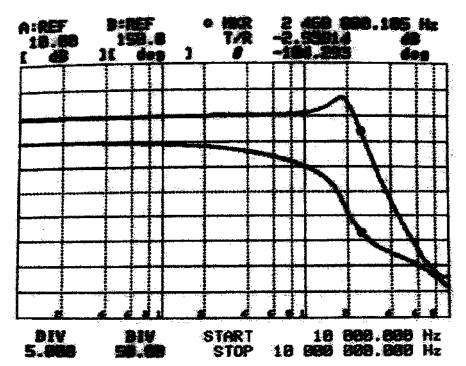

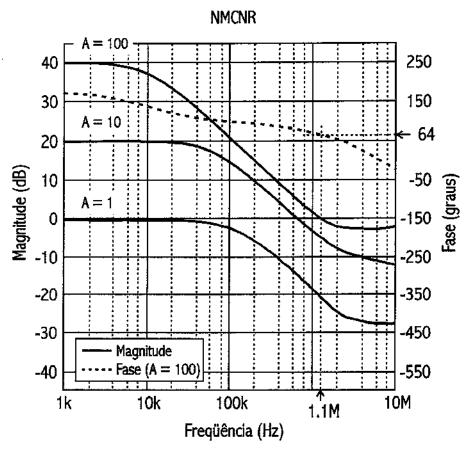

|   | 5.2.6 Compensação em Freqüência Tipo Miller Aninhada com<br>Cancelamento de Zero por Resistor (NMCNR)     | 169              |

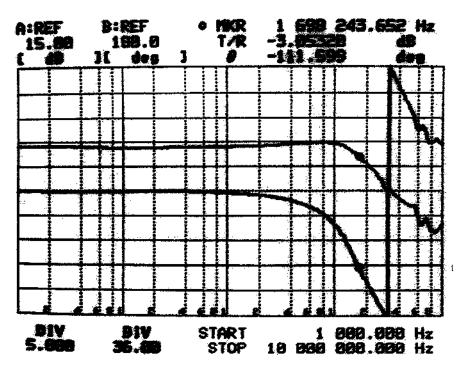

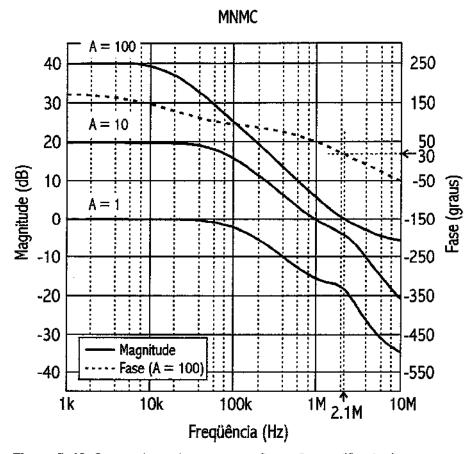

| 5.2.7 Compensação em Freqüência Tipo Miller Aninhada com Multi-<br>Caminho (MNMC)  | 170 |

|------------------------------------------------------------------------------------|-----|

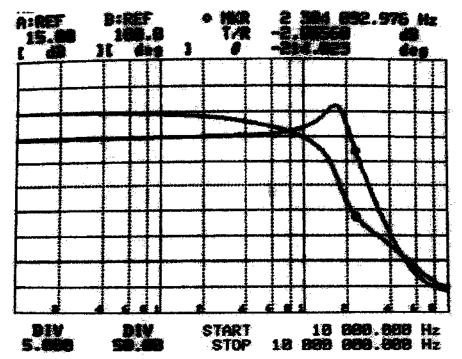

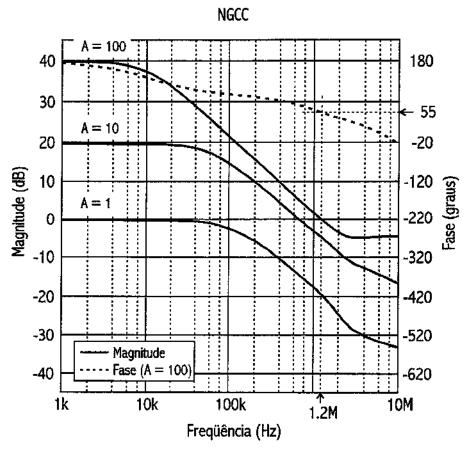

| 5.2.8 Compensação em Freqüência Tipo g <sub>M</sub> - C Aninhada (NGCC)            | 173 |

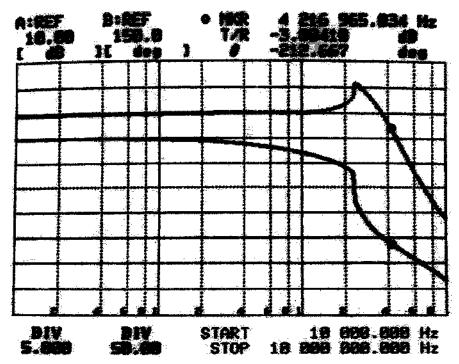

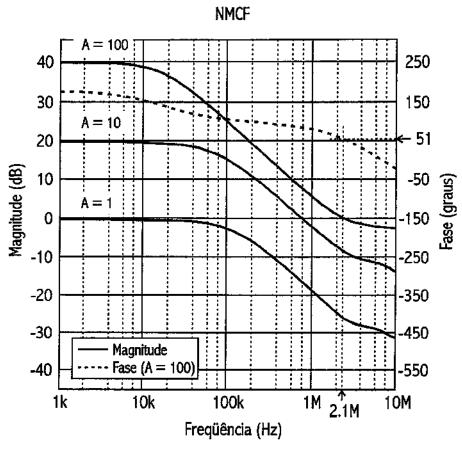

| 5.2.9 Compensação em Freqüência Tipo Miller Aninhada com<br>Antecipação (NMCF)     | 174 |

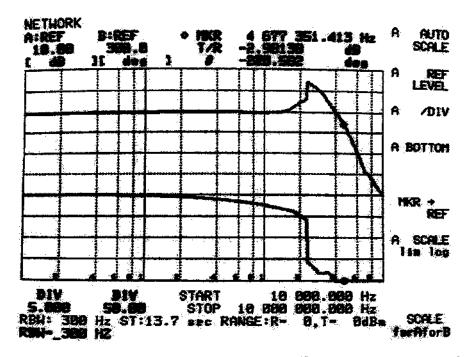

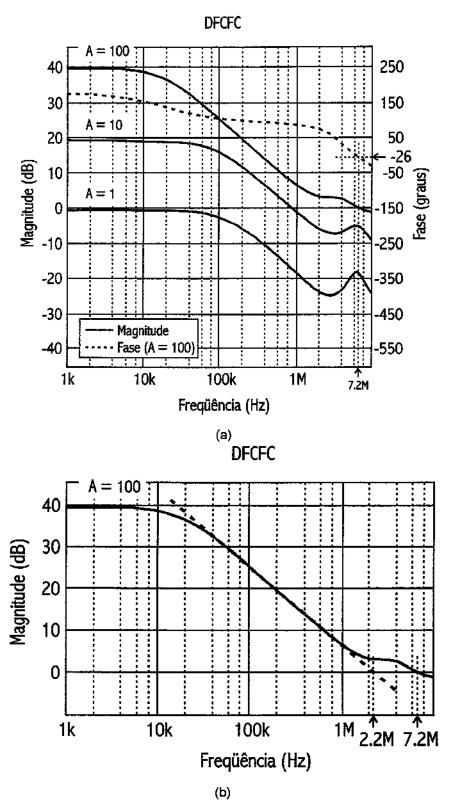

| 5.2.10 Compensação em Freqüência com Controle do Fator de<br>Amortecimento (DFCFC) | 177 |

| 6 Conclusões                                                                       | 183 |

| Referências                                                                        | 185 |

| Apêndice A                                                                         | 189 |

| Apêndice B                                                                         | 209 |

## ÍNDICE DE FIGURAS E TABELAS

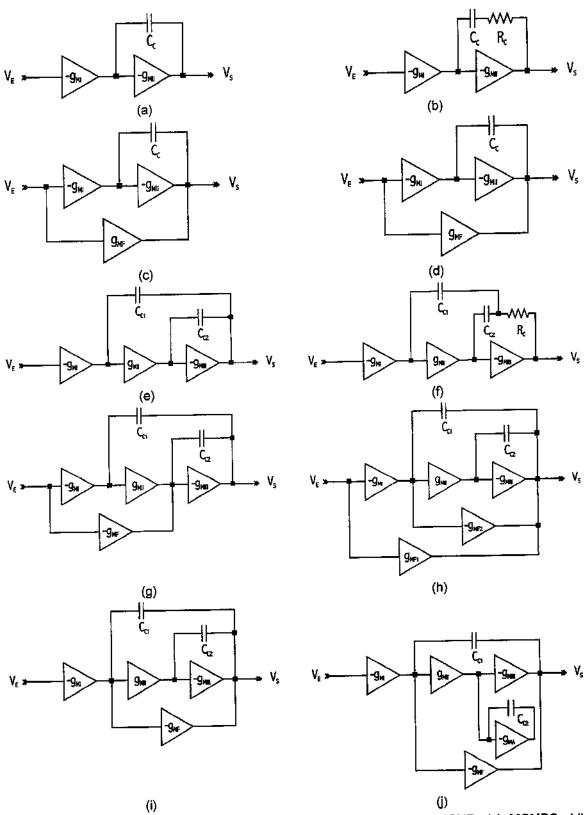

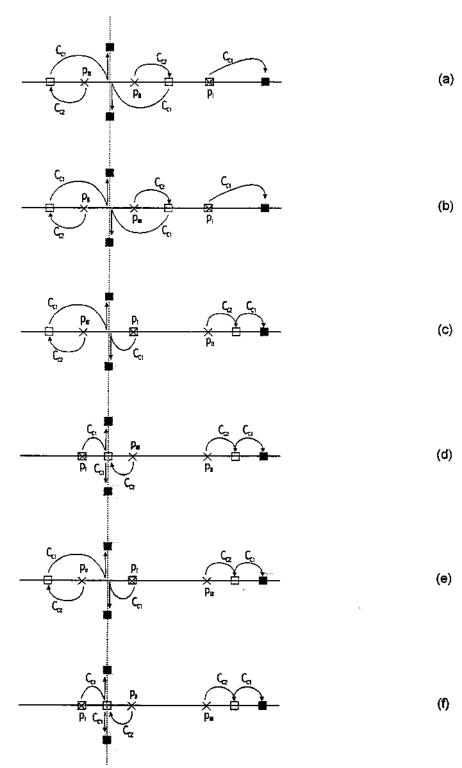

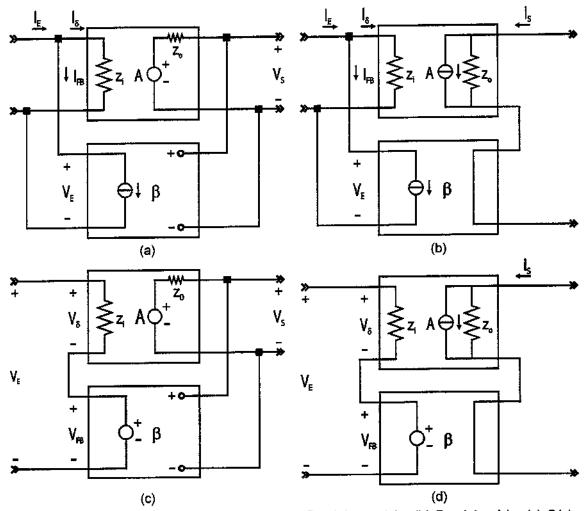

| Figura 1–1  Estruturas de compensação em freqüência. (a) MC. (b) MCNR. (c) MCMPC. (d) MCMZC. (e) NMC. (f) NMCNR. (g) MNMC. (h) NGCC. (i) NMCF. (j) DFCFC. | 3  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 2–1                                                                                                                                                | e  |

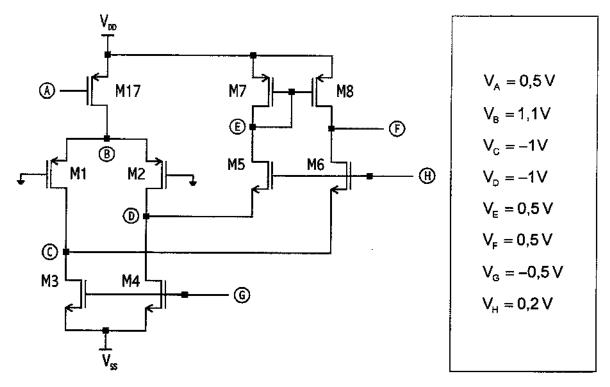

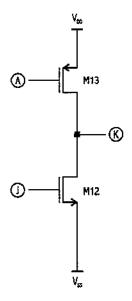

| Figura 2–2 Definição dos pontos de polarização para o estágio de entrada do amp-op de dois estágios.                                                      | 8  |

| Tabela 2–1 Definição dos valores de tensão do estágio de entrada para o amp-op de dois estágios.                                                          | 8  |

| Figura 2–3                                                                                                                                                | 10 |

| Tabela 2–2<br>Definição dos valores de tensão do estágio de entrada para o amp-op de dois estágios.                                                       | 10 |

| Figura 2–4                                                                                                                                                | 15 |

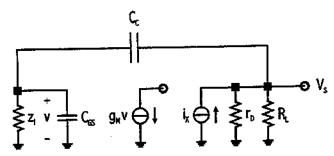

| Figura 2–5Modelo de pequenos sinais equivalente em torno da freqüência de 500MHz para cálculo de                                                          | 17 |

| p <sub>1</sub> e z <sub>1.</sub>                                                                                                                          |    |

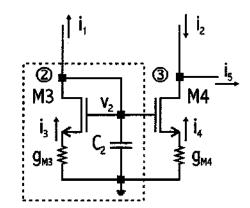

| Figura 2–6<br>Modelo de pequenos sinais equivalente para cálculo de p <sub>2</sub> e z <sub>23</sub>                                                      | 18 |

| Figura 2–7<br>Gráfico de (2-20) representando os efeitos de p <sub>2</sub> e z <sub>23 ,</sub>                                                            | 19 |

| Fìgura 2–8<br>Modelo de pequenos sinais equivalente para cálculo de p <sub>1,</sub> p <sub>2</sub> e z <sub>1</sub> .                                     | 21 |

| Figura 2–9<br>Análise na freqüência do amplificador sem realimentação.                                                                                    | 25 |

| Figura 2–10                                                                                                                                               | 26 |

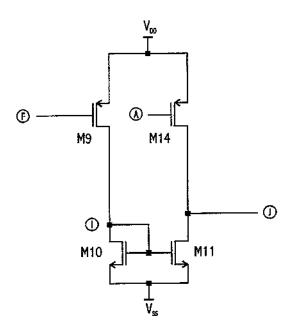

| Figura 2–11<br>Definição dos pontos de polarização para o estágio de entrada do amp-op de três estágios.                                                  | 28 |

| Tabela 2–3<br>Definição dos valores de tensão do segundo estágio para o amp-op de três estágios.                                                          | 28 |

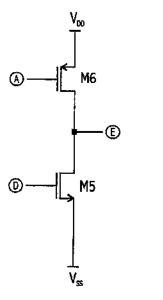

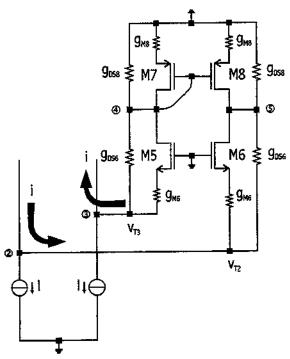

| Figura 2–12Definição dos pontos de polarização para o segundo estágio do amp-op de três estágios.                                                         | 31 |

| Tabela 2–4                                                                                                                                                                                                                  | 31 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Definição dos valores de tensão do segundo estagio para o amp-op de tres estagios.                                                                                                                                          | 32 |

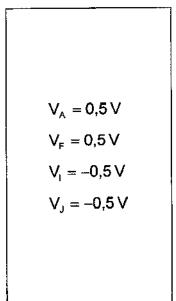

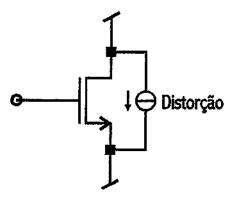

| Figura 2–13<br>Diagrama de blocos do funcionamento do segundo estágio de ganho.                                                                                                                                             |    |

| Figura 2–14                                                                                                                                                                                                                 | 33 |

| Tabela 2–5  Definição dos valores de tensão do terceiro estágio para o amp-op de três estágios.                                                                                                                             | 33 |

| Figura 2–15                                                                                                                                                                                                                 | 34 |

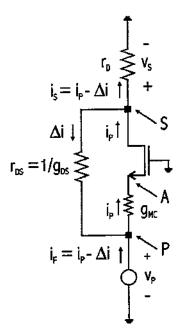

| Figura 2–16Realimentação negativa do transistor cascode.                                                                                                                                                                    | 35 |

| Figura 2–17                                                                                                                                                                                                                 | 39 |

| Figura 2–18                                                                                                                                                                                                                 | 42 |

| Figura 2–19                                                                                                                                                                                                                 | 43 |

| Figura 2–20                                                                                                                                                                                                                 | 45 |

| Figura 2–21                                                                                                                                                                                                                 | 45 |

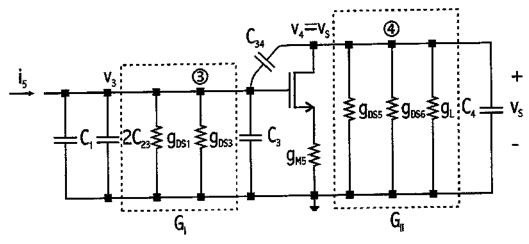

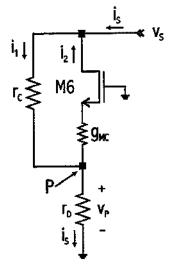

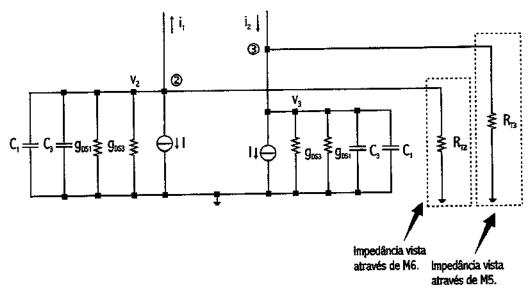

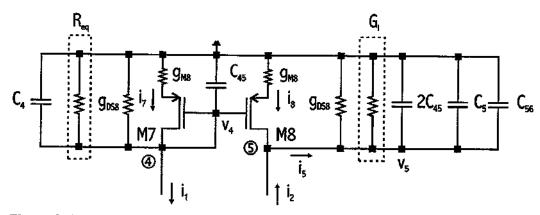

| Figura 2–22  Circuito equivalente para cálculo dos pólos nos nós @ e ⑤.                                                                                                                                                     | 46 |

| Figura 2–23                                                                                                                                                                                                                 | 48 |

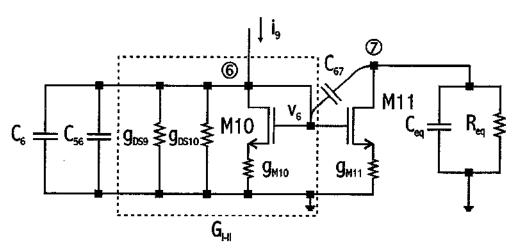

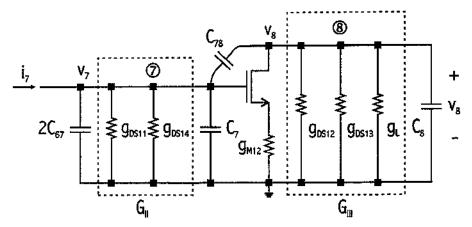

| Figura 2–24.  Circuito equivalente para cálculo dos pólos nos nós ⑦ e ⑧.                                                                                                                                                    | 49 |

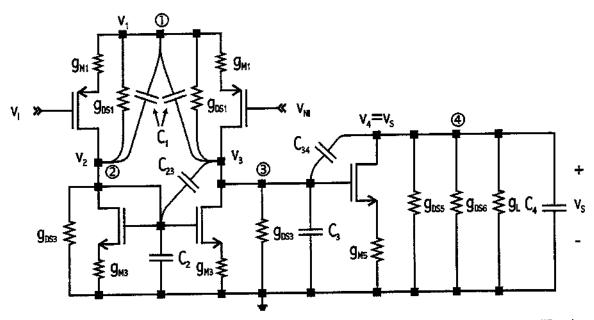

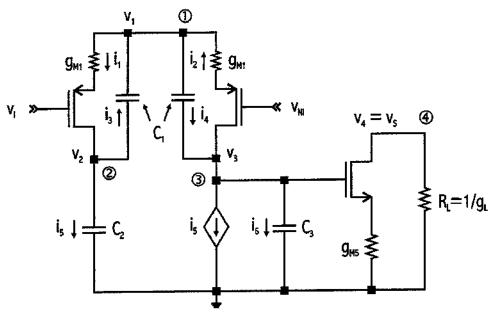

| Figura 3–1                                                                                                                                                                                                                  | 54 |

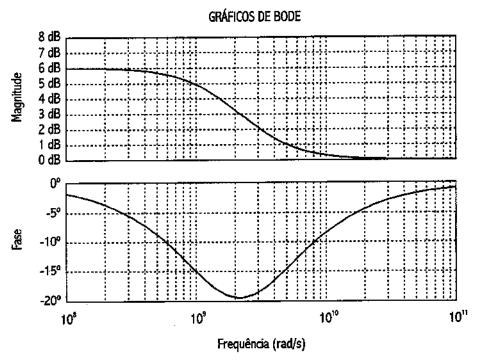

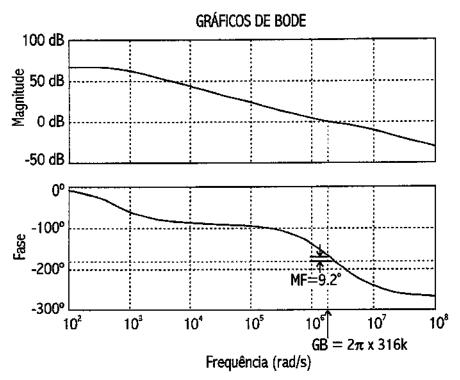

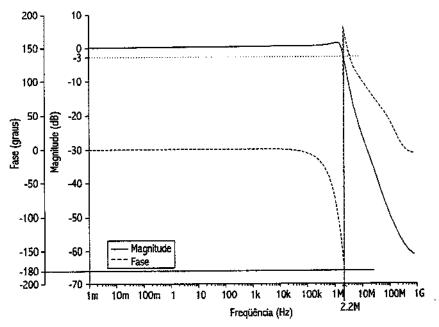

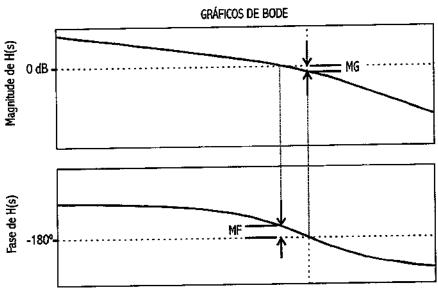

| Figura 3–2.  Diagrama de Bode obtido pela simulação do amplificador de dois estágios sem compensação em freqüência.                                                                                                         | 55 |

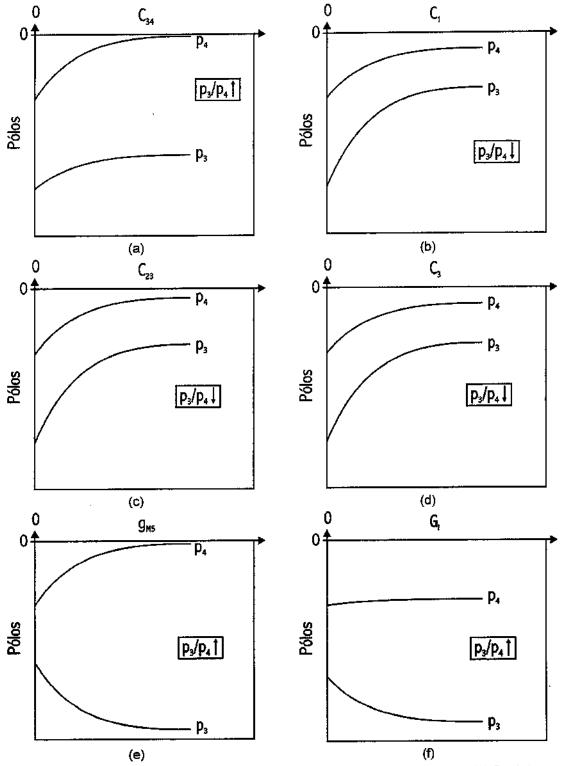

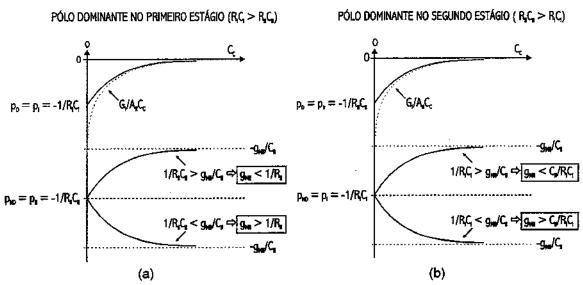

| Figura 3–3  Variação da posição dos pólos com parâmetros do amplificador. (a) Posição dos pólos versus C <sub>34</sub> (b) Posição dos pólos versus C <sub>1</sub> (c) Posição dos pólos versus C <sub>23</sub> (d) Posição | 57 |

| dos pólos versus C <sub>3</sub> (e) Posição dos pólos versus g <sub>M5</sub> (f) Posição dos pólos versus G <sub>I</sub>                                                                                                    |    |

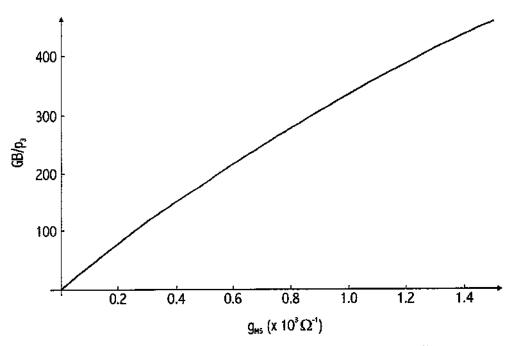

| Figura 3–4<br>Variação da razão entre produto ganho-banda e segundo pólo com g <sub>M5</sub>                                                                                                                                                                                | 59 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

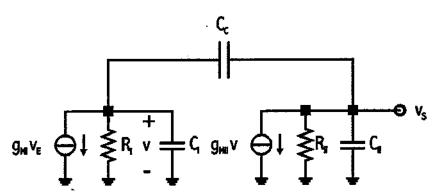

| Figura 3–5Modelo tradicional de um amplificador de dois estágios.                                                                                                                                                                                                           | 61 |

| Figura 3–6                                                                                                                                                                                                                                                                  | 63 |

| Figura 3–7                                                                                                                                                                                                                                                                  | 65 |

| Figura 3–8Amplificador operacional de dois estágios com compensação em freqüência tipo Miller.                                                                                                                                                                              | 66 |

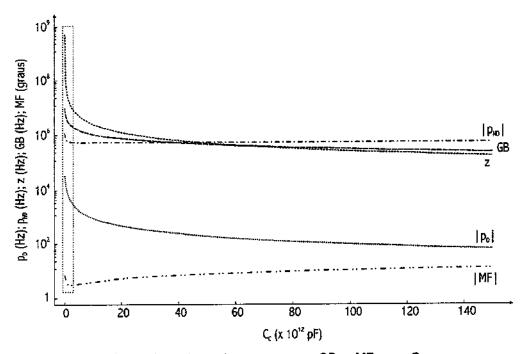

| Figura 3–9<br>Variação dos valores de p <sub>D</sub> , p <sub>ND</sub> , z, GB e MF com C <sub>C</sub> .                                                                                                                                                                    | 67 |

| Figura 3–10                                                                                                                                                                                                                                                                 | 70 |

| Figura 3–11                                                                                                                                                                                                                                                                 | 75 |

| Figura 3–12                                                                                                                                                                                                                                                                 | 76 |

| Figura 3–13Amplificador com compensação em freqüência tipo Miller com cancelamento de zero por resistor.                                                                                                                                                                    | 76 |

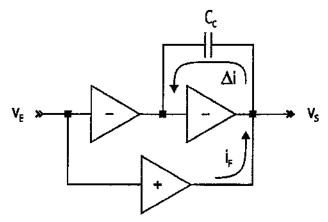

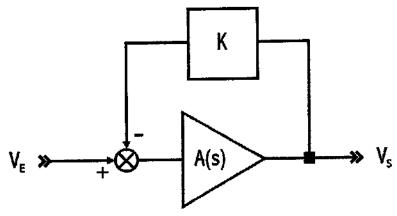

| Figura 3–14Diagrama de blocos mostrando o princípio de funcionamento do efeito de cancelamento do zero feito pela corrente de antecipação.                                                                                                                                  | 78 |

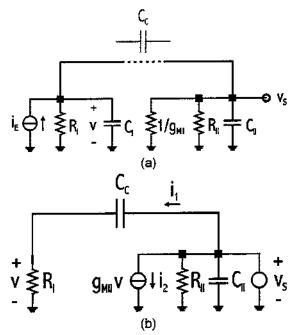

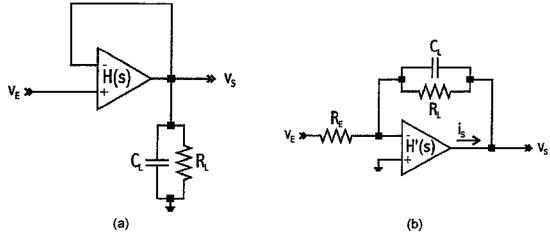

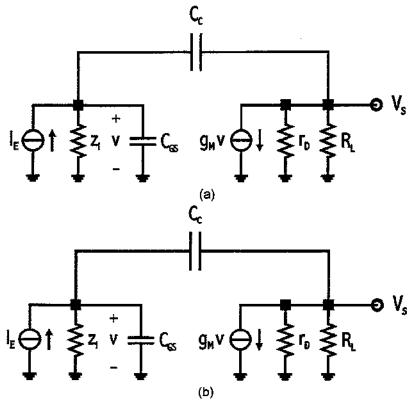

| Figura 3–15Amplificador de dois estágios compensado em freqüência. (a) Compensação em freqüência tipo Miller com cancelamento de zero por multi-caminho. (b) Modelo de pequenos sinais para o amplificador compensado em freqüência cancelamento de zero por multi-caminho. | 79 |

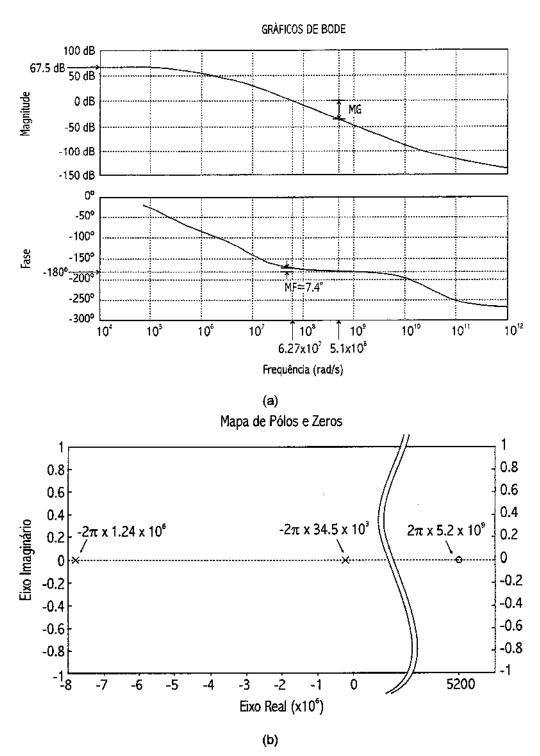

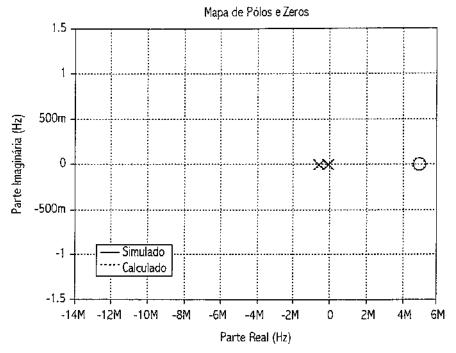

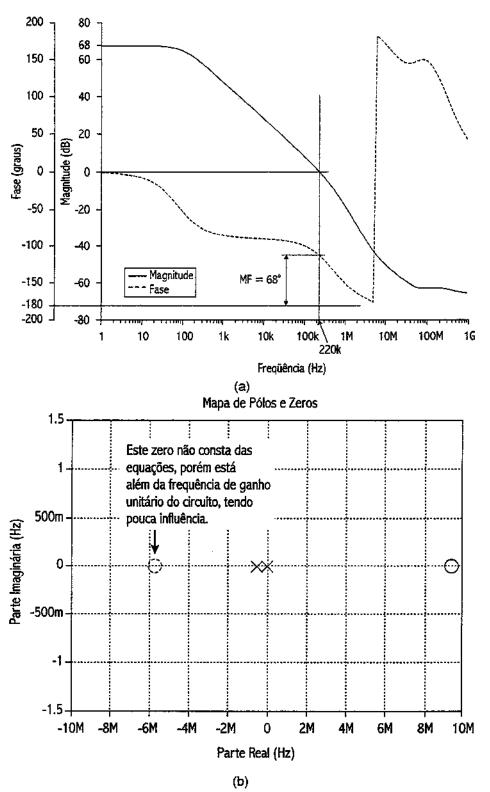

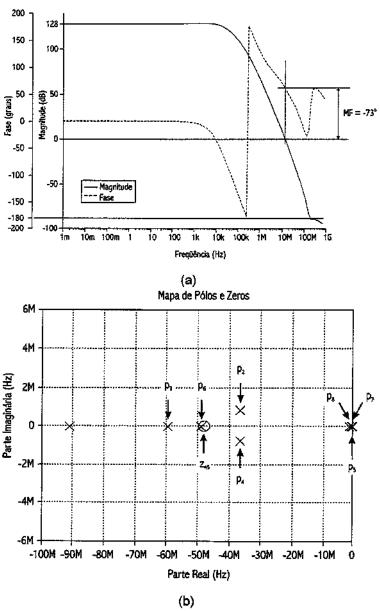

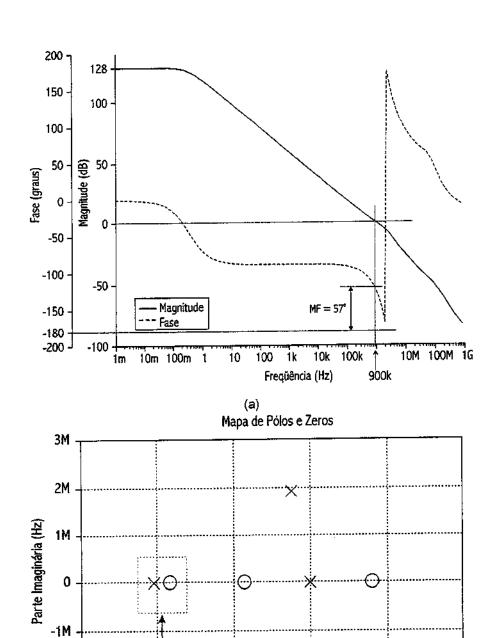

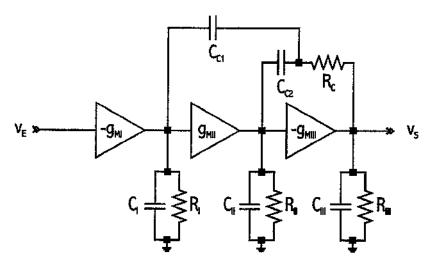

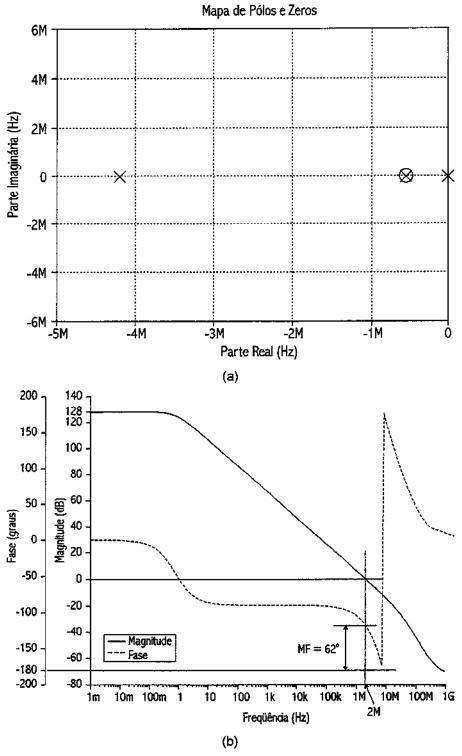

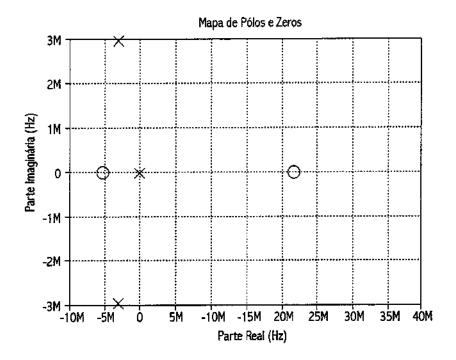

| Figura 3–16Simulações para o amplificador compensado em freqüência por cancelamento de zero por multi-caminho. (a) Diagrama de Bode. (b) Posicionamento dos pólos e zeros.                                                                                                  | 82 |

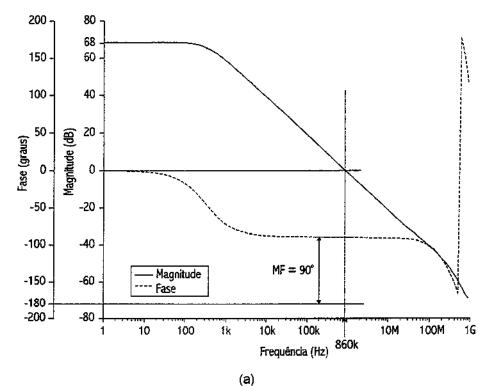

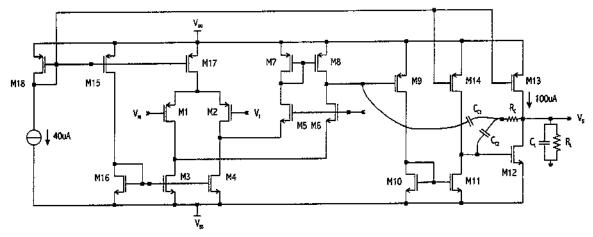

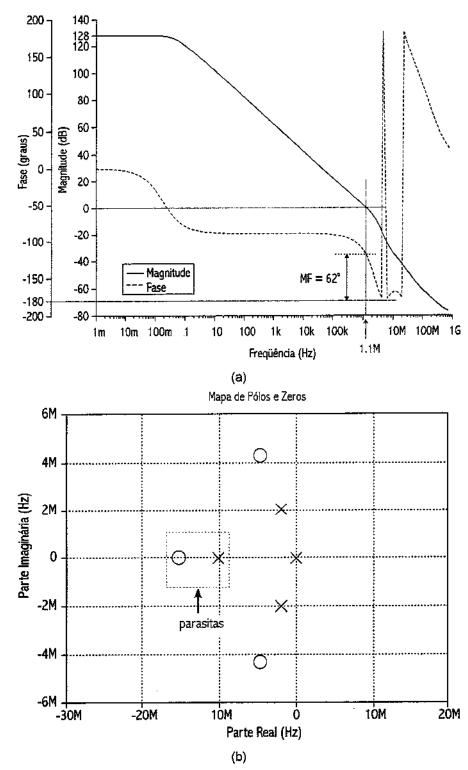

| Figura 3–17Simulações para o amplificador compensado em freqüência por cancelamento do segundo pólo por multi-caminho. (a) Diagrama de Bode. (b) Posicionamento dos pólos e zeros.                                                                                          | 86 |

| Figura 3–18                                                                                                                                                                                                                                                                 | 88 |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

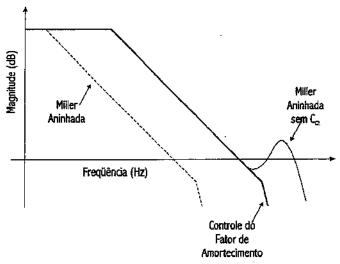

| Figura 4–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92<br>93 |

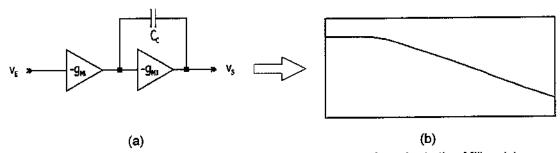

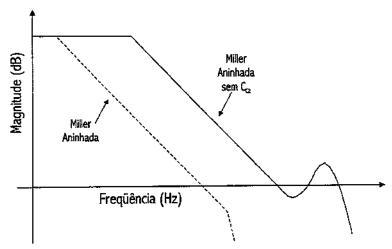

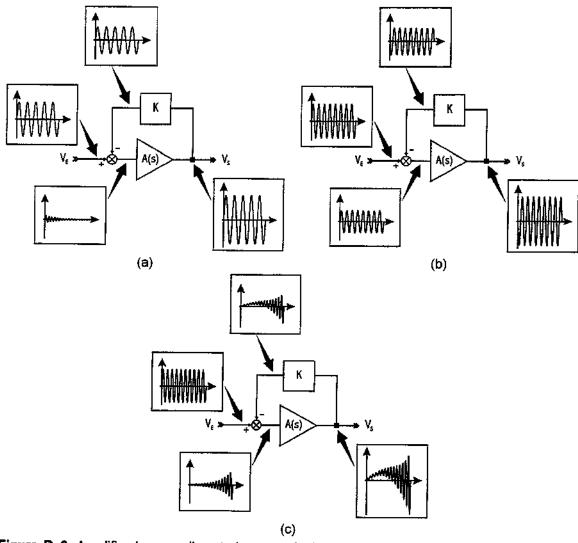

| Figura 4–2Amplificador de dois estágios com compensação em freqüência tipo Miller. (a) Diagrama de olocos. (b) Resposta em freqüência desprezando efeitos do zero.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93       |

| Figura 4–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93       |

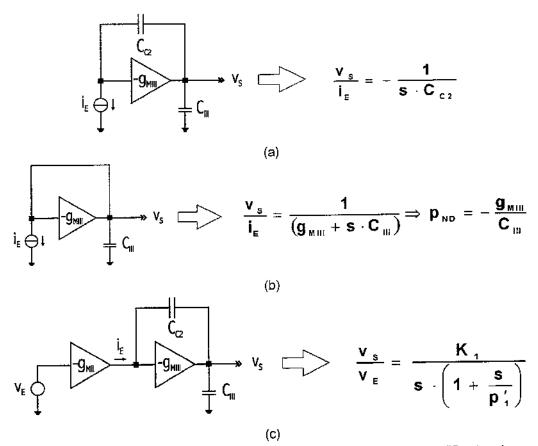

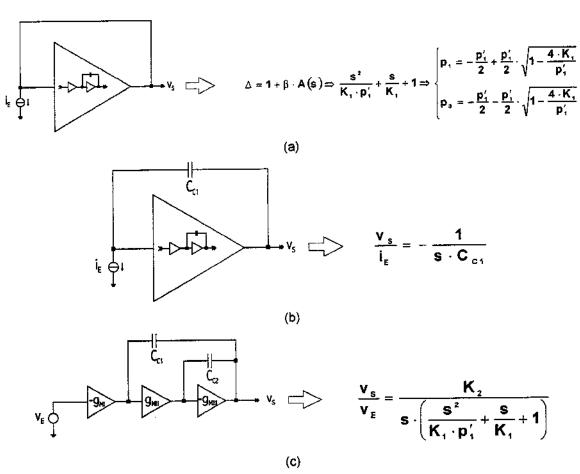

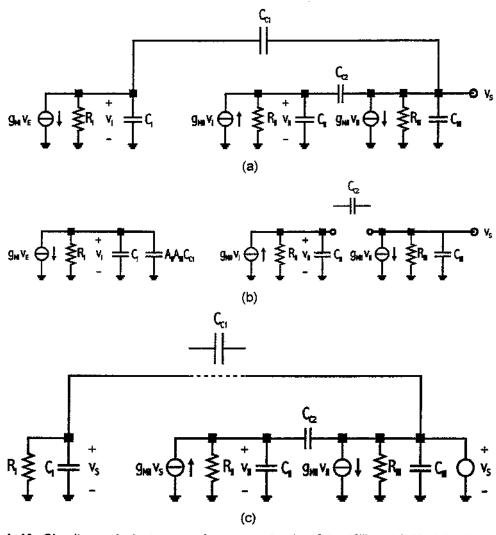

| Figura 4–4.  Obtenção da função de transferência simplificado do amplificador de dois estágios. (a) Função de transferência do integrador. (b) Efeito das freqüências além da freqüência do pólo dominante no caminho de realimentação. (c) Integrador com fonte de corrente substituída por um bloco de transcondutância.                                                                                                                                                                                                                                                                                 | 95       |

| Figura 4-5  Obtenção da função de transferência simplificado do amplificador de três estágios com compensação tipo Miller aninhada. (a) Efeito das freqüências além da freqüência do pólo dominante no caminho de realimentação. (b) Função de transferência do integrador. (c) Integrador com fonte de corrente substituída por um bloco de transcondutância.                                                                                                                                                                                                                                             | 97       |

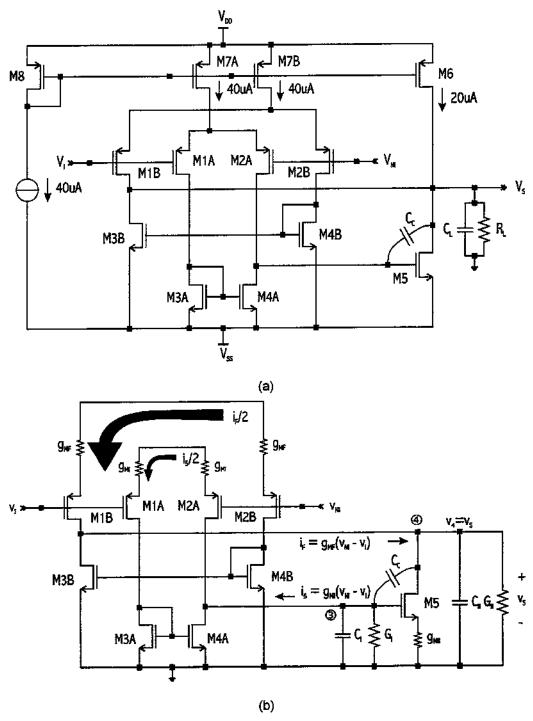

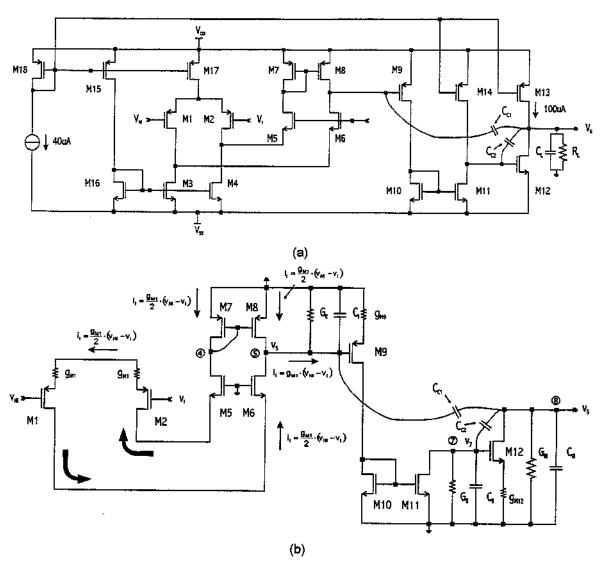

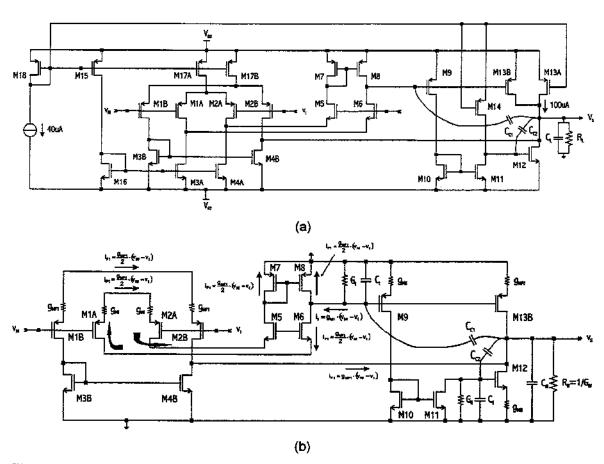

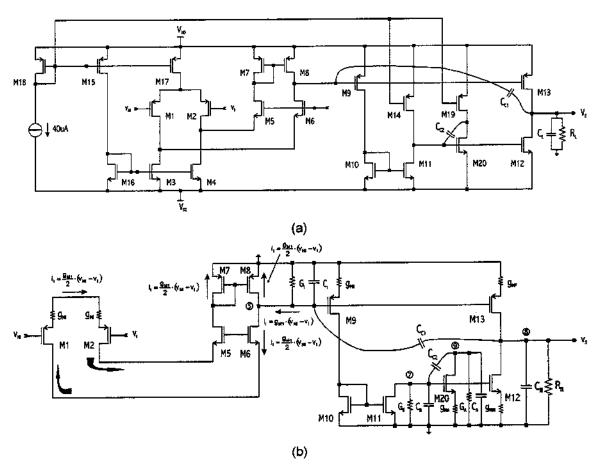

| Figura 4–6Amplificador de três estágios. (a) Compensação em freqüência tipo Miller aninhada. (b) Modelo de pequenos sinais do amplificador com compensação tipo Miller aninhada.                                                                                                                                                                                                                                                                                                                                                                                                                           | 98       |

| Figura 4–7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100      |

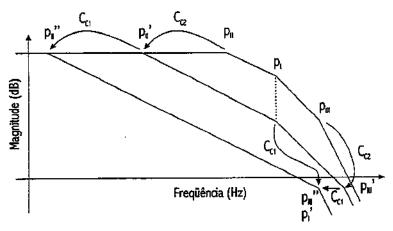

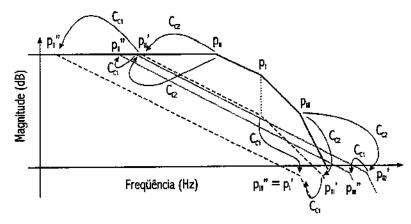

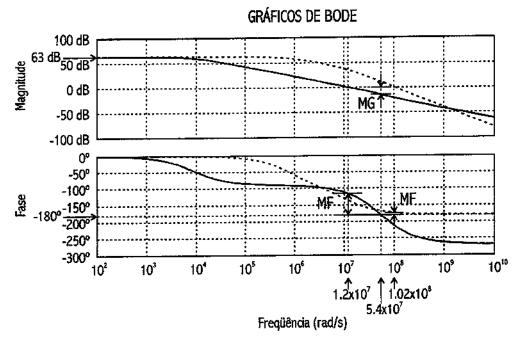

| Figura 4–8<br>Efeito da inclusão dos capacitores de compensação C <sub>C1</sub> e C <sub>C2</sub> no diagrama de Bode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 101      |

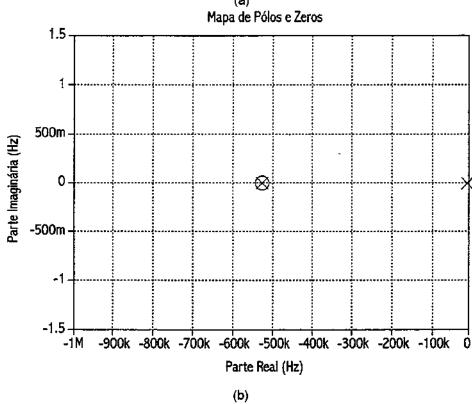

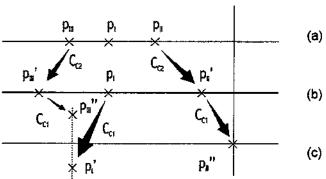

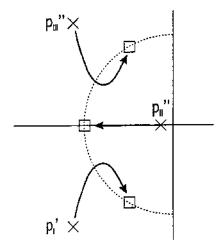

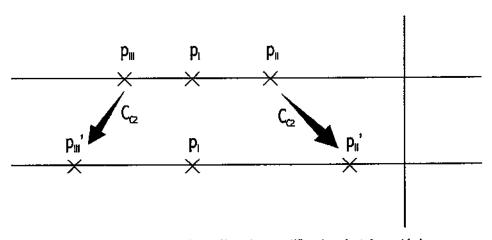

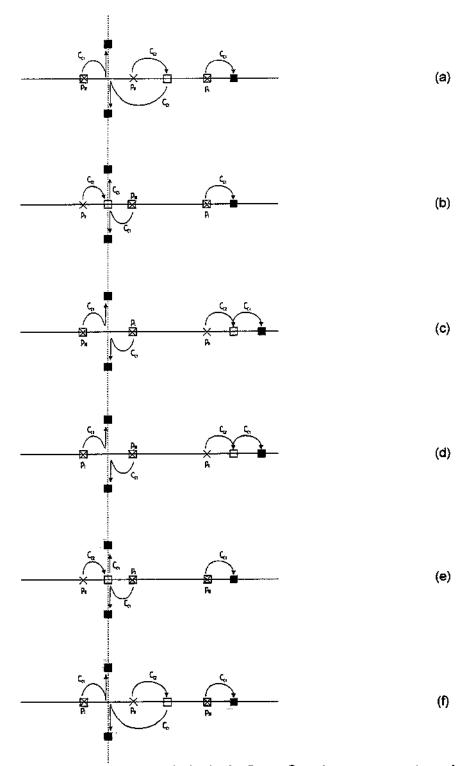

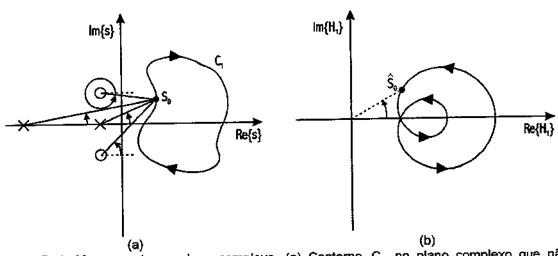

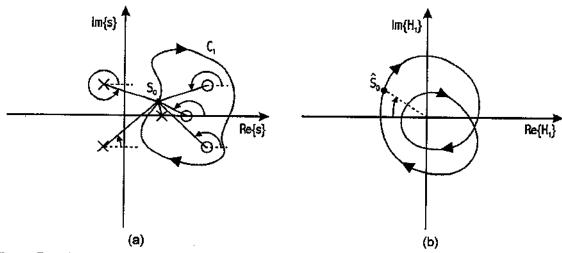

| Figura 4–9.  Movimentação dos pólos com a inclusão de $C_{C1}$ e $C_{C2}$ . A cruz representa posição inicial dos pólos. O quadrado vazio representa a posição intermediária dos pólos com a inclusão de $C_{C2}$ . O quadrado cheio representa a posição final dos pólos com a inclusão de $C_{C1}$ . (a) $p_{\parallel} < p_{\parallel} < p_{\parallel}$ . (b) $p_{\parallel} < p_{\parallel} < p_{\parallel}$ . (c) $p_{\parallel} < p_{\parallel}$ . (d) $p_{\parallel} < p_{\parallel} < p_{\parallel}$ . (e) $p_{\parallel} < p_{\parallel}$ . (f) $p_{\parallel} < p_{\parallel} < p_{\parallel}$ . | 102      |

| Figura 4–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 104      |

| Figura 4–11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109      |

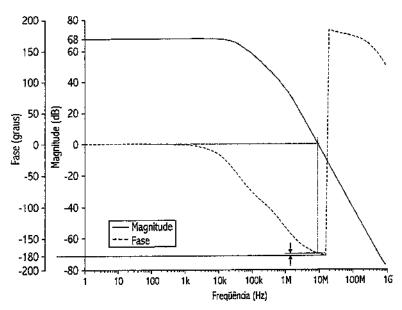

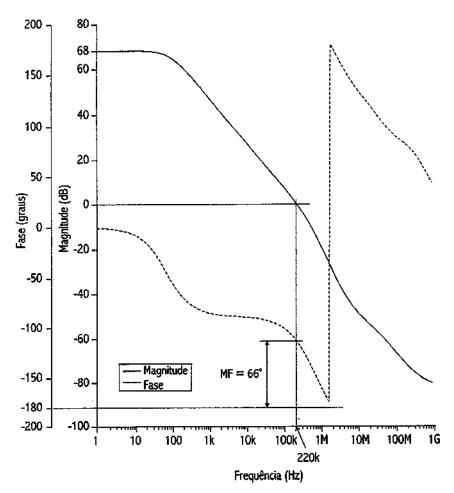

| Figura 4–12Diagrama de Bode simulado para o amplificador de três estágios em malha fechada.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109      |

| Figura 4–13                                                                                                                                                                                                        | 111 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 4–14.  Diagrama de blocos do amplificador com compensação tipo Miller aninhada com cancelamento de zero por resistor.                                                                                       | 112 |

| Figura 4–15                                                                                                                                                                                                        | 113 |

| Figura 4–16                                                                                                                                                                                                        | 117 |

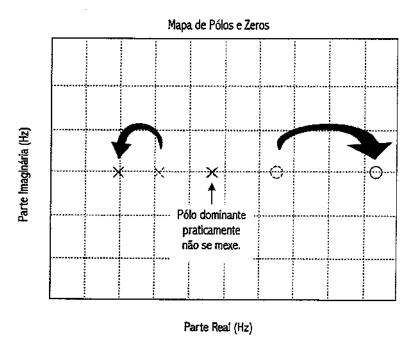

| Figura 4–17<br>Movimentação dos pólos do amplificador de três estágios com a inserção de C <sub>C1</sub> .                                                                                                         | 118 |

| Figura 4–18                                                                                                                                                                                                        | 119 |

| Figura 4–19  Diagramas de Bode antes e depois de $C_{C1}$ . (a) Diagrama de Bode do amplificador considerando apenas $C_{C2}$ . (b) Diagrama de Bode após a colocação de $C_{C1}$ e do estágio de corrente direta. | 120 |

| Figura 4–20                                                                                                                                                                                                        | 121 |

| Figura 4–21                                                                                                                                                                                                        | 123 |

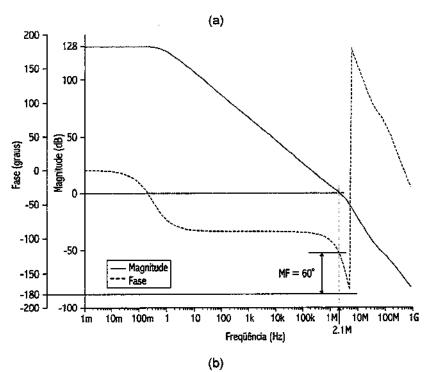

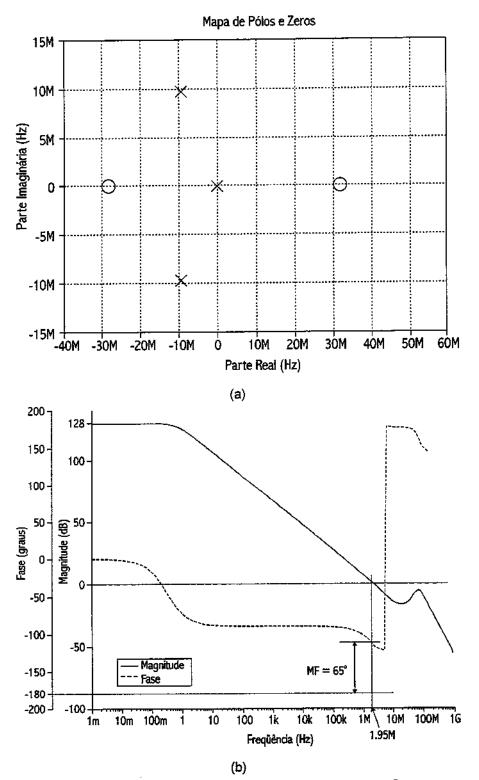

| Figura 4–22Simulações do amplificador com compensação tipo Miller aninhada com multi-caminho. (a) Posicionamento de pólos e zeros. (b) Diagrama de Bode.                                                           | 126 |

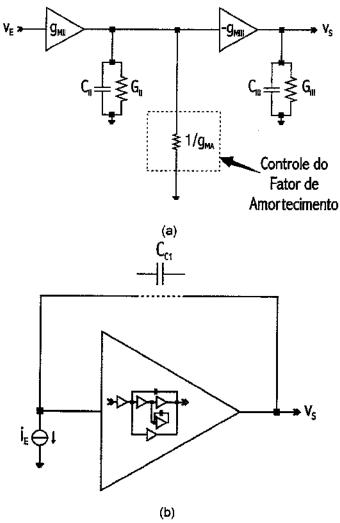

| Figura 4–23lmplementação sistemática do amplificador com compensação g <sub>M</sub> – C.                                                                                                                           | 128 |

| Figura 4–24                                                                                                                                                                                                        | 128 |

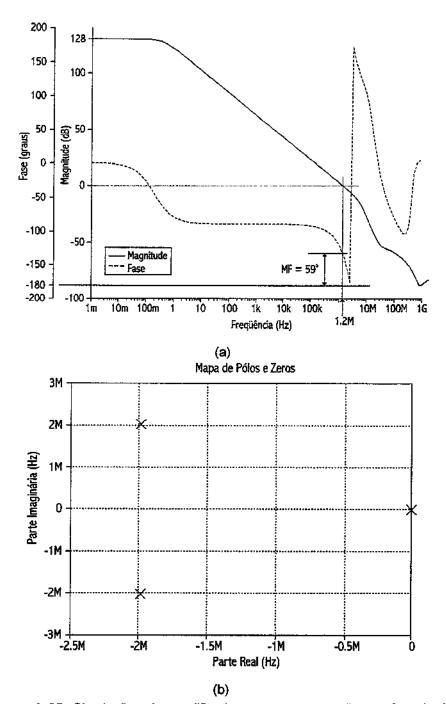

| Figura 4–25Simulações do amplificador com compensação em freqüência g <sub>M</sub> –C aninhada. (a)                                                                                                                | 132 |

| Diagrama de Bode. (b) Posicionamento de pólos e zeros.                                                                                                                                                             |     |

| Figura 4–27Simulações do amplificador com compensação em freqüência tipo Miller aninhada com antecipação. (a) Diagrama de Bode. (b) Posicionamento de pólos e zeros.                                                             | 139 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 4–28                                                                                                                                                                                                                      | 140 |

| Figura 4–29                                                                                                                                                                                                                      | 141 |

| Figura 4–30                                                                                                                                                                                                                      | 142 |

| Figura 4–31                                                                                                                                                                                                                      | 145 |

| Figura 4–32                                                                                                                                                                                                                      | 147 |

| $\begin{aligned} &p_{1} < p_{11} < p_{11}, & \text{ (b)} & p_{1} < p_{111} < p_{11}, & \text{ (c)} & p_{11} < p_{1} < p_{111}, & \text{ (d)} & p_{11} < p_{111} < p_{1}, & \text{ (e)} & p_{111} < p_{1} < p_{1} \end{aligned} $ |     |

| Figura 4–33                                                                                                                                                                                                                      | 152 |

| Figura 4–34                                                                                                                                                                                                                      | 153 |

| Tabela 5–1                                                                                                                                                                                                                       | 155 |

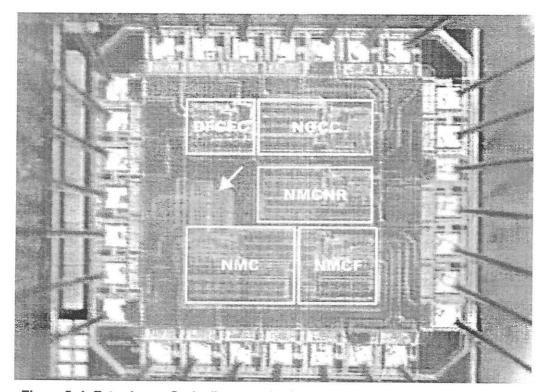

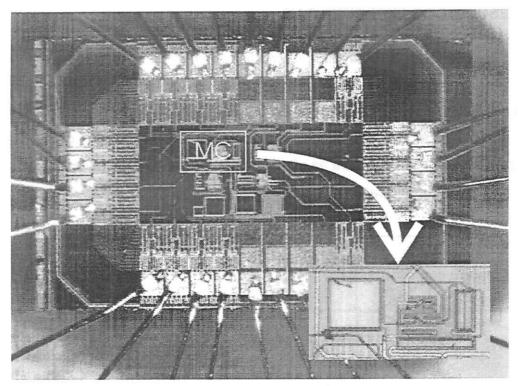

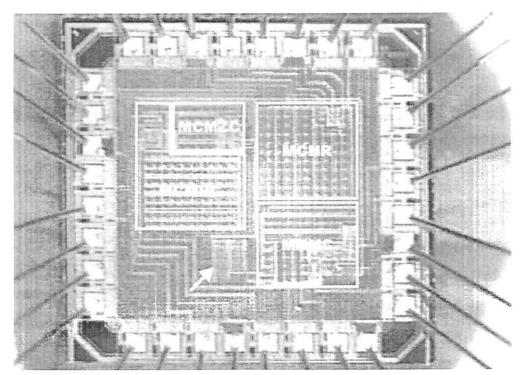

| Figura 5–1Fotomicrografia do <i>die</i> contendo cinco amplificadores.                                                                                                                                                           | 156 |

| Figura 5–2Fotomicrografia do <i>di</i> e contendo um amplificador.                                                                                                                                                               | 157 |

| Figura 5–3  Fotomicrografia do <i>die</i> contendo quatro amplificadores.                                                                                                                                                        | 157 |

| Figura 5–4Configuração dos circuitos de teste. (a) Seguidor de tensão. (b) Amplificador de tensão.                                                                                                                               | 158 |

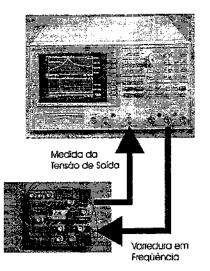

| Figura 5–5.  Arranjo de teste com o Network Analyser HP4195A e a placa de teste. O <i>chip</i> de teste encontra-se no meio da placa de teste.                                                                                   | 160 |

| Figura 5–6                                                                                                                                                                                | 161 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 5–7                                                                                                                                                                                | 162 |

| Figura 5–8Curvas de ganho para a configuração amplificador inversor.                                                                                                                      | 162 |

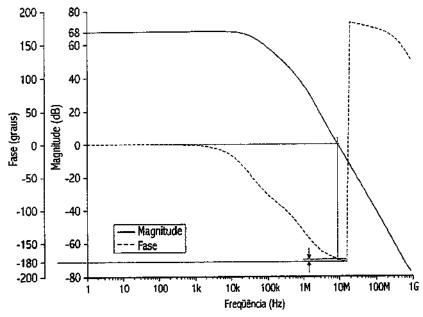

| Figura 5–9  Diagrama de Bode do amplificador com estrutura de compensação em freqüência tipo Miller com cancelamento de zero por multi-caminho para a configuração de seguidor de tensão. | 163 |

| Figura 5–10Curvas de ganho para a configuração amplificador inversor.                                                                                                                     | 164 |

| Figura 5–11                                                                                                                                                                               | 165 |

| Figura 5–12Curvas de ganho para a configuração amplificador inversor.                                                                                                                     | 166 |

| Figura 5–13                                                                                                                                                                               | 167 |

| Figura 5–14                                                                                                                                                                               | 168 |

| Figura 5–15                                                                                                                                                                               | 169 |

| Figura 5–16                                                                                                                                                                               | 170 |

| Figura 5–17                                                                                                                                                                               | 171 |

| Figura 5–18Curvas de ganho para a configuração amplificador inversor.                                                                                                                     | 172 |

| Figura 5–19                                                                                                                                                                               | 173 |

| Figura 520                                                                                                                                                                                | 174 |

| Figura 5–21                                                                                                                                                                               | 175 |

| Figura 5–22Curvas de ganho para a configuração amplificador inversor.                                                   | 176 |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 5–23                                                                                                             | 177 |

| Figura 5–24                                                                                                             | 178 |

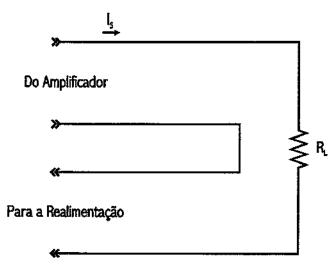

| Figura A–1                                                                                                              | 189 |

| Figura A–2                                                                                                              | 192 |

| Figura A–3                                                                                                              | 193 |

| Figura A–4Amostragem do sinal de tensão na saída na saída do amplificador.                                              | 193 |

| Figura A–5Amostragem do sinal de tensão na saída na saída do amplificador.                                              | 194 |

| Figura A–6                                                                                                              | 195 |

| Figura A–7Circuito com realimentação paralela-paralela.                                                                 | 197 |

| Figura A–8                                                                                                              | 198 |

| Figura A–9Calculo da razão de retorno.                                                                                  | 202 |

| Figura A–10Modelamento de ruído e distorções.                                                                           | 206 |

| Figura B–1                                                                                                              | 209 |

| e α=1.                                                                                                                  |     |

| Figura B–2                                                                                                              | 210 |

| entrada com frequência $\omega=\omega_2$ . (c) Sistema instável com sinal de entrada com frequência $\omega>\omega_2$ . |     |

| Figura B–3                                                                                                              | 212 |

| Figura B–4                                                                                           | 213 |

|------------------------------------------------------------------------------------------------------|-----|

| Figura B–5                                                                                           | 214 |

| Figura B–6                                                                                           | 215 |

| Figura B-7                                                                                           | 218 |

| Figura B-8                                                                                           | 219 |

| Figura B–9                                                                                           | 220 |

| Figura B–10                                                                                          | 221 |

| Figura B–11                                                                                          | 222 |

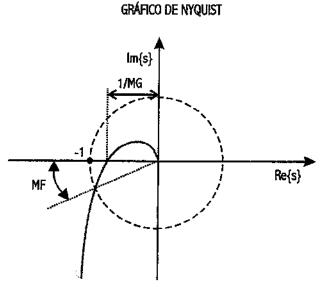

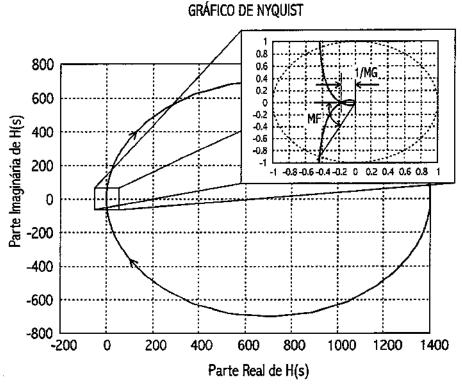

| Figura B–12Gráfico de Nyquist com a ausência do capacitor C <sub>C</sub> . A margem de fase é de 6°. | 223 |

| Figura B–13                                                                                          | 223 |

## NOTAÇÃO UTILIZADA

| SÍMBOLO                         | SIGNIFICADO                                                                      |

|---------------------------------|----------------------------------------------------------------------------------|

| Cc                              | Capacitância de compensação do amplificador de dois estágios                     |

| C <sub>C1</sub>                 | Capacitância de compensação da malha externa do<br>amplificador de três estágios |

| C <sub>C2</sub>                 | Capacitância de compensação da malha interna do<br>amplificador de três estágios |

| 9мі                             | Transcondutância associada ao primeiro estágio                                   |

| <b>9</b> мп                     | Transcondutância associada ao segundo estágio                                    |

| <b>9</b> мііі                   | Transcondutância associada ao terceiro estágio                                   |

| <b>9</b> мғі                    | Transcondutância de compensação de zero associada à entrada do estágio i         |

| <b>9</b> ма                     | Transcondutância do amplificador auxiliar                                        |

| $V_{NI}$                        | Entrada não-inversora                                                            |

| $V_{l}$                         | Entrada inversora                                                                |

| $C_{pi}$                        | Capacitância parasita associada ao nó і                                          |

| $C_i$                           | Capacitância total associada ao nó i                                             |

| <b>9</b> мі                     | Transcondutância do transistor i                                                 |

| <b>9</b> DSi                    | Condutância de saída do transistor i                                             |

| CL                              | Capacitância de carga                                                            |

| $R_{\!\scriptscriptstyle\perp}$ | Resistência de carga                                                             |

| TxS                             | Taxa de subida                                                                   |

| $V_{GS}$                        | Tensão porta-fonte                                                               |

| $V_{DS}$                        | Tensão dreno-fonte                                                               |

| $I_D$                           | Corrente de dreno quiescente                                                     |

| μN                              | Mobilidade do elétron livre                                                      |

| ħЬ                              | Mobilidade do elétron livre                                                      |

| $\lambda_{N}$                   | Fator de modulação de canal do transistor canal N                                |

| $\lambda_{P}$                   | Fator de modulação de canal do transistor canal P                                |

| $V_{TH}$                        | Tensão de limiar                                                                 |

W Largura de canal L Comprimento de canal Resistência incremental de saída associada ao estágio i roi GB Produto ganho-banda Ganho DC associado ao estágio i  $A_i$ Capacitância porta-fonte associada ao transistor i  $C_{GSi}$ Capacitância dreno-substrato associada ao transistor i Capacitância porta-dreno associada ao transistor i  $C_{GDi}$ Tensão dreno-fonte de saturação V<sub>DSsati</sub> Cii Capacitância entre os nós i e j Pólo associado ao nós i рí Zero associado aos nós i e j  $Z_{ij}$ Pólo associado à saída do primeiro estágio Pι Pólo associado à saída do segundo estágio ŊΠ Pólo associado à saída do terceiro estágio  $p_{iii}$ Gι Condutância associada à saída do primeiro estágio  $G_{II}$ Condutância associada à saída do segundo estágio Condutância associada à saída do terceiro estágio  $G_{III}$ Condutância de conversão tensão-corrente  $G_{I-II}$ Capacitância por área de porta-canal  $C_{ox}$ Ganho total do amplificador Αo Efeito de corpo γN Tensão correspondente ao nível de Fermi ΦfN Tensão fonte-substrato  $V_{SB}$

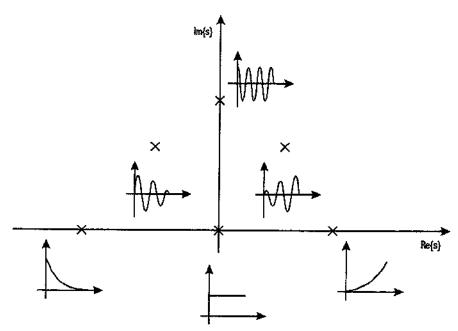

## Capítulo 1 Introdução

Três influências têm mudado, nos últimos tempos, a tendência dos projetos de circuitos integrados. A primeira é a crescente demanda por circuitos *mixed-signal* [1], [2] que integram circuitos analógicos e digitais em um mesmo substrato. A segunda influência diz respeito ao escalonamento, cada vez mais intenso, dos processos de fabricação [3], [4]. A terceira, e mais importante, é a necessidade crescente de operação em baixa tensão e com o mínimo possível de potência consumida, ou seja, baixa potência [5].

rate Herrick Co.

Para tentar lidar com essas novas tendências, um vasto universo de novos circuitos analógicos tem surgido, dentre os quais se destacam as novas estruturas de amplificadores operacionais [6], [7], que por sua vez trouxeram novos desafios relacionados à estabilidade em frequência.

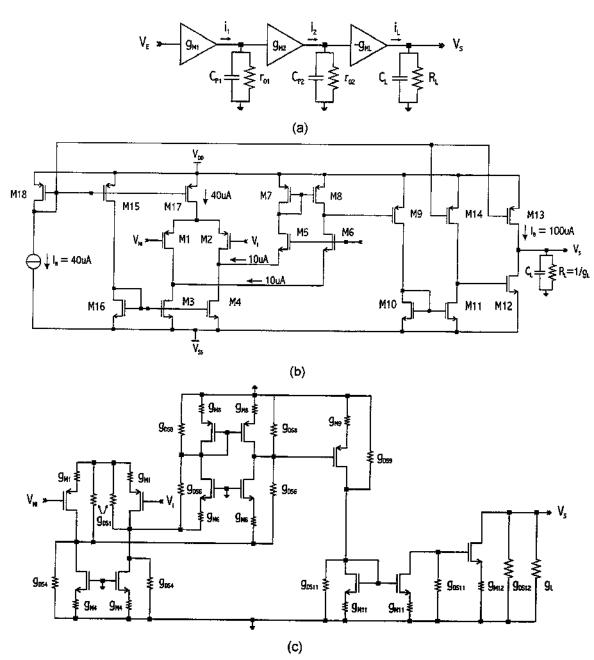

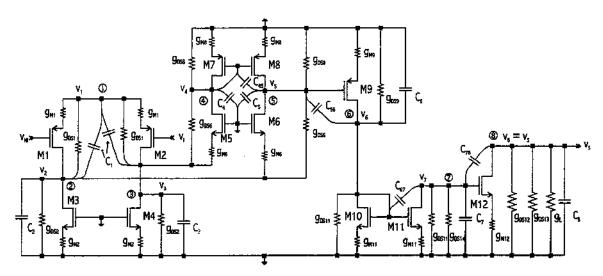

Foi com o intuito de entender e de aplicar mecanismos eficientes de compensação em freqüência no projeto de amplificadores operacionais que este trabalho foi desenvolvido. Para isso, foram projetados 10 amp-ops, cada um implementando um mecanismo de compensação em freqüência distinto: compensação Miller (MC), compensação Miller com compensação de zero por resistor (MCNR), compensação Miller com compensação de segundo pólo por zero de multi-caminho (MCMPC), compensação Miller com compensação de zero por multi-caminho (MCMZC), compensação Miller aninhada (NMC), compensação Miller aninhada com compensação de segundo pólo por zero de multi-caminho (MNMC), compensação Miller tipo g<sub>M</sub> – C aninhada (NGCC), compensação Miller aninhada com compensação de zero do semiplano direito por multi-caminho (NMCF) e, por fim, compensação Miller com controle de fator de amortecimento (DFCFC).

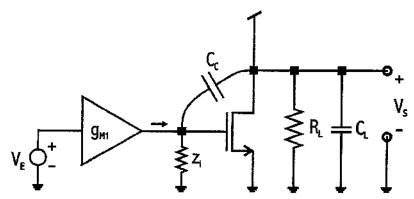

Foram estudados e implementados amplificadores de transcondutância [7], [8], [9] de dois e de três estágios. Para os amplificadores de dois estágios foi

estabelecida como carga uma associação paralela de R=100k $\Omega$  e C=50pF. Para os de três estágios, R=25k $\Omega$  e C=50pF.

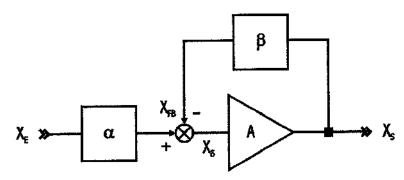

As estruturas de compensação citadas acima são resumidas e mostradas através de diagrama de blocos na Figura 1–1.

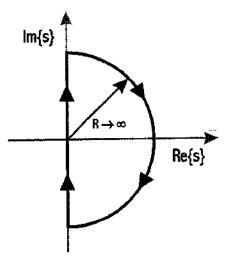

Este trabalho está dividido em 6 capítulos. Os métodos de compensação em freqüência são analisados de uma forma cronológica-evolutiva de forma a dar uma visão evolutiva do assunto. Após esta introdução, o Capítulo 2 trata do projeto de amplificadores de dois e três estágios, analisando seu comportamento tanto em baixas como em altas freqüências. O Capítulo 3 analisa as várias estruturas de compensação em freqüência de amplificadores de dois estágios. O Capítulo 4 utiliza dos conhecimentos adquiridos no capítulo anterior para analisar as estruturas de compensação em freqüência de amplificadores de três estágios. Nestes dois últimos capítulos foram estabelecidos critérios para se calcular os componentes das estruturas de compensação em função de parâmetros do circuito. O Capítulo 5 traz a implementação e os resultados experimentais. No Capítulo 6 é apresentada a conclusão do trabalho. Finalmente, o Apêndice A e o Apêndice B fazem uma revisão de teoria de rede, modelamento e análise na freqüência pelos métodos de Bode e de Nyquist, mostrando como aplicá-los a amplificadores operacionais.

Figura 1-1. Estruturas de compensação em freqüência. (a) MC. (b) MCNR. (c) MCMPC. (d) MCMZC. (e) NMC. (f) NMCNR. (g) MNMC. (h) NGCC. (i) NMCF. (j) DFCFC.

# Capítulo 2 Amplificador Operacional de Transcondutância

Diferente dos amplificadores operacionais1 comerciais, os amplificadores implementados neste trabalho, que serviram como prova material dos estudos realizados, não incorporam um estágio de saída, seja ele do tipo seguidor de mais apropriado considerá-los Sendo assim. seria tensão ou inversor. OTA Operational inglês, transcondutância (em amplificadores de Transconductance Amplifier), tal como é comum vê-los citado na literatura. Porém, ao conectar uma carga no seu terminal de saída e considerarmos a tensão sobre a carga como sendo a variável de saída, estes amplificadores assumem a forma de um amplificador de tensão, podendo, portanto, manter a denominação de ampop.

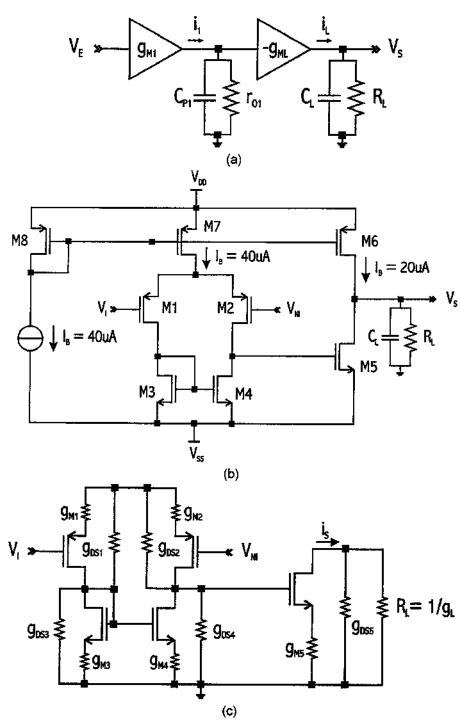

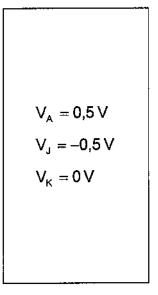

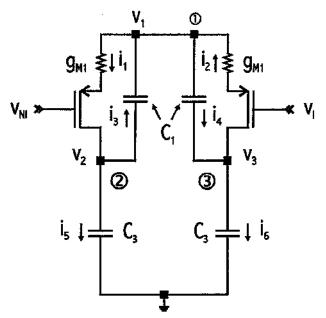

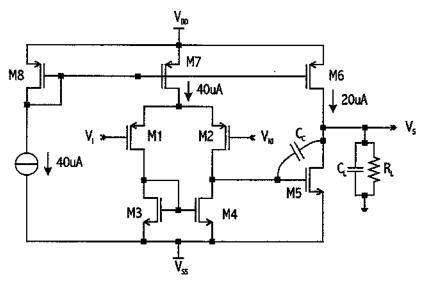

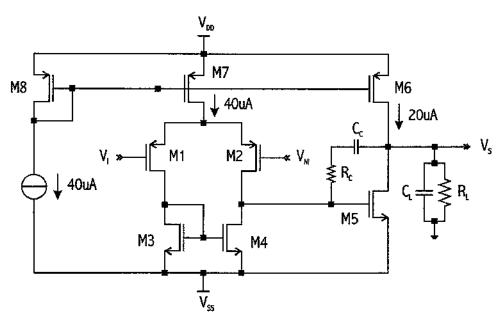

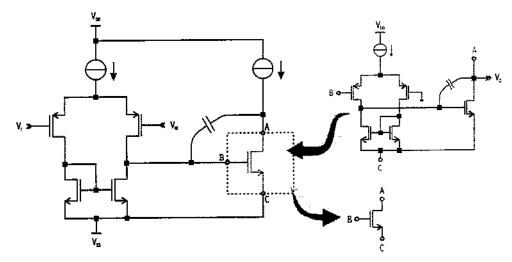

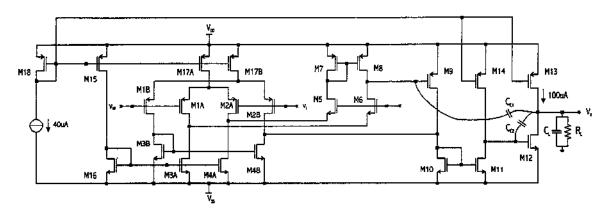

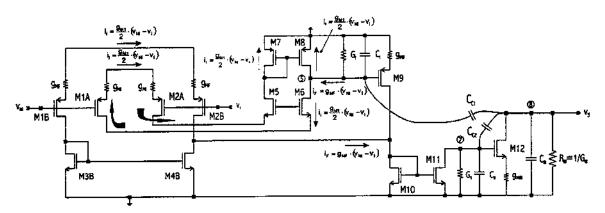

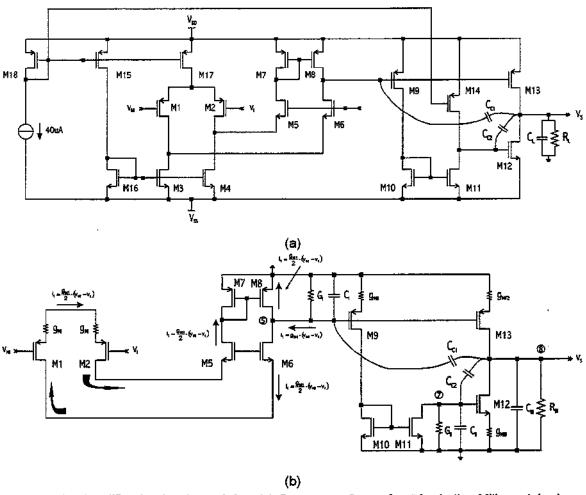

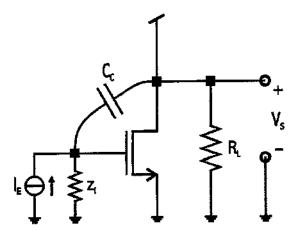

## 2.1 AMPLIFICADOR OPERACIONAL DE DOIS ESTÁGIOS

O amp-op de dois estágios é constituído de um par diferencial de entrada, que perfaz o primeiro estágio de ganho, e o segundo estágio de ganho que é composto por um simples transistor polarizado em fonte comum [8], [10]. As Figura 2–1a, Figura 2–1b e Figura 2–1c apresentam, respectivamente, o diagrama de blocos, a topologia e o circuito equivalente de pequenos sinais para baixas freqüências do amplificador de dois estágios.

Foram projetados três amplificadores deste tipo. Nestes três casos foram estabelecidas as seguintes especificações: tensão simétrica de  $\pm 2\,\text{V}$ , ganho mínimo em baixas freqüências de  $60\,\text{dB}$ , ou seja  $1.000\,\text{V}_{\text{V}}$ , e produto ganho-

O nome amplificador operacional é atribuido a Ragazzini et al. [11] que demonstrou que um amplificador eletrônico ideal de alto ganho pode realizar operações arbitrárias na variável laplaciana s.

banda, *a priori*, de 1 MHz para uma carga resistiva de 100kΩ em paralelo com um capacitor de 50 pF. As especificações do processo são dadas em [12] e [13].

Figura 2-1. Amplificador de dois estágios. (a) Diagrama de blocos. (b) Esquema elétrico do amplificador (c) Modelo de pequenos sinais em baixas freqüências.

## 2.1.1 POLARIZAÇÃO

O estágio de saída foi polarizado com uma corrente de  $20\,\mu\text{A}$ , o suficiente para garantir a excursão de  $\pm 2\,\text{V}$  sobre a carga resistiva de  $100\,k\Omega$ . Projetando esta corrente para os transistores de entrada temos, então,  $20\,\mu\text{A}$  em cada transistor PMOS do par diferencial de entrada. Desta forma, a polarização do par diferencial é dada por uma fonte de  $40\,\mu\text{A}$ . Apesar desta polarização garantir ganhos de tensão moderados e excursão de saída, a taxa de subida na saída é prejudicado. Para a carga capacitiva de  $50\,\text{pF}$  e sem compensação temos uma taxa de subida (TxS) dado por

$$||_{S_{MAX}}| = C_L \cdot TxS \Rightarrow TxS = 0.4 \frac{V}{\mu s}.$$

(2-1)

O valor baixo da taxa de subida na saída é uma conseqüência de um compromisso entre o valor do capacitor de compensação - portanto, a área ocupada - e consumo de potência. Como será visto, o valor do capacitor de compensação é inversamente proporcional ao valor da transcondutância do transistor de saída. Assim, para aumentar da taxa de subida é necessário aumentar a corrente do transistor de saída e, portanto o consumo. Por outro lado, o aumento da corrente faz aumentar sua transcondutância e, deste modo, diminuir o capacitor de compensação. Assim, o equilíbrio entre baixo consumo e área ocupada pelo capacitor de compensação depende das especificações do projeto. Neste projeto foi optado pelo favorecimento de um baixíssimo consumo em detrimento da área e da velocidade.

Para o primeiro estágio foram definidas as polarizações mostradas na Figura 2-2 a seguir e resumidas na Tabela 2-1.

Figura 2–2. Definição dos pontos de polarização para o estágio de entrada do amp-op de dois estágios.

**Tabela 2–1.** Definição dos valores de tensão do estágio de entrada para o amp-op de dois estágios.

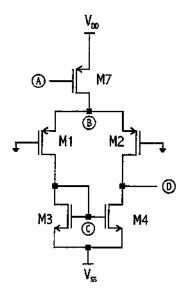

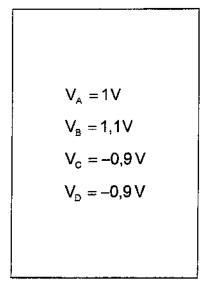

A tensão no ponto A em relação ao terra foi escolhida de forma a polarizar a fonte de corrente M7 na saturação. A tensão dreno-fonte de saturação em M7 é dada por  $\left|V_{DS_{SAT}M7}\right| = V_{GSM7} - V_{TH} = 1 - 0.85 = 150\,\text{mV}$ . Isso permitiria que a tensão no ponto B fosse até aproximadamente 1,8 V. Porém, para a corrente de  $40\,\mu\text{A}$  e tensão  $V_{GSM1} = -1.8\,\text{V}$  em M1 o ganho do primeiro estágio sería reduzido, pois diminui-se o valor do comprimento W dos transistores M1 e M2. Deste modo optou-se por um valor de tensão menor no ponto B de modo a garantir uma transcondutância maior em M1 e M2. O valor da tensão no ponto B foi de 1,1V em relação ao terra. A tensão no ponto C deve ser a menor possível. No entanto, como esta tensão é a tensão de porta do transistor M3 e M4 ela está limitada a tensão de limiar do transistor NMOS. Foi escolhido  $V_{C} = -0.9\,\text{V}$  em relação ao terra para este ponto.

A escolha da maior tensão possível no ponto B e da menor tensão possível no ponto C é guiada pela maximização da excursão da tensão de modo comum. Porém, o projeto não se fixou de forma rigorosa nesse requisito, pois o interesse era obter um alto ganho de tensão em detrimento a outros requisitos.

Para garantir que a tensão no ponto D seja igual a tensão no ponto C, ou seja,  $V_D = -0.9 \, \text{V}$  em relação ao terra, o tamanho dos transistores M1 e M2 do par diferencial e M3 e M4 do espelho de corrente é feito igual.

Considerando o casamento entre M1 e M2, e M3 e M4 perfeito, e portanto  $g_{M1} = g_{M2}$  e que  $g_{M3} = g_{M4}$ , podemos calcular as dimensões dos transistores e o ganho de pequenos sinais do primeiro estágio.

Deste modo, para a equação do transistor  $I_D = \frac{1}{2} \cdot \mu_N \cdot C_{OX} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})^2$  [8], [14] ou  $I_D = K' \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})^2$ , onde K' = K/2, sendo K chamado de parâmetro de transcondutância [12] com unidade de  $A/V^2$  e para uma alimentação simétrica de  $\pm 2\,V$ , temos para os transistores M1 e M2 do par diferencial PMOS

$$\frac{W_{M1}}{L_{M1}} = \frac{W_{M2}}{L_{M2}} = \frac{I_D}{K' \cdot (V_{GS} - V_{TH})^2} = \frac{20 \cdot 10^{-6}}{40 \cdot 10^{-6} / 2 \cdot (1,05 - 0,825)^2} \approx \frac{20}{1}.$$

(2-2)

Para o par M3 e M4 do espelho de corrente NMOS temos

$$\frac{W_{M3}}{L_{M3}} = \frac{W_{M4}}{L_{M4}} = \frac{20 \cdot 10^{-6}}{110 \cdot 10^{-6} / 2 \cdot (1, 1 - 0, 88)^2} \approx \frac{7,5}{1}.$$

(2-3)

E para a fonte de corrente PMOS, formada pelo transistor M7 que polariza o estágio de entrada temos

$$\frac{W_{M7}}{L_{M7}} = \frac{40 \cdot 10^{-6}}{40 \cdot 10^{-6} / 2 \cdot (0.93 - 0.822)^2} \approx \frac{171}{1}.$$

(2-4)

Para M7, o valor de V<sub>GS</sub> obtido na simulação foi 0,93 V em vez do valor de 1V definido na Tabela 2–1. Apesar da pequena diferença em relação ao valor

nominal - apenas 4% - a diferença nas dimensões do transistor é substancial - 78%.

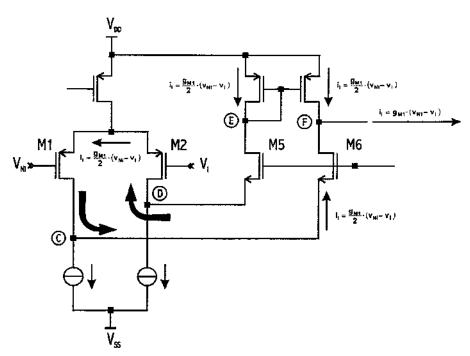

O segundo estágio possui uma polarização que é conseqüência da polarização do primeiro estágio. A Figura 2–3 mostra as tensões de polarização para o segundo estágio do amplificador e a Tabela 2–2 resume os valores dessas tensões.

Figura 2–3. Definição dos pontos de polarização para o segundo estágio do ampop de dois estágios.

Tabela 2-2. Definição dos valores de tensão do estágio de entrada para o amp-op de dois estágios.

Para garantir uma margem de fase em torno de 60° o segundo pólo  $\omega_{P2}$  deve estar por volta de uma oitava acima da freqüência de ganho unitário [9]. Para uma freqüência de ganho unitário  $\omega_o = 2 \cdot \pi \cdot 1 \cdot 10^6 \, \text{rad/s}$ , teríamos  $\omega_{P2} = 2 \cdot \pi \cdot 2 \cdot 10^6 \, \text{rad/s}$  e seria necessário ter uma corrente mínima em M5 dada pela expressão [8]

$$I_{DM5_{MIN}} = -\frac{C_{D}}{\left(\frac{1}{V_{GSM5} - V_{THN}}\right) \cdot \left(\frac{3}{\omega_{P2}} + \frac{2 \cdot L_{M7}^{2}}{\mu_{N} \cdot (V_{GSM7} - V_{THN})}\right)},$$

(2-5)

onde  $\mu_N$  é a mobilidade dos portadores do tipo N. A capacitância  $C_D$  é a capacitância vista do dreno do transistor M5. Neste caso, temos a capacitância vista do dreno aproximadamente igual capacitância da carga, ou seja,  $C_D \approx C_L = 50\,\text{pF}$ . Fazendo as substituições obtemos uma corrente mínima de  $l_{DM5} \approx 7\,\mu\text{A}$ . Portanto adotamos  $l_{DM5} = 20\,\mu\text{A}$ , pois assim

$$\frac{W_{M5}}{L_{M5}} = \frac{W_{M4}}{L_{M4}} = \frac{W_{M3}}{L_{L3}} = \frac{7.5}{1}.$$

(2-6)

Para que a tensão de saída seja zero é necessário que a corrente da fonte formada pelo transistor M6 seja igual a corrente de M5, ou seja,  $20\,\mu\text{A}$ . Para isso, basta fazer  $W_{\text{M6}}$  aproximadamente metade da dimensão de  $W_{\text{M7}}$ , pois ambos os transistores possuem o mesmo valor de tensão entre porta e fonte. Da mesma forma, para que M8 também conduza  $40\,\mu\text{A}$  com o mesmo  $V_{\text{GS}}$  de M7, as dimensões de M8 e M7 devem ser iguais. Portanto

$$\frac{W_{M6}}{L_{M6}} = \frac{V_{M7}}{2} = \frac{92.5}{1}$$

(2-7)

е

$$\frac{W_{M8}}{L_{M2}} = \frac{W_{M7}}{L_{M7}} = \frac{185}{1}.$$

(2-8)

## 2.1.2 GANHO EM BAIXA FREQÜÊNCIA

O ganho do estágio de entrada é projetado para ser muito maior que o ganho do segundo estágio. Este critério visa garantir um ganho DC moderado, já que o ganho do segundo estágio é baixo devido à baixa resistência de saída proporcionada pela carga.

O ganho em baixas freqüências para o primeiro estágio é o ganho de um par diferencial tendo como carga um espelho de corrente e alimentado por uma fonte de corrente. O par diferencial, juntamente com o espelho de corrente, transforma tensão diferencial de entrada em uma variação de corrente. Para pequenos sinais, essa variação é linear e proporcional a tensão de entrada. A variação de corrente gerada flui por uma resistência de saída incremental no dreno de M4 e M2. Esse fluxo de corrente sobre a resistência de saída gera uma tensão incremental de saída. A relação entre as variações da tensão de saída e as variações da tensão de entrada resulta no ganho de pequenos sinais do primeiro estágio do circuito da Figura 2–1b. Assim, o ganho A, do primeiro estágio em baixas freqüências é dado por [9]

$$A_{1} \cong \frac{g_{M1}}{g_{DS2} + g_{DS4}}, \tag{2-9}$$

onde  $g_{M1}$  é a transcondutância do transistor M1,  $g_{DS2}$  é a condutância de saída do transistor M2 e  $g_{DS4}$  é a condutância de saída do transistor M4. O valor de  $A_1$  considera o par diferencial PMOS e o espelho de corrente NMOS perfeitamente casados, além de considerar a resistência de saída da fonte de corrente M7 infinita. Esta aproximação é muito boa para cálculos práticos e apresenta uma boa concordância com as simulações.

Em baixas freqüências, o segundo estágio não carrega a saída do primeiro estágio. Desta forma, para saber o ganho DC total, basta calcular o ganho do segundo estágio e multiplicar pelo valor do ganho do primeiro.