## Universidade Estadual de Campinas Faculdade de Engenharia Elétrica e de Computação

# Um Ambiente Computacional para apoio ao Ensino de Estrutura de Processamento

#### Adriane Bellé

Orientador: José Raimundo de Oliveira

Dissertação de Mestrado apresentada à Faculdade de Engenharia Elétrica e de Computação como parte dos requisitos para obtenção do título de Mestre em Engenharia Elétrica. Área de concentração: Engenharia de Computação.

#### Banca Examinadora:

Prof. Dr. José Raimundo de Oliveira (Presidente)

Prof. Dr. Mauricio Araujo Dias (FCT/UNESP)

Prof. Dr. Furio Damiani (FEEC/UNICAMP)

Campinas - SP Dezembro de 2011

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA E ARQUITETURA - BAE - UNICAMP

Bellé, Adriane

B415a

Um ambiente computacional para apoio ao ensino de estrutura de processamento / Adriane Bellé. --Campinas, SP: [s.n.], 2011.

Orientador: José Raimundo de Oliveira. Dissertação de Mestrado - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Engenharia de computador. 2. Simulação (Computadores). 3. Emuladores (Programas de computador). 4. Microprocessadores (Projetos e construção). 5. Computadores (Estudo e ensino). I. Oliveira, José Raimundo de. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. III. Título.

Título em Inglês: A computational environment to support the teaching of structure processing

Palavras-chave em Inglês: Computer engineering, Computer (Simulation), Emulators (Design abd construction), Computers (Estudy and teaching)

Área de concentração: Engenharia de Computação

Titulação: Mestre em Engenharia Elétrica

Banca examinadora: Maurício Araujo Dias, Furio Damiani

Data da defesa: 22-12-2011

Programa de Pós Graduação: Engenharia Elétrica

#### COMISSÃO JULGADORA - TESE DE MESTRADO

Candidata: Adriane Bellé

Data da Defesa: 22 de dezembro de 2011

Título da Tese: "Um Ambiente Computacional para apoio ao Ensino de Estrutura

de Processamento"

Prof. Dr. José Raimundo de Oliveira (Presidente):

Prof. Dr. Mauricio Araujo Dias: Mauricio

Prof. Dr. Furio Damiani: \_

## Resumo

A tecnologia dos processadores tem crescido rapidamente nos últimos anos. Em contrapartida, o ensino de arquitetura de computadores tem dificuldade de acompanhar esta evolução. Os livros textos e as aulas ainda utilizam de recursos estáticos que precisam de longas explicações. Esta dinâmica torna-se incompatível, inclusive, com as experiências, como usuários, de muitos alunos.

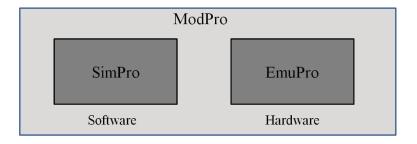

Este trabalho propõe o desenvolvimento de um ambiente computacional (*framework*) para apoio ao ensino de arquitetura de processamento, denominado MODPRO. A ideia é dispor de módulos que possam ser interligados formando diversas possíveis estruturas de processamento. Desta maneira, o professor pode desenvolver junto aos alunos e expor de forma visual (utilizando de animações) desde componentes básicos até estruturas de processamento mais avançadas.

O MODPRO é composto por um simulador, denominado SIMPRO o qual exibe de forma animada, passo a passo, ou em tempo real, o fluxo de dados e de sinais dentro da estrutura de processamento estudada. O SIMPRO foi desenvolvido em linguagem Javascript e utiliza recursos de *Cascading Style Sheets*, podendo, ainda, ser acessado pela web. O MODPRO ainda é composto por um emulador, chamado EMUPRO que contém os mesmos módulos do SIMPRO. O seu diferencial está relacionado ao fato de ter sido totalmente desenvolvido em hardware, utilizando a ferramenta QUARTUS II da Altera. Com este recurso, os alunos podem, em laboratório, validar a estrutura desenvolvida em classe.

Por serem modulares, tanto o simulador SIMPRO quanto o emulador EMUPRO permitem que novos recursos (módulos) possam ser adicionados, permitindo assim, o ensino e o estudo de diferentes estruturas de processamento.

**Palavras-chave**: Ensino de Arquitetura de Computador; Simulação e Emulação de Processador; FPGA.

## **Abstract**

The processor technology has grown rapidly in recent years. In constrast, the teaching of computer architectures has difficulties to follow such evolution. The books and the classes still use static resources which need long explanations. This dynamic becomes incompatible with the experiences desirable for most students.

This work proposes the development of a computational environment (framework) to support the teaching of processing architecture, which is called MODPRO. The idea is to have modules that can be connected together forming several possible processing structures. Therefore, the professor can develop different scenarios with the students and expose in a visual way (using animation features), from basic components to more advanced processing structures.

The ModPro consists of a simulator, called SIMPro which displays (in an animated form), step by step or in real-time, the data flow and the signal processing within the structure being studied. The SIMPro was developed in JavaScript language, uses Cascading Style Sheets and can be accessed via web. The ModPro also consistes in an emulator called EMUPro, which contains the same modules of SIMPro. Its differential is related to the fact that it has been developed entirely in hardware, using the development environment QUARTUS II from Altera. Basically, with the features of ModPro, the students can validate, in laboratory, the frameworks and the processing structures developed during the classes.

Because they are modular, both the simulator SIMPRO and the emulator EMUPRO allow the addition of new features (modules), besides allowing the teaching and the study of different processing structures.

**Keywords**: Computer Architecture Teaching; Processor simulation and emulation; FPGA.

## Agradecimentos

A Deus, pela minha vida, pela minha família e por me ensinar que a persistência é sem dúvida, o caminho para uma grande conquista.

Ao meu querido orientador, Prof. José Raimundo de Oliveira, pela confiança, dedicação, orientação, pelos ensinamentos e acima de tudo, pela humildade e por ser um grande exemplo de Professor. Serei eternamente grata.

Aos meus queridos pais, Leda e Attílio, razão do meu viver, pelo carinho, amor, apoio, por acreditarem em mim e não me deixarem nunca desistir. Tudo o que tenho, e o que sou devo à vocês. Obrigada por este amor incondicional, amo vocês.

Aos meus irmãos, Edivane e Edivar e minha cunhada Raquel, por vibrarem comigo, me apoiarem e estarem sempre ao lado, meu muito obrigada.

Aos meus sobrinhos, Laura e Leonardo, meus grandes amores, que encheram minha vida de alegria e amor.

Aos meus queridos amigos, que me acompanharam por todos esses anos, Wilfredo Puma, Rafael Pasquini, Tatiana Pazeto, Adler Silva, Jeremias Machado, Leandro Monteiro, Antonio Carlos Rodrigues, Letícia Ritnner, Tatiane Bonfim e em especial a Dra. Margareth Brigante (*in memoriam*) obrigada de coração, por tudo o que vocês fizeram por mim, pela amizade e pelos ótimos momentos compartilhados juntos.

Aos demais amigos e colegas de pós-graduação, com quem eu tive o privilégio de conviver. Em especial, meus amigos de laboratório André Delai e Filipe Fazanaro, por todo apoio e ajuda incondicional, que vocês dedicaram à mim.

Aos funcionários da Elétrica, Sr. Hélio, Noêmia, Edson, Juraci, em especial à Gislaine, pela dedicação, e a todos, que sempre me trataram com muito carinho e sempre estiveram à disposição para tudo o que eu precisei.

Agradeço à todos da comunidade FEEC, desde a diretoria e aos funcionários responsáveis pela limpeza, que sempre se preocuparam em proporcionar um ambiente agradável para os estudos.

A Nina, minha cachorrinha, minha companheira fiel de todos os momentos.

Aos meus queridos e amados pais, Leda e Attílio, meus irmãos Edivar e Edivane, minha cunhada Raquel e meus sobrinhos Laura e Leonardo

# Sumário

| Li | Lista de Figuras |                                       |     |  |

|----|------------------|---------------------------------------|-----|--|

| Li | sta de           | e Tabelas                             | xiv |  |

| G  | lossár           | io                                    | XV  |  |

| 1  | Intr             | rodução                               | 1   |  |

|    | 1.1              | Motivação                             | 1   |  |

|    | 1.2              | Objetivos                             | 2   |  |

|    | 1.3              | Organização do Trabalho               | 2   |  |

| 2  | Con              | nceitos Básicos                       | 4   |  |

|    | 2.1              | Arquitetura de Computadores           | 4   |  |

|    |                  | 2.1.1 Arquitetura de <i>Princeton</i> | 4   |  |

|    |                  | 2.1.2 Arquitetura de <i>Harvard</i>   | 6   |  |

|    | 2.2              | Computadores Paralelos                | 7   |  |

|    |                  | 2.2.1 Processadores <i>Multicore</i>  | 9   |  |

|    | 2.3              | Processamento Digital de Sinais       | 10  |  |

|    | 2.4              | Unidade de Controle                   | 11  |  |

|    | 2.5              | Simulação e Emulação de Processadores | 12  |  |

|    |                  | 2.5.1 Simulador                       | 13  |  |

|    |                  | 2.5.2 Emulador                        | 13  |  |

|    | 2.6              | Resumo do capítulo                    | 14  |  |

| 3  | O A              | mbiente Computacional Proposto        | 15  |  |

|    | 3.1              | O Ambiente ModPro                     | 15  |  |

|    | 3.2              | Unidade de controle                   | 17  |  |

|    |                  | 3.2.1 RI - Registrador de Instrução   | 17  |  |

SUMÁRIO x

|   |            | 3.2.2                                                                                                        | Decodificador de Instruções                                                                                                                                                                                                                                                                                                                                                 | 17                                                                       |

|---|------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|   |            | 3.2.3                                                                                                        | LUT - Look-up Table                                                                                                                                                                                                                                                                                                                                                         | 17                                                                       |

|   |            | 3.2.4                                                                                                        | Registrador de estado                                                                                                                                                                                                                                                                                                                                                       | 18                                                                       |

|   |            | 3.2.5                                                                                                        | Sistema de relógio                                                                                                                                                                                                                                                                                                                                                          | 18                                                                       |

|   |            | 3.2.6                                                                                                        | MIR - Registrador de micro-instrução                                                                                                                                                                                                                                                                                                                                        | 18                                                                       |

|   | 3.3        | Operac                                                                                                       | dores                                                                                                                                                                                                                                                                                                                                                                       | 18                                                                       |

|   |            | 3.3.1                                                                                                        | Unidade Lógica e Aritmética - <b>ULA</b>                                                                                                                                                                                                                                                                                                                                    | 19                                                                       |

|   |            | 3.3.2                                                                                                        | Multiplicador/Divisor                                                                                                                                                                                                                                                                                                                                                       | 19                                                                       |

|   | 3.4        | Regist                                                                                                       | radores                                                                                                                                                                                                                                                                                                                                                                     | 19                                                                       |

|   |            | 3.4.1                                                                                                        | Registradores contadores                                                                                                                                                                                                                                                                                                                                                    | 19                                                                       |

|   |            | 3.4.2                                                                                                        | Registrador de passagem                                                                                                                                                                                                                                                                                                                                                     | 19                                                                       |

|   |            | 3.4.3                                                                                                        | Registrador de propósito geral                                                                                                                                                                                                                                                                                                                                              | 20                                                                       |

|   | 3.5        | Barran                                                                                                       | nentos                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                       |

|   |            | 3.5.1                                                                                                        | Barramento Bidirecional                                                                                                                                                                                                                                                                                                                                                     | 20                                                                       |

|   |            | 3.5.2                                                                                                        | Barramento Unidirecional                                                                                                                                                                                                                                                                                                                                                    | 20                                                                       |

|   | 3.6        | Memó                                                                                                         | ria                                                                                                                                                                                                                                                                                                                                                                         | 20                                                                       |

|   | 3.7        | Resum                                                                                                        | no do capítulo                                                                                                                                                                                                                                                                                                                                                              | 21                                                                       |

| 4 | Exe        | mplos d                                                                                                      | e Simulação e Emulação                                                                                                                                                                                                                                                                                                                                                      | 22                                                                       |

|   | 4.1        | _                                                                                                            | volvimento do SIMPRO                                                                                                                                                                                                                                                                                                                                                        | 22                                                                       |

|   |            |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                             |                                                                          |

|   |            | 4.1.1                                                                                                        | Conjunto de Instruções                                                                                                                                                                                                                                                                                                                                                      | 23                                                                       |

|   |            | 4.1.1<br>4.1.2                                                                                               |                                                                                                                                                                                                                                                                                                                                                                             | 23<br>24                                                                 |

|   |            |                                                                                                              | Conjunto de Instruções                                                                                                                                                                                                                                                                                                                                                      |                                                                          |

|   |            | 4.1.2                                                                                                        | Memória Externa                                                                                                                                                                                                                                                                                                                                                             | 24                                                                       |

|   |            | 4.1.2<br>4.1.3                                                                                               | Memória Externa                                                                                                                                                                                                                                                                                                                                                             | 24<br>24                                                                 |

|   | 4.2        | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                                                                             | Memória Externa                                                                                                                                                                                                                                                                                                                                                             | 24<br>24<br>25                                                           |

|   | 4.2        | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                                                                             | Memória Externa   Decodificador   Conjunto de Sinais de Controle   Execução de uma Instrução                                                                                                                                                                                                                                                                                | 24<br>24<br>25<br>25                                                     |

|   | 4.2        | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1                                                          | Memória Externa                                                                                                                                                                                                                                                                                                                                                             | 24<br>24<br>25<br>25<br>27                                               |

|   |            | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1<br>Simula                                                | Memória Externa                                                                                                                                                                                                                                                                                                                                                             | 24<br>24<br>25<br>25<br>27<br>29                                         |

|   | 4.3        | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1<br>Simula                                                | Memória Externa  Decodificador  Conjunto de Sinais de Controle  Execução de uma Instrução  ação da Arquitetura de <i>Princeton</i> no SIMPRO  Exemplo de Execução de uma Instrução  ação da Arquitetura de <i>Harvard</i> no SIMPRO                                                                                                                                         | 24<br>24<br>25<br>25<br>27<br>29<br>32                                   |

|   | 4.3<br>4.4 | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1<br>Simula                                                | Memória Externa  Decodificador  Conjunto de Sinais de Controle  Execução de uma Instrução  ação da Arquitetura de <i>Princeton</i> no SIMPRO  Exemplo de Execução de uma Instrução  ação da Arquitetura de <i>Harvard</i> no SIMPRO  ação da Unidade MAC no SIMPRO                                                                                                          | 24<br>24<br>25<br>25<br>27<br>29<br>32<br>33                             |

|   | 4.3<br>4.4 | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1<br>Simula<br>Deserve                                     | Memória Externa  Decodificador  Conjunto de Sinais de Controle  Execução de uma Instrução  ação da Arquitetura de <i>Princeton</i> no SIMPRO  Exemplo de Execução de uma Instrução  ação da Arquitetura de <i>Harvard</i> no SIMPRO  ação da Unidade MAC no SIMPRO  volvimento do EMUPRO                                                                                    | 244<br>245<br>25<br>27<br>29<br>32<br>33<br>34                           |

|   | 4.3<br>4.4 | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1<br>Simula<br>Deserve<br>4.5.1                            | Memória Externa  Decodificador  Conjunto de Sinais de Controle  Execução de uma Instrução  ação da Arquitetura de <i>Princeton</i> no SIMPRO  Exemplo de Execução de uma Instrução  ação da Arquitetura de <i>Harvard</i> no SIMPRO  ação da Unidade MAC no SIMPRO  volvimento do EMUPRO  Componente Registrador                                                            | 244<br>245<br>255<br>277<br>299<br>322<br>333<br>344<br>355              |

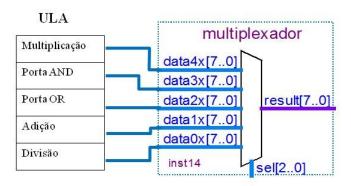

|   | 4.3<br>4.4 | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1<br>Simula<br>Deserv<br>4.5.1<br>4.5.2                    | Memória Externa  Decodificador  Conjunto de Sinais de Controle  Execução de uma Instrução  ação da Arquitetura de <i>Princeton</i> no SIMPRO  Exemplo de Execução de uma Instrução  ação da Arquitetura de <i>Harvard</i> no SIMPRO  ação da Unidade MAC no SIMPRO  volvimento do EMUPRO  Componente Registrador  Componentes da Unidade Lógica e Aritmética                | 244<br>245<br>255<br>277<br>299<br>323<br>334<br>353<br>37               |

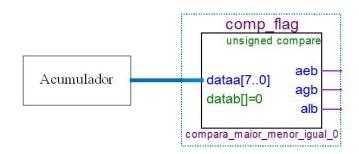

|   | 4.3<br>4.4 | 4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>Simula<br>4.2.1<br>Simula<br>Simula<br>Deserv<br>4.5.1<br>4.5.2<br>4.5.3 | Memória Externa  Decodificador  Conjunto de Sinais de Controle  Execução de uma Instrução  ação da Arquitetura de <i>Princeton</i> no SIMPRO  Exemplo de Execução de uma Instrução  ação da Arquitetura de <i>Harvard</i> no SIMPRO  ação da Unidade MAC no SIMPRO  volvimento do EMUPRO  Componente Registrador  Componentes da Unidade Lógica e Aritmética  Multiplexador | 244<br>245<br>255<br>277<br>299<br>322<br>333<br>344<br>355<br>377<br>39 |

| SUMÁRIO | xi |

|---------|----|

|---------|----|

|    |           | 4.5.7    | Componente Memória Externa                | 4 |  |

|----|-----------|----------|-------------------------------------------|---|--|

|    | 4.6       | Emula    | ção da Arquitetura de Princeton no EMUPRO | 4 |  |

|    | 4.7       | Resum    | o do capítulo                             | ۷ |  |

| 5  | Conclusão |          |                                           |   |  |

|    | 5.1       | Trabal   | hos Futuros                               | 2 |  |

|    |           | 5.1.1    | Exemplo de Arquitetura Paralela no ModPro | 2 |  |

|    |           | 5.1.2    | Interface para o SIMPRO                   | 2 |  |

| D. | ·fonôn    | oios Dil | nlingráficas                              | _ |  |

# Lista de Figuras

| 2.1  | Arquitetura de <i>Von Neumann</i>                                         | 5  |

|------|---------------------------------------------------------------------------|----|

| 2.2  | Execução de uma instrução na arquitetura de <i>Princeton</i>              | 6  |

| 2.3  | Ilustração da arquitetura de <i>Harvard</i>                               | 7  |

| 2.4  | Execução de uma instrução na arquitetura de <i>Harvard</i>                | 7  |

| 2.5  | Arquitetura SISD                                                          | 8  |

| 2.6  | Arquitetura SIMD                                                          | 8  |

| 2.7  | Arquitetura MISD                                                          | 9  |

| 2.8  | Arquitetura MIMD                                                          | 9  |

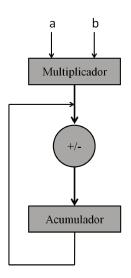

| 2.9  | Unidade MAC                                                               | 11 |

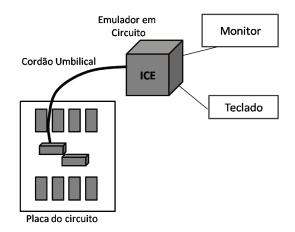

| 2.10 | Desenvolvimento com Emulador em circuito                                  | 14 |

| 3.1  | Ilustração do framework proposto                                          | 16 |

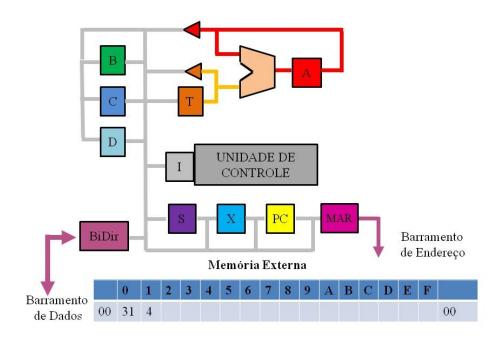

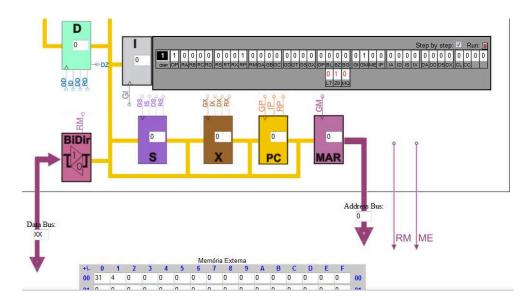

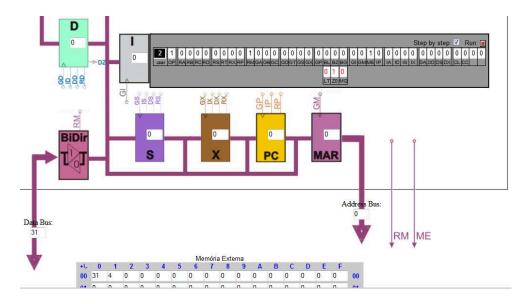

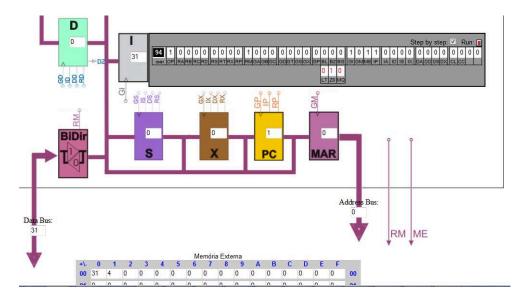

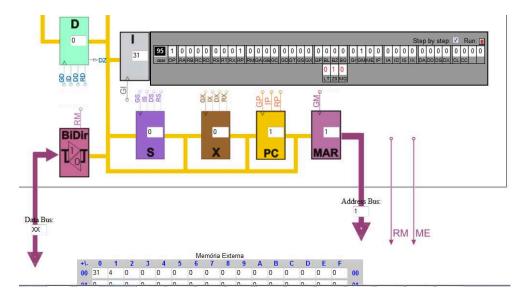

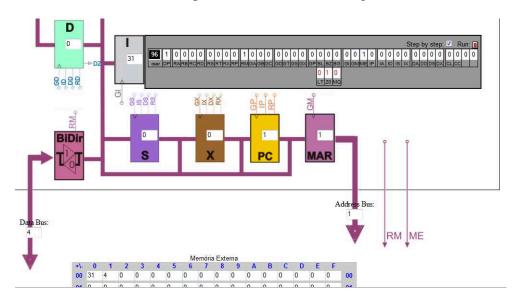

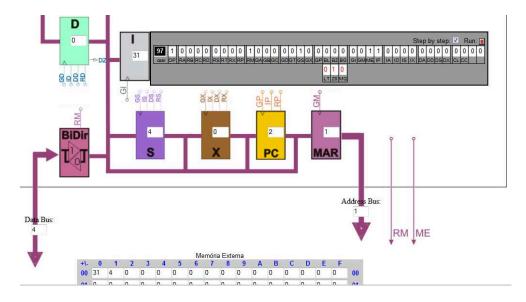

| 4.1  | Simulação da Arquitetura de Princeton no SimPro                           | 28 |

| 4.2  | Simulação da Instrução LOADI S - Conteúdo do PC                           | 29 |

| 4.3  | Simulação da Instrução LOADI S - Leitura do Barramento pelo MAR           | 30 |

| 4.4  | Simulação da Instrução LOADI S - Leitura do Barramento pelo RI            | 30 |

| 4.5  | Simulação da Instrução LOADI S - Incremento do PC                         | 31 |

| 4.6  | Simulação da Instrução LOADI S - Leitura do Barramento pelo MAR           | 31 |

| 4.7  | Simulação da Instrução LOADI S - Leitura do Barramento pelo Registrador S | 32 |

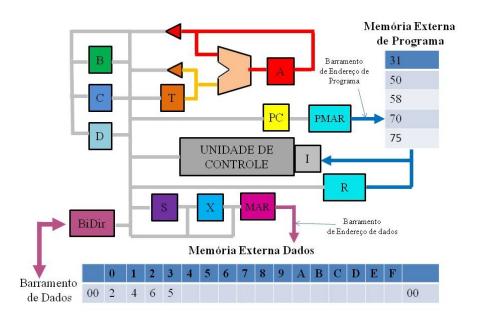

| 4.8  | Simulação da Arquitetura de Harvard no SimPro                             | 32 |

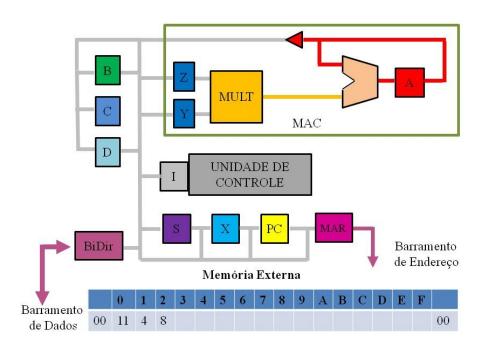

| 4.9  | Simulação da Estrutura MAC no SIMPRO                                      | 33 |

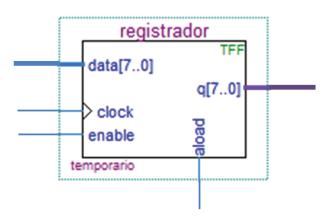

| 4.10 | Registrador TFF                                                           | 35 |

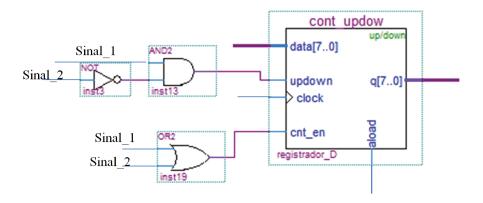

| 4.11 | Registrador UpDown                                                        | 36 |

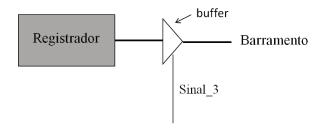

| 4.12 | Buffer de Leitura                                                         | 36 |

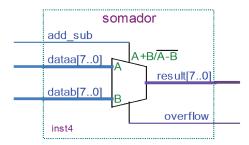

| 4.13 | Somador e Subtrador                                                       | 37 |

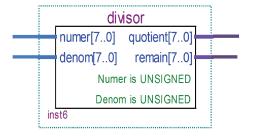

| 4.14 | Divisor                                                                   | 38 |

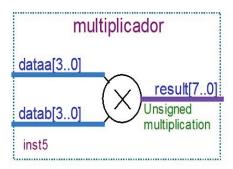

| 4.15 | Multiplicador                                                             | 38 |

| xiii |

|------|

|      |

| 4.16       | Portas Lógicas AND e OR                               | 38 |

|------------|-------------------------------------------------------|----|

| 4.17       | Multiplexador                                         | 39 |

| 4.18       | Circuito de Exceção do Acumulador                     | 40 |

| 4.19       | Circuito de Carregamento do PC                        | 40 |

| 4.20       | Decodificador de Instruções                           | 41 |

| 4.21       | Look-Up Table                                         | 41 |

| 4.22       | Memória Externa                                       | 42 |

| 4.23       | Emulação da Arquitetura de <i>Princeton</i> no SIMPRO | 43 |

| <b>5</b> 1 | Simulação de Estrutura SIMD                           | 46 |

| 5.1        | Simulação da Estrutura SIMD                           | 40 |

| 5.2        | Simulação da Estrutura MIMD                           | 46 |

|            |                                                       |    |

# Lista de Tabelas

| 4.1 | Definindo o conjunto de instruções        | 24 |

|-----|-------------------------------------------|----|

| 4.2 | Memória externa                           | 24 |

| 4.3 | Decodificador de instruções               | 25 |

| 4.4 | Conjunto de sinais de controle            | 26 |

| 4.5 | Exemplo de uma instrução executada na LUT | 27 |

## Glossário

- PMAR Registrador de Endereço de Memória de Programa (do inglês *Program Memory Address Register*)

- BDM Background Debug Mode

- CPU Unidade Central de Processamento (do inglês Central Processing Unit)

- CSS Cascading Style Sheets

- DSP Processamento Digital de Sinais (do inglês Digital Signal Processing)

- FPGA Field Programmable Gate Array

- ICE Emulador em Circuito (do inglês *In circuit emulator*)

- JTAG Joint Test Action Group

- LUT Tabela de Endereços (do inglês *Look-Up Table*)

- MAC Unidade de Multiplicação e Acumulação (do inglês Multiply-Accumulate)

- MAR Registrador de Endereço de Memória (do inglês Memory Address Register)

- MIMD Múltiplas Instruções, Múltiplos Dados (do inglês Multiple Instruction Multiple Data)

- MIR Registrador de Micro-Instruções (do inglês *Micro-Instruction Register*)

- MIR Registrador de micro-instruções (do inglês *Micro-Instruction Register*)

- MISD Múltiplas Instruções, Único Dado (do inglês Multiple Instruction Single Data)

- PC Contador de Programa (do inglês *Program Counter*)

- RI Registrador de Instrução (do inglês *Instruction Register*)

GLOSSÁRIO xvi

- RI Registrador de Instruções (do inglês *Joint Test Action Group*)

- ROM Memória somente de Leitura (do inglês *Read Only Memory*)

- S Apontador de Pilha (do inglês *Stack Pointer*)

- SIMD Única Instrução, Múltiplos Dados (do inglês Single Instruction Multiple Data)

- SISD Única Instrução, Único Dado (do inglês Single Instruction Single Data)

- ULA Unidade Lógica e Aritmética (do inglês Arithmetic Logic Unit)

# Capítulo 1

# Introdução

Com o objetivo de melhorar o ensino de estruturas de processamento e de prover aos alunos um conhecimento sobre as novas tecnologias, este trabalho propõe uma ferramenta didática para o ensino de um processador, utilizando um ambiente gráfico para ilustrar o funcionamento de uma determinada estrutura de processamento.

## 1.1 Motivação

A tecnologia investida nos computadores atualmente está se desenvolvendo muito rapidamente quando o assunto é o processador. Os processadores disponíveis no mercado possuem características únicas que atendem a diferentes públicos que não levam em consideração somente o seu custo/benefício mas, também, alguns outros fatores tais como a velocidade do processador, desempenho em se tratando do tempo para a execução de uma determinada tarefa e a quantidade de memória. Tais fatores podem ser considerados de extrema importância no momento de se adquirir um computador.

Com base nesse avanço tecnológico dos processadores, o ensino de arquitetura de computadores, exige uma constante atualização pois, conforme a tecnologia se desenvolve, novos conceitos acabam surgindo. Por outro lado, os professores tem dificuldade de acompanhar esta evolução pois os livros textos usados como referências e a forma como as aulas são ministradas utilizam de recursos estáticos que precisam de longas explicações. Esta dinâmica é incompatível, inclusive, com as experiências, como usuários, de muitos alunos.

O cenário que existe hoje dentro de uma sala de aula, mostra que os estudantes estão expostos a vários conceitos ou características que surgem, relacionadas à tecnologia de processamento, e começam a usufruir dessa tecnologia sem mesmo, antes, entender como esses conceitos são aplicados nas novas estruturas de processamento que estão surgindo.

1.2 Objetivos 2

Diante disso, a preocupação que existe é como apresentar os conceitos relacionados à estrutura de processamento para permitir uma rápida compreensão pelo aluno, bem como para permitir uma rápida adaptação a novas estruturas que emergem.

## 1.2 Objetivos

Dentro do contexto de ensino de arquitetura de computadores, o objetivo deste trabalho consiste em desenvolver um ambiente computacional, um *framework* didático, voltado para o ensino de arquitetura de processamento, sendo esse ambiente denominado de MODPRO. Este *framework* é formado por uma biblioteca composta de módulos específicos (tais como, registradores, ULA -Unidade Lógica e Aritmética (do inglês *Arithmetic Logic Unit*), memória ... etc) que podem ser conectados por um barramento para formar diversas estruturas de processamento. Assim sendo, o professor poderá mostrar, através de blocos gráficos e animação, os componentes básicos que compõe o processador e, também, estruturas de processamento mais avançadas.

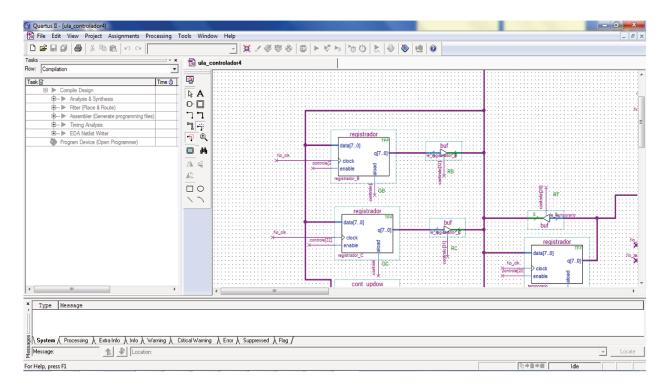

O MODPRO é composto por um simulador, denominado SIMPRO, o qual foi desenvolvido em software utilizando a linguagem JavaScript e, através dele, é possível acompanhar de forma animada a execução de uma instrução realizada pelo processador, bem como os sinais de controle responsáveis por ativar a execução da instrução. O emulador, chamado EMUPRO, também faz parte do *framework*. Ele foi desenvolvido em hardware utilizando o ambiente QUARTUS II, versão 9.1 da Altera, sendo a emulação realizada através de um FPGA (*Field Programmable Gate Array*) [1].

## 1.3 Organização do Trabalho

De modo a facilitar a sua compreensão, este trabalho foi dividido como se segue.

No Capítulo 1, apresenta-se a introdução e a contextualização do trabalho desenvolvido, descrevendo o problema abordado e os respectivos objetivos.

No Capítulo 2, são abordados alguns conceitos básicos, aplicados a este estudo, tais como as arquiteturas *Princeton* e *Harvard*, Computadores paralelos, Processador Digital de Sinal, unidade MAC, arquitetura multicore, simuladores, emuladores e unidades de controle, destacando as principais características de cada um dos tópicos.

O Capítulo 3 faz uma descrição do *framework* proposto, denominado de SIMPRO, descrevendo o seu processo de desenvolvimento bem como o conjunto de componentes que fazem parte desse simulador.

No Capítulo 4, é descrito o desenvolvimento do emulador EMUPRO e seus principais componentes. Além disso, são apresentados alguns exemplos de simulação das arquiteturas de *Princeton*, de

Harvard e a unidade MAC e, também, exemplos de emulações aplicada à arquitetura de Princeton.

No Capítulo 5, são apresentadas as conclusões e as discussões relacionadas ao trabalho bem como sugestões de trabalhos futuros, sinalizando a simulação da arquitetura paralela e o desenvolvimento de uma interface para o SimPro.

# Capítulo 2

## **Conceitos Básicos**

Este capítulo introduz os principais conceitos utilizados nos demais capítulos deste trabalho. São aqui apresentadas as principais características das arquiteturas conhecidas como de *Princeton* e de *Harvard*, identificando suas principais diferenças. Uma introdução à classificação de Flynn, que ordena os sistemas de computadores em categorias, será feita. Esta classificação é muito utilizada para caracterizar os sistemas com capacidade de processamento paralelo. Também são introduzidas algumas características da arquitetura multicore (quando se utiliza dois ou mais processadores em um único *chip*), muito utilizada nos recentes processadores comerciais. Outro conceito aqui destacado é a Unidade de Multiplicação e Acumulação (MAC)(do inglês *Multiply-Accumulate*) presente em todos processadores digitais de sinais (DSP) do mercado. Um destaque especial, é dado à estrutura de controle da unidade central de processamento. Por último, serão discutidos os conceitos de simulação e emulação de sistemas de computadores.

## 2.1 Arquitetura de Computadores

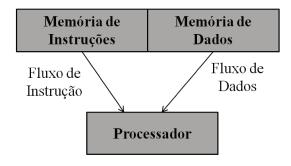

A arquitetura de *Princeton* e a arquitetura *Harvard* consistem nas duas principais classes de arquiteturas de computadores existentes. A mais importante diferença está relacionada na maneira como a memória é acessada. Ao longo dessa seção, será realizada uma breve descrição sobre estas arquiteturas.

## 2.1.1 Arquitetura de Princeton

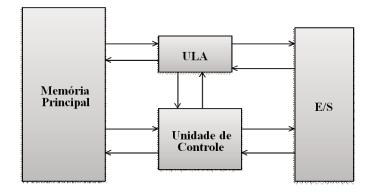

A arquitetura de *Princeton*, também conhecida como máquina de *Von Neumann*, ainda está presente na maioria dos computadores digitais. Esta arquitetura é composta por cinco unidades básicas: a memória principal, a unidade lógica e aritmética, a unidade de controle, e o equipamento de entrada

e saída [2]. Na Figura 2.1, tem-se uma ilustração destas unidades e suas interconexões.

Fig. 2.1: Arquitetura de Von Neumann.

As unidades básicas da arquitetura *Princeton* podem ser descritas da seguinte maneira [3]:

- A memória principal é responsável por armazenar os dados e as instruções;

- A *ULA* realiza operações sobre os dados.

- A unidade de controle é a responsável pela interpretação e execução das instruções na memória;

- O equipamento de entrada e saída (E/S) é acionado pela unidade de controle.

Von Neumann definiu alguns pontos para esta arquitetura [3]:

- O computador deve conter uma unidade especializada para desempenhar as operações aritméticas de adição, subtração, divisão e multiplicação, que constitui a unidade lógica e aritmética;

- As operações podem ser executadas sequencialmente, através da unidade de controle;

- Qualquer dispositivo que precisar executar sequências de operações longas, precisa ter uma memória associada;

- O dispositivo precisa ter unidades para transferir informações de entrada e saída.

A característica básica da arquitetura de *Princeton* é que os dados e as instruções compartilham a mesma memória sendo acessada por um único barramento que também é utilizado para a transferência de dados e busca de instruções. Pelo fato de utilizarem o mesmo barramento, a transferência e a busca devem ser escalonadas e, consequentemente, não podem ser executadas ao mesmo tempo [4, 5, 6].

O ciclo de busca e execução é realizado através da CPU, que obtém a instrução da memória e a decodifica para identificar qual operação será realizada, executando a respectiva instrução. A instrução é composta por duas partes: OPCODE, que especifica a operação que será executada, e o

operando que informa quais dados serão operados [4].

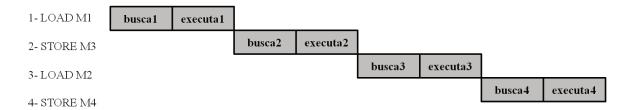

A execução de uma instrução é realizada através (1) de sua busca na memória, (2) da decodificação realizada através da unidade de controle e (3) da execução da instrução. Quando ocorrer uma execução que requer dados (os quais possam ser lidos ou escritos na memória), esses somente serão obtidos após a conclusão da instrução em execução [4]. Baseando-se nisso, é possível considerar o conjunto de instruções de acesso à memória representadas por LOAD e STORE os quais são ilustrados na Figura 2.2.

Fig. 2.2: Execução de uma instrução na arquitetura de *Princeton*.

A instrução STORE M3, somente poderá ser executada após a completa execução da instrução anterior, LOAD M1. Dessa forma, fica claro que as instruções são executadas sequencialmente na arquitetura de *Princeton*, ou seja, somente quando a instrução atual concluir sua execução é que a próxima poderá iniciar o ciclo de busca e execução.

A arquitetura de *Princeton* apresenta um gargalo entre a CPU - Unidade Central de Processamento (do inglês *Central Processing Unit*) e a memória, devido ao fato de os dados e as instruções compartilharem a mesma memória e, além disso, utilizar o mesmo barramento o que acarreta em uma diminuição no tráfego (*throughput*) dos dados [4].

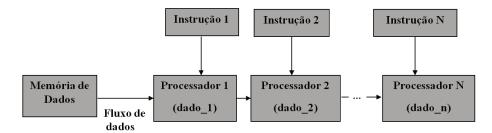

#### 2.1.2 Arquitetura de Harvard

A arquitetura de *Harvard* foi criada na Universidade de Harvard dentro do primeiro projeto de computador, denominado Harvard Mark I, o qual foi coordenado por Howard Aiken em 1944, em parceria da IBM e da marinha norte americana. Os protótipos iniciais faziam uso de válvulas e suas operações internas eram controladas por relés [4].

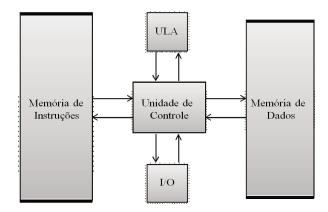

A principal característica da arquitetura de *Harvard* consiste na existência de duas memórias distintas, sendo uma aplicada às instruções e a outra aos dados [4, 6, 5]. Pelo fato de possuírem barramentos distintos, torna-se possível o acesso simultâneo, permitindo realizar a busca de instruções e de dados simultaneamente [4]. Na Figura 2.3, tem-se uma ilustração dessa arquitetura.

Fig. 2.3: Ilustração da arquitetura de *Harvard*.

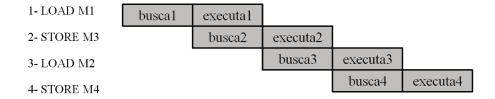

O ciclo de busca de uma instrução e o de execução de outra instrução podem ser sobrepostos aplicando-se o conceito de *pipelining*, ou seja, o processador desenvolve um ciclo de execução enquanto realiza a busca da próxima instrução que será executada. A Figura 2.4 mostra uma sequência de execuções de instruções na arquitetura de *Harvard*.

Fig. 2.4: Execução de uma instrução na arquitetura de *Harvard*.

Com base na Figura 2.4, considere o conjunto de instruções de acesso à memória LOAD e STORE. Observe que enquanto a instrução LOAD M1 está executando, a instrução seguinte, STORE M3 pode iniciar seu ciclo de busca e execução.

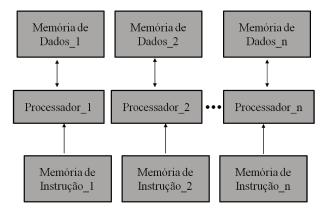

## 2.2 Computadores Paralelos

O processamento paralelo tem o objetivo de dividir as tarefas de modo que os processadores trabalhem de forma sincronizada, sendo que cada um executa uma tarefa. Baseando-se na classificação de computadores paralelos proposta por Flynn [7] (que observou o paralelismo nos fluxos de instruções e de dados), os computadores podem ser agrupados em quatro categorias [8] discutidas a seguir.

#### SISD - Única Instrução, Único Dado (Single Instruction Single Data)

Esta categoria é a mais simples e representa as máquinas clássicas de Von Neumann ou o monoprocessador. Existe um único fluxo de instruções e um único fluxo de dados, além de um único processador que executa uma única sequência de instruções que operam nos dados armazenados em uma única memória. Nesta categoria um único dado é operado por vez [7, 3], como pode ser observada na Figura 2.5.

Fig. 2.5: Arquitetura SISD.

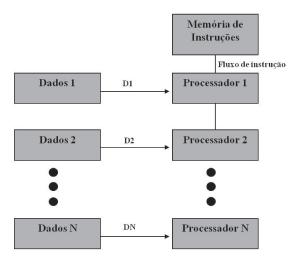

#### SIMD - Única Instrução, Múltiplos Dados (Single Instruction Multiple Data)

A categoria SIMD mostrada na Figura 2.6, possui uma única instrução que é executada em um conjunto diferente de dados e por diferentes processadores [3]. Cada processador possui sua própria memória de dados mas compartilham a mesma memória de instruções, ou seja, todos executam a mesma instrução, porém sobre diferentes dados, e possuem uma única unidade de controle, para busca e execução de instruções [8].

Fig. 2.6: Arquitetura SIMD.

#### MISD - Múltiplas Instruções, Único Dado (Multiple Instruction Single Data)

Uma sequência de dados é enviada para um conjunto de processadores, sendo que cada um executa uma sequência de diferentes instruções [3]. A Figura 2.7 mostra a arquitetura MISD.

Fig. 2.7: Arquitetura MISD.

#### MIMD - Múltiplas Instruções, Múltiplos Dados (Multiple Instruction Multiple Data)

Um conjunto de processadores, representam a categoria MIMD sendo que cada um busca suas próprias instruções e executa sobre seus próprios dados [8]. Essa arquitetura pode ser observada na Figura 2.8.

Fig. 2.8: Arquitetura MIMD.

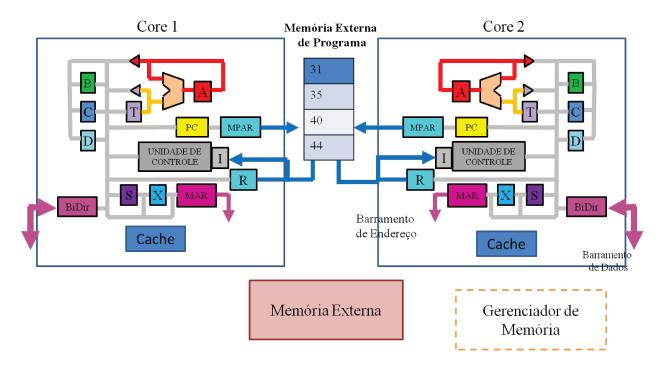

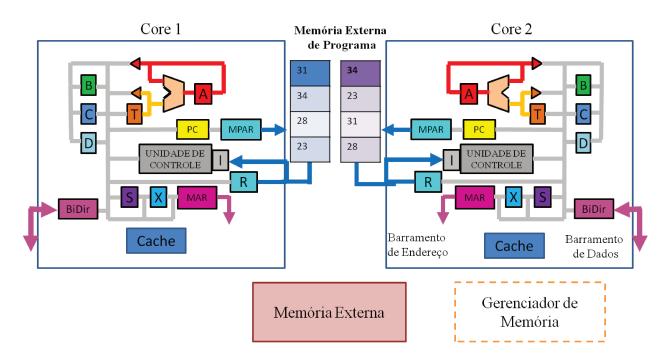

#### 2.2.1 Processadores Multicore

Os processadores *multicore* estão sendo aceitos na maioria dos segmentos da indústria, incluindo DSP. As implementações de processadores *multicore* são numerosas e diversas. Os projetos variam de máquinas com multiprocessadores convencionais, até projetos que consistem de um grande número de unidades lógicas e aritméticas (ULAs) programáveis [9].

A tecnologia *multicore* consiste em um sistema de computador que contém múltiplos processadores ou núcleos (*cores*) que fazem parte de um único *chip* [10, 3]. O sistema operacional trata cada um desses núcleos, como se fosse um processador diferente, com seus próprios recursos de execução como memória cache, registradores, ULA e unidade de controle, podendo processar várias instruções simultaneamente [10, 3]. O uso de vários núcleos possibilita executar instruções em paralelo e também diminui o problema do gargalo que causa atrasos e congestionamentos dos dados [10].

O objetivo de um sistema *multicore* é permitir maior utilização de paralelismo no nível de *threads*, que estão cada vez mais sendo utilizadas pelos projetos de software, para aplicações como multimídia e o amplo uso de ferramentas de visualização [10].

A principal vantagem de sistemas *multicore* é que o aumento de desempenho, pode estar relacionado ao número de processadores ao invés da frequência [9].

As arquiteturas *multicore* apresentam a possibilidade de distribuir as diferentes tarefas para os vários núcleos, obtendo maior eficácia (*troughput*) do sistema e um melhor desempenho por parte dos aplicativos mesmo que vários deles estejam executando simultaneamente [11].

## 2.3 Processamento Digital de Sinais

O processamento digital de sinais (DSP), (do inglês *Digital Signal Processing*), é uma área da ciência e engenharia que tem crescido muito nos últimos anos. Este crescimento é o resultado do avanço significativo na tecnologia do computador digital e fabricação de circuitos integrados. Os computadores digitais e o hardware digital associado nas últimas décadas eram grandes e seu custo era alto, como consequência, seu uso limitou-se para cálculos científicos e aplicações de negócios [12].

O DSP foi criado no início da década de 80, pelas principais empresas de eletrônicos, tais como a Texas Instruments, Analog Devices e Motorola, tornando-se em pouco mais de uma década um dos componentes mais importantes em eletrônica, sendo hoje a parte fundamental de muitos equipamentos de diversas áreas da indústria [13]. Ele surgiu com o propósito de se criar um microprocessador com uma arquitetura desenvolvida para realizar operações específicas necessárias ao processamento digital de sinal. Hoje, tem-se um produto que engloba, em um único *chip*, tecnologia suficiente para realizar praticamente qualquer tipo de processamento e análise de dados e sinais [13].

O DSP é um processador programável de propósito geral, que processa um sinal digital, e que possuem um custo razoável e um tempo eficiente para implementar algoritmos de processamento de sinal digital. A maioria dos DSPs são baseados na arquitetura de *Harvard*[14], que possui barramentos distintos para dados e para instruções e também possuem uma unidade de multiplicação paralela e muito rápida, denominada MAC, a qual é responsável pela execução de uma operação de

2.4 Unidade de Controle

multiplicação em um único ciclo de clock [15, 14].

Por outro lado, há uma desvantagem que inclui a necessidade de hardware adicional como interface para portas I/O, conversores de dados analógico-digital e digital-analógico e unidades de memória interna. Além disso, devido à sua generalidade, os circuitos DSP são eficientes em relação à velocidade computacional quando comparado ao hardware dedicado para uma determinada aplicação [15].

#### Unidade de Multiplicação e Acumulação

O DSP é composto por uma unidade de multiplicação e acumulação, conhecida também por MAC. Esta unidade é projetada para resolver operações de cálculo para multiplicações de vetores e matrizes [8], exigida em algoritmos de filtragem digital e processamento de sinais variantes no tempo [15]. O objetivo do MAC é multiplicar dois operandos, a e b, e adicionar o resultado do produto no acumulador, como pode ser observado na Figura 2.9. No próximo loop, ou seja, na entrada dos novos operandos, o valor do acumulador, resultante das multiplicações anteriores dos operandos, é somado e acumulado ao resultado da multiplicação dos novos operandos.

Fig. 2.9: Unidade MAC.

#### 2.4 Unidade de Controle

A unidade de controle tem a função de ativar os sinais de controle responsáveis pela execução de uma instrução. Ela tem como entrada o código da instrução a ser executada. Este código fica armazenado durante o ciclo de execução da instrução num registrador, chamado RI - Registrador

de Instruções (do inglês *Instruction Register*). A partir desse código, a unidade de controle gera sequencialmente os sinais de controle que realizam as micro-operações necessárias à realização da instrução. Por micro-operação entende-se, por exemplo, o gatilho de um registrador, a ativação de um barramento ou o apagamento (*reset*) de um registrador. A unidade de controle pode ser de dois tipos: *hardwired* ou microprogramada.

A unidade de controle do tipo *hardwired*, também conhecida como implementada por hardware, é um circuito lógico baseado em uma máquina de estado que implementa os estados necessários para ativar todos os sinais de controle de um conjunto de instruções [3, 16]. Este tipo de unidade de controle tem a vantagem de ocupar menos espaço que a outra alternativa. No entanto, ela é pouco flexível para, por exemplo, incluir nova instrução. Neste caso o projeto de todo o circuito lógico deverá ser refeito.

A unidade de controle microprogramada é especificada por um microprograma que consiste de uma sequência de microinstruções em uma linguagem de microprogramação [3]. Este microprograma pode ser armazenado numa ROM - Memória somente de Leitura (do inglês *Read Only Memory*), chamada de memória de microprograma ou micromemória, que em cada posição armazena um vetor com todos os sinais de controle para os componentes do processador [16]. Cada sinal de controle ocupa um *bit* da palavra armazenada. Em cada passo de execução de uma instrução, uma nova posição desta memória é acessada e seus *bits* definem o estado de cada sinal de controle. Durante cada passo de execução de uma instrução, esta palavra é mantida estável num registrador, chamado de MIR - Registrador de Micro-Instruções (do inglês *Micro Instruction Register*). A memória de microprograma é também referenciada como uma LUT - Tabela de endereços (do inglês *Look-Up Table*). A unidade de controle microprogramada possui a vantagem de ser flexível para incluir novas instruções, ou mesmo, otimizar as existentes. No entanto, ela pode necessitar de uma área física maior para sua implementação.

Para um estudo aprofundado sobre a estrutura de processamento e sobre os tipos de unidades de controle, vide [3] ou [16].

## 2.5 Simulação e Emulação de Processadores

Segundo Michaelis [17] o termo **Simular** significa, dentre outros, *Arremedar ou imitar*. Ainda segundo este dicionário, o termo **Emular** significa, dentre outros, *comportar-se como alguma outra coisa*. Ou seja, de forma livre pode-se dizer que os dois termos têm um significado muito próximo, de "imitar". Em computação, uma distinção é feita dependendo de como esta "imitação" é implementada. Originalmente, diz-se simular, quando esta "imitação" é realizada em software. Diz-se emular, quando ela é implementada por hardware.

#### 2.5.1 Simulador

A simulação é utilizada para descrever e analisar o comportamento de um sistema e, usualmente, é realizada através de softwares de desenvolvimento (tais como o QUARTUS II da Altera [18]) e tem a função de verificar computacionalmente a operação de um processo ou de um sistema implementado fisicamente [19]. O resultado de uma simulação ajuda a definir o *layout* físico de um sistema, limitando a funcionalidade e o controle do sistema [20].

Existem alguns simuladores como o SIMULINK, voltado para simulação de sistemas dinâmicos [21], o SPICE, que permite analisar o comportamento elétrico de um circuito [22] e o ARENA que é um ambiente gráfico de simulação que ajuda a demonstrar, prever e medir estratégias do sistema para obter um desempenho eficaz, eficiente e otimizado [23]. Estes simuladores foram desenvolvidos com o intuito de poder realizar qualquer tipo de simulação, para qualquer área de atuação. Contudo, dependendo do sistema, a simulação pode se tornar complexa e levar muito tempo para ser concluída.

#### 2.5.2 Emulador

Durante muito tempo o desenvolvimento de sistemas de programas para microcomputador utilizou o que era chamado de *ICE* - Emulador em circuito (do inglês *In circuit emulator*). Eram equipamentos fornecidos por fabricantes de microprocessadores e por alguns fabricantes de instrumentos que permitiam o teste e a depuração do programa juntamente com o teste e a depuração do circuito em desenvolvimento. Estes equipamentos dispunham de diversos recursos como grande quantidade de memória, recursos de interface com o usuário, software de desenvolvimento de programas (compiladores e montadores) e recursos de depuração. Em geral, os recursos de depuração destes equipamentos permitiam ao programador, acompanhar a execução de seu programa de forma controlada. Ou seja, estabelecendo pontos de parada (*breakpoints*) em determinadas posições do programa e nestes pontos observar, ou se necessário modificar os conteúdos de determinados elementos armazenadores (posições de memória ou variáveis do programa e registradores) [24, 25].

Os ICE's se ligavam ao circuito em desenvolvimento através do que era chamado de "cordão umbilical"que tinha em uma de suas extremidades um conector com pinos compatíveis com o microprocessador utilizado no circuito. Esta extremidade era ligada ao soquete do microprocessador no circuito em teste e rodava o programa residente na memória do emulador, observe a Figura 2.10. Após toda a depuração, o cordão umbilical era retirado e o microprocessador colocado em seu soquete juntamente com a memória de programa (em geral, EPROM) com o programa depurado.

Fig. 2.10: Desenvolvimento com Emulador em circuito

Hoje em dia, os emuladores em circuito não são mais usados. Dois são os principais motivos. Primeiro, o surgimento de simuladores cada vez mais sofisticados, que permitem um desenvolvimento em condições mais próximas do processador alvo. Também, graças ao desenvolvimento da microeletrônica, hoje em dia os processadores têm integrado em seus chips diversos recursos que permitem a depuração no próprio circuito final do desenvolvimento. São exemplos destes recursos o padrão IEEE 1149 JTAG - *Joint Test Action Group* [26] e o BDM - *Background Debug Mode*, da Freescale [27].

## 2.6 Resumo do capítulo

Neste capítulo, foram apresentados, de forma resumida, diversos conceitos importantes no estudo de arquitetura de computadores. Muitos destes conceitos poderiam necessitar de um capítulo inteiro para descrevê-los de forma completa. Aqui não se pretendeu esgotar cada um destes conceitos e sim apresentá-los de forma suficiente para o entendimento do seu uso no restante deste trabalho. Para aqueles interessados em um estudo mais aprofundado sobre os tópicos aqui abordados recomenda-se as referências [2, 3]. Dentre os conceitos aqui apresentados, destaca-se o de microprogramação. Este conceito é fundamental para este trabalho, pois ele foi utilizado para a implementação da unidade de controle descrita no capítulo 3.

Os conceitos de simulação e emulação aqui apresentados são muito amplos. Nos próximos capítulos deste trabalho, os termos "simulador"e "emulador"são utilizados de forma a distinguir o que foi implementado em software do que foi implementado em hardware.

# Capítulo 3

# O Ambiente Computacional Proposto

Um processador é composto por um conjunto de elementos básicos que, trabalhando juntos, realizam a execução de instruções. Esses elementos são os registradores, unidades de operação lógica e aritmética, memória, unidade de controle e barramentos. Dentro deste contexto, este capítulo propoe um ambiente computacional *framework*, voltado para o ensino de estruturas de processamento.

#### 3.1 O Ambiente ModPro

O ambiente computacional proposto é denominado MODPRO. Trata-se de um recurso didático para ser usado no ensino de arquitetura de processamento de dados, ou seja, tem como objetivo o ensino do funcionamento de processadores, bem como, de cada um de seus componentes. A idéia é que através de um conjunto de módulos interligáveis seja possível formar diversas estruturas de processamento. Desta forma, o professor pode desenvolver, em sala de aula, junto com o aluno e mostrar de forma visual com animação, desde componentes básicos do processador até as estruturas de processamento que estão emergindo no mercado. Este ambiente é composto por um simulador, denominado SIMPRO, e por um emulador, chamado EMUPRO, como pode ser observado na Figura 3.1. Observe que os termos simulador e emulador são usados aqui de forma livre, somente para distinguir que o SIMPRO é implementado em software e o EMUPRO é realizado em hardware.

O MODPRO é composto por um conjunto de elementos básicos que são descritos tanto no SimPro quanto no EmuPro. No SIMPRO, estes elementos são representados, principalmente, de forma simbólica, no EMUPRO, eles são descritos através de módulos funcionais no ambiente de desenvolvimento QUARTUS II da Altera.

Fig. 3.1: Ilustração do *framework* proposto.

O SIMPRO é um conjunto de recursos gráficos (módulos) que permite ao professor ensinar de forma animada, passo a passo os sinais de controle e todo o fluxo de dados durante a execução do ciclo de uma instrução pelo processador. Os módulos do SIMPRO permitem ao professor moldar/criar uma determinada arquitetura de componentes, possibilitando a inclusão de novas estruturas de processamento. O SimPro tem o compromisso de ficar disponível na internet, onde poderá ser exercitado pelos alunos.

O EMUPRO, contém os mesmos módulos do SIMPRO, mas é totalmente desenvolvido em hardware, utilizando a ferramenta QUARTUS II da Altera [18]. Através deste recurso, os alunos podem, em laboratório, validar a estrutura desenvolvida em classe.

Para a elaboração do MODPRO foi considerado que cada um dos seus elementos básicos, ou módulo, possui sinais de controle que vêm de um módulo central de controle. Este módulo central de controle, aqui chamado de unidade de controle, é do tipo microprogramado. Assim, esta unidade de controle é comum a qualquer implementação de processador. O que varia da implementação de um processador para outro é a quantidade de sinais de controle que esta unidade gera e o microprograma nela residente.

Além da unidade de controle, os demais módulos disponíveis no MODPRO são classificados nos seguintes tipos:

- Operadores;

- Registradores;

- Barramentos;

- Memória.

As seções seguintes descrevem cada um dos elementos básicos disponíveis no MODPRO.

3.2 Unidade de controle

#### 3.2 Unidade de controle

Este é o módulo mais importante de todo o MODPRO. Ele é comum a todas implementações de processadores. A unidade de controle do MODPRO é do tipo microprogramada, de forma que é possível microprogramar toda e qualquer sequência de micro-operações para realizar qualquer instrução.

A Unidade de Controle é composta por:

- RI Registrador de Instruções;

- Decodificador de Instruções;

- LUT *Look-up Table*;

- Registrador de estado;

- Sistema de relógio;

- MIR Registrador de micro-instrução (do inglês Micro-Instruction Register)

#### 3.2.1 RI - Registrador de Instrução

O registrador de instruções é a entrada da unidade de controle. Ele recebe, após um ciclo de busca de instrução, do barramento de dados interno, o código que representa a instrução a ser executada. Ele possui um único sinal de controle referenciado por um gatilho, que permite a entrada de dados para este registrador.

#### 3.2.2 Decodificador de Instruções

O circuito de decodificação de instruções é responsável por converter o código da instrução a ser executada no endereço inicial na LUT, a partir de onde inicia a sequência de microoperações para a execução da instrução. No SIMPRO este circuito não é explicitamente representado, está dentro do bloco que representa a unidade de controle, dessa forma, ele é implementado por uma tabela de conversão. No EMUPRO também é implementado por uma tabela que é transformada em circuito pelo sistema Quartus II. Este módulo não possui sinais de controle.

## 3.2.3 LUT - Look-up Table

Este é o coração de todo o ambiente, é a memória de microprograma, responsável por armazenar todas as sequências de micro-operações de todas as instruções implementadas no processador desen-

3.3 Operadores 18

volvido. Ela é uma memória, sendo que para cada um de seus endereços encontram-se associados ou são associados valores binários, que representam sinais para o controle dos componentes do projeto.

#### 3.2.4 Registrador de estado

O registrador de estado sinaliza as condições finais da execução completa de uma instrução. Por exemplo, se após a execução de uma instrução um registrador foi levado a conter o valor zero, isto estará sinalizado num bit no registrador de estado. Estas condições podem ser utilizadas na implementação de instruções de desvio condicionado.

#### 3.2.5 Sistema de relógio

O sistema de relógio da unidade de controle permite o funcionamento de todo ambiente em duas formas básicas:

**Passo a passo:** quando a cada ciclo de relógio o sistema para, o que permite uma visualização do estado de cada um dos módulos envolvidos na execução da presente instrução.

Tempo de execução real: quando o relógio do sistema roda livremente.

No SIMPRO, o sistema de relógio é implícito ao bloco da unidade de controle. Dele somente são visíveis dois botões, um que permite a seleção da forma de funcionamento (passo a passo) e outro que dispara o ciclo de relógio. No EMUPRO, o sistema de relógio utiliza o relógio da placa da FPGA, uma chave seletora, que permite a execução passo a passo, e um botão que dispara o ciclo de relógio.

## 3.2.6 MIR - Registrador de micro-instrução

O registrador de micro-instrução recebe em cada ciclo de relógio a palavra com os *bits* de controle de todos os módulos do processador. Este registrador mantém estes sinais de controle durante todo o ciclo de relógio.

## 3.3 Operadores

São chamados módulos operadores aqueles responsáveis pelas operações lógicas e aritméticas realizadas no processador. Estão disponíveis os seguintes módulos operadores:

- Unidade Lógica e Aritmética (ULA)

- Multiplicador/divisor

3.4 Registradores 19

#### 3.3.1 Unidade Lógica e Aritmética - ULA

A ULA é responsável por realizar as operações lógicas e aritméticas dos dados no computador. As operações lógicas estão relacionadas às operações *bit* a *bit* de **AND**, **OR**, **NOT** e **XOR**. Esta unidade também realiza as operações aritméticas básicas de adição e subtração.

#### 3.3.2 Multiplicador/Divisor

Este módulo realiza as operações de multiplicação e divisão inteiras.

## 3.4 Registradores

Os registradores são memórias que armazenam temporariamente as informações que devem ser usadas na execução de uma instrução. Eles são formados por um conjunto de *flip-flops*, sendo que cada um é capaz de armazenar um *bit*. Existem vários tipos de registradores que fazem parte do MODPRO de forma que cada um é responsável por uma determinada função dentro do processador.

Estão disponíveis no MODPRO os seguintes tipos de registradores:

- Registradores contadores

- Registrador de passagem

- Registrador de propósito geral

## 3.4.1 Registradores contadores

Na biblioteca do MODPRO existe o chamado registrador contador. É um tipo de registrador com capacidade de contagem crescente ou decrescente. Em geral, ele é instanciado para realizar funções específicas dentro de uma estrutura de processamento. Exemplos de uso, Contador de Programa (PC), do inglês *Program Counter* e o Apontador de Pilha S, do inglês *Stack Pointer*.

## 3.4.2 Registrador de passagem

Na biblioteca do MODPRO está disponível ainda o chamado registrador de passagem. Este tipo de registrador é instanciado para funções de armazenamento temporário dentro de uma estrutura de processamento. Em geral, as instâncias deste tipo de registrador não são visíveis pelo jogo de instruções implementado. O nome deste tipo de registrador está associado ao fato de que o seu uso é, em geral, para interligar (ponto a ponto) somente dois módulos da estrutura de processamento

3.5 Barramentos 20

implementada. Exemplos de uso, MAR - Registrador de Endereço de Memória (do inglês *Memory Address Register*) e outros registradores temporários.

#### 3.4.3 Registrador de propósito geral

O último tipo de registradores disponíveis na biblioteca do MODPRO é chamado de registrador de propósito geral. Este tipo é instanciado para formar os registradores que serão visíveis ao jogo de intruções, ou seja, que estão presentes nas instruções.

#### 3.5 Barramentos

Entende-se por barramento um conjunto de fios paralelos os quais permitem a ligação entre os componentes. Eles são usados para transmitir dados, endereços e sinais de controle [2]. Estão disponíveis no MODPRO dois tipos de barramento: o bidirecional e o unidirecional.

#### 3.5.1 Barramento Bidirecional

São módulos de interligação nos dois sentidos (leitura ou escrita). Exemplo do uso: na implementação do barramento interno de dados e no barramento de dados da memória externa.

#### 3.5.2 Barramento Unidirecional

São módulos de interligação num único sentido. Exemplo do uso: na implementação do barramento de endereço e de controle da memória.

## 3.6 Memória

O MODPRO define um módulo de memória. O módulo de memória é útil para armazenar informações (dados e ou programas). Ela é composta por um conjunto de células. Cada célula tem associada um endereço, que pode ser referenciado por um programa [2].

Instâncias deste módulo podem ser usadas para a implementação de unidade de memória de dados, de programa e memórias cache.

## 3.7 Resumo do capítulo

Neste capítulo, foi descrita a proposta de um ambiente computacional para apoio ao ensino de estruturas de processamento. Este ambiente é formado por duas partes, pelo SIMPRO e pelo EMUPRO. Este ambiente define uma biblioteca de módulos que podem compor uma estrutura de processamento. Cada módulo desta biblioteca é descrito na forma simbólica, para uso no SIMPRO e na sua forma lógica operacional para uso no EMUPRO.

O SIMPRO foi desenvolvido usando a linguagem *JavaScript*, empregando recursos de CSS - *Cascading Style Sheets* e, permite ser acessado pela web. Seu uso está focado para fins didáticos, ou seja, para o ensino no curso introdutório de arquitetura de computadores.

O SIMPRO pode utilizar os componentes do MODPRO para compor uma determinada estrutura de processamento. Dessa forma, através de um conjunto de recursos gráficos, o SIMPRO permite ao professor mostrar de forma animada, passo a passo (ou em tempo de execução), os sinais de controle e todo o fluxo de dados durante o ciclo de uma instrução executada pelo processador. Com isso, os alunos podem acompanhar a execução de uma determinada instrução dentro da estrutura de processamento estudada.

O EMUPRO foi desenvolvido em hardware, usando a ferramenta QUARTUS II (versão 9.1) da Altera [18]. A sua função consiste em emular a sequência de um ciclo de instrução, usando um FPGA. O EMUPRO é utilizado para validar em laboratório, a estrutura de processamento apresentada aos alunos através do SIMPRO.

No próximo capítulo serão apresentados exemplos da aplicação do ambiente computacional MOD-PRO.

# Capítulo 4

# Exemplos de Simulação e Emulação

Este capítulo apresenta o desenvolvimento do SIMPRO e do EMUPRO bem como alguns exemplos de aplicação. Para o SIMPRO foram aplicados exemplos utilizando as arquiteturas de *Princeton*, de *Harvard* e a estrutura do MAC. O objetivo é mostrar como estas arquiteturas serão simuladas no SIMPRO. Para o exemplo no EMUPRO, foi utilizada a arquitetura de *Princeton*. A escolha das arquiteturas de *Princeton* e de *Harvard*, como exemplo de simulação e também emulação, se deve ao fato delas serem mais conhecidas na literatura. Já a utilização da estrutura do MAC é justificada por ser considerada mais atual dentre as três.

## 4.1 Desenvolvimento do SIMPRO

O SIMPRO foi desenvolvido baseado em um processador de 8 *bits*, sendo composto por uma ULA e pelos seguintes registradores: Acumulador (A), registradores B, C, D, o registrador Temporário (T), o *Stack Pointer* (S), o Registrador de Instruções (RI), registrador X, o PC, e o MAR. Também faz parte do SIMPRO a memória externa composta por um conjunto de instruções e, tambem, o barramento de comunicação entre os registradores e a ULA.

Esse conjunto de componentes faz parte da biblioteca do *framework* e foi selecionada para compor o SIMPRO. As representações associadas a cada registrador foram definidas para serem usadas no SIMPRO, ou seja, para cada tipo de estrutura que for estudada, o professor poderá escolher os componentes desejados, nomeando-os de acordo com a estrutura ensinada.

A ULA tem o papel de realizar as operações aritméticas de adição, subtração, divisão e multiplicação e as operações lógicas AND e OR representadas respectivamente por & e |. Os resultados das operações realizadas pela ULA são armazenados no Acumulador (A).

Os registradores que fazem parte do SIMPRO são responsáveis por armazenar os valores dos operandos para que posteriormente estes sejam utilizados nas operações realizadas pela ULA.

O SIMPRO é composto por quatro arquivos importantes que identificam os dados que serão processados sendo, então, os responsáveis por todo funcionamento do processador. O projetista é o responsável por definir quais e quantas operações serão utilizadas no SIMPRO. Estes arquivos são descritos da seguinte maneira:

- o conjunto de instruções que o processador é capaz de executar;

- a memória externa;

- o decodificador:

- ea LUT.

### 4.1.1 Conjunto de Instruções

O conjunto de instruções contém todas as instruções que o processador poderá executar. Este arquivo é composto por números que foram definidos pelo projetista e que variam entre 0 a 255. Cada número representa o código da operação, denominado OPCODE, que identifica a operação que será executada. A cada OPCODE está associada uma instrução e, consequentemente, este número permite identificar qual instrução deverá ser executada.

Cada instrução tem associada uma abreviação, denominada mnemônico, que é usada pela linguagem *Assembly* para identificar a instrução que deverá ser executada [3]. Por exemplo, o mnemônico ADD é uma instrução que realiza a operação de adição.

Para exemplificar o conjunto de instruções, observe a Tabela 4.1. O OPCODE '00' representa a função que é identificada pelo mnemônico HALT cujo objetivo é parar o processamento. O OPCODE '01' está associado à função CLR A que tem o papel de zerar o acumulador. Já o OPCODE '02' representa a função INC A que irá incrementar o conteúdo do acumulador e '31' está relacionado à função LOADI S que realiza o carregamento imediato, ou seja, o conteúdo da próxima posição de memória para o registrador *stack pointer* (S). Baseado nisso, se define a tabela com o conjunto de instruções que o processador poderá desempenhar.

| OPCODE | Instrução |  |  |

|--------|-----------|--|--|

| 00     | HALT      |  |  |

| 01     | CLR A     |  |  |

| 02     | INC A     |  |  |

| :      | :         |  |  |

| 31     | LOADI S   |  |  |

Tab. 4.1: Definindo o conjunto de instruções.

#### 4.1.2 Memória Externa

A memória externa é composta pelo conjunto de instruções e pelos dados. Este arquivo é constituído por um *array* de 256 palavras que variam de [0...255]. Cada palavra representa uma posição (célula) na memória externa e o respectivo conteúdo de memória de cada posição indica o OPCODE associado a cada instrução. Para exemplificar, observe a Tabela 4.2.

| Posição de Memória | Conteúdo da Memória/OPCODE |  |  |

|--------------------|----------------------------|--|--|

| 0                  | 31                         |  |  |

| 1                  | 315                        |  |  |

| 2                  | 29                         |  |  |

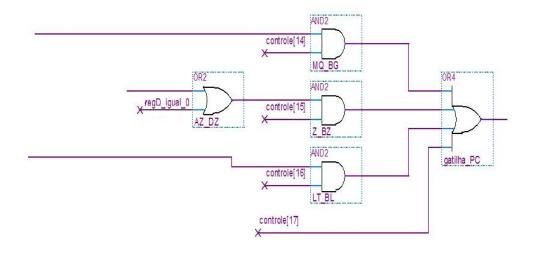

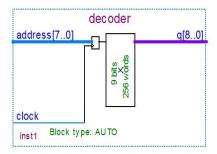

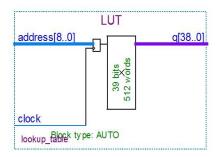

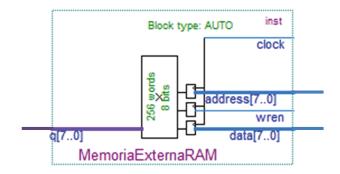

| 3                  | 35                         |  |  |