#### Ricardo Ito

Engenheiro Eletricista, UNESP Guaratinguetá, 1993

| Este exempler defendida por | Corresponde & eleção final da tese |

|-----------------------------|------------------------------------|

|                             | e aprovada pela Comissão           |

| Branch # \$111              | <u>d</u> 1 1 3 5                   |

|                             | all the                            |

"PROJETO DE UM CONVERSOR ANÁLOGO-DIGITAL EM CORRENTE CHAVEADA (SI)"

Dissertação apresentada à Faculdade de Engenharia Elétrica, UNICAMP, como requisito parcial para obtenção do título de "Mestre em Engenharia Elétrica"

Orientador: Prof. Dr. Alberto Martins Jorge

Universidade Estadual de Campinas Faculdade de Engenharia Elétrica Departamento de Microeletrônica

Novembro de 1995

JM-000333339-5

## FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA - BAE - UNICAMP

It6p

Ito, Ricardo

Projeto de um conversor análogo-digital em corrente chaveada (SI) / Ricardo Ito.--Campinas, SP: [s.n.], 1995.

Orientador: Alberto Martins Jorge.

Dissertação (mestrado) - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica.

1. Conversores analógicos-digitais. 2. Circuitos de comutação. 3. Sistemas de tempo discreto. I. Jorge, Alberto Martins. II. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica. III. Título.

Aos meus pais ROBERTO KIYOKASO ITO e MARIA SANAE K. ITO

Este trabalho contou com o apoio das seguintes entidades:

- CNPq através do processo no. 132046/94-6

- Quickchip Engenharia e Projetos Eletrônicos Ltda.

#### **AGRADECIMENTOS**

Ao Prof. Alberto Martins Jorge, pela orientação objetiva em todas as etapas do trabalho.

Ao Prof. Galdenoro Botura Júnior, pelo incentivo recebido desde a iniciação científica.

Ao Prof. Luciano Szezerbatty, pelos conselhos e experiência compartilhada.

À Elisabete A. Sakai, pelo apoio em todos os momentos importantes e pela ajuda na edição desta dissertação.

À Ximena e ao Razera pela convivência e troca de experiência.

À Quickchip por acreditar nos resultados deste projeto.

Enfim, a todos que deram direta ou indiretamente sua contribuição para o contéudo desse texto, a gratidão do autor.

# ÍNDICE

| CAPÍTULO I<br>INTRODUÇÃO                                                         | 1  |

|----------------------------------------------------------------------------------|----|

| CAPÍTULO II<br>ANÁLISE DOS ESPELHOS DINÂMICOS DE CORRENTE                        | 3  |

| II.1. SISTEMAS EM CORRENTE CHAVEADA:                                             | 3  |

| II.2. CÉLULA DE MEMÓRIA DE CORRENTE [2]:                                         | 3  |

| II.3. COMPORTAMENTO NÃO-IDEAL DAS CÉLULAS DE MEMÓRIA DE CORRENTE:                | 4  |

| II.3.1. Erros de descasamento de ganho e de tensão de limiar dos transistores:   |    |

| II.3.2. Erros causados pela diferença entre as condutâncias de entrada e saída:  |    |

| II.3.3. Erros de 'settling':                                                     | 7  |

| II.3.4. Erros de injeção de carga:                                               | 7  |

| CAPÍTULO III                                                                     |    |

| SIMULAÇÕES DE ALGUMAS CONFIGURAÇÕES DE ESPELHOS                                  |    |

| III.1. O SIMULADOR ELÉTRICO E OS PARÂMETROS DE SIMULAÇÃO:                        |    |

| III.2. O ESPELHO SIMPLES COM CHAVES IDEAIS:                                      |    |

| III.3. As CHAVES MOS:                                                            |    |

| III.4. O ESPELHO DINÂMICO SIMPLES COM CHAVES MOS:                                |    |

| III.5. O ESPELHO DINÂMICO "CASCODE":                                             |    |

| III.6. O ESPELHO DINÂMICO "REGULATED CASCODE":                                   |    |

| III.6.1. Com chaves ideais:                                                      |    |

| III.6.3. Com chaves NMOS:                                                        |    |

| III.6.4. Com "chaves Dummy":                                                     |    |

| III.7. ANÁLISE COMPARATIVA DOS ESPELHOS SIMULADOS:                               |    |

| III.8. FAIXA DINÂMICA DO ESPELHO "REGULATED CASCODE" NMOS:                       |    |

| III.9. O ESPELHO DINÂMICO "REGULATED CASCODE" PMOS:                              |    |

| III.10. FAIXA DINÂMICA DO ESPELHO "REGULATED CASCODE" PMOS:                      |    |

| CAPÍTULO IV IMPLEMENTAÇÃO DO ADC                                                 | 27 |

|                                                                                  |    |

| IV.1. INTRODUÇÃO:                                                                |    |

| IV.2. OS CIRCUITOS DE ENTRADA:                                                   |    |

| IV.3. O COMPARADOR DE CORRENTE:                                                  |    |

| IV.5. O CIRCUITO COMPLETO DO CONVERSOR A/D EM CORRENTE CHAVEADA:                 |    |

| IV.5.1. Erros de injeção de carga e "Clock Feed Through":                        |    |

| IV.5.2. Erro de modulação de canal no transistor de armazenamento:               | 48 |

| IV.5.3. Dependência da precisão do espelho com o sinal de corrente de entrada: . |    |

| IV.5.4. Oscilações devido a malha de realimentação:                              |    |

| IV.5.5. Variação da corrente de referência com o sinal em conversão:             |    |

| IV.5.6. Faixa dinâmica reduzida do espelho PMOS:                                 |    |

| IV.6. A CONFIGURAÇÃO FINAL DO CONVERSOR A/D:                                     | 58 |

| IV.7. COMPORTAMENTO DO CONVERSOR COM A TEMPERATURA:                              | 59 |

| CAPÍTULO V<br>CONCLUSÕES FINAIS                                                  | 62 |

| REFERÊNCIAS BIBLIOGRÁFICAS | 65   |

|----------------------------|------|

| ANEXO I                    | . 68 |

# **CAPÍTULO I**

## Introdução

A tecnologia de fabricação de CI's avançou muito no campo de circuitos digitais, e junto com isso foram desenvolvidas ferramentas de projeto cada vez mais poderosas, facilitando o trabalho do projetista, aumentando a chance de acertos numa primeira rodada, reduzindo o tempo de projeto e diminuindo custos. Os circuitos analógicos por sua vez, não tiveram tal desenvolvimento, mas o surgimento de novas tecnologias de fabricação e projeto prometem reverter esse quadro.

Circuitos Integrados Analógicos que incorporam funções digitais e analógicas num único encapsulamento vem se tornando muito importantes em diversos campos de aplicações.

Entre essas inovações podemos citar:

- •BJT perfeitamente complementar:

- Tecnologia de fabricação de CIs BiCMOS (Transistores bipolares e CMOS);

- Semicondutores em GaAs (Arseneto de.Gálio);

- Transistores HEMT (High Eletron Mobility Transistor).

Com essa nova perspectiva, existe ainda uma tendência de projeto de circuitos com baixo consumo de energia, cuja primeira ação é a redução da tensão de alimentação dos Cl's. Começa-se então a pensar em novas técnicas de projeto de circuitos analógicos.

Uma tendência que vem se firmando, é a aproximação de modo corrente, que rapidamente vem ganhando espaço em relação a de modo tensão. São muitas as vantagens proporcionadas por esta aproximação. Entre elas podemos citar a possibilidade de projetos de circuitos muito mais rápidos, trabalhando com menores tensões de alimentação e menor consumo de energia.

Uma outra técnica de projeto, chamada 'Corrente Chaveada', é considerada por muitos especialistas da área, como substituta da já consagrada 'Capacitores Chaveados'. Trata-se circuitos destinados ao processamento de sinais por amostragem, ou como são conhecidos, Processadores Digitais de Sinais (DSPs). Nesta nova técnica, os sinais são amostrados em corrente, e desta forma trazem os benefícios dos circuitos em modo corrente: rapidez de processamento, baixo consumo e operação com baixas tensões de alimentação.

Uma comparação básica da técnica de circuitos em Corrente Chaveada com os Capacitores Chaveados, traz as seguintes vantagens para a primeira:

- Não necessitam de capacitores com 2 terminais flutuantes;

- •Possibilidade de trabalhar com baixas tensões de alimentação;

- Os capacitores não necessitam ser lineares;

- •Baixo consumo de energia;

•Circuitos totalmente compatíveis com a tecnologia CMOS Digital.

Os circuitos em Corrente Chaveada ainda não alcançaram porém, um amadurecimento suficiente para suplantar os Capacitores Chaveados. Eles apresentam alguns problemas como por exemplo a qualidade dos transistores na tecnologia CMOS Digital, problemas com as chaves MOS, etc. Porém, muito vem sendo estudado a respeito desses circuitos e acredita-se que seu aprimoramento está ocorrendo rapidamente, e que em breve serão muito utilizados para o processamento digital de sinais.

Na técnica de Corrente Chaveada, existe uma célula básica denominada Espelho Dinâmico de Corrente. Essas células podem ser chamadas ainda de Copiadores de Corrente ou Células de memória de corrente. Sendo assim, a síntese de células precisas e de boa performance, levará certamente a evolução de toda a técnica.

Muito já se pesquisou e ainda vem se pesquisando a respeito dessas células, e resultados bastante significativos foram obtidos, no sentido de levantamento dos problemas existentes, e propostas de soluções dos mesmos. Porém ainda é necessário muito trabalho até que sinais amostrados em corrente sejam processados por circuitos em Corrente Chaveada de forma precisa, rápida e confiável.

Algumas configurações de células de memória de corrente já foram publicadas e intensamente exploradas, em aplicações que vão desde Deslocadores de Fase e Integradores até Conversores Análogo/Digitais e Filtros Digitais. Cada uma delas propõe um tipo de solução, buscando sempre reduzir os erros causados pelo chaveamento de corrente, e tornar o circuito independente da dispersão de parâmetros dos transistores.

A proposta desta dissertação é de fazer um estudo comparativo de algumas configurações dessas células, focalizando e avaliando os problemas de cada uma, e com os resultados desse estudo implementar um conversor Análogo/Digital, adquirindo assim uma boa familiarização com a técnica de Corrente Chaveada.

# **CAPÍTULO II**

# Análise dos espelhos dinâmicos de corrente

#### II.1. Sistemas em corrente chaveada

Um sistema em Corrente chaveada (SI) pode ser definido como um sistema formado por circuitos de amostragem de dados analógicos onde os sinais são representados na forma de corrente, diferentemente dos sistemas em capacitores chaveados (SC), onde os sinais são amostrados em tensão [13].

As aplicações para os sistemas SI são as mesmas para sistemas SC, tais como filtros digitais, conversores A/D e D/A. Os circuitos SI possuem uma característica importante, que é a possibilidade de implementação em tecnologia digital CMOS VLSI [21]. Ao contrário dos circuitos SC, não são necessários capacitores lineares com terminais flutuantes [2].

Qualquer circuito que manipule sinais em corrente, desenvolve também variações de tensão ao longo de seus nós de ligação. Entretanto, as tensões desenvolvidas nos circuitos SI, não necessitam ser grandes nem lineares para a correta operação do mesmo. Isso permite a operação em baixos níveis de tensão [1].

Para a implementação de algorítimos de processamento de sinais amostrados, os circuitos em corrente chaveada devem possibilitar a implementação de algumas operações básicas:

- 1) Soma e subtração correntes;

- 2) Excitação de outros circuitos em modo corrente, em nós de baixa impedância;

- 3) Escalonamento de correntes (multiplicação por um valor fixo);

- 4) Possibilidade de memorização.

Para a realização destas tarefas, existe uma célula denominada "Célula de memória de corrente" ou "Espelho dinâmico de corrente" [6].

### II.2. Célula de memória de corrente [2]

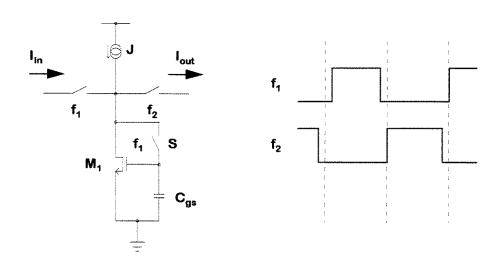

O circuito da figura II.1(a) mostra uma célula de memória de corrente básica, que utiliza um único transistor M<sub>1</sub>.

A célula funciona a partir dos sinais de clock mostrados na figura II.1(b), e seu funcionamento é o seguinte: na fase  $f_1$ , a chave S está fechada e o transistor está conectado como diodo, alimentado pela soma das corrente de entrada lin e de polarização J. Inicialmente, esta corrente flui também pela capacitância C que está descarregada, até que sua tensão ultrapasse o valor da tensão  $V_t$  de  $M_1$  e atinja o valor de  $V_{gs}$  correspondente a corrente ( $I_{in}+J$ ). Na fase  $f_2$ , a chave S é aberta e a tensão  $V_{gs}$  é mantida no capacitor C, sustentando então a corrente ( $I_{in}+J$ ) através do 'drain' de  $M_1$ . Com a chave de entrada aberta e a de saída fechada, fluirá pelo terminal de saída a corrente  $I_0=-I_{in}$ .

Esse efeito de memorização de corrente, ocorre devido ao armazenamento da tensão  $V_{\rm gs}$  no capacitor C. Porém tal capacitor não necessita ser linear, nem

ter seus terminais flutuantes, o que o torna compatível com a tecnologia CMOS VLSI digital.

figura II.1 - Célula de memória de corrente básica.

Na prática, o sinal de controle de f<sub>1</sub> que comanda a chave S deve ser ligeiramente adiantado ao sinal da chave que injeta a corrente l<sub>in</sub>, a fim de garantir que a memorização da corrente de entrada ocorra antes que a mesma seja interrompida.

O transistor de memorização M<sub>1</sub> e as chaves (também implementadas por transistores MOS) possuem comportamentos não-ideais, trazendo erros de amostragem e armazenamento. Esses erros serão tratados a seguir.

# II.3. Comportamento não-ideal das células de memória de corrente [2]

Imperfeições nos transistores MOS causam desvios da performance ideal da células de memória de corrente. São quatro as principais fontes de erro:

- 1) Descasamento de ganho e de tensão de limiar dos transistores;

- 2) Variações na condutância de 'drain';

- 3) Resposta em frequência do transistor;

- 4) Injeção de carga das chaves.

# II.3.1. Erros de descasamento de ganho e de tensão de limiar dos transistores

São resultados de pequenas mas inevitáveis diferenças nas características DC dos transistores da célula de memória.

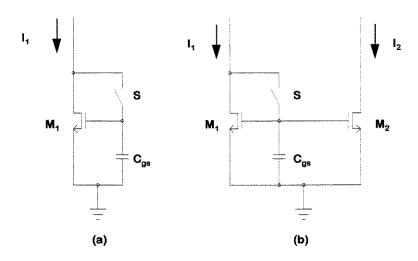

Na figura II.2(a) é mostrada uma célula de memória básica, onde um único transistor funciona como entrada e saída da corrente memorizada. Neste caso não existirá portanto erros de descasamento. Entretanto, em algumas configurações de circuitos em corrente chaveada, são necessários transistores adicionais implementados como espelhos de corrente, tal como mostrado na figura II.2(b), em que aparecem então os erros de descasamento. Esse circuito

será então analisado quanto aos efeitos no descasamento de ganho e tensão de limiar no comportamento da célula de memória de corrente.

figura II.2 - Célula de memória de corrente.

Com a chave S fechada o circuito é um simples espelho e considerando que  $M_1$  e  $M_2$  são idênticos, então a corrente de entrada  $I_1$  é reproduzida exatamente como  $I_2$ . Na prática  $M_1$  e  $M_2$  não serão idênticos devido a pequenas variações no processo de fabricação do circuito integrado, gerando pequenas diferenças nas características DC desses transistores, resultando em erro na corrente reproduzida  $I_2$ .

Quando a chave S se abre, a corrente  $I_2$  é armazenada somada com o erro produzido na fase anterior. Com  $M_1$  e  $M_2$  operando na saturação, suas correntes de 'drain' são dadas por:

$$I_{1} = \frac{\beta_{1}}{2} \left( V_{gs1} - V_{t1} \right)^{2} \left( 1 + \lambda_{1} V_{ds1} \right)$$

[II.1]

onde:

$$\beta = \mu C_{ox} \left[ \frac{W}{L} \right]$$

[II.2]

е

$$I_{2} = \frac{\beta_{2}}{2} \left( V_{gs2} - V_{t2} \right)^{2} \left( 1 + \lambda_{2} V_{ds2} \right)$$

[II.3]

Da equação [II.1] vem:

$$V_{gs1} = V_{t1} + \sqrt{\frac{2I_1}{\beta_1} (1 + \lambda_1 V_{ds1})}$$

[II.4]

Com a chave S fechada,  $V_{gs2}$  é forçado ao valor de  $V_{gs1}$ . Introduzindo a relação  $V_{gs1}$ = $V_{gs2}$  na equação [II.4] vem:

$$I_{2} = \frac{\beta_{2}}{2} \left( V_{gs1} - V_{t2} \right)^{2} \left( 1 + \lambda_{2} V_{ds2} \right)$$

$$= \left[ \frac{\beta_{2}}{2} \left[ \left( V_{gs1}^{2} + V_{t2}^{2} - 2 V_{gs1} V_{t2} \right)^{2} \left( 1 + \lambda_{2} V_{ds2} \right) \right]$$

[II.5]

Considerando  $V_{t1}\cong V_{t2}\cong V_t$  e Introduzindo [II.4] em [II.5], depois de algumas simplificações vem:

$$I_{2} = \frac{\beta_{2}}{2} (1 + \lambda_{2} V_{ds2}) \left[ \delta V_{t}^{2} + 2 \delta V_{t} (V_{gs} - V_{t}) \right] \frac{\beta_{2}}{\beta_{1}} \left[ \frac{1 + \lambda_{2} V_{ds2}}{1 + \lambda_{1} V_{ds2}} \right]$$

[II.6]

onde  $\delta V_t = V_{t1} - V_{t2}$ .

Dividindo por I1 [II.1] vem:

$$\frac{I_2}{I_1} = \frac{\beta_2}{\beta_1} \left[ \frac{1 + \lambda_2 V_{ds2}}{1 + \lambda_1 V_{ds1}} \right] \left[ \frac{1 + 2\delta V_t}{V_{gs} - V_t} \right]$$

[II.7]

Observa-se que a influência da tensão Vds pode ser minimizada mantendo as tensões  $V_{ds2}$  e  $V_{ds1}$  iguais, através de circuitos mais aprimorados. Portanto, redefinindo  $\beta$  como sendo o ganho do transistor a uma certa tensão  $V_{ds}$ , o termo (1+ $\lambda V_{ds}$ ) passa a estar embutido em  $\beta$ , e a equação [II.7] se resume a:

$$\frac{I_2}{I_1} = \frac{\beta_2}{\beta_1} \left[ \frac{1 + 2\delta V_t}{V_{gs} - V_t} \right]$$

[II.7]

Desta forma o erro de descasamento será:

$$\varepsilon_{\rm m} = \frac{I_2 - I_1}{I_1} \cong \frac{\delta \beta}{\beta} + \frac{2\delta V_{\rm t}}{V_{\rm ss} - V_{\rm t}}$$

[II.8]

onde  $\delta\beta = \beta_2 - \beta_1$ .

Este resultado expressa o erro de descasamento especificamente para o ganho e tensão de limiar do transistor.

Existem alguns pontos que devem ser observados no projeto de células de memória de corrente que são:

- 1) Existe pouca correlação entre os erros contidos em V<sub>t</sub> e β;

- 2) As variâncias de V<sub>t</sub> e β não diminuem com o aumento da área do transistor;

- 3) Com o escalonamento do transistor para um processo CMOS de dimensões menores, a variância de V<sub>t</sub> aumenta com o dobro da espessura do óxido, enquanto que a variância de β permanece constante;

# II.3.2. Erros causados pela diferença entre as condutâncias de entrada e saída

Na fase de amostragem da célula de memória básica (figura II.1), a tensão de 'drain' do transistor de memorização assume o mesmo valor da sua tensão de 'gate'. Na fase de amostragem, quando o transistor entrega a corrente de saída para sua carga, a tensão de 'drain' pode sofrer alteração em seu valor e com isso alterar o valor da corrente de saída. Isso ocorre devido a dois fatores principais:

#### 1) Efeito de modulação de canal:

Expresso pela equação do transistor MOS operando na região de saturação:

$$I_{ds} = \left[\frac{\beta}{2}\right] \left(V_{gs} - V_{t}\right)^{2} \left(1 + \lambda V_{ds}\right)$$

[II.9]

onde  $\lambda$  é o parâmetro que representa a modulação de canal, definindo a condutância de 'drain' do transistor de memorização:

$$g_{ds} = \frac{\delta I_{ds}}{\delta V_{ds}} = \lambda V_{ds}$$

[II.10]

### 2) Capacitância intrínseca Cdg:

Variações na tensão de 'drain' causam fluxo de cargas através da capacitância intrínseca  $C_{dg}$  e da capacitância de memorização C. A tensão de 'gate' sofrerá então mudanças em seu valor produzindo erros na corrente reproduzida pela célula de memória.

Esses dois efeitos conjugados produzem um erro  $\delta l_{ds}$  resultante das variações na tensão  $V_{ds}$ :

$$\delta I_{ds} = \delta V_{ds} \left\{ g_{ds} + \left[ \frac{C_{dg}}{C + C_{dg}} \right] g_{m} \right\}$$

[II.11]

A célula de memória apresentará o comportamento desejado quando a condutância de saída (gom) apresentar o valor:

$$g_{om} = g_{ds} + \left[\frac{C_{dg}}{C + C_{dg}}\right]g_{m}$$

[II.12]

Ocorrerá um erro  $\epsilon g$  na célula de memória quando a condutância de saída  $(g_{om})$  não for desprezível comparada com a transcondutância do transistor  $(g_m)$  quando conectado como diodo.

#### II.3.3. Erros de 'settling'

A operação da célula de memória envolve a carga da capacitância de 'gate' do transistor de memorização conectado como diodo. Se a carga desta capacitância não for completada durante o intervalo de tempo em que a chave S está fechada, surgirá um erro na tensão  $V_{\rm gs}$  armazenada, produzindo um erro na corrente reproduzida na saída.

$$\delta I_{ds} = \delta V_{os}, g_{m}$$

[II.13]

Esse comportamento causa restrições na resposta em frequência da célula de memória. O tempo para as fases de armazenamento e reprodução devem ser suficientes para que os erros de 'settling' sejam evitados.

Esses tempos dependem basicamento do valor da corrente amostrada e do tamanho do transistor de armazenamento.

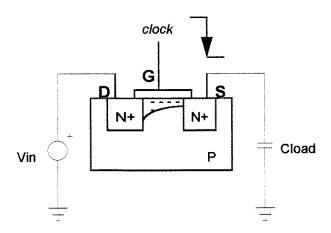

# II.3.4. Erros de injeção de carga

Na fase de reprodução de corrente de uma célula de memória, a tensão  $V_{\rm gs}$  do transistor de memorização deve ser a mesma armazenada na fase de amostragem. A carga do capacitor C é estabelecida através de chaves que na prática são implementadas por transistores MOS.

figura II.3 - Desligamento de uma chave numa célula de memória.

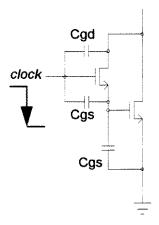

No processo de desligamento de uma chave MOS, cargas móveis formadas na camada de inversão do transistor fluem através de seus terminais de 'drain', 'source' e substrato.

A mudança rápida na tensão do terminal de 'gate' causa o fluxo de cargas através da capacitância intrínseca de 'gate' pelos terminais de 'source' e 'drain'. Uma fração desta carga, é absorvida pela capacitância  $C_{\rm gs}$  do transistor de memorização, produzindo um erro  $\delta V$  na tensão de amostragem e consequentemente um erro  $\delta I$  na corrente de saída.

O problema de injeção de carga [7,8,9] foi identificado nos primeiros ensaios da técnica de Capacitores Chaveados. Desde então, vários modelos foram propostos para se trabalhar com esse fenômeno.

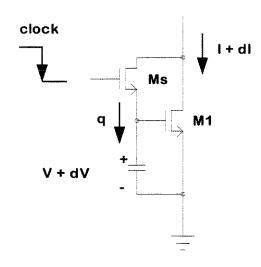

Seja o circuito da figura II.4.

figura II.4 - circuito para análise de injeção de carga.

Fazendo uma análise incremental do circuito e aplicando a lei dos nós vem:

$$C_1 \frac{dv_1}{dt} = -i_d + \left(\frac{C_g}{2}\right) \frac{d}{dt} \left[v_g - v_1\right]$$

[II.14]

$$i_s + C_s \frac{dv_s}{dt} = i_d + \left(\frac{C_g}{2}\right) \frac{d}{dt} \left[v_g - v_s\right]$$

[II.15]

Supondo que a tensão de 'gate', v<sub>g</sub> varia linearmente com o tempo:

$$v_g = v_h - u.t [II.16]$$

onde v<sub>h</sub>: Tensão de chavemento no nível alto u: taxa de variação de v<sub>g</sub> com o tempo

Considerando que, para baixos níveis de diferença de potencial entre 'drain' e 'source' ( $V_{ds} \cong 0$ ), a corrente de 'drain' segue a equação:

$$i_d = \beta (V_{gs} - V_t) V_{ds}$$

[II.17]

onde  $\begin{aligned} v_{\mathsf{d}s} &= v_1 - v_s \\ \beta &= \mu C_{\mathsf{ox}} \left[ \frac{W}{L} \right] \end{aligned}$

Definindo a variável v<sub>ht</sub>:

$$\mathbf{v}_{ht} = \mathbf{v}_{h} - \mathbf{v}_{s} - \mathbf{v}_{te} \tag{II.18}$$

onde vte: tensão de limiar efetiva

Tem-se então:

$$i_{d} = \beta (v_{g} - v_{s} - v_{t})(v_{1} - v_{s})$$

$$i_{d} = \beta (v_{h} - u.t - v_{s} - v_{t})(v_{1} - v_{s})$$

$$i_{d} = \beta (v_{ht} - u.t)(v_{1} - v_{s})$$

[II.19]

Combinando as equações [II.14], [II.15] e [II.19] e depois de alguns arranjos matemáticos vem:

$$\left(C_1 + \frac{C_g}{2}\right) \frac{d\mathbf{v}_1}{dt} = -\beta \left(\mathbf{v}_{ht} - \mathbf{u} \cdot \mathbf{t}\right) \left(\mathbf{v}_1 - \mathbf{v}_s\right) + \left(\frac{C_g}{2}\right) \mathbf{u}$$

[II.20]

$$\left(C_s + \frac{C_g}{2}\right) \frac{dv_s}{dt} = \beta \left(v_{ht} - u.t\right) \left(v_1 - v_s\right) + \left(\frac{C_g}{2}\right) u - \frac{v_s}{r_s}$$

[II.21]

Admitindo-se que  $C_1 >> C_g/2$  e  $C_s >> C_g/2$ , então:

$$C_1 \frac{dv_1}{dt} = -\beta \left(v_{ht} - u.t\right) \left(v_1 - v_s\right) + \left(\frac{C_g}{2}\right) u$$

[II.22]

$$C_s \frac{dv_s}{dt} = \beta (v_{ht} - u.t)(v_t - v_s) + \left(\frac{C_g}{2}\right)u - \frac{v_s}{r_s}$$

[II.23]

À partir dessas equações, importa saber qual o incremento de carga no capacitor C<sub>I</sub> após a transição de abertura da chave. Uma medida deste incremento pode ser feita através da relação Q<sub>I</sub>/Q<sub>ch</sub>, onde Q<sub>ch</sub> é a carga no canal antes da abertura.

$$Q_1 = C_1.dv_1 [II.24]$$

$$Q_{ch} = C_{ox}(v_h - v_{te} - v_s) = C_{ox}, v_{ht}$$

[II.25]

Para chegar às equações numéricas das equações, utiliza-se a transformação:

$$\mathbf{B} = \mathbf{v}_{ht} \sqrt{\frac{\beta}{\mathbf{u}.C_t}}$$

[II.26]

E obtem-se uma família de curvas parametrizadas por C<sub>s</sub>/C<sub>l</sub>.

figura II.5 - Curvas de QI/Qch parametrizadas por Cs/CI.

De acordo com as curvas da figura II.5, observa-se que quando as capacitâncias  $C_s$  e  $C_l$  são iguais, ou seja  $C_s/C_l$  = 1, a relação  $Q_l/Q_{ch}$  é sempre igual a 0,5, de forma que no desligamento da chave MOS, a carga do canal do transistor escoa pelos terminais de 'drain' e 'source' em porções iguais.

Quando a capacitância  $C_s$  vai aumentando em relação a  $C_l$ , a quantidade de carga absorvida por  $C_l$  diminui. Pelas curvas da figura II.5, se  $C_s$  = 100. $C_l$ , apenas 10% da carga do canal toma o caminho da capacitância  $C_l$ .

Para se minimizar o efeito de injeção de carga, podem ser adotadas 2 soluções:

- 1) Fazer  $C_s >> C_l$  e minimizar a porção de carga a ser absorvida pela capacitância de carga  $C_l$ .

- 2) Produzir uma situação em que a porção de carga que toma o caminho de  $C_l$  seja sempre conhecida. E desta forma, adotar medidas complementares para a eliminação desta carga de erro. Isso pode ser conseguido fazendo-se  $C_s = C_l$  ou então fazendo com que o fator B seja pequeno (por exemplo, fazendo u tender para infinito).

Dentre essas duas soluções a primeira não é prática, uma vez que seria necessário uma capacitância C<sub>s</sub> muito grande para reduzir a porção de carga Q<sub>I</sub> a valores desprezíveis. A segunda solução, particularmente a que procura fazer com que B assuma um valor pequeno, é a mais prática, uma vez que pode ser conseguida sem manipulações com as capacitâncias do circuito, ou

seja, fazendo com que a tensão de controle da chave  $\mathbf{v}_{g}$  apresente transições rápidas (u assumindo um valor alto).

Desta forma, a quantidade de carga que será absorvida pela capacitância de carga C<sub>1</sub> será sempre metade da carga formada no canal do transistor que opera como chave.

# CAPÍTULO III

# Simulações de algumas configurações de espelhos

#### III.1. O simulador elétrico e os parâmetros de simulação

Já pensando na implementação do circuito, foi escolhida a 'Foundry' AMS (Austrian Mikro Sistemes) [35] para a execução do Circuito Integrado referente a este projeto. Foi feita essa escolha por dois motivos principais: 1) É uma 'v 'foundry' experimentada por pesquisadores da Telebrás (Telecomunicações Brasileiras) e EFEI (Escola Federal de Engenharia de Itajubá), que têm desenvolvido circuitos em SI com resultados bastante positivos [31]; 2) A AMS faz parte do grupo de "Foundries" que executam circuitos para o Projeto Multiusuário Paulista financiado pela FAPESP (Fundação de Amparo à Pesquisa do Estado de São Paulo), por onde será possível realizar a integração do circuito projetado num espaço de tempo relativamente curto.

Como software de simulação, foi escolhido o PSPICE versão 4.05 da Microsim Corporation [4], devido a boa qualidade dos dados obtidos e de sua versatilidade em relação a equipamentos de simulação, já que 'roda' em qualquer plataforma PC equipada com Co-Processador Aritmético e 4Mbytes de memória RAM, hoje uma configuração bastante comum.

Foram utilizados portanto os parâmetros elétricos para o PSPICE, referentes aos transitores NMOS e PMOS, componentes principais do sistema projetado. Esses parâmetros estão listados na figura III.1 para o caso típico.

| NMOS                                                                                                            |                                                                                                                    |                                                                                                                       |                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| LEVEL=2<br>CJ=0.360E-03<br>JS=0.010E-03<br>XJ=0.175E-06<br>NSUB=33.30E+15<br>UCRIT=28.70E+04<br>DELTA=0.000E+00 | CGSO=0.290E-09<br>MJ=0.430E+00<br>PB=0.960E+00<br>LD=-0.050E-06<br>NFS=0.452E+12<br>UEXP=0.251E+00<br>KF=0.101E-25 | CGDO=0.290E-09<br>CJSW=0.250E-09<br>RSH=25.50E+00<br>WD=0.398E-06<br>NEFF=5.250E+00<br>UTRA=0.000E+00<br>AF=1.330E+00 | CGBO=0.170E-09<br>MJSW=0.190E+00<br>TOX=23.80E-09<br>VTO=0.736E+00<br>UO=515.0E+00<br>VMAX=77.30E+03<br>XQC=0.499 (*)  |

| PMOS                                                                                                            |                                                                                                                    |                                                                                                                       |                                                                                                                        |

| LEVEL=2<br>CJ=0.340E-03<br>JS=0.020E-03<br>XJ=0.056E-06<br>NSUB=18.00E+15<br>UCRIT=21.60E+04<br>DELTA=0.798E+00 | CGSO=0.290E-09<br>MJ=0.530E+00<br>PB=0.970E+00<br>LD=0.043E-06<br>NFS=1.300E+12<br>UEXP=0.268E+00<br>KF=0.390E-27  | CGDO=0.290E-09<br>CJSW=0.220E-09<br>RSH=46.00E+00<br>WD=0.448E-06<br>NEFF=3.090E+00<br>UTRA=0.000E+00<br>AF=1.290E+00 | CGBO=0.170E-09<br>MJSW=0.200E+00<br>TOX=23.80E-09<br>VTO=-0.751E+00<br>UO=175.0E+00<br>VMAX=54.00E+03<br>XQC=0.499 (*) |

<sup>(\*)</sup> vide referência bibliográfica [34].

figura III.1 - Parâmetros elétricos para PSPICE dos transistores NMOS e PMOS

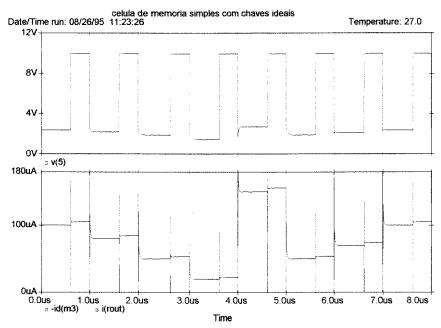

#### III.2. O espelho simples com chaves ideais

Iniciando os estudos dos espelhos dinâmicos de corrente, foi simulado o espelho simples [6], onde foi possível confirmar o princípio de funcionamento

desses circuitos, bem como visualizar a ocorrência dos principais desvios. Nessa primeira simulação foram utilizadas chaves ideais.

Para essa simulação foi utilizado o circuito da figura III.2.

Vale fazer um comentário a respeito da chave ideal utilizada nesta simuação. O PSPICE na versão utilizada neste trabalho (v. 4.05), já modela a chave ideal através de 4 parâmetros:  $R_{on}$  (Resistência da chave no estado ligada),  $R_{off}$  (resistência da chave no modo desligada),  $V_{on}$  (limiar de tensão de controle para estado ligada) e  $V_{off}$  (limiar de tensão de controle para estado desligada) [4]. Segundo alguns resultados consultados na literatura [36], a chave MOS de dimensão mínima possui um valor de  $R_{on}$  que varia entre  $2K\Omega$  e  $10K\Omega$ , enquanto  $R_{off}$  é da ordem de  $1G\Omega$ .

figura III.2 - O espelho simples com chaves ideais.

Na figura III.3 são apresentadas duas curvas que correspondem aos resultados da simulação do circuito da figura III.2.

Na curva inferior estão as corrente de entrada (corrente de 'drain' do transistor  $M_3)$  e saída (corrente pelo resistor  $R_{\text{out}}$ ). No intervalo de 0 a  $0.6\mu s$ , as chaves  $S_1$  e  $S_2$  do espelho estão fechadas, e o espelho está no estado de amostragem da corrente de entrada que é de  $100\mu A$  neste intervalo. De  $0.6\mu s$  a  $1.0\mu s$ , apenas a chave  $S_3$  está fechada, e o espelho se encontra no estado de reprodução da corrente, estabelecida através do resistor  $R_{\text{out}}$ . Posteriormente, as fases de amostragem e reprodução se repetem para outros valores de

corrente de entrada. Essa repetição se dá sempre com 0.6µs para a fase de amostragem e 0.4µs para a fase de reprodução.

| Corrente entrada | Corrente saída | Erro absoluto | Erro percentual |

|------------------|----------------|---------------|-----------------|

| [μ <b>A</b> ]    | [μ <b>Α</b> ]  | [μ <b>Α</b> ] | [%]             |

| 100.87           | 105.54         | 4.74          | 4.7             |

| 80.78            | 85.03          | 4.26          | 5.3             |

| 50.55            | 54.05          | 3.50          | 6.9             |

| 20.29            | 22.56          | 2.27          | 11              |

| 150.88           | 156.41         | 5.52          | 3.7             |

| 50.57            | 54.02          | 3.45          | 6.8             |

| 70.67            | 74.71          | 4.04          | 5.7             |

| 100.81           | 105.56         | 4.75          | 4.7             |

figura III.3 - Resultado da simulação.

Entre as correntes de entrada e saída, existe um erro absoluto que vai de  $2,27\mu A$  (para  $20\mu A$  de corrente de entrada) até  $5,52\mu A$  (para  $150\mu A$  de corrente de entrada) que correspondem respectivamente a menor e maior correntes de entrada aplicada. Esses valores representam erros percentuais entre 3,7 e 11%.

A curva superior dá a tensão no 'drain' do transistor  $M_1$ . Pela grande variação observada neste gráfico, pode-se prever desvios devido ao efeito de modulação de canal neste transistor. No intervalo de 3,0 e 4,0 $\mu$ s, quando ocorre o maior erro percentual de amostragem/reprodução do espelho, observa-se também a maior variação da tensão de 'drain' de  $M_1$ .

Para o resultado apresentado na figura III.3, a fonte de erro predominante é mesmo a modulação de canal observada no espelho  $M_1$ .

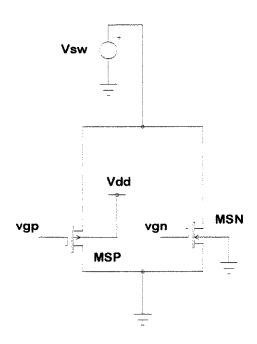

#### III.3. As chaves MOS

Chaves analógicas são comumente implementadas por transistores MOS, sejam de canal N ou P [36].

A chave ideal quando no estado ON, deve apresentar resistência e tensão nulas entre os terminais de contato. No estado OFF, deve apresentar uma resistência infinita, isolando completamente os terminais. E ainda a tensão de controle não influencia o sinal que está sendo chaveado.

O transistor MOS operando como chave, é configurado com o terminal de 'gate' como controle do estado da chave (ON ou OFF), os terminais de 'drain' e 'source' como contatos, e o substrato aterrado para transistor NMOS ou ligado na alimentação para transistor PMOS.

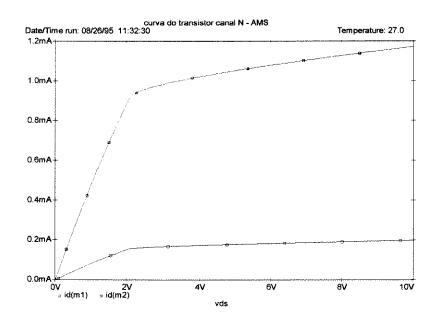

Sejam as curvas  $I_d$  (corrente de 'drain') x  $V_{ds}$  (tensão entre 'drain' e 'source') de dois transistores mostradas na figura III.4.

figura III.4 - curvas características de 2 transistores NMOS.

A curva superior é a de um transistor de dimensões W= $2\mu$ m e L= $1\mu$ m e a inferior W= $1\mu$ m e L= $1\mu$ m. Foi aplicado em ambos os transistores uma tensão entre 'gate' e 'source' de 10 volts.

Para o transistor operar como chave, a tensão entre contatos deve ter valores os menores possíveis. Isso sugere uma tensão  $V_{\rm ds}$  baixa, estando portanto o dispositivo operando na região triodo. Existirá portanto um limite de corrente para a chave a partir da qual o transistor passa a operar na região de saturação, com uma resistência de condução maior, em que variações no sinal chaveado podem representar maiores variações na tensão entre os terminais da chave. Esse limite pode ser controlado pelas dimensões da chave.

Na curva inferior da figura III.4, pode-se observar que a corrente limite para esse transistor operar como chave não atinge  $200\mu A$ . A partir desse valor o transistor começa a entrar na região de saturação e a tensão entre os terminais de contato  $(V_{ds})$  se torna cada vez maior. Na curva superior, o

transistor possui o dobro da largura, e portanto o limite de corrente é maior (~900µA).

As mesmas conclusões são válidas para o transistor PMOS, preservando-se as polaridades dos sinais.

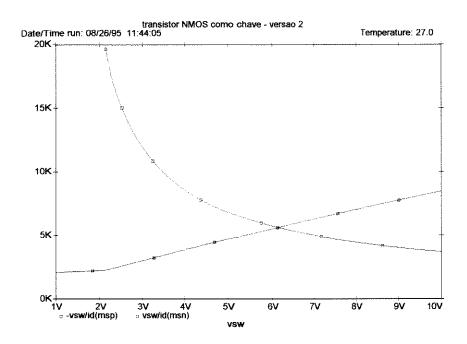

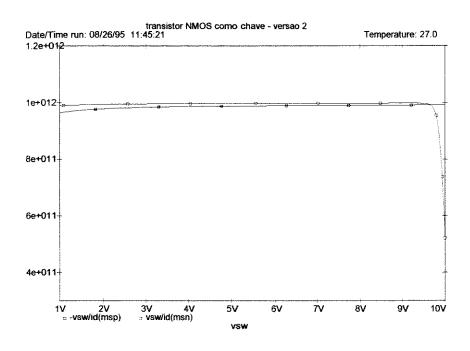

Nas figuras III.5 e III.6 são mostradas as curvas das resistências estáticas de chaves PMOS e NMOS em função da tensão do sinal chaveado.

figura III.5 - resistência das chaves NMOS e PMOS no estado ON.

figura III.6 - resistência das chaves NMOS e PMOS no estado OFF.

Nestas figuras são apresentados resultados simulados, obtidos para o circuito da figura III.7. No estado ON o transistor NMOS está com sua tensão de 'gate' em  $V_{dd}$ , ou seja, 10 volts, enquanto que o transistor PMOS está com o 'gate' aterrado. No estado OFF a situação é a inversa.

Na figura III.5 a curva crescente é a resistência da chave NMOS e a decrescente da chave PMOS. Na figura III.6 as curvas são quase coincidentes.

figura III.7 - circuito utilizado para medida da resistência das chaves.

Pelas curvas da figura III.5 observa-se que a chave NMOS possui um comportamento melhor para sinais de tensão mais baixa, situação em que o transistor está operando na região triodo. A chave PMOS por sua vez apresenta o comportamento inverso. Possui menores resistências de condução quando o sinal assume valores de tensão mais altos.

Uma configuração de chave bastante utilizada é a com transistores complementares (NMOS e PMOS). Neste tipo de chave, os transistores estão ligados em paralelo, e os sinais de controle para cada transistor são invertidos. Desta forma, quando a chave está no estado ON, no terminal de 'gate' do transistor NMOS é aplicada a tensão da fonte,  $V_{dd}$ , e o terminal de 'gate' do transistor PMOS é aterrado. No estado OFF, a situação se inverte.

Desta forma, analisando novamente as curvas da figura III.5, conclui-se que a chave complementar apresentará no estado ON uma resistência aproximadamente constante, independente da tensão do sinal chaveado.

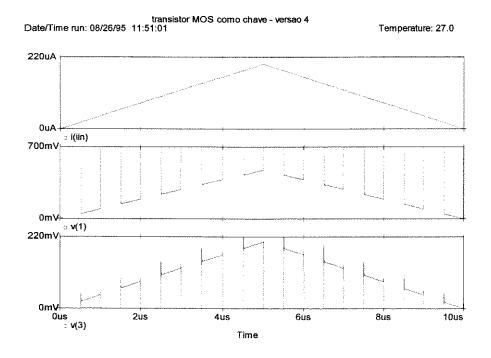

Na figura III.8 é mostrada uma simulação desta configuração de chave, com a aplicação de um sinal de corrente. Na figura III.9 está apresentado o circuito simulado. É aplicada na chave uma corrente variável  $I_{in}$ , a qual é chaveada a cada  $0.5\mu s$ . O sinal é entregue a uma resistência de carga de  $1K\Omega$ .

figura III.8 - simulação da chave MOS complementar.

figura III.9 - chave MOS complementar (circuito simulado).

Para a chave da figura III.9 tem-se que a sua resistência  $R_{on}$  está em torno de  $2K\Omega$ ,  $R_{off}$   $10G\Omega$ , e a queda de tensão nos terminais de contato é de 0,4volts para uma corrente de entrada de  $200\mu A$ .

#### III.4. O espelho dinâmico simples com chaves MOS

figura III.10 - Espelho dinâmico simples com chaves complementares CMOS.

Na figura III.10 é apresentado o circuito para a simulação do espelho dinâmico implementado com chaves MOS complementares. São injetadas diferentes valores de corrente de entrada. No intervalo de 0 a  $0.5 \mu s$  as chaves  $S_1$  e  $S_2$  estão fechadas e o espelho se encontra na fase de amostragem da corrente de entrada. De 0.5 a  $1.0 \mu s$   $S_1$  e  $S_2$  estão abertas e  $S_3$  fechada; é então a fase de reprodução da corrente. Posteriormente, os ciclos se repetem para diferentes valores de corrente de entrada.

É apresentado ainda na figura III.10, um circuito gerador das fases de amostragem e reprodução do espelho. Nada mais é que dois inversores CMOS ligados em cascata, gerando duas formas de onda quadradas com níveis simétricos. Esses sinais são aplicados nos 'gates' dos transistores configurados como chaves.

Na figura III.11 temos os sinais da simulação do circuito da figura III.10. A primeira curva dá a tensão de 'drain' do transistor de memorização. Observa-se novamente que essa tensão varia bastante entre as fases de amostragem e reprodução. Na segunda curva, vê-se as correntes de entrada e saída, e o erro existente entre elas, devido principalmente a modulação de canal. Neste caso o erro absoluto máximo foi de 21,25μA e o mínimo de 6,85μA. O erro percentual esteve entre 13,6 e 32,0%. Comparando-se com os resultados para chaves ideais, verifica-se que o erro com chaves MOS aumentou bastante. Isso devido aos efeitos de injeção de carga e 'Clock Feed Through' (CFT) causados pela introdução das chaves MOS [20,23,25].

O erro de injeção de carga se deve as cargas acumuladas no canal dos transistores configurados como chave, que no momento do desligamento das mesma, procuram um ponto de compensação. Um desses pontos é o 'gate' do transistor de memorização. Desta forma, a carga na capacitância  $C_{\rm gs}$  intrínseca do transistor é alterada e consequentemente muda o valor da tensão  $V_{\rm gs.}$  A

corrente na fase de reprodução será portanto diferente da corrente amostrada [23].

| Espelho simples com chaves CMOS - Resultados numéricos |                |               |                 |

|--------------------------------------------------------|----------------|---------------|-----------------|

| Corrente entrada                                       | Corrente saída | Erro absoluto | Erro percentual |

| [μ <b>A</b> ]                                          | [μ <b>A</b> ]  | [μ <b>Α</b> ] | [%]             |

| 104.72                                                 | 120.78         | 16.06         | 15.3            |

| 84.12                                                  | 97.35          | 13.23         | 15.7            |

| 52.95                                                  | 63.38          | 10.42         | 19.7            |

| 21.41                                                  | 28.26          | 6.85          | 32.0            |

| 155.79                                                 | 177.04         | 21.25         | 13.6            |

| 52.95                                                  | 63.26          | 10.3          | 19.4            |

| 73.76                                                  | 85.80          | 12.04         | 16.3            |

| 104.72                                                 | 120.77         | 16.06         | 15.3            |

figura III.11 - Simulação do espelho simples com chaves complementares CMOS.

O erro de CFT, ocorre nas transições da chave S<sub>2</sub>, ligada ao 'gate' do transistor M<sub>1</sub>. No momento em que o circuito passa do estado de amostragem para reprodução, todas as 3 chaves estão também comutando. Neste pequeno intervalo de tempo, os pulsos de alta frequência, que são gerados nas chaves, podem percorrer o circuito através de capacitâncias parasitas, e atingir o 'gate' do transistor M<sub>1</sub>, alterando a tensão estabelecida no estado de amostragem. Isto alterará então a corrente de saída do circuito.

Uma maneira bastante utilizada de se reduzir o erro de injeção de carga é utilizar as chamadas 'Dummy Switches' [25]. No capítulo IV essa configuração de chave será melhor estudada.

Uma forma de se diminuir o erro causado pelo CFT, é fazendo com que o desligamento de  $S_2$  ocorra ligeiramente antes dos chaveamento de  $S_1$  e  $S_3$ . Desta forma, a alteração no valor da tensão de 'gate' de  $M_1$ , será devido apenas a  $S_2$ , eliminando-se a contribuição de  $S_1$  e  $S_3$ .

#### III.5. O espelho dinâmico 'Cascode'

O circuito simulado do espelho dinâmico 'Cascode' [8,24] pode ser visto na figura III.12.

figura III.12 - O espelho dinâmico 'Cascode'.

Na figura III.13 são apresentadas as formas de onda da simulação desse circuito. A primeira curva corresponde a tensão de 'drain' do transistor de memorização. A segunda, as correntes de entrada e saída.

Esta configuração de espelho apresenta uma melhoria significativa quanto a precisão da corrente reproduzida. O transistor 'Cascode' possui uma polarização de 'gate' constante, e sua função é tornar a tensão de 'drain' do transistor de memorização menos sujeita a variações, diminuindo assim o erro de modulação de canal.

Essas simulações foram feitas com as chaves ideais. Isto possibilita analisar essa configuração observando apenas o erro de modulação de canal. As fases de amostragem e reprodução da corrente se processam da mesma forma que no espelho simples.

Pelos resultados obtidos da simulação, observa-se que o erro absoluto mínimo e máximo foram de 2,43µA e 4,38µA respectivamente. O erro percentual esteve entre 2,9 e 12%. Nota-se portanto uma pequena melhoria de precisão em relação ao espelho simples com chaves ideais. Porém pela curva superior da figura III. 13, vê-se que a tensão de 'drain' do transistor de memorização ainda sofre uma variação significativa entre as fases de amostragem e

reprodução. Permanece portanto o erro de modulação de canal, porém em menor intensidade.

| Corrente entrada | Corrente saída | Erro absoluto | Erro percentua |

|------------------|----------------|---------------|----------------|

| [µA]             | [μ <b>Α</b> ]  | [µA]          | . [%]          |

| 100.06           | 104.43         | 4.38          | 4.4            |

| 80.13            | 84.38          | 4.25          | 5.3            |

| 50.14            | 53.82          | 3.68          | 7.3            |

| 20.25            | 22.69          | 2.43          | 12             |

| 149.35           | 153.63         | 4.28          | 2.9            |

| 50.34            | 53.81          | 3.47          | 6.9            |

| 70.37            | 74.14          | 3.77          | 5.4            |

| 100.06           | 104.32         | 4.26          | 4.3            |

figura III.13 - Simulação do espelho dinâmico 'Cascode'.

#### III.6. O espelho dinâmico 'Regulated Cascode'

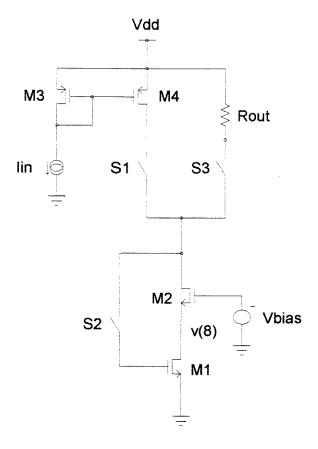

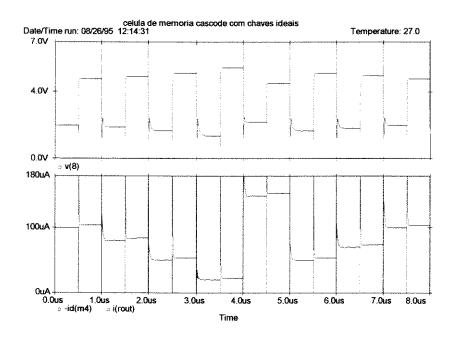

#### III.6.1. Chaves ideais

Uma variação do espelho 'Cascode' é espelho 'Regulated Cascode' [5,10,12], que leva este nome por manter constante a tensão de 'drain' do transistor de memorização através de uma malha realimentada. Este espelho realiza uma melhor compensação do erro de modulação de canal, e portanto, apresenta resultados mais precisos para a corrente saída na fase de reprodução.

As figuras III.14 e III.15 mostram o circuito do espelho 'Regulated Cascode' com chaves ideais e as formas de onda de simulação.

Nota-se na forma de onda da corrente de saída oscilações em torno do valor reproduzido nesta fase. Esta oscilações ocorrem devido a estrutura

realimentada do espelho, que após o chaveamento busca o ponto de estabilidade do circuito.

figura III.14 - O espelho dinâmico 'Regulated Cascode'.

Na curva superior da figura III.15, observa-se que a tensão no terminal de 'drain' do transistor de memorização é constante para a maioria das correntes estabelecidas. Porém para correntes de entrada abaixo de um determinado limite, a tensão no 'drain' na fase de amostragem sofre um decréscimo em seu valor. Isto porém não afeta significativamente a precisão do espelho.

Os erros absolutos máximo e mínimo são respectivamente  $0.21\mu$ A e  $0.05\mu$ A. Os erros percentuais por sua vez, estão entre 0.01 e 0.84%. Nota-se portanto uma grande melhoria na precisão entre os sinais amostrados e reproduzidos.

| Espelho "Regulated Cascode com chaves ideais" Resultados numéricos |                |               |                 |  |

|--------------------------------------------------------------------|----------------|---------------|-----------------|--|

| Corrente entrada                                                   | Corrente saída | Erro absoluto | Erro percentual |  |

| [µA]                                                               | [µA]           | [μA]          | [%]             |  |

| 100.06                                                             | 100.11         | 0.05          | 0.05            |  |

| 80.17                                                              | 80.38          | 0.21          | 0.26            |  |

| 50.23                                                              | 50.30          | 0.08          | 0.16            |  |

| 20.15                                                              | 20.32          | 0.17          | 0.84            |  |

| 149.38                                                             | 149.35         | 0.02          | 0.01            |  |

| 50.23                                                              | 50.34          | 0.11          | 0.22            |  |

| 70.20                                                              | 70.27          | 0.06          | 0.09            |  |

| 100.06                                                             | 100.11         | 0.05          | 0.05            |  |

figura III.15 - Resultados da simulação do espelho 'Regulated Cascode'.

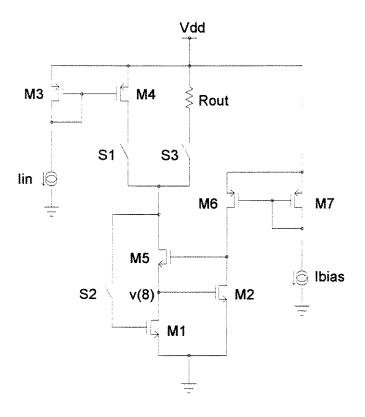

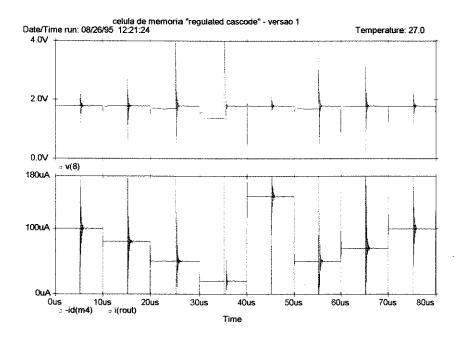

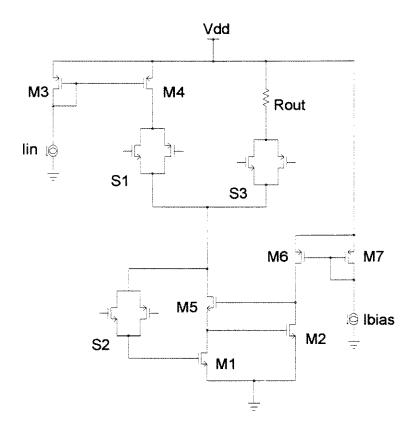

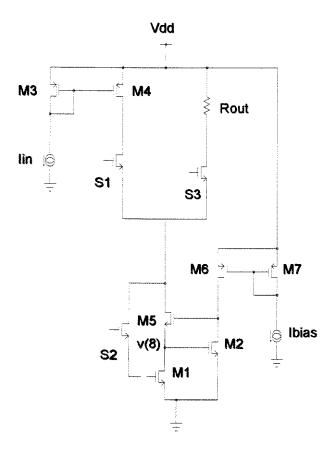

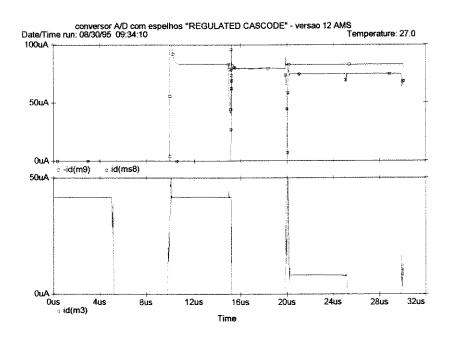

## III.6.2. Chaves CMOS

Nas figuras III.16 e III.17 são apresentadas respectivamente o circuito e as formas de onda da simulação do espelho 'Regulated Cascode' com chaves complementares CMOS.

Percebe-se que os erros absolutos e percentuais aumentam significativamente em relação aos resultados para chaves ideais. Esse aumento se deve aos erros de injeção de carga e 'Clock Feed Through' introduzidos pelas chaves transistorizadas. Outra mudança bastante perceptível é em relação ao comportamento da corrente de saída, que se apresenta bem mais estável em relação aos resultados da figura III.15. As oscilações da malha realimentada foram praticamente suprimidas. Isso ocorreu porque foram otimizadas as dimensões dos transistores do circuito. Na simulação da figura III.15 os transistores que compunham o espelho foram definidos com dimensões iguais de 50μm de largura por 30μm de comprimento. Nos resultados apresentados

na figura III.17 apenas o transistor de memorização  $M_1$  manteve esse padrão alto de dimensões (100 x  $20\mu m$ ), a fim de definir uma capacitância  $C_{gs}$  relativamente alta, para armazenamento da tensão correspondente a corrente amostrada. Os transistores restantes por sua vez foram reduzidos, e tornaram o circuito mais rápido e compacto.

figura III.16 - Espelho dinâmico 'Regulated Cascode' com chaves CMOS.

A amplitude e frequência das oscilações na corrente reproduzida estão relacionadas principalmente com as dimensões dos transistores que compõem a malha realimentada ( $M_2$  e  $M_5$ ). Quanto maiores forem esses transistores, maiores serão suas capacitâncias parasitas, cujos valores determinarão o comportamento das oscilações. Verificou-se que as oscilações reduziam, quando aumentavam-se as dimensões de  $M_2$  e diminuiam-se as de  $M_5$ .

Os erros absolutos dessa configuração com chaves CMOS, estiveram entre 0.21 e  $1.21\mu$ A, enquanto que os erros percentuais variaram entre 0.41 e 1.58%.

| Espelho "Regulated Cascode com chaves CMOS" Resultados numéricos |                |               |                 |

|------------------------------------------------------------------|----------------|---------------|-----------------|

| Corrente entrada                                                 | Corrente saída | Erro absoluto | Erro percentual |

| [µ <b>A</b> ]                                                    | [μ <b>Α</b> ]  | [μ <b>Α</b> ] | [%]             |

| 99.41                                                            | 98.64          | 0.77          | 0.77            |

| 80.36                                                            | 79.81          | 0.55          | 0.68            |

| 51.09                                                            | 50.83          | 0.26          | 0.50            |

| 20.89                                                            | 20.92          | 0.33          | 1.58            |

| 145.06                                                           | 143.85         | 1.21          | 0.83            |

| 51.09                                                            | 50.88          | 0.21          | 0.41            |

| 70.70                                                            | 70.27          | 0.43          | 0.61            |

| 99.39                                                            | 98.59          | 0.80          | 0.80            |

figura III.17 - Simulação do Espelho 'Regulated Cascode' com chaves CMOS.

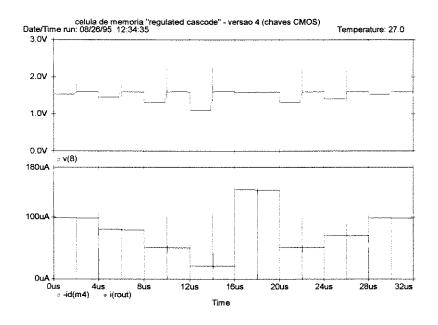

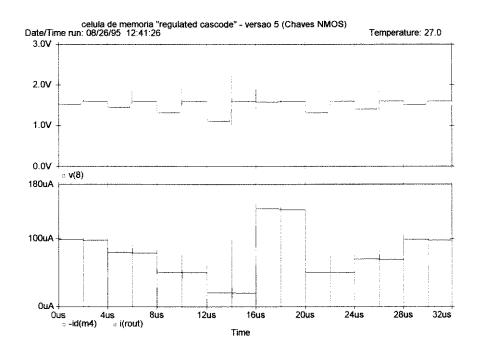

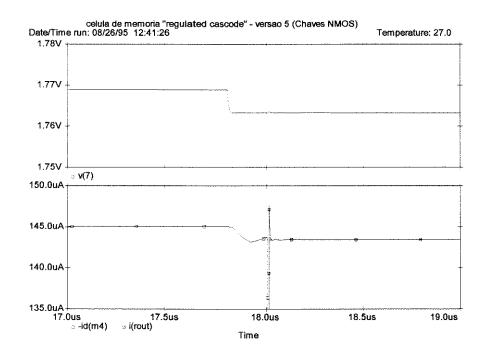

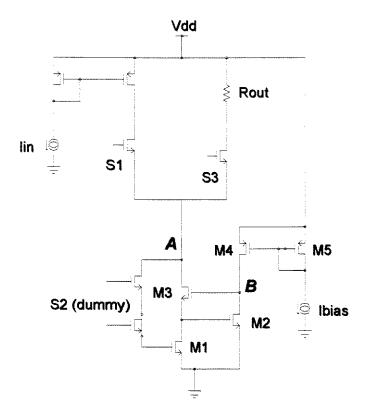

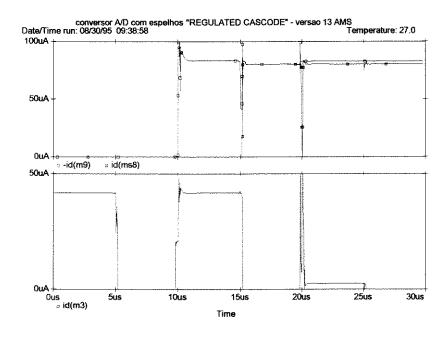

#### III.6.3. Chaves NMOS

Os espelhos dinâmicos de corrente apresentados na literatura não utilizam a configuração de chaves complementares [2,16]. Chaves com apenas um transistor NMOS são capazes de desempenhar bem a função além de simplificar a implementação do circuito nas etapas de edição do 'lay-out', bem como nos sinais de chaveamento do espelho.

Nas figuras III.18 e III.19 são apresentados respectivamento o circuito do espelho com chaves NMOS e as formas de onda da simulação desse circuito.

Analisando os resultados da simulação do espelho com chaves NMOS, verifica-se que os erros absoluto e percentual tiveram um pequeno acréscimo. Isso porque com as chaves complementares os erros de injeção de carga e 'Clock Feed Through' são menos acentuados. Nas chaves CMOS as cargas em trânsito no momento da abertura da chave são tanto positivas (transistor PMOS) quanto negativas (transistor NMOS). Desta forma essas cargas acabam se cancelando e apenas o saldo dessa recombinação será injetado no 'gate' do transistor de memorização. Fato semelhante acontece em relação ao

'Clock Feed Through', em que nas chaves CMOS o sinal de chaveamento também possui duas polaridades, e as influências de cada um são parcialmente anuladas.

figura III.18 - Espelho dinâmico 'Regulated Cascode' com chaves NMOS.

Os erros abolutos para essa configuração estiveram entre 0,19 e 1,59 $\mu$ A e os percentuais entre 0,9 e 1,1%.

| Espelho "Regulated Cascode com chaves NMOS" Resultados numéricos |                |               |                 |

|------------------------------------------------------------------|----------------|---------------|-----------------|

| Corrente entrada                                                 | Corrente saída | Erro absoluto | Erro percentual |

| [uA]                                                             | [uA]           | [uA]          | [%]             |

| 99.40                                                            | 98.29          | 1.11          | 1.1             |

| 80.37                                                            | 79.49          | 0.88          | 1.1             |

| 51.09                                                            | 50.60          | 0.49          | 0.9             |

| 20.89                                                            | 20.70          | 0.19          | 0.9             |

| 145.07                                                           | 143.48         | 1.59          | 1.1             |

| 51.09                                                            | 50.60          | 0.49          | 0.9             |

| 70.70                                                            | 69.96          | 0.75          | 1.1             |

| 99.40                                                            | 98.29          | 1,11          | 1.1             |

figura III.19 - Simulações do espelho 'Regulated Cascode' com chaves NMOS.

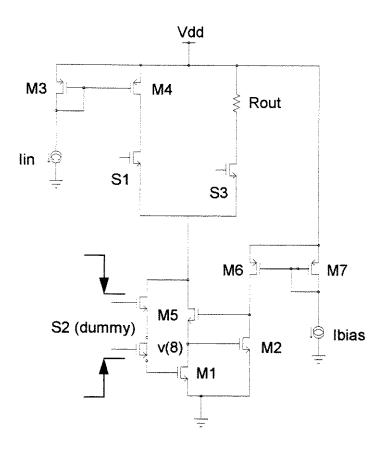

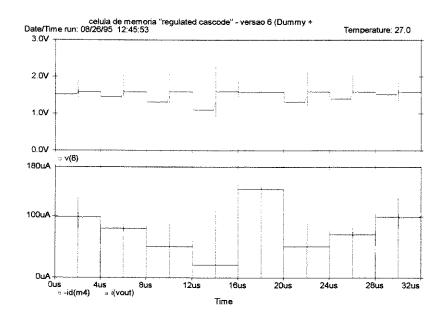

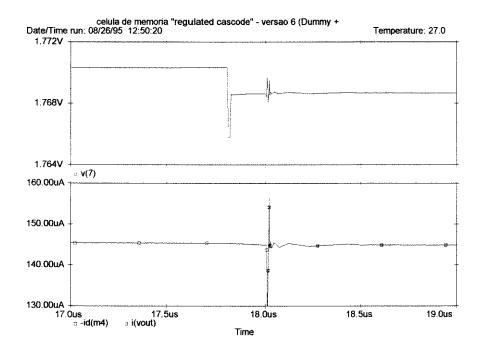

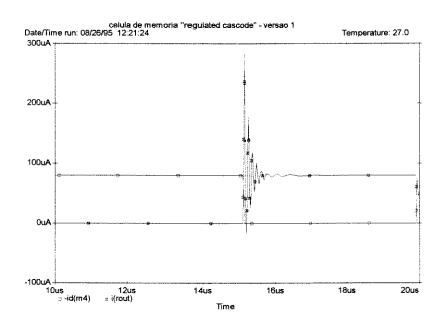

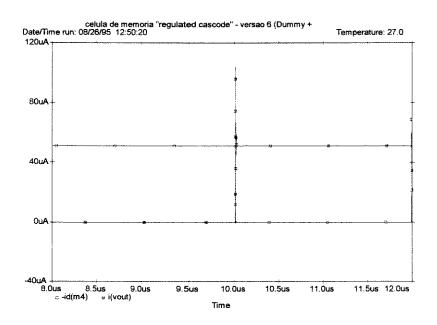

## III.6.4. Chaves 'Dummy'

Uma forma de minimizar os erros devido injeção de carga e 'Clock Feed Through' é utilizando as chamadas 'Dummy Switches' [16,25]. Nas figuras III.20 e III.21 são apresentados o circuito e as formas de onda de simulação para o espelho 'Regulated Cascode' com chaves 'dummy'.

Pelos resultados da figura III.21 percebe-se uma grande melhoria na precisão dos resultados com a utilização das chaves 'dummy'. Os erros absolutos variaram entre 0,04 e 0,46µA enquanto os erros percentuais estiveram entre 0,06 e 0,48%.

As chaves 'dummy' efetuam a diminuição dos erros de injeção de carga e 'Clock Feed Through' introduzindo cargas de polaridade oposta as causadoras do erro de armazenamento na capacitância  $C_{\rm gs}$ , através de um transistor 'dummy', que não possui nenhuma função de chaveamento, mas sim de gerar essas cargas opostas, diminuindo assim a intensidade desses erros. Isso é

conseguido aplicando no 'gate' desse transistor adicional, uma fase de chaveamento invertida da fase do transistor que efetivamente opera como chave.

figura III.20 - O espelho 'Regulated Cascode' com chaves 'dummy'.

Vale observar que apenas a chave ligada ao 'gate' do transistor de armazenamento necessita ser 'dummy', apesar de que nos outros pontos também ocorrem esses erros. Isso porque nesse ponto, a injeção de carga e 'Clock Feed Through' afetam diretamente a precisão do espelho.

| Espelho "Regulated Cascode" com chaves 'dummy'<br>Resultados numéricos |                |               |                 |  |

|------------------------------------------------------------------------|----------------|---------------|-----------------|--|

| Corrente entrada                                                       | Corrente saida | Erro absoluto | Erro percentual |  |

| [uA]                                                                   | [uA]           | [uA]          | [%]             |  |

| 99.48                                                                  | 99.28          | 0.20          | 0.20            |  |

| 80.41                                                                  | 80.35          | 0.06          | 0.08            |  |

| 51.11                                                                  | 51.17          | 0.05          | 0.10            |  |

| 20.89                                                                  | 20.99          | 0.10          | 0.48            |  |

| 145.44                                                                 | 144.98         | 0.46          | 0.32            |  |

| 51.11                                                                  | 51.16          | 0.06          | 0.12            |  |

| 70.75                                                                  | 70.70          | 0.04          | 0.06            |  |

| 99.49                                                                  | 99.28          | 0.21          | .021            |  |

figura III.21 - Simulações do espelho 'Regulated Cascode' com chaves 'dummy'.

#### III.7. Análise comparativa dos espelhos simulados

Uma maneira de se analisar o desempenho de cada um dos espelhos simulados, é comparar os erros absolutos e percentuais máximos de cada um deles. Isso é feito na tabela da figura III.22.

Dentre os espelhos simulados com chaves transistorizadas (CMOS, NMOS ou 'dummy'), o que apresentou menores erros absolutos e percentuais foi o espelho "Regulated Cascode" com chaves 'dummy' (0,46µA e 0,48%).

Esses resultados comprovam a eficiência das configurações tanto do espelho 'Regulated Cascode' como da chave 'dummy', já estudados e implementados por outros autores [5,10,12]. Uma característica importante dessas configurações simuladas, é que todas possuem a mesma sequência simples de chaveamento.

Outras configurações de espelho tais como S<sup>2</sup>I [9], 'Algorithmic' [7], S<sup>n</sup>I [19], 'Muller-enhanced' [16], 'Folded-Cascode' [2], 'Error feedback' [14] e configurações diferenciais [32], também são capazes de produzir resultados

com boas precisões. A configuração 'Regulated Cascode' porém, é a que apresenta melhor compromisso entre precisão dos resultados e complexidade do circuito das fases de amostragem de corrente. É constituído basicamente de 3 transistores mais uma fonte de corrente, a qual pode ser compartilhada por outras células. E os sinais de controle das fases são os mesmos que para a célula de memória simples. Isso facilita muito na implementação de uma aplicação em corrente chaveada.

| Performance dos espelhos dinâmicos simulados |                  |                              |                               |  |

|----------------------------------------------|------------------|------------------------------|-------------------------------|--|

| Configuração                                 | Tipo de<br>chave | Erro Absoluto<br>máximo [μΑ] | Erro percentual<br>máximo [%] |  |

| Simples                                      | ideal            | 5.52                         | 11                            |  |

| Simples                                      | CMOS             | 21.25                        | 32                            |  |

| Cascode                                      | ideal            | 4.38                         | 12                            |  |

| "Reg. Cascode"                               | ideal            | 0.21                         | 0.84                          |  |

| "Reg. Cascode"                               | CMOS             | 1.21                         | 1.58                          |  |

| "Reg. Cascode"                               | NMOS             | 1.59                         | 1.1                           |  |

| "Reg. Cascode"                               | 'dummy'          | 0.46                         | 0.48                          |  |

figura III.22 - Performance dos espelhos simulados.

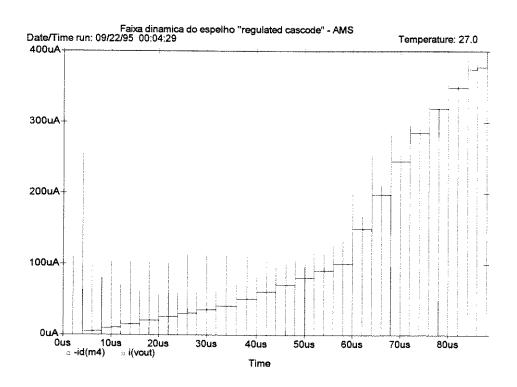

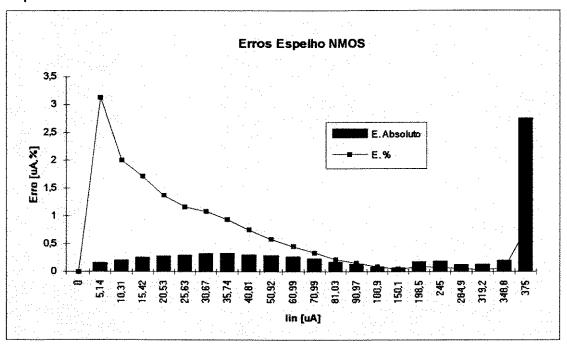

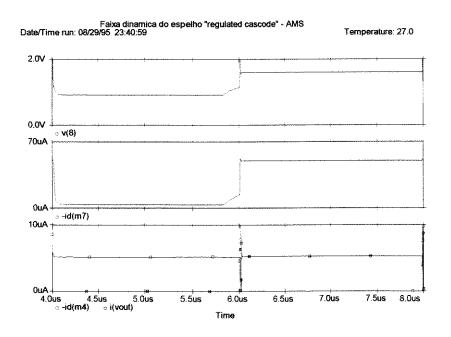

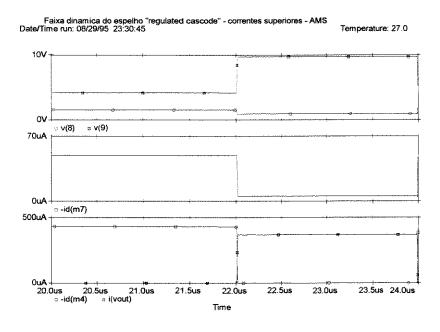

# III.8. Faixa dinâmica do espelho 'Regulated Cascode' NMOS

Para a utilização do espelho 'Regulated Cascode' como célula básica para um conversor A/D, é fundamental conhecer a faixa dinâmica deste espelho, ou seja, os valores de corrente de entrada que o espelho é capaz de armazenar dentro de uma determinada precisão mínima [28]. Na figura III.23 são apresentadas as curvas de simulação do mesmo circuito da figura III.20 para um número maior de níveis corrente de entrada.

Na figura III.24 é apresentado o resultado da figura III.23 em forma de gráfico. Neste gráfico nota-se que o espelho mantém um erro absoluto máximo de aproximadamente 0,335µA (desconsiderando o último ponto) e percentual de 3,13%. Porém esses níveis, que podem ser considerados elevados, passam a ser aceitáveis para a aplicação num conversor A/D se considerados os seguintes aspectos:

- Para o conversor A/D idealizado, é importante manter um erro absoluto controlado, enquanto o erro percentual tem importância secundária;

- Se considerado que correntes entre 0 e  $200\mu A$  constituem uma faixa dinâmica aceitável para a implementação do conversor A/D, o erro absoluto máximo de  $0,335\mu A$  seria suficiente para obter um conversão digital de até 8 bits.

| Faixa dinâmica do espelho NMOS: |            |      |

|---------------------------------|------------|------|

| lin [uA]                        | E.Abs [uA] | E %  |

| 0                               | 0          | 0    |

| 5,14                            | 0,161      | 3,13 |

| 10,31                           | 0,207      | 2,00 |

| 15,42                           | 0,263      | 1,71 |

| 20,53                           | 0,282      | 1,37 |

| 25,63                           | 0,298      | 1,16 |

| 30,67                           | 0,331      | 1,08 |

| 35,74                           | 0,335      | 0,94 |

| 40,81                           | 0,308      | 0,75 |

| 50,92                           | 0,296      | 0,58 |

| 60,99                           | 0,272      | 0,45 |

| 70,99                           | 0,239      | 0,34 |

| 81,03                           | 0,177      | 0,22 |

| 90,97                           | 0,141      | 0,15 |

| 100,92                          | 0,087      | 0,09 |

| 150,13                          | 0,069      | 0,05 |

| 198,46                          | 0,181      | 0,09 |

| 245,03                          | 0,190      | 0,08 |

| 284,92                          | 0,131      | 0,05 |

| 319,15                          | 0,132      | 0,04 |

| 348,77                          | 0,203      | 0,06 |

| 374,97                          | 2,756      | 0,74 |

figura III.23 - Faixa dinâmica do espelho NMOS

Os erros medidos na simulação são devidos principalmente a injeção de carga e 'Clock Feed Through'. Esses erros são dependentes do sinal de entrada, mas podem ser bastante reduzidos com a utilização das chaves 'dummy'. O melhor desempenho dessa configuração de chave porém, depende do correto dimensionamento dos seus transistores. Existe uma regra prática que diz que o transistor 'dummy' deve ter a metade do tamanho do transistor principal. Porém isso não é muito bem definido e pode não oferecer os melhores resultados [16]. O PSPICE porém não oferece o modelamento de conservação de carga, e portanto não oferece precisão suficiente para se fazer tal otimização. Isso feito, poderia melhorar ainda a precisão do espelho e garantir um maior número de bits de conversão.

Os detalhes sobre a implementação do conversor A/D, estão descritos no capítulo IV.

figura III.24 - Faixa dinâmica do espelho NMOS

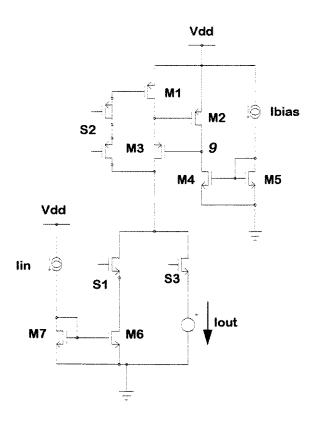

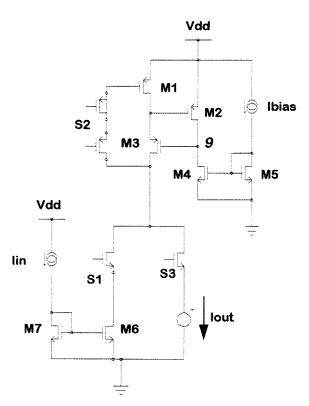

#### III.9. O espelho dinâmico 'Regulated Cascode' PMOS

O algoritmo de conversão análogo-digital exige células de memória de ambas as polaridades.

Na figura III.25 é apresentada a simulação do espelho PMOS para determinação de sua faixa dinâmica. O circuito é simétrico ao apresentado na figura III.20.

figura III.25 - O Espelho 'Regulated Cascode' PMOS.

# III.10. Faixa dinâmica do espelho 'Regulated Cascode' PMOS

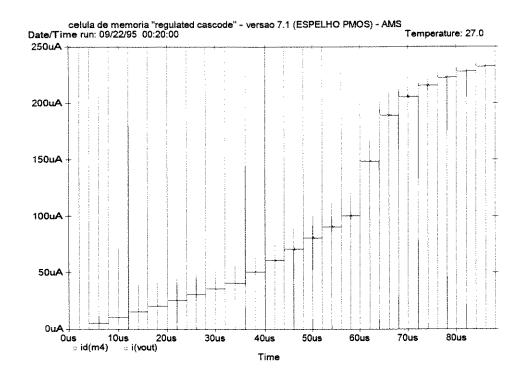

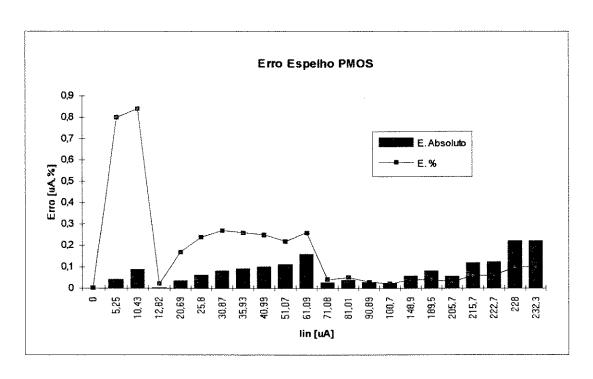

Na figura III.26 é apresentado o resultado de uma simulação para determinação da faixa dinâmica do espelho PMOS:

Na figura III.27 temos o resultado da figura III.26 em forma de gráfico. O espelho PMOS obteve um desempenho um pouco melhor em relação ao NMOS, com um erro absoluto máximo de 0,222µA e percentual de 0,80%. Possui porém uma faixa dinâmica de trabalho reduzida, conforme nota-se pela faixa de valores de corrente de entrada aplicadas ao circuito.

Considerando uma faixa de 0 a  $200\mu A$ , o espelho PMOS obteve um erro absoluto máximo de  $0,102\mu A$ , o que a princípio permite a implementação de um conversor A/D de até 9 bits.

| Faixa dinâmica do espelho PMOS: |             |      |

|---------------------------------|-------------|------|

| lin [uA]                        | E. Abs [uA] | E. % |

| 0                               | 0           | 0    |

| 5,25                            | 0,042       | 0,80 |

| 10,43                           | 0,088       | 0,84 |

| 12,82                           | 0,002       | 0,02 |

| 20,69                           | 0,036       | 0,17 |

| 25,80                           | 0,062       | 0,24 |

| 30,87                           | 0,082       | 0,27 |

| 35,93                           | 0,093       | 0,26 |

| 40,99                           | 0,102       | 0,25 |

| 51,07                           | 0,112       | 0,22 |

| 61,09                           | 0,160       | 0,26 |

| 71,08                           | 0,027       | 0,04 |

| 81,01                           | 0,038       | 0,05 |

| 90,89                           | 0,028       | 0,03 |

| 100,69                          | 0,024       | 0,02 |

| 148,87                          | 0,058       | 0,04 |

| 189,45                          | 0,082       | 0,04 |

| 205,68                          | 0,057       | 0,03 |

| 215,74                          | 0,119       | 0,06 |

| 222,73                          | 0,124       | 0,06 |

| 228,02                          | 0,222       | 0,10 |

| 232,25                          | 0,221       | 0,10 |

figura III.26 - Faixa dinâmica do espelho PMOS

figura III.27 - Faixa dinâmica do espelho PMOS

# **CAPÍTULO IV**

# Implementação do ADC

#### IV.1. Introdução

Para as simulações do conversor A/D foram utilizados os mesmos modelos dos espelhos dinâmicos, apresentados no capítulo III. O simulador também foi o PSPICE 4.05 da MicroSim.

O algorítimo de conversão segue o método de aproximações sucessivas, determinando primeiramente o bit mais significativo e em seguida os próximos [11,17,22]. O número de bits de conversão é limitado apenas pela precisão da célula de armazenamento da corrente. O resultado é processado de maneira sequencial, de forma que com a mesma estrutura do conversor, é possível se obter conversões com número de bits ajustável [15].

O conversor A/D em questão utiliza 3 células de armazenamento de corrente. Essas células serão implementadas pelos já descritos Espelhos Dinâmicos de Corrente. De acordo com as simulações apresentadas no capítulo anterior, a configuração de melhor performance foi a 'Regulated Cascode' com chaves 'dummy'. Essa portanto será utilizada no circuito do conversor.

Na figura IV.1 é apresentado um circuito simplificado do conversor A/D com espelhos dinâmicos simples e chaves ideais. São mostradas também as tensões de controle das chaves, que em cada ciclo de 4 fases executam a conversão de um bit digital. O sinal em nível alto corresponde a chave fechada e em baixo a chave aberta.

Na primeira fase de conversão, as chaves S<sub>1</sub>, S<sub>2</sub> e S<sub>3</sub> estão fechadas e a corrente de entrada I<sub>in</sub> é armazenada no espelho formado pelo transistor M<sub>1</sub>. Na segunda fase, estão fechadas as chaves S<sub>1</sub>, S<sub>4</sub> e S<sub>5</sub>, e a mesma corrente l<sub>in</sub> é armazenada no espelho formado pelo transistor M2. Na terceira fase, fecham-se as chaves S2, S4, S6 e S7, de forma que os espelhos NMOS (formados por M<sub>1</sub> e M<sub>2</sub>) estão reproduzindo a corrente armazenada nas duas primeiras fases, e o espelho PMOS (formado pelo transistor M<sub>3</sub>) está armazenando a soma dessas correntes. Na última fase, apenas Se e Se estão fechadas. O espelho PMOS está portanto, reproduzindo o valor 2.1in (o dobro da corrente de entrada), a qual é comparada com uma corrente de referência Iref. Se 2.Iin for maior que Iref o primeiro bit convertido será 1. Neste caso, nas duas primeiras fases de conversão do próximo bit, a chave S<sub>8</sub> ficará fechada de forma que sejam armazenadas nos espelho NMOS a corrente 2.1in subtraida da corrente de referência Iref. Se na comparação das correntes, 2.Iin foi menor que I<sub>ref</sub>, então S<sub>8</sub> ficará aberta nas duas próximas fases e serão armazenados nos espelhos NMOS o valor de 21in.

O circuito do conversor A/D pode ser dividido em 5 blocos principais:

- 1) A célula de armazenamento de corrente;

- 2) As chaves:

- 3) Os circuitos de entrada;

- 4) O comparador de corrente;

- 5) Gerador dos sinais de controle e registradores de resultado.

figura IV.1 - Circuito simplificado do conversor A/D e as fases de conversão.

Os dois primeiros ítens já foram tratados no capítulo III. A seguir serão apresentadas portanto, as soluções adotadas para os três ítens restantes.

#### IV.2. Os circuitos de entrada

Além dos sinais de controle são duas as entradas para o circuito do conversor A/D, as quais a princípio estão no forma de correntes: o sinal de entrada analógico e o de referência (ou fundo de escala).

Em termos de praticidade e compatibilidade com outros sistemas (de medida ou de aplicação), o ideal seria que esses sinais fossem introduzidos na forma de tensão, o que para o caso deste trabalho, implicaria na implementação de conversores tensão-corrente. Existem inúmeras configurações para este tipo de circuitos. A determinação da mais adequada, não faz parte do objetivo principal traçado e implicaria em maiores riscos na implementação do circuito final. Por este motivo, optou-se por fazer essas entradas na forma de corrente. Nas simulações isso foi feito através de espelhos tradicionais, tomando-se os devidos cuidados para problemas de imprecisão nos valores.

Esses circuitos de entrada estão representados pelos espelhos de corrente simples (PMOS para a corrente de entrada e NMOS para a corrente de referência) no lado esquerdo da figura IV.1.

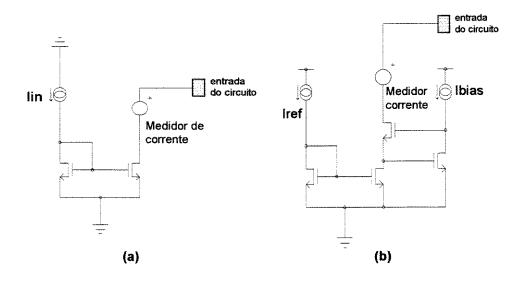

figura IV.2 - Circuito de entrada do conversor A/D.

Na figura IV.2(a) é apresentado o circuito utilizado nas simulações para a introdução do sinal analógico de corrente, e na figura IV.2(b) o circuito de entrada para a corrente de referência. Neste último foi utilizada a mesma estrutura dos espelhos dinâmicos 'Regulated Cascode', com o objetivo de implementar um gerador de corrente de alta impedância e que mantenha um valor preciso durante a operação do conversor A/D.

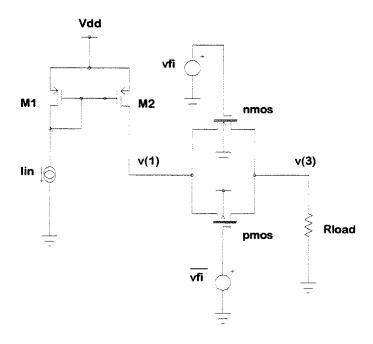

#### IV.3. O comparador de corrente

O comparador de corrente é o bloco de saída do conversor A/D. Ele determina os bits convertidos em cada uma das etapas. É um bloco crítico, já que sua precisão está ligada diretamente a precisão dos resultados de conversão.

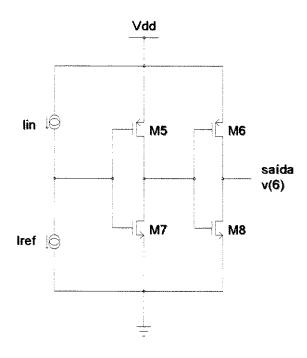

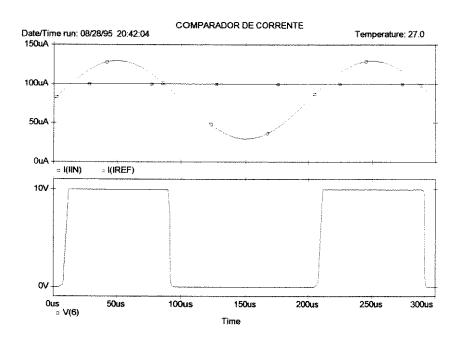

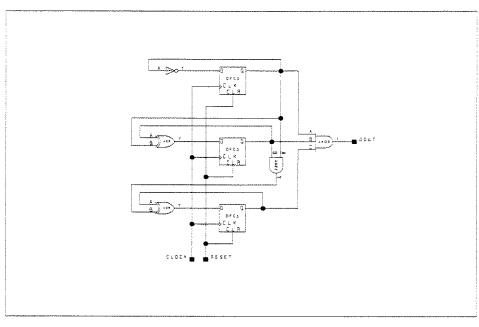

O comparador é formado pelos inversores ligados em cascata [2] no lado direito da figura IV.1. Tal configuração foi testada em simulação e apresentou resultados bastante positivos. O circuito simulado e as formas de onda resultantes estão apresentadas nas figuras IV.3 e IV.4 respectivamente.

figura IV.3 - O comparador de corrente.

figura IV.4 - Simulação do comparador de corrente.

Na simulação do circuito comparador de correntes, foi introduzida uma corrente de referência fixa e uma corrente senoidal, conforme visto nas formas

de onda da figura IV.4. Percebe-se que o sinal de saída (em tensão), comuta no cruzamento destas correntes. Ou seja, quando a corrente de entrada senoidal é maior que a corrente de referência, a saída assume um nível digital alto e quando a corrente de entrada é menor o nível digital é baixo.

Os transistores que compõe os inversores do circuito comparador de correntes foram implementados com dimensões reduzidas (W=1µm e L=1µm), a fim de minimizar as capacitâncias de 'gate' e tornar o circuito mais rápido. Porém, na forma de onda de saída, pode-se notar uma inclinação finita do sinal no momento de comutação de estados. O tempo de resposta máximo do circuito foi de 270ns, o que seria suficiente para operar o conversor A/D a 3,7Mhz. Esse resultado garante a utilização desta configuração de comparador, uma vez que a velocidade de conversão é limitada por outros fatores.

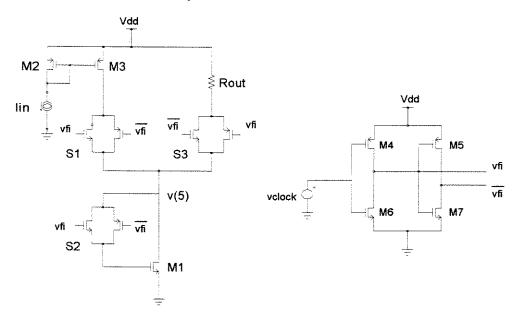

#### IV.4. Gerador dos sinais de controle e registradores de resultado

Esta é a porção digital do conversor.

Lembrando que o objetivo principal deste trabalho é apenas apresentar uma técnica de conversão A/D em corrente chaveada, e estudar os espelhos dinâmicos de corrente, foi poupado o trabalho de implementação destes blocos do circuito do conversor. Será apresentada porém, uma sugestão de projeto para esta parte digital, a qual poderia vir a compor um 'chip' mais elaborado, para o circuito estudado.

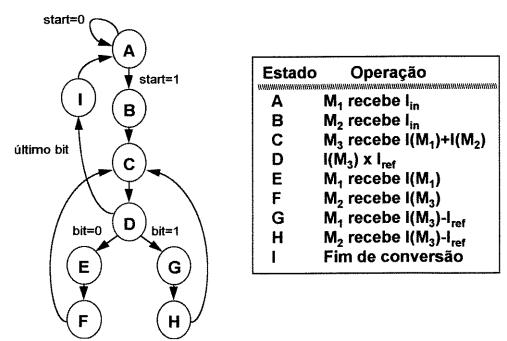

figura IV.5 - Diagrama de estado para o circuito de controle do conversor A/D.

Para as simulações do conversor, os sinais de controle foram gerados por fontes de tensão ideais, enquanto o registro dos resultados foi feito observando-se diretamente o sinal de saída do comparador de correntes.

Para a realização dos testes do circuito integrado, planeja-se implementar esse bloco digital com componentes discretos.

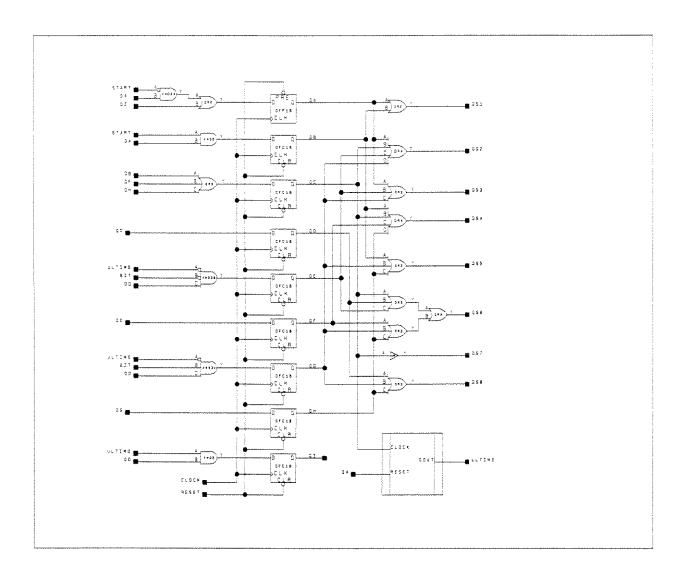

figura IV.6 - Circuito de controle para o conversor A/D.

As vantagens apresentadas por essa escolha são a de concentrar os esforços e cuidados para os blocos que realmente tratam do Processamento de Sinais em Corrente Chaveada, bem como reduzir as chances de erro de implementação do Chip a somente esses blocos.

Os sinais de controle para a conversão do sinal analógico podem ser descritos pelo diagrama de estados mostrado na figura IV.5.

A implementação deste circuito de controle pode ser feita por uma máquina síncrona, estabelecendo-se para cada estado um Flip-Flop tipo D, cujas saídas são realimentadas e através de uma lógica combinacional geram suas próprias entradas. As saídas dos FF's passam por uma lógica combinacional e geram ainda os sinais de controle das chaves. Na figura IV.6 é mostrado a implementação deste circuito.

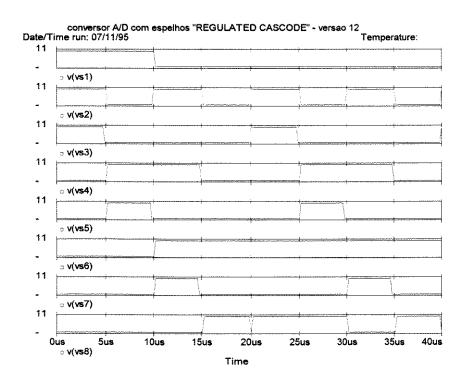

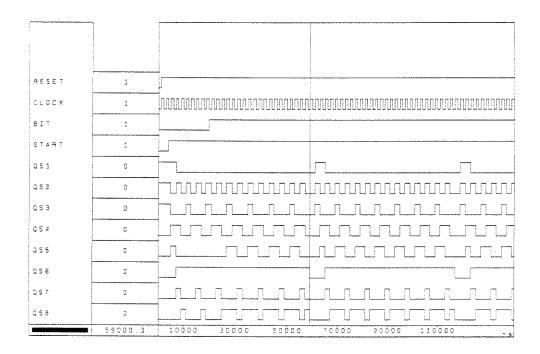

Esse circuito foi simulado gerando as formas de onda da figura IV.7.

figura IV.7 - Sinais de controle das chaves para o conversor A/D.

No primeiro esquema da figura IV.6, é apresentado o diagrama lógico do circuito de controle do conversor A/D. Nesse esquema, existe um bloco cuja saída (denominada 'último'), é ativada quando o conversor está processando o último bit digital. Esse bloco é detalhado logo abaixo, tratando-se de um contador que é incrementado cada vez que a máquina de estados passa pelo estado C. Sendo o contador de módulo n, o número de bits convertidos será sempre (n-1).

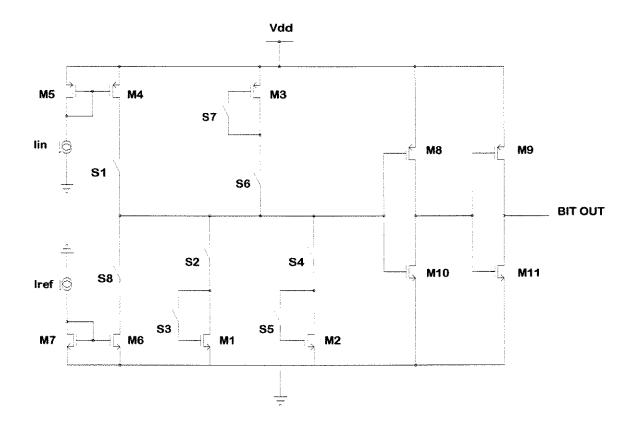

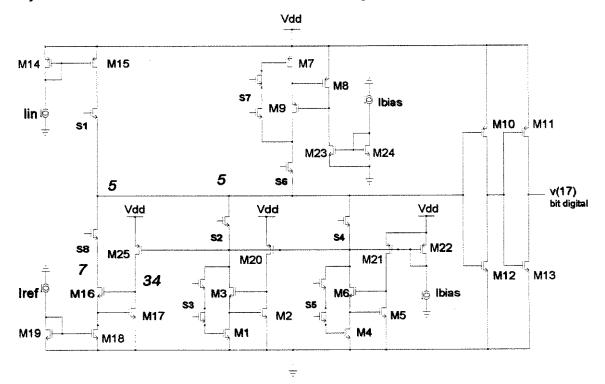

# IV.5. O circuito completo do Conversor A/D em Corrente Chaveada

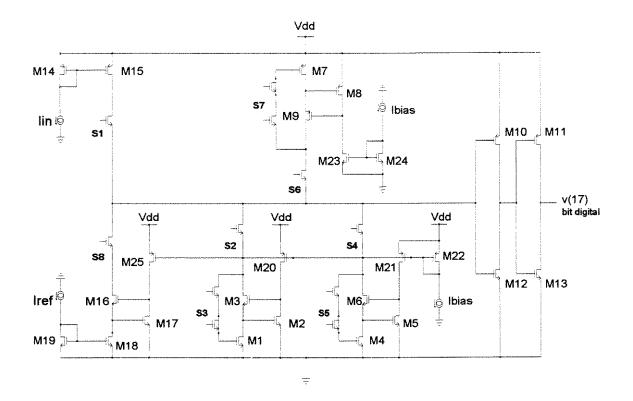

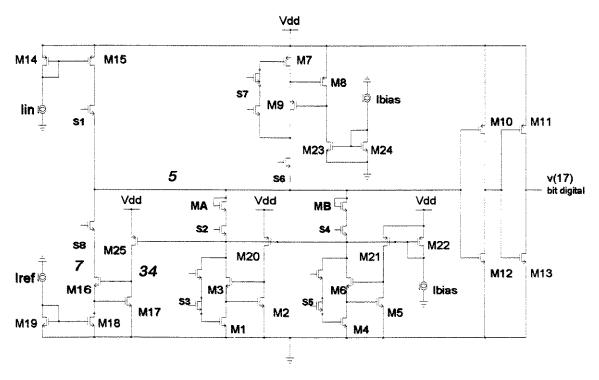

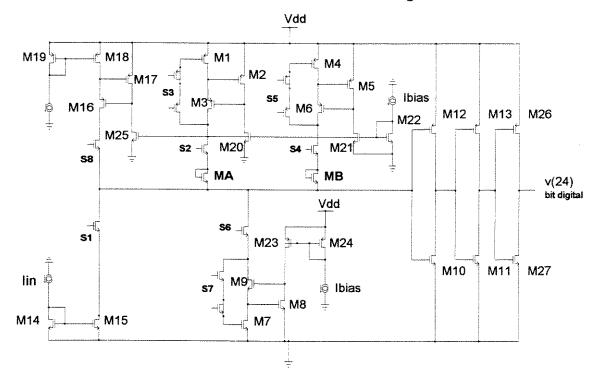

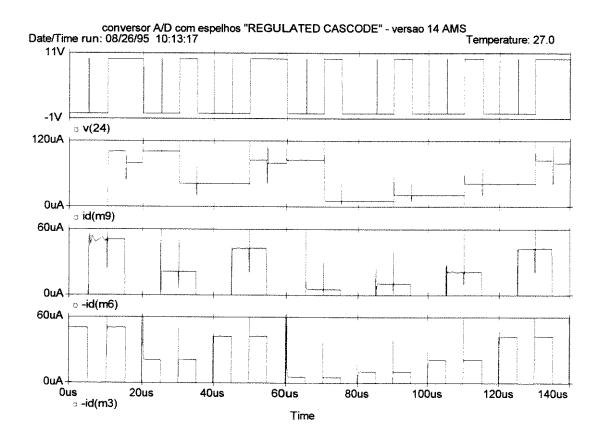

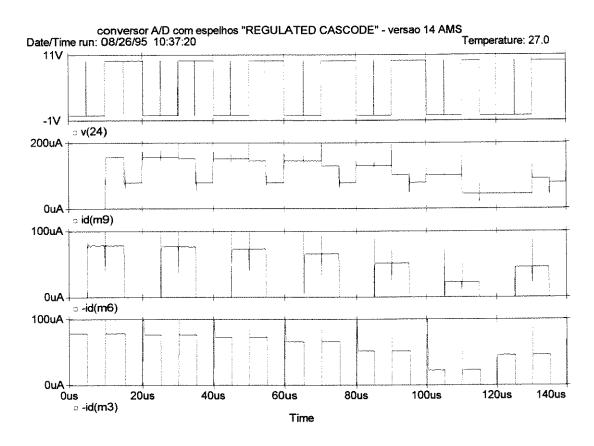

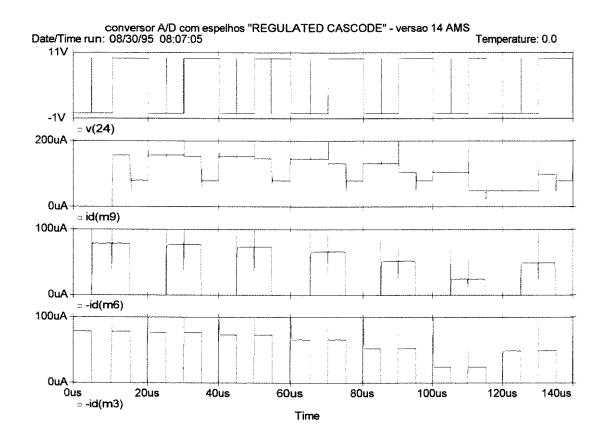

O circuito do conversor A/D com Espelhos 'Regulated Cascode' e chaves 'dummy' estão apresentados na figura IV.8.

figura IV.8 - Circuito completo do conversor A/D.

Para o circuito da figura IV.8, as fases de conversão são as mesmas apresentadas para o circuito simplificado da figura IV.1.

No projeto deste circuito, vários problemas surgiram e foram solucionados. Nas simulações finais foram obtidos resultados satisfatórios quanto o desempenho do circuito em relação a qualidade e precisão dos dados digitais convertidos.

Para acompanhamento da evolução deste projeto, serão destacados os principais problemas enfrentados durante seu desenvolvimento, analisando-se as causas, consequências e soluções adotadas para cada um deles. Eles são:

- 1) Erros por injeção de carga e 'Clock Feed Through';

- 2) Erro por modulação de canal no transistor de armazenamento;

- 3) Dependência da precisão do espelho com o sinal de corrente;

- Oscilações devido a malha de realimentação;

- 5) Variação da corrente de referência com o sinal em conversão;

- Faixa dinâmica reduzida do espelho PMOS.

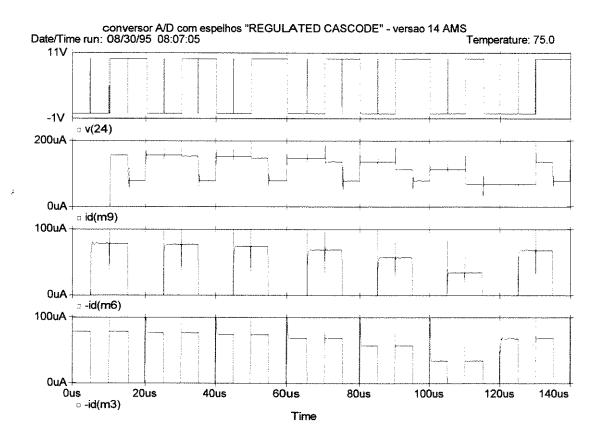

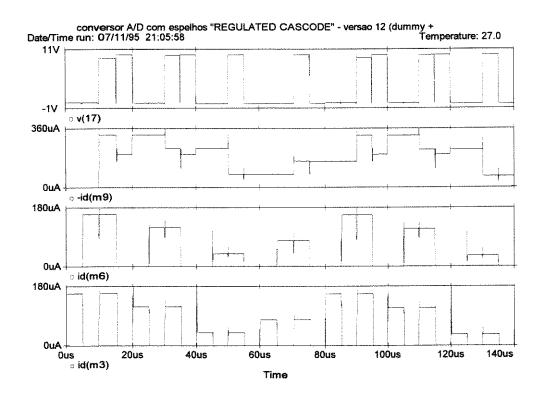

#### IV.5.1. Erros de injeção de carga e 'Clock Feed Through'