## UNIVERSIDADE ESTADUAL DE CAMPINAS FACULDADE DE ENGENHARIA ELÉTRICA

# TESE DE MESTRADO UTILIZAÇÃO DE EQUIPAMENTOS AUTOMÁTICOS DE TESTE EM CIRCUITOS INTEGRADOS DIGITAIS.

AUTOR : Rogério Lara Leite

ORIENTADOR : Dr. José Antônio Siqueira Dias

#### TESE

preparada no

# Departamento de Eletrônica e Microeletrônica - DEMIC da Faculdade de Engenharia Elétrica da UNICAMP

visando a obtenção

### do Título de Mestre em Engenharia Elétrica - FEE/UNICAMP

Especialidade: Eletrônica

por

Rogério Lara Leite 7/536

Engenheiro Eletricista

Utilização de Equipamentos Automáticos de Teste em Circuitos Integrados Digitais

Banca Examinadora:

Prof. Dr. José Antonio Siqueira Dias (Presidente) - DEMIC/FEE/UNICAMP.

Prof. Dr. Laércio Caldeira - Escola Federal De Eng. de ITAJUBÁ - EFEI.

Prof. Dr. Alberto Martins Jorge - DEMIC/FEE/Unicamp.

UNICAMA BIBLIOTECA CENTRAL defendida por Ruyino lava leita de final de tese defendida por Ruyino lava leita leita Comissão Julgadora em 27 09 94 ...

3418972

#### **AGRADECIMENTOS**

Este trabalho contou com a colaboração de várias pessoas sem as quais não teria sido possível realizá-lo. Em especial ao orientador desta tese, professor Dr. José Antônio Siqueira Dias. Também foi muito importante o apoio da TELEBRÁS - Telecomunicações Brasileiras S. A - que forneceu a infra-estrutura necessária ao desenvolvimento deste trabalho.

Para minha esposa

Maria Isabel

e para minhas duas filhas

Helena

e

Júlia.

| 1 | 1 |

|---|---|

Para meus pais pelo incentivo e apoio que recebi.

#### **RESUMO**

Este trabalho comenta alguns aspectos importantes do teste automático de um circuito integrado digital. Apresenta os principais tipos de testes elétricos realizados por um equipamento automático de teste, comentando as diferenças dos testes dependendo da tecnologia do componente, nas diversas fases da vida de um circuito integrado digital. São descritos, de forma suscinta, os principais mecanismos de falhas em CI's digitais e são apresentadas as principais medições elétricas necessárias para avaliar o desempenho de um circuito integrado. Descrevemos também o equipamento automático de teste (ATE) e sua linguagem de programação, comentando como esta máquina é importante para testar circuitos integrados digitais. O trabalho termina com dois programas de teste reais, escritos em Pascal, comentando os resultados das medições de cada programa.

#### ABSTRACT

This work comments some important aspects of the digital integrated circuit automatic test. It presents the most common electrical tests done by an Automatic Test Equipment - ATE. The test differences depending on chip technology in the various steps of the integrated circuit life are commented. The main IC's digital faults and failures mechanisms are commented in a introductory way. The principal electrical measurements necessary to estimate the performance of an digital IC is presented. The architecture and the language of the ATE is presented, discussing how this machine is important to test digital integrated circuits. The work ends with two real test programs, written in Pascal commenting the results of the measurements of each test program.

# Sumário

| L | INT | RODUÇÃO AC             | TESTE DE CIRCUITOS INTEGRADOS DIGITAIS | 3   |

|---|-----|------------------------|----------------------------------------|-----|

|   | 1.1 | OBJETIVO D             | A ENGENHARIA DE TESTE                  | 4   |

|   | 1.2 | CUSTO / EFI            | CIÊNCIA                                | 4   |

|   | 1.3 | CONSIDERAÇÕES          |                                        |     |

|   | 1.4 | 1.4 APLICAÇÃO DO TESTE |                                        |     |

|   |     | 1.4.1 <b>Depuraç</b> ã | o do protótipo                         | 6   |

|   |     | 1.4.2 Avaliação        | funcional                              | 6   |

|   |     | 1.4.3 Caracter         | zação                                  | 6   |

|   |     | 1.4.4 Produção         |                                        | 7   |

|   |     | 1.4.5 Ensaios o        | e confiabilidade                       | 7   |

|   |     | 1.4.6 Inspeção         | de recebimento                         | 8   |

|   |     | 1.4.7 Análise d        | e falhas                               | 8   |

|   | 1.5 | FATORES QUI            | INFLUENCIAM NO TESTE                   | 8   |

|   |     | 1.5.1 Propósito        | do teste                               | 9   |

|   |     | 1.5.2 <b>Tipos de</b>  | testes                                 | 9   |

|   |     | 1.5.3 Tecnolog         | a do dispositivo                       | 10  |

|   |     | 1.5.4 Estágio d        | e fabricação do dispositivo            | 10  |

|   |     | 1.5.5 <b>Tipos de</b>  | dispositivos                           | 11  |

|   | 1.6 | EQUIPAMENT             | OS AUTOMÁTICOS DE TESTE - ATE          | 12  |

|   | 1.7 | TESTE DE CII           | RCUITOS DIGITAIS                       | 13  |

|   | 1 2 | REFERÊNCIA             | S RIBLIOGRÁFICAS                       | 1.4 |

| 2 | FA         | LHAS E MECANISMOS DE FALHAS          | 16 |

|---|------------|--------------------------------------|----|

|   | 2.1        | INTRODUÇÃO                           | 17 |

|   | 2.2        | FALHAS TIPO "SINGLE STUCK-AT"        | 17 |

|   | 2.3        | MÚLTIPLAS FALHAS "STUCK-AT"          | 18 |

|   |            | 2.3.1 Múltiplas falhas interativas   | 19 |

|   |            | 2.3.2 Falhas "Bridging"              | 19 |

|   | 2.4        | FALHAS INTERMITENTES                 | 20 |

|   |            | 2.4.1 Vibração                       | 20 |

|   |            | 2.4.2 Estresse térmico               | 21 |

|   | 2.5        | DESCARGA ELETROSTÁTICA - ESD         | 22 |

|   | 2.6        | SOBRE ESTRESSE ELÉTRICO - EOS        | 23 |

|   | 2.7        | CORROSÃO                             | 24 |

|   | 2.8        | FALHAS EM MEMÓRIAS                   | 24 |

|   |            | 2.8.1 Principais falhas nas memórias | 26 |

|   |            | 2.8.2 Descrição das falhas           | 26 |

|   |            | 2.8.3 Padrões de teste               | 27 |

|   | 2.9        | REFERÊNCIAS BIBLIOGRÁFICAS           | 28 |

| 3 | $	ext{TE}$ | ESTES REALIZADOS POR UM ATE          | 29 |

|   | 3.1        | TIPOS DE TESTES                      | 30 |

|   | 3.2        | FUNCIONAL                            | 30 |

|   | 3.3        | PARAMÉTRICO DC                       | 31 |

|   |            | 3.3.1 Testes paramétricos realizados | 32 |

|   |            | 3.3.2 Teste de continuidade          | 32 |

|   |            | 3.3.3 Medição de IIL                 | 34 |

|   |            | 3.3.4 Medição de IIH                 | 34 |

|   |            | 3.3.5 Medição de IOZ                 | 35 |

|   |            | 3.3.6 Medição de VIH E VIL           |    |

|     |        |                                                                                                                                | viii |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------|------|

|     | 3.3.7  | Medição de VOH E VOL                                                                                                           | 40   |

|     | 3.3.8  | Medição de IDD ou ICC                                                                                                          | 41   |

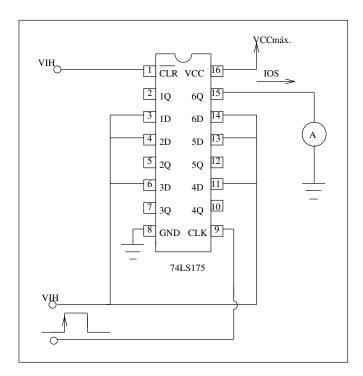

|     | 3.3.9  | Medição de IOS                                                                                                                 | 43   |

|     | 3.3.10 | Medição de IOL                                                                                                                 | 44   |

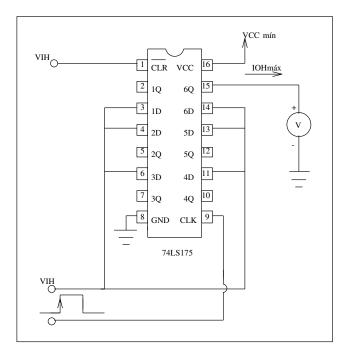

|     | 3.3.11 | Medição de IOH                                                                                                                 | 46   |

| 3.4 | PAR    | AMÉTRICO AC                                                                                                                    | 46   |

|     | 3.4.1  | Evento                                                                                                                         | 47   |

|     | 3.4.2  | Atraso de propagação                                                                                                           | 48   |

|     | 3.4.3  | tPHL                                                                                                                           | 48   |

|     | 3.4.4  | tPLH                                                                                                                           | 49   |

|     | 3.4.5  | $tPD  \dots $            | 49   |

|     | 3.4.6  | tPHZ                                                                                                                           | 49   |

|     | 3.4.7  | $tPLZ \ \dots $          | 50   |

|     | 3.4.8  | tPZH                                                                                                                           | 50   |

|     | 3.4.9  | $tPZL \ \dots $          | 50   |

|     | 3.4.10 | Tempos de transição                                                                                                            | 52   |

|     | 3.4.11 | $\mathbf{tTLH}  \dots $  | 53   |

|     | 3.4.12 | $\mathbf{tTHL} \ \dots $ | 53   |

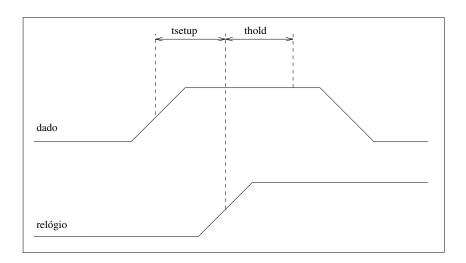

|     | 3.4.13 | Tempo de "setup" e de "hold"                                                                                                   | 53   |

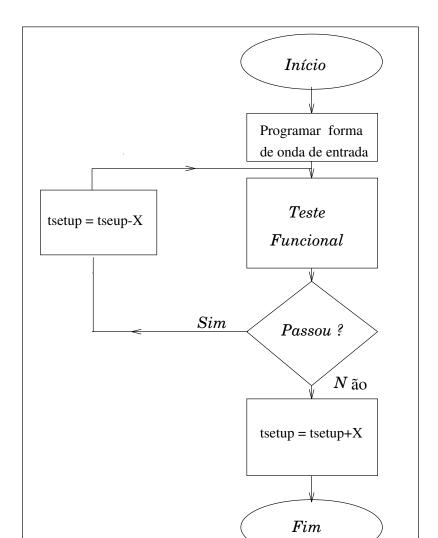

|     | 3.4.14 | Tempo de "setup"                                                                                                               | 54   |

|     | 3.4.15 | Procedimento para medição do tempo de "setup"                                                                                  | 54   |

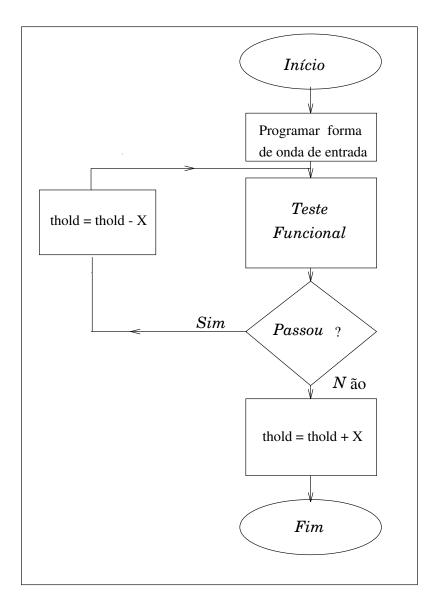

|     | 3.4.16 | Tempo de "hold"                                                                                                                | 55   |

|     | 3.4.17 | Procedimento para medição do tempo de "hold"                                                                                   | 56   |

|     | 3.4.18 | $\mathbf{tW}  \dots $    | 57   |

|     | 3.4.19 | fmax                                                                                                                           | 58   |

| 3.5 | REFE   | ERÊNCIAS BIBLIOGRÁFICAS                                                                                                        | 58   |

60

${\bf 4}\quad {\bf ATE}\ {\bf E}\ {\bf LINGUAGENS}\ {\bf DE}\ {\bf PROGRAMAÇ\~AO}$

| 4.1 | DEFINIÇÃO                                                   | 61 |

|-----|-------------------------------------------------------------|----|

| 4.2 | HISTÓRICO                                                   | 61 |

| 4.3 | APLICAÇÃO DOS ATE'S                                         | 61 |

| 4.4 | CUSTO DO TESTADOR                                           | 62 |

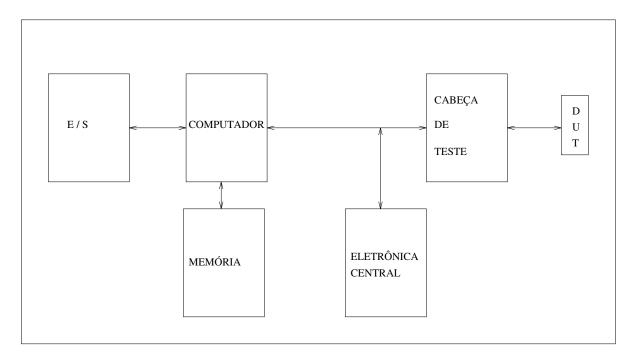

| 4.5 | ARQUITETURA BÁSICA DE UM ATE                                | 62 |

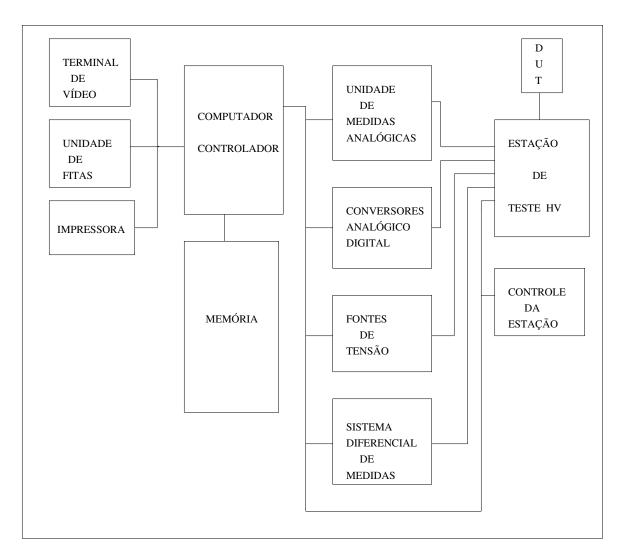

| 4.6 | J325 - SISTEMA AUTOMÁTICO DE TESTES DE CIRCUITOS INTE-      |    |

|     | GRADOS DIGITAIS                                             | 64 |

|     | 4.6.1 Introdução                                            | 64 |

|     | 4.6.2 Terminal de vídeo                                     | 64 |

|     | 4.6.3 Unidade de fitas                                      | 65 |

|     | 4.6.4 Impressora                                            | 65 |

|     | 4.6.5 Computador                                            | 66 |

|     | 4.6.6 Memória                                               | 66 |

|     | 4.6.7 Unidade de medidas analógicas (AMU)                   | 66 |

|     | 4.6.8 Conversores analógicos digitais e digitais analógicos | 68 |

|     | 4.6.9 Fontes de tensão para o dispositivo                   | 68 |

|     | 4.6.10 Sistema de medidas diferenciais                      | 68 |

|     | 4.6.11 Estações de teste                                    | 68 |

|     | 4.6.12 Características da estação HV                        | 69 |

|     | 4.6.13 A estação HV do J325                                 | 69 |

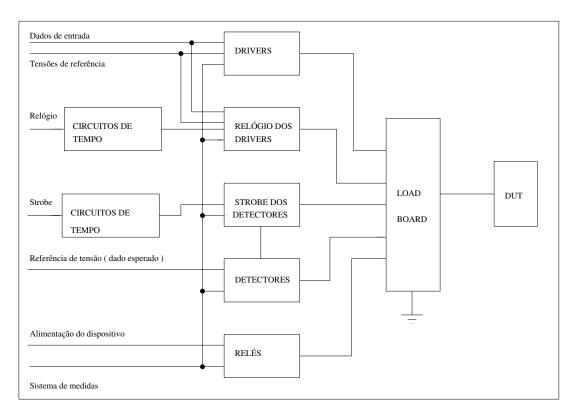

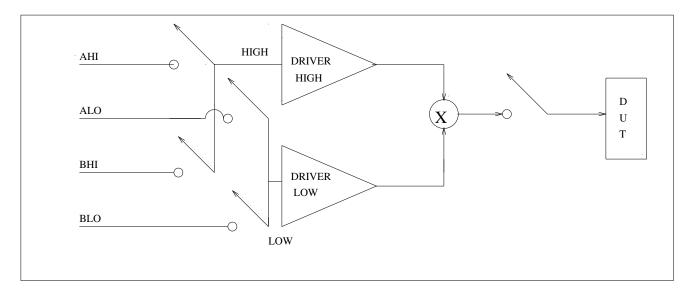

|     | 4.6.14 "Drivers" e detectores                               | 70 |

|     | 4.6.15 "Load board"                                         | 70 |

|     | 4.6.16 DIB - "Device interface board"                       | 72 |

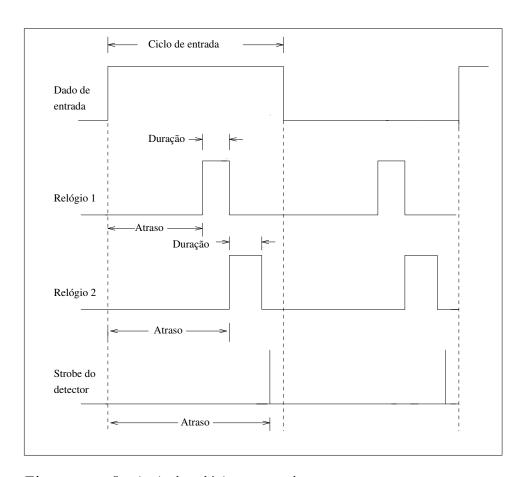

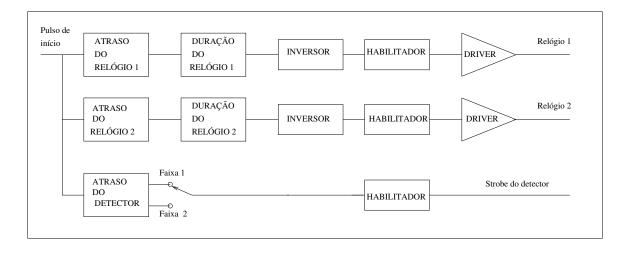

|     | 4.6.17 Circuitos de tempo                                   | 72 |

|     | 4.6.18 Modos de operação                                    | 74 |

|     | 4.6.19 Cargas externas                                      | 75 |

| 4.7 | Linguagem de Programação dos ATE                            | 75 |

|     | 4.7.1 A linguagem de programação Pascal-T                   | 76 |

|   |     | 4.7.2 Estrutura do Programa             | 76  |

|---|-----|-----------------------------------------|-----|

|   |     | 4.7.3 Definições de canais              | 78  |

|   |     | 4.7.4 Teste de continuidade             | 79  |

|   |     | 4.7.5 Níveis de tensão das fontes       | 80  |

|   |     | 4.7.6 Níveis de tensão dos "drivers"    | 80  |

|   |     | 4.7.7 Medidas de tensões e de correntes | 81  |

|   |     | 4.7.8 Programando o teste funcional     | 82  |

|   |     | 4.7.9 Temporização                      | 83  |

|   | 4.8 | MACROS                                  | 84  |

|   | 4.9 | REFERÊNCIAS BIBLIOGRÁFICAS              | 85  |

| 5 | PR  | OGRAMA DE TESTE - APLICAÇÕES            | 86  |

|   | 5.1 | INTRODUÇÃO                              | 87  |

|   | 5.2 | PROGRAMA DE TESTE                       | 87  |

|   | 5.3 | RESULTADOS                              | 98  |

|   |     | 5.3.1 "Datalog" do 74HCT32              | 98  |

|   |     | 5.3.2 "Datalog" do HM62256              | .00 |

|   | 5.4 | CONCLUSÃO                               | 01  |

|   | 5.5 | REFERÊNCIAS BIBLIOGRÁFICAS              | U:  |

#### INTRODUÇÃO

A evolução atual da tecnologia de semicondutores possibilita a produção de dispositivos com mais de 10.000.000 de transistores difundidos em uma única pastilha de silício, com tecnologia de  $0.4\mu m$ . O aumento da complexidade dos circuitos integrados eleva o grau de dificuldade para os projetistas de circuitos integrados, responsáveis pelo desenvolvimento do *chip*, e para os engenheiros de teste, responsáveis por verificar que o circuito fabricado satisfaça plenamente as especificações elétricas e funcionais.

Do ponto de vista de teste, um circuito integrado encapsulado deve ser considerado como uma caixa preta, com um número finito de entradas e saídas. Diferentemente de circuitos eletrônicos montados em placas de circuitos impressos, não se tem acesso a pontos intermediários do circuito integrado, a menos que este ponto seja levado a um terminal (pino) do CI. Daí a preocupação, hoje em dia, dos projetistas de CI com a testabilidade do componente em desenvolvimento.

O teste requer que certas condições de entrada sejam aplicadas ao dispositivo e as saídas sejam comparadas com respostas esperadas, conhecidas, que foram geradas na fase de projeto por um simulador.

Circuitos puramente digitais podem ser funcionalmente verificados pela aplicação de padrões ou seqüências de padrões de "0"s e "1"s (níveis baixos e altos de tensão), com duração de tempo pré-definidas, nas entradas do CI, para produzir o padrão ou a seqüência de padrões desejada na saída do componente.

Circuitos puramente analógicos, entretanto, necessitam do uso de geradores de sinais mais especializados para estimular o componente e equipamentos mais sofisticados para observar e medir a resposta do componente. Isto requer um equipamento de teste mais complexo, contendo vários equipamentos de estímulo e de medida de resposta, possibilitando ao engenheiro de teste, total controle das funções de cada instrumento de medida através de um programa.

Circuitos digitais de grande complexidade, com escala de integração VLSI e circuitos mistos, onde funções analógicas e digitais estão reunidas em um único circuito integrado, o que está se tornado cada vez mais frequente nos dias de hoje, requerem um equipamento deste tipo para serem testados.

Constata-se, hoje em dia, que as ferramentas de projeto de CI e de desenvolvimento de progamas para testes de circuitos integrados estão acompanhando e viabilizando a complexa evolução dos Circuitos Integrados. Tais ferramentas necessitam de pessoal especializado para operação, progamação e manutenção.

Este trabalho descreve o Teste de Circuitos Integrados Digitais, em seus aspectos gerais, utilizando Equipamentos Automáticos de Testes - ATE . No Capítulo I temos uma visão geral do que venha a ser teste de circuitos digitais. O Capítulo II discute as Falhas e os Mecanismos em Circuitos Integrados Digitais. A descrição do ATE e os Tipos de Teste que realiza são apresentados no Capítulo III. A Arquitetura e a Linguagem de Programação dos ATE's está no Capítulo IV e no Capítulo V estão as aplicações práticas.

# Capítulo 1

# INTRODUÇÃO AO TESTE DE CIRCUITOS INTEGRADOS DIGITAIS

#### 1.1 OBJETIVO DA ENGENHARIA DE TESTE

O objetivo de se testar um componente é assegurar que o dispositivo desempenhe corretamente todas as funções para que foi projetado, considerando-se o pior caso das especificações para o ambiente de teste especificado. Equipamentos Automáticos de Teste são controlados por computador, o que requer do engenheiro de teste uma experiência em ciência da computação tanto em programação quanto operação de sistemas. O engenheiro de teste deve saber também, como interfacear corretamente o dispositivo a ser testado ao equipamento de teste.

#### 1.2 CUSTO / EFICIÊNCIA

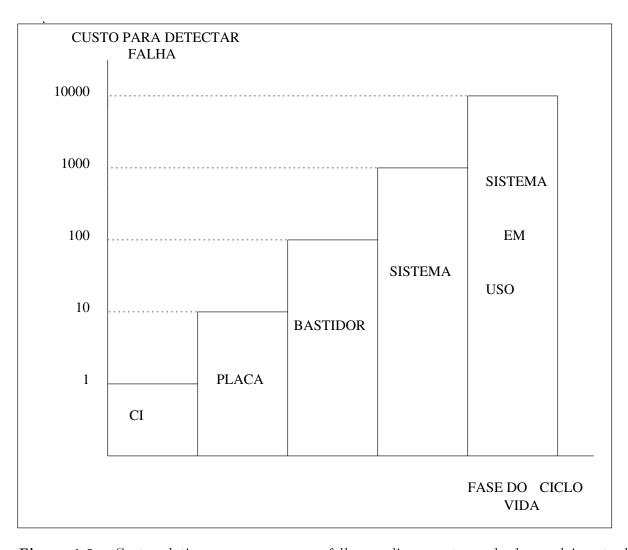

O teste representa cerca de 40% do custo do dispositivo, podendo, em alguns casos, atingir até 60% do custo de desenvolvimento do componente. O custo de um teste deve ser mantido o mais baixo possível. Este custo varia dependendo do tipo de teste a ser realizado e do tipo de componente a ser testado. A figura 1.0 mostra a variação relativa do custo para corrigir uma falha em diversas etapas do desenvolvimento de um sistema.

#### 1.3 CONSIDERAÇÕES

O engenheiro de teste, além de se preocupar com o desenvolvimento de programa de teste ( para equipamentos automáticos de teste - ATE ), deve também se preocupar com a "fiação" que conecta o componente em teste no equipamento de teste, que se não for bem feita, pode acarretar distorções nas medidas realizadas.

É importante ajustar a diferença entre o ambiente de teste e o ambiente final de campo no qual o componente será utilizado.

Figura 1.0 : Custo relativo para reparar uma falha em diversas etapas do desenvolvimento de um sistema.

## 1.4 APLICAÇÃO DO TESTE

O teste de um componente pode ser necessário para vários propósitos diferentes a saber:

- Depuração do Protótipo

- Avaliação Funcional

- Caracterização

- Produção

- Ensaios de confiabilidade

- Inspeção de Recebimento

- Análise de Falhas

#### 1.4.1 Depuração do protótipo

É um teste realizado durante a fase de desenvolvimento do *Chip*. Após o projeto e após exaustivas simulações do funcionamento do circuito, é construído um protótipo do integrado. Algumas das amostras construídas vão para o teste, onde será verificado se o protótipo satisfaz o projeto lógico.

#### 1.4.2 Avaliação funcional

Este teste também é realizado durante a fase de desenvolvimento do Chip. Tem a finalidade de verificar se o projeto lógico cumpre as especificações.

#### 1.4.3 Caracterização

A função da caracterização é determinar se o projeto está correto e levantar as características elétricas do dispositivo. Isto significa realmente medir as características AC e DC ao invés de verificar se o dispositivo atende as especificações-padrões da tecnologia utilizada.

A caracterização é o tipo de teste utilizado para levantar as especificações finais do componente (Manual do Componente). Neste caso, o tempo de teste não é crítico, a meta é obter medidas precisas e exatas.

Requer-se, além de um bom testador, um equipamento térmico especial para aquecer e resfriar o componente na cabeça de teste, para se obter as medidas dos parâmetros em temperaturas extremas.

Durante esta fase é necessário também utilizar ferramentas (softwares ) estatísticas

para verificar e estudar as variações e desvios das medidas realizadas. É nesta fase também que são gerados os limites de passagem e falha (guardbands) que serão utilizados no teste de produção. É a etapa mais cara do teste.

#### 1.4.4 Produção

O objetivo do teste de produção é assegurar que o dispositivo encapsulado esteja dentro das especificações, geradas na fase de caracterização, e que funcione corretamente. Este tipo de teste deve ser rápido para uma melhor relação custo/eficiência, isto é, deve ter uma máxima cobertura em um mínimo tempo. Este é o tipo de teste utilizado nas fábricas de circuitos integrados para teste de seus produtos.

$\label{eq:continuous} \mbox{Um outro tipo de teste de produção \'e o chamado $Wafer Sort$ , que tem a finalidade}$  de selecionar os componentes antes do encapsulamento.

#### 1.4.5 Ensaios de confiabilidade

O objetivo destes ensaios é verificar a conformidade dos componentes após submetidos a condições estressantes para avaliar se são ou não confiáveis. Os ensaios que necessitam de teste elétrico no decorrer de sua execução são: variação rápida de temperatura, seqüência climática, calor úmido prolongado, calor úmido polarizado, vida operacional, armazenagem a alta temperatura e sensibilidade a descarga eletrostática.

O ensaio de vida operacional consiste em assegurar que o dispositivo funcione corretamente durante um determinado número mínimo de anos. O processo de envelhecimento do componente é baseado em estressar o componente em uma temperatura elevada. Devem ser feitas correlações entre a vida útil do dispositivo em temperatura ambiente e em uma temperatura mais elevada.

A idéia deste tipo de ensaio é colocar o dispositivo em uma estufa com temperatura especificada ( maior que a temperatura ambiente), com a polarização adequada, por um período de tempo, e então testá-lo novamente. Com base na temperatura e no tempo em que o componente ficou na estufa, pode-se determinar a expectativa de vida do componente. Este procedimento requer análises estatísticas e probabilísticas com profundidade.

#### 1.4.6 Inspeção de recebimento

Este tipo de teste consiste em verificar se o componente recebido está funcionando de acordo com as especificações do fabricante. É um teste rápido, por amostragem de lote, mas assegura que o lote de peças recebidas está em perfeitas condições de utilização, garantindo maior confiabilidade ao produto final.

#### 1.4.7 Análise de falhas

Como o próprio nome diz, significa analisar, pesquisar a causa de uma determinada falha em um circuito integrado. Para realizar este trabalho, o analista de falhas necessita, além das técnicas e equipamentos de microscopia, de uma capela e de produtos químicos para a abertura do componente e de um teste funcional e paramétrico do componente, a fim de verificar o tipo de falha para orientar o trabalho de busca da causa da falha.

Algumas vezes, o analista de falhas e o engenheiro de teste vão juntos ao equipamento automático de teste para depurar a falha do CI. Neste caso, às vezes, é necessário alterar o programa de teste para caracterizar bem a falha e quantificar precisamente o valor de um parâmetro medido, que porventura tenha ultrapassado o limite da escala programada para o medidor. Geralmente o teste do *chip* é realizado antes que o analista abra o componente para iniciar o trabalho de pesquisa da falha.

#### 1.5 FATORES QUE INFLUENCIAM NO TESTE

$\label{tension} T\'{e}cnicas \ diferenciadas \ de teste s\~{a}o \ aplicadas \ dependendo \ da \ finalidade \ do \ teste. Tais$   $t\'{e}cnicas \ dependem \ :$

- Do propósito do teste

- Do tipo de teste a ser aplicado

- Da tecnologia utilizada no *chip*

- Do estágio de fabricação do dispositivo

- Do tipo de dispositivo

#### 1.5.1 Propósito do teste

A complexidade de um programa de teste, o pessoal envolvido, o custo e o tipo de equipamento necessário para o teste variam dependendo se o teste é para depuração do protótipo, para avaliação funcional, para caracterização do dispositivo, para teste de vida, para produção, para inspeção de recebimento ou para análise de falhas.

O teste funcional é suficiente para a depuração do protótipo e para a avaliação funcional.

Um teste paramétrico realizado durante a fase de caracterização de um *chip* é bem diferente de um teste paramétrico para a produção ou para a inspeção de recebimento, embora a mesma especificação seja verificada em cada um dos casos.

Na caracterização, os parâmetros AC e DC do componente são realmente medidos e seus limites são levantados, inclusive em temperaturas diferentes.

Para o ensaio de vida é necessário um teste paramétrico e um teste funcional, além de estufas para envelhecimento do componente. Na produção e na inspeção de recebimento estes parâmetros são "checados" contra os limites do manual.

#### 1.5.2 Tipos de testes

Há basicamente três tipos de testes elétricos realizados em um componente:

- Funcional

- Paramétrico DC

- Paramétrico AC

O teste funcional verifica se o dispositivo está operando como o esperado. Neste teste a tabela da verdade do componente é verificada. Este tipo de teste será discutido com mais

detalhes no Capítulo III.

O teste paramétrico DC verifica se o dispositivo opera bem em seu ambiente especificado. Este teste mede a corrente de consumo do dispositivo e sua habilidade de operar corretamente com níveis de tensão apropriados. As correntes de fuga também são medidas neste teste.

$O\ teste\ paramétrico\ AC\ est\'a\ relacionado\ com\ tempos,\ com\ atrasos\ de\ propagação, tempos$  de transição, tempos de acessos, etc.

Tanto as medidas paramétricas DC quanto as medidas paramétricas AC estão comentadas no Capítulo III.

#### 1.5.3 Tecnologia do dispositivo

Os parâmetros DC e AC de um componente eletrônico variam bastante, dependendo da tecnologia utilizada. Os dispositivos processados em cada tecnologia possuem características elétricas diferentes. Assim, diferentes especificações devem ser verificadas ou testadas de maneiras diferenciadas. Por exemplo, as exigências de níveis de tensão de entrada e as correntes de fuga para a tecnologia ECL possuem significados diferentes das mesmas exigências de um TTL ou CMOS, com alta impedância de entrada. As tensões de saídas de um CMOS são medidas sem carga, enquanto que as mesmas medidas para um TTL são realizadas com uma corrente de carga.

O resultado de um teste paramétrico AC para dispositivos ECL são dependentes do tempo de subida do sinal de entrada, o que tem pouca influência nos resultados destas medidas para os dispositivos CMOS.

#### 1.5.4 Estágio de fabricação do dispositivo

O modo de intefacear o dispositivo sob teste depende do estágio de fabricação do dispositivo. Isto tem efeito no ambiente elétrico em que o dispositivo que está sendo testado está envolvido.

Quando se realiza um teste, é aconselhável ter o pin electronics do testador mais próximo possível do componente sob teste, a fim de se evitar interferências devido as indutâncias e capacitâncias dos cabos envolvidos. O pin electronics do testador é a eletrônica ou os circuitos

eletrônicos localizados na cabeça de teste do testador, que estimulam o dispositivo e detectam sua resposta. São os canais de *driver* e de comparadores.

Durante o teste de Wafer, isto é, do chip antes de ser encapsulado, a interface do testador com o wafer é difícil de ser realizada, pois envolve fiação coaxial externa, considerando que a cabeça de teste do ATE muitas vezes é grande e difícil de ser movida.

Em alguns casos é possível interfacear o testador com um equipamento micromanipulador. Este equipamento, comandado pelo ATE, coloca as micro agulhas nos pads do circuito integrado para estimulá-lo e medir sua resposta.

O wafer sort é um teste complicado de ser realizado, além de ser caro. É necessário um estudo bem detalhado de sua viabilidade econômica, pois, por outro lado, o encapsulamento do CI também é caro. Então, encapsular somente as pastilhas selecionadas pode ser vantajoso economicamente, dependendo do caso.

No teste de Wafer, o problema de interface do dispositvo com o testador é crítico. O engenheiro de teste deve tomar bastante cuidado com a fiação ( os cabos coaxiais) e fazer os ajustes de software necessários, tanto de timing quanto de níveis para corrigir eventuais distorções ocasionadas pelos cabos.

O problema acima de interfaceamento é menor no teste com o *chip* encapsulado. Neste caso, o soquete que suportará o componente a ser testado é montado em um *Device Interface Board - DIB*, uma placa de *interface* que vai conectada na cabeça de teste bem próxima do *pin electronics*. Mesmo assim, as ligações dos canais do testador com os pinos do dispositivo devem ser realizadas com cabos coaxiais e deve-se tomar os cuidados necessários para se trabalhar com alta freqüência.

#### 1.5.5 Tipos de dispositivos

As diferenças do teste também dependem do tipo de dispositivo que será testado.

As memórias e os dispositivos lógicos utilizam aparatos diferentes para gerar seus padrões funcionais de teste.

Os testadores de *chips* lógicos armazenam a tabela da verdade do dispositivo na memória de padrão e aplicam esses padrões seqüencialmente ao dispositivo.

Os testadores de memória utilizam algoritmos geradores de padrões (ALPG). Vários tipos de instruções criam um padrão de teste completo para o teste da memória.

Os gate arrays são testados no testador de lógica, mas podem ser testados também em testadores de memória, devido ao tamanho pequeno da tabela da verdade que define a sua lógica.

Há possibilidade de se testar memórias em testadores de lógicas; o problema é que o padrão de teste fica grande e o programa de teste fica um pouco lento, inviável para o teste de produção.

#### 1.6 EQUIPAMENTOS AUTOMÁTICOS DE TESTE - ATE

Os Equipamentos Automáticos de Teste, os ATE (Automated Test Equipment), são sistemas programáveis que controlam e monitoram os circuitos integrados em teste para determinar se são ou não operacionais, estimulando as entradas e analisando as saídas do circuito. São equipamentos imprescindíveis e importantíssimos para a verificação do correto funcionamento de circuitos integrados, que cada vez mais estão se tornando mais complexos, contendo mais transistores chaveando em velocidades cada vez maiores e, portanto, mais difícil de serem testados.

Os equipamentos programáveis que possibilitam a automação dos testes dos circuitos integrados estão em constante evolução, acompanhando e auxiliando esta fantástica e rápida evolução dos circuitos integrados.

Os dispositivos desenvolvidos pela indústria de semicondutores de vanguarda são sempre mais evoluídos que os *chips* que vão nos equipamentos automáticos de teste. Embora sendo construídos de componentes de uma geração tecnológica anterior, os ATE possuem a missão de testar os componentes de última geração.

Os ATE contêm um conjunto de equipamentos para estímulo, para medida da resposta do componente, fontes de tensão, fontes de corrente, processadores digitais de sinais, etc. Todos esses equipamentos são totalmente controlados por um computador.

Alguns ATE possuem um computador somente para comandar os equipamentos relacionados com a cabeça de teste, e um outro computador para a *interface* homem/máquina e para

o gerenciamento da rede local.

O engenheiro de teste possui total controle dos equipamentos através de um programa escrito em linguagem de alto nível. Este assunto será comentado com mais detalhes no capítulo IV.

#### 1.7 TESTE DE CIRCUITOS DIGITAIS

O objetivo primário do engenheiro de teste é assegurar que o circuito digital em perfeito funcionamento opere de acordo com sua tabela da verdade. A tabela da verdade (padrão de teste) é armazenada na memória de padrão do testador. Cada linha do padrão, chamada de Vetor de Teste, contém os bits de estímulos e a resposta esperada.

Para estimular o dispositivo, os vetores de teste armazenados na memória de padrão do ATE passam por um circuito chamado formatador, que combina os dados digitais com as bordas de tempo, programadas para gerar a forma de onda digital desejada. Esta forma de onda passa depois por um circuito de *driver* que coloca os níveis de tensão, programados para o nível lógico 1 e para o nível lógico 0.

A forma de onda digital completa é aplicada ao dispositivo sob teste em uma dada freqüência também programada por Software, através de uma interface chamada de Loadboard, ou em alguns testadores Device Interface Board - DIB, que conecta os canais do testador com o soquete que contém o componente a ser testado. O dispositivo responde com uma saída, que passa através do Loadboard e vai para o comparador localizado na cabeça de teste. O dado esperado é comparado com as tensões de referência em um dado instante de tempo. Tanto as tensões de referências quanto o instante de tempo em que a comparação será realizada podem ser alterados no programa de teste.

É possível conectar nos pinos de saída do componente, cargas ou correntes de cargas programáveis, necessárias para as medidas paramétricas ou para a execução de um teste funcional mais rigoroso. Naturalmente, existe um *driver* e um comparador para cada pino do CI, exceto, é claro, para os pinos de alimentação, que são conectados a uma fonte de tensão programável para o pino de VDD e ao terra para o pino de GND.

Os vetores de teste armazenados na memória de padrão do testador são utilizados também para colocar o dispositivo em uma determinada condição ou estado que possibilite a realização de medidas paramétricas AC e DC.

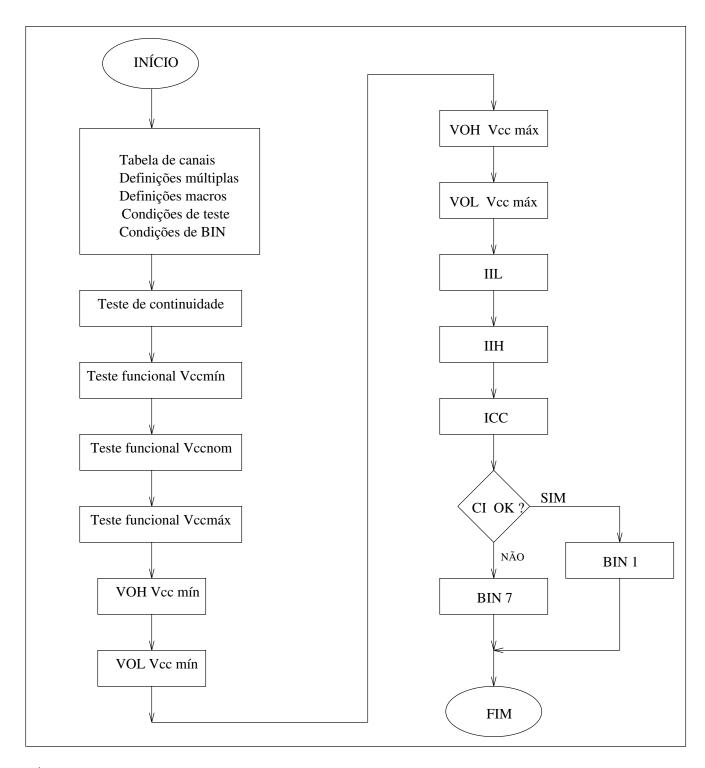

O computador toma a decisão se o componente passa ou não, comparando o que foi medido com o que foi programado. O resultado do teste, chamado datalog, pode ser armazenado em disco ou fita, apresentado na tela do testador ou impresso em papel.

Às vezes não é necessário visualizar ou gravar os valores das medidas realizadas e sim a classificação do componente. Isto é feito pelo Bin. Alguns ATE apresentam o número do Bin na tela; outros, mais antigos, acendem um LED correspondente ao resultado do teste. O engenheiro de teste programa o Bin. Por exemplo, se o componente falhou no teste paramétrico DC o Bin 2 programado aparece na tela do testador, ou o LED do 2 do Binbox acende. Se o componente estiver bom, o Bin 1 aparecerá na tela ou o LED 1 acenderá.

O capítulo III comenta os testes funcional, paramétrico DC e paramétrico AC com mais detalhes.

#### 1.8 REFERÊNCIAS BIBLIOGRÁFICAS

- STEVENS, Anthony K. Introduction to component testing. Addison-Wesley, 1986.

- BENNETTS, R. G. Design of testable logic circuits. London, Addison-Wesley, 1984.

- BRAGA, Flávio. Teste de circuitos integrados. Documentação interna ao CPqD TELEBRÁS,

DME, Seção de Aplicação, 1992.

- FEUGATE JUNIOR, Robert J; MCLNTYRE, Steven M. Introduction to VLSI testing. Englewood Cliffs, Prentice-Hall, 1988.

- NOVO, Marco Antônio Duarte; RIBEIRO, Álvaro José Lopes; PEDRINI, Hélio; Uma metodologia para caracteriazção de CI's no CPqD. IN: Anais do Congresso da Sociedade Brasileira de Microeletrônica 8., Campinas, 1993.

- CORTNER, J. Max. Digital test engineering. "Wiley-Interscience", 1987.

- FANTINI,F; GIOVANETTI, A; GAVIRAGHI; BRAMBILLA, P. Asic qualification and testing: some meaningful examples. Teletra S. P. A. 20059 Vimercate, Italy.

- FRANK, Edward H; SPROUL, Robert F. Testing and debugging custom integrated circuits; Computing Surveys, Vol 13, N. 4, December 1981.

# Capítulo 2

# FALHAS E MECANISMOS DE FALHAS

#### 2.1 INTRODUÇÃO

Se não existisse a possibilidade de falha em um circuito integrado digital não haveria a necessidade de testá-lo. O tipo de uma falha pode influenciar o projeto do teste. Portanto, é apropriado discutir os tipos de falhas mais comuns que ocorrem em um circuito digital, antes de descrever os métodos de teste. Uma falha pode ser descrita como falta da performance esperada.

Para a eletrônica digital, a performance desejada é uma condição (ou seqüência) esperada de saída em resposta a uma condição (seqüência) de entrada. Uma falha é uma anomalia física, ou uma anomalia do projeto original do circuito integrado. Mais precisamente, em eletrônica, uma falha é um defeito como um circuito aberto, um curto-circuito, um circuito intermitente ou o aparecimento de um ponto de terra indesejado no circuito integrado.

Sempre que uma falha é introduzida erroneamente em um circuito integrado durante sua fabricação ou no campo por estresse ambiental, mecânico ou elétrico, cai em uma das seguintes categorias: um fio quebrado no circuito integrado, trilha de metalização rompida, quebra de um terminal ou um conector com um pino contaminado cria um circuito aberto. Espalhamento de solda faltando isolação ou excessos de metal causam curto-circuitos. É comum, na prática da eletrônica digital, categorizar falhas pelos efeitos que elas causam no estado lógico de um circuito ao invés de apontá-las diretamente pelas causas. Esta organização será utilizada neste capítulo, onde também serão discutidas as falhas mais simples e mais comuns .

#### 2.2 FALHAS TIPO "SINGLE STUCK-AT"

Uma falha tipo *single stuck at* faz com que um e somente um nó de um circuito digital permaneça em um determinado nível lógico. A falha tipo *stuck-at-1* (s-a-1) inibe o nó de comutar para 0, enquanto a falha tipo *stuck-at-0* (s-a-0) inibe a comutação para 1.

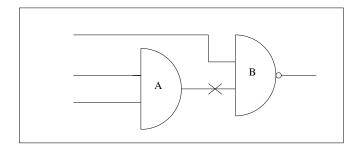

Para a lógica de 3 estados, a falha stuck-at-off (s-a-Z) pode ser definida como a impossibilidade de um sinal lógico de comutar em um barramento. A figura 2.0 mostra o diagrama esquemático do efeito de uma falha S-a-1, causada por um corte na trilha do circuito impresso. Podem ocorrer outros tipos de defeitos no CI ocasionando o mesmo erro na lógica do circuito. Uma trilha

aberta entre a metalização do pad e o fio que conecta o terminal de entrada ou saída do encapsulamento, por exemplo, poderia resultar em um aberto tanto na saída da porta A como na entrada da porta B. Os dois casos causarão uma falha tipo S-a-1 na porta TTL.

Talvez o mais indeterminado defeito na lógica comum é o defeito no habilitador de barramento. A saída de um driver tri-state pode estar amarrada no estado de alta impedância por um curto no caminho do habilitador. Neste caso, a falha é do tipo stuck-at 1 (s-a-1) se o barramento estiver com um resistor de pull-up como carga, ou se o tempo para o circuito comutar para nível lógico 1 não for suficiente, como resultado de correntes de fuga (IIH) de uma porta que está sendo excitada pelo circuito.

O caso de um aberto no caminho do habilitador é mais grave, pois o circuito não irá para o estado de alta impedância, ocasionando uma colisão no barramento.

Figura 2.0: O corte da trilha deste circuito resulta em uma falha tipo stuck at 1 para a porta B.

#### 2.3 MÚLTIPLAS FALHAS "STUCK-AT"

Mesmo sendo aplicado com freqüência, o modelo de falha tipo single stuck at é uma simplificação da realidade. Em circuitos reais, principalmente os que são fabricados pela primeira vez, quase sempre ocorrem múltiplas falhas. Um CI fabricado incorretamente pode gerar falhas em mais de um nó do circuito; uma corrosão ocorrida no chip causará provavelmente mais que um circuito aberto. Se as falhas não são interativas ou interdependentes, a situação de análise se torna direta. Dois circuitos abertos em diferentes bits de um barramento de comunicação podem não interagir. Neste caso, as falhas podem ser consideradas isoladas e tratadas como tal, uma vez que o teste para detectar um tipo não afetará a detecção do outro.

#### 2.3.1 Múltiplas falhas interativas

Este tipo de falha é um caso bem diferente, podendo levar a imprecisões no grau de cobertura do teste. Se o barramento de comunicação descrito acima fosse verificado por um circuito detector de paridade, cuja saída fosse o único ponto de observação, a condição de duas falhas citadas acima poderia não ser detectada pelo teste de paridade.

Considere o caso em que 32 zeros serão aplicados no barramento. Paridade par será indicada, significando que o circuito está funcionando bem. Se duas das linhas do barramento estiverem com falhas tipo S-a-1, a paridade permacerá par, sinalizando erroneamente que o circuito está bom. É óbvio que se as entradas do circuito detector de paridade fossem observadas, as falhas seriam identificadas.

#### 2.3.2 Falhas "Bridging"

Estas falhas podem ser causadas pelo deslocamento do terminal de um componente que toca em outro circuito, formando um caminho de passagem para a corrente elétrica. Com o tempo, temperatura e campos elétricos trabalhando nos metais do circuito integrado, a migração de íons pode criar estranhos estalagmites que crescem e contactam outras regiões de metal e/ou silício no circuito.

Este tipo de falha é também conhecido como Wisker. O efeito no circuito envolvido depende da tecnologia de implementação da lógica. Para TTL, uma porta wired-and é criada. No caso do ECL esta falha cria um circuito wired-Or.

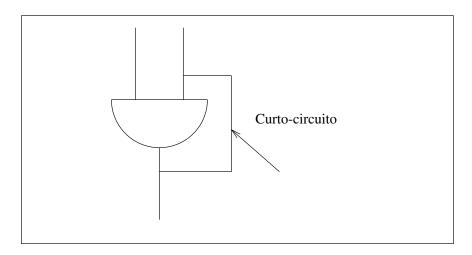

Quando uma falha tipo *bridging* conecta a saída de um circuito com sua entrada, uma malha de realimentação é estabelecida. Um exemplo simples é mostrado na figura 2.1. Esta falha pode converter o circuito combinacional em um *latch* sequencial, pela malha de realimentação.

Figura 2.1: Falha tipo bridge em uma porta and.

#### 2.4 FALHAS INTERMITENTES

Qualquer circuito eletrônico, independente de sua velocidade, leva um certo tempo para desempenhar sua função. O processo de teste também requer um tempo para sua execução. Quando uma falha aparece e desaparece durante o teste, é dita falha intermitente.

Geralmente uma falha que aparece e desaparece, sem que nenhuma ação corretiva seja tomada, é uma falha intermitente. Mas, do ponto de vista de teste, a intermitência só deverá ocorrer durante a execução do programa de teste; caso contrário, não seria possível detectá-la.

Os mecanismos que causam falhas intermitentes são de natureza ambiental. É difícil de identificar uma falha intermitente apenas analisando a lógica do circuito integrado. É razoável, nestas circunstâncias, considerar a implementação física do circuito. Pode parecer estranho que um curto-circuito no transistor de saída, formando um S-at-0, possa desaparecer sozinho. Se este curto-circuito for resultado de partículas de metal livres, dentro do encapsulamento do CI, uma vibração pode temporariamente remover a falha.

#### 2.4.1 Vibração

A vibração é realmente a principal causa de falhas intermitentes. Os condutores vibram e se tocam, placas se flexionam e se quebram, conexões soldadas fatigam e se soltam. Os

testes para verificar o desempenho de componentes eletrônicos sob condições de alta vibração podem ser realizados utilizando-se vibradores. Equipamentos sofisticados, com possibilidade de gerar padrões de vibração na freqüência de áudio ou próximo da faixa de freqüencia supersônica, são disponíveis no mercado.

A dificuldade de se testar ou identificar falhas intermitentes está na coincidência da ocorrência da falha durante a execução do programa de teste. Modernos equipamentos automáticos de teste (ATE) podem facilmente ser configurados para repetir uma seqüência de teste *ad infinitum*, o que, sem dúvida, auxilia a detecção de falhas intermitentes. A limitação está no custo, já que o tempo de teste é caro.

#### 2.4.2 Estresse térmico

O estresse térmico também causa falhas intermitentes, mas o período de tempo da intermitência é muito maior. A maioria dos problemas térmicos são causados pela diferença dos coeficientes de expansão térmica dos materiais utilizados para manufaturar dispositivos eletrônicos.

Realmente, com o aumento da temperatura, cada material cria um estresse no outro, resultando em uma expansão ou em uma contração. A tensão mecânica pode criar fendas e outros efeitos que resultam em falhas elétricas. Se a temperatura do circuito diminuir, a fenda pode se fechar, corrigindo temporariamente a falha. Neste caso, uma única passagem pela seqüência de teste tem boa probabilidade de detectar a falha se o teste for realizado na temperatura de ocorrência da falha, com auxílio de equipamentos térmicos especiais.

Como extremo distante das falhas intermitentes, estão as interferências eletromagnéticas, os picos (glitches) de alimentação, radiações cósmicas, etc, que podem ocasionar falhas espúrias de curta duração (nanosegundos) no circuito integrado. Estas falhas são praticamente impossíveis de se isolar para detecção. Felizmente, estas falhas não ocorrem com freqüência. Nestes casos, o esforço maior está em proteger o circuito destes tipos de falha.

#### 2.5 DESCARGA ELETROSTÁTICA - ESD

Sempre que dois materiais entram em contacto , com um certo movimento entre eles e então são separados rapidamente, uma carga de igual intensidade e polaridade oposta é desenvolvida nas superfícies.

Se um dos materiais é um condutor, ele mantém a carga até que seja aterrado, e esta carga é considerada uma carga móvel. Se o material for um isolante, a carga é imóvel e ela permanece no material até ser neutralizada de alguma maneira .

A ESD (descarga eletrostática) é uma das causas importantes das falhas nos vários estágios de um dispositivo semicondutor: na produção, na montagem, no teste, na instalação e no campo. Daí a importância do correto manuseio dos componentes eletrônicos. A utilização de pulseiras, calcanheiras e mantas antiestáticas é muito importante quando se está manuseando componentes semicondutores, especialmente em se tratando de dispositivos fabricados com tecnologia CMOS. A utilização de embalagem apropriada para o transporte e armazenagem de circutos integrados, como canaletas e sacos antiestáticos, podem evitar falhas causadas por ESD.

Existem três fontes principais de carga que podem levar a eventos de descarga eletrostática, podendo danificar ou alterar significativamente as características do dispositivo semicondutor:

- HBM (Human body model ) Modelo do corpo humano.

Uma pessoa carregada toca um dispositivo e descarrega a sua carga armazenada para ou através do terra do dispositvo.

- CDM (Charged Device Model) Modelo do dispositivo carregado.

O próprio dispositivo atuando como uma placa de um capacitor pode armazenar cargas. No contacto com um terra efetivo, o pulso de descarga pode danificar o dispositivo.

- FIM (Field induced model ) Modelo de campo induzido.

Um campo eletrostático está sempre associado com objetos carregados. Sob circunstâncias particulares, um dispositivo inserido neste campo pode ter um potencial induzido através de um

óxido, que ocasiona um breakdown.

Os danos provocados por ESD podem tanto provocar a falha completa do dispositivo por desvios paramétricos, curtos ou abertos, como levar ao enfraquecimento do dispositivo, pelo aquecimento, derretimento, por danos nos óxidos, nas junções ou em componentes do disposivo. Os tipos de falhas provocadas por ESD podem ser classificados como :

- falhas de corrente ou de potência, comumente reconhecidas por pontos quentes ou zonas de derretimento;

- falhas de potencial que estão caracterizadas onde tenha ocorrido o rompimento do dielétrico ou a quebra da superfície ou um arco voltáico.

Geralmente o teste de curto e aberto já detecta a falha, quando um CI sofreu uma descarga eletrostática de alta intensidade. Se o equipameto de teste estiver operando no modo continue on fail, os demais testes também apresentarão falhas, principalmente o teste de leakage e o teste funcional.

#### 2.6 SOBRE ESTRESSE ELÉTRICO - EOS

A causa fundamental deste tipo de falha é o sobreaquecimento do material por onde uma corrente excessiva está circulando, provocando uma situação de corrida térmica. Este processo pode levar ao derretimento do silício no ponto de maior temperatura, destruindo sua estrutura cristalina e ocasionando um curto na junção.

Pode ser observado que quando a resistência de junção cai dramaticamente como resultado do derretimento do silício, pode ser esperado um acréscimo na dissipação de potência das interconexões do metal. Se o transiente elétrico que originou estresse continuar, o metal pode derreter. Se o transiente for uma alta tensão, um arco voltáico pode ocorrer, ocasionando danos severos ao dispositivo.

Não é fácil para o analista de falhas definir se a causa da falha foi por ESD ou por EOS, devido a semelhança nos danos causados no dispositivos pelos dois mecanismos.

#### 2.7 CORROSÃO

A corrosão de estruturas metálicas de filme fino nos componentes de estado sólido, como nos circuitos integrados, constituem a principal causa deste tipo de falha. Estas estruturas metálicas, usualmente constituídas de alumínio ou de ouro, podem abranger contactos elétricos do semicondutor, linhas de interconexão e pads . Com exceção dos pads, estas estruturas são quase sempre cobertas por uma camada de material vítreo inorgânico e/ou polímero orgânico (passivação) que protege o dispositivo quimicamente e mecanicamente. Estes filmes de passivação, quando não apresentam defeitos, previnem com muita eficiência os dispositivos que estão sob esta camada. Entretanto, defeitos estruturais na camada de passivação ou a presença de áreas de metal livres desta camada, como nos pads , tornam o metal vulnerável ao ataque da corrosão, pelos agentes químicos do ambiente, do encapsulamento plástico, ou da presença de atmosfera nos encapsulamentos defeituosos.

A corrosão do metal de alumínio nos semicondutores é freqüentemente acelerada na presença de contaminantes como umidade, íons clorídricos e íons de sódio. O principal efeito da corrosão é um aumento da resistência ôhmica, dificultando a passagem da corrente elétrica. Em muitos casos a corrosão leva a um aberto da ligação, acarretando em falha no dispostivo.

#### 2.8 FALHAS EM MEMÓRIAS

Provavelmente um dos mais complexos grupos de falhas consiste das falhas de memórias. A extrema miniaturização para um constante aumento da capacidade de armazenamento dos *chips* de memória, torna-os sujeito a vários efeitos de interdependência, acarretando o que é comumente chamado de "falhas de vizinhança" (*neighborhood faults*).

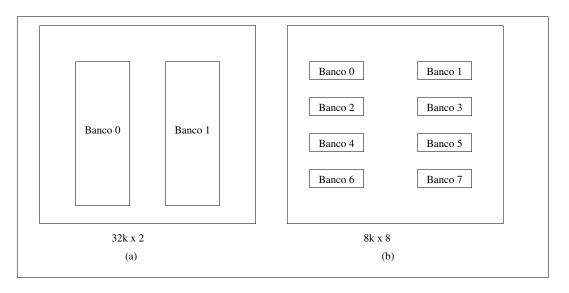

A tendência para uma particular falha depende da disposição física dos elementos internos de armazenamento e dos caminhos de acesso a estes elementos A figura 2.2 mostra esta diferença. Além das variações térmicas e das flutuações da alimentação, o tempo é um fator a mais nas memórias dinâmicas.

Como exemplo, uma sequência típica de teste de uma memória RAM dinâmica será explorada. Colocar 1M, 4M, 16M células em um único die requer um projeto de célula que

deixe um espaço mínimo entre todos os elementos. Com este espaçamento tão reduzido, efeitos como migração de cargas e efeitos de campo se tornam críticos para a operação . O mecanismo de armazenamento é um capacitor.

Infelizmente, a implementação interna do *chip* de memória não é apresentada no datasheet do fabricante. Deste modo, um teste pode ter grau de cobertura diferente, para um mesmo componente, de fabricante diferente, com disposição diferente das células internas de memória. Testes exaustivos que verificam a interferência entre dois bits quaisquer da memória eliminam a dependência do layout do circuito, mas o tempo de teste aumenta, aumentando o custo.

Seqüências de padrões de teste devem ser cuidadosamente elaboradas para verificar as fallhas fundamentais em primeiro lugar. Verificar curtos ou abertos nas linhas de endereçamento, escrevendo dados em cada linha de endereçamento e então verificando os dados escritos por uma seqüência de leituras é um teste popular para memórias com organização interna tipo  $8 \text{K} \times 8$ ,  $16 \text{K} \times 8$ ,  $32 \text{K} \times 8$ , etc.

Para memórias verticais, como as de 1M x 1, 4M x1, etc, uma técnica diferente deve ser aplicada. Uma das seqüências de testes bastante utilizadas é o padrão *chekerboard*, para memórias com mais de uma linha de dados. Este teste coloca cada linha de dado em "0" e todas as linhas adjacentes em "1", e vice-versa. Este padrão detecta curtos, abertos e falhas tipo *bridging* entre as linhas de dados.

O teste de memória deve verificar a operação de cada célula e a interdependência entre as células. A essência deste procedimento é selecionar cuidadosamente cada padrão de teste para cobrir um grupo de falhas que pode ocorrer na memória sob teste.

Existem equipamentos automáticos de teste especialmente projetados para testar memórias, com facilidades para a geração dos diversos tipos de padrões de teste.

Figura 2.2: Estruturas internas alternativas para uma RAM de 64k.

#### 2.8.1 Principais falhas nas memórias

As falhas mais comuns que devem ser detectadas na memórias são:

- Curtos e abertos nas células

- Curtos e abertos nos endereços

- Distúrbios envolvendo a célula

- Cobertura de escrita

- Tempo de acesso

#### 2.8.2 Descrição das falhas

- Célula em curto Célula curtocircuitada para zero ou para um (VCC ou GND).

- Célula aberta Célula não muda de estado quando for realizada uma escrita.

- Célula adjacente em curto Dependendo da natureza do curto, escrever em uma determinada célula, faz com que também seja escrito o mesmo valor (ou seu complementar) na célula adjacente.

- Endereços em curto ou em aberto Algumas células possuem mais que um endereço e alguns endereços acessam mais que uma célula. Este tipo de defeito não é fácil de ser detectado, uma vez que o engenheiro de teste não vê realmente a célula, mas sim apenas a resposta de saída a um dado endereço, e não sabe fisicamente qual célula foi realmente lida.

- Distúrbios nas células Todas as células devem manter seus estados após uma escrita e durante uma leitura. Algumas vezes, ler ou escrever em uma célula pode ocasionar uma mudança de estado na célula vizinha.

- Cobertura de escrita É o intervalo de tempo requerido antes que a próxima célula possa ser lida, após uma escrita.

- Tempo de acesso Possui vários significados, mas é geralmente o tempo entre a habilitação de leitura, *chip select* ou variação do endereço e o aparecimento do dado na saída. O tempo de acesso pode depender da seqüência na qual as células da memória são acessadas.

#### 2.8.3 Padrões de teste

Padrões de teste são seqüências de padrões de níveis lógicos altos e baixos aplicados à memória para testá-la. A capacidade de um determinado padrão de teste detectar uma falha depende, principalmente, do projeto, geometria e *layout* das células da memória. Os padrões para teste de memória mais comuns são :

- Padrão de teste de "Um e Zero"

- Padrão de teste chekerboard

- Padrão de teste Marchante

- Padrão de teste Caminhante

- Padrão de teste Galopante de cobertura de escrita.

# 2.9 REFERÊNCIAS BIBLIOGRÁFICAS

- HUNGER, B. A. Electrostatic Discharge. IRPS 1981, pp. 193-199.

- CORTNER, J. Max. Digital test engineering. "Wiley-Interscience", 1987.

- STEVENS, Anthony K. Introduction to component testing

- CORSI, A; MORANDI, C; A review of ram testing methodologies; Microelectronics Journal, Vol 14, N. 2, 1983.

- SMIDTTH, J. S. Electrical Overstress Failure Analysis in Microcircuits IRPS 1978, pp 41-46.

- SCHNABLE, G. L., Comizzoli, R. B., Kern, W., White, L. K. A Survey of Corrosion Failure

Mechanisms in Microeletronic Devices. RCA Review, vol 40, December 1979.

# Capítulo 3

# TESTES REALIZADOS POR UM ATE

#### 3.1 TIPOS DE TESTES

Há três tipos de testes elétricos realizados em um componente digital:

- Funcional

- Paramétrico DC

- Paramétrico AC

#### 3.2 FUNCIONAL

Consiste em verificar se o componente está funcionando corretamente, ou seja, verificar se o componente está desempenhando corretamente a função, ou as funções para as quais foi projetado. Neste teste, geralmente são aplicados, na entrada do CI, padrões ou seqüência de padrões de "0" e "1" com amplitude e duração pré-definidas, e a saída é comparada com o padrão ou a seqüência de padrões esperados em um dado instante de tempo. Basicamente, em circuitos digitais mais simples, a verificação da tabela da verdade é suficiente para o teste funcional.

O teste funcional é a parte mais complexa de um programa de teste. Sua complexidade é diretamente proporcional à complexidade do CI. Geralmente o padrão de teste para CI's LSI, VLSI são gerados juntamente com o projeto do *chip*, com o auxílio de simulador. Tais padrões de teste são extremamente complexos e grandes.

Normalmente o nível de tensão aplicado à entrada do CI para "rodar" o teste funcional é VIH mínimo para nível lógico "1" e VIL máximo para nível lógico "0", para a tensão de alimentação nominal. A saída é comparada com os valores de VOH mínimo e VOL máximo, para uma corrente de carga de IOHmáx. e IOLmáx. Estes valores de corrente de carga, de tensão de entrada e de tensão de saída são especificados no manual do componente ou da tecnologia. Neste teste está embutido parte do teste paramétrico DC.

O tempo de duração do nível lógico "1" e do nível lógico "0" aplicado na entrada do *chip* e o tempo exato em que a saída deve ser comparada com os valores de referência é totalmente controlado por *software* nos equipamentos de testes modernos; por isso, muitas vezes, o teste funcional

contém também parte do teste paramétrico AC.

No caso de programas de teste para qualificação de componentes, realiza-se o teste funcional três vezes, com tensão de alimentação nominal, máxima e mínima.

## 3.3 PARAMÉTRICO DC

Neste tipo de teste os parâmetros DC do componente são medidos de duas maneiras, a saber:

- Forçando-se uma corrente programada no dispositivo e medindo-se a tensão.(Este tipo de procedimento é feito para as medições de tensão como no caso de VOH e VOL).

- Forçando-se uma tensão programada ao dispositivo e medindo a corrente. (Este tipo de procedimento é feito para as medições de corrente como no caso de IIL e IIH).

Os principais parâmetros de tensão e corrente máxima e mínima, especificados para a operação funcional do dispositivo são:

- IIL Corrente de fuga de entrada para nível baixo máximo aplicado.

- IIH Corrente de fuga de entrada para nível alto máximo aplicado.

- IOZH Corrente de fuga de uma saída em alta impedância para VOL máximo aplicado.

- IOZL Corrente de fuga de uma saída em alta impedância para VOH mínimo aplicado.

- VIL Tensão máxima de entrada nível baixo (limite para o nível lógico "0").

- VIH Tensão mínima de entrada nível alto (limite para o nível lógico "1").

- VOL Tensão máxima de saída nível baixo (limite do nível lógico "0")

- VOH Tensão mínima de saída nível alto (limite do nível lógico "1").

- IOS Corrente de curto-circuito na saída.

- IDDdin Corrente de consumo dinâmico máxima.

- IDDest Corrente de consumo estático máxima.

- IOL Corrente de saída mínima para determinada tensão de saída nível baixo (VOL).

- IOH Corrente de saída mínima para determinada tensão de saída nível alto (VOH).

#### 3.3.1 Testes paramétricos realizados

- Continuidade (curto e aberto)

- Fuga IIH,IIL,IOZ

- Limiares (threshold) VIL, VIH

- Tensões de saídas VOL p/IOL máx. e VOH p/IOH máx.

- Consumo de potência (ICC,IDD)

- Corrente de curto-circuito (IOS)

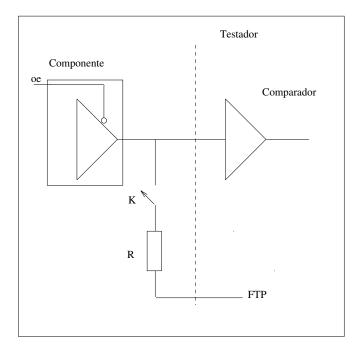

#### 3.3.2 Teste de continuidade

A finalidade do teste de continuidade é assegurar que a interface do testador está em contacto com o dispositivo sob teste. No teste de continuidade é verificado também se há curto-circuito ou circuito aberto nos terminais do CI. Isto é feito aplicando-se uma corrente conhecida  $(+ou-100\mu A)$  no pino e medindo-se a tensão resultante. Se a tensão do pino estiver próxima de 0V, o diodo de proteção do pino está defeituoso, causando um curto-circuito. Se a tensão do pino atingir um certo valor crítico, isto indica que existe um circuito aberto nos circuitos do pino.

Para um dado pino passar no teste de continuidade, a tensão no pino deve estar entre a tensão de aberto e de curto-circuito. Os limites de tensão que dividem esta região dependem do dispositivo que está sendo testado. Entretanto, como regra geral para falhas de curto-circuito, os limites de tensão estão na faixa de + ou - 0.5V e para falhas de aberto de + ou - 4.0V .Usualmente este é o primeiro a teste a ser realizado. A ordem dos testes em um programa comum é :

• Teste de Continuidade

- Teste Funcional

- Teste Paramétrico DC

- Teste Paramétrico AC

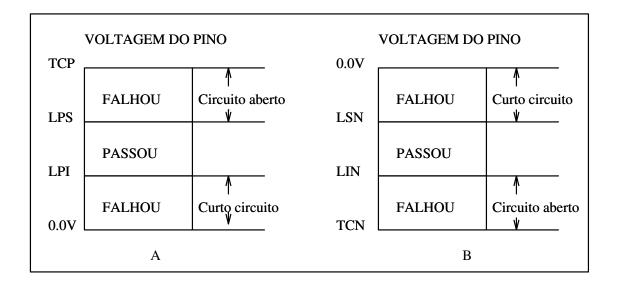

A figura 3.1 mostra os limites para o teste de continuidade.

Figura 3.1: Regiões de aceitação/rejeição para o teste de continuidade.

A : Regiões de aceitação/rejeição para correntes de teste positivas

B : Regiões de aceitação/rejeição para correntes de teste negativas

LSN: Limite superior negativo

LPS: Limite positivo superior

LIN: Limite inferior negativo

LPI: Limite positivo inferior

TCN : Tensão de carga negativa

TCP : Tensão de carga positiva

#### 3.3.3 Medição de IIL

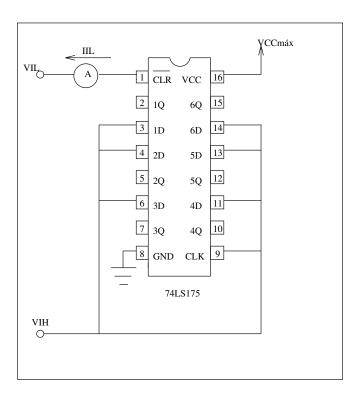

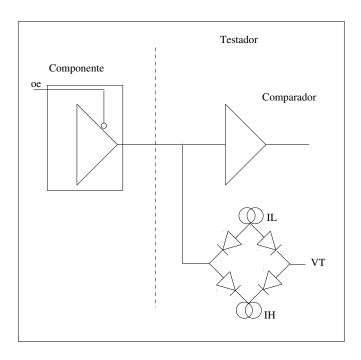

A medição de IIL é realizada forçando-se VIL na entrada desejada e medindo-se a corrente desta entrada com as demais entradas em nível lógico"1", com o *chip* alimentado com VCC máximo e com as saídas em aberto. Quando se utiliza equipamentos automáticos de teste este processo é automaticamente repetido para cada entrada do *chip* que foi programada para ser medida. A figura 3.2 a seguir, ilustra o procedimento para a medição de IIL.

Figura 3.2 : Medição de IIL.

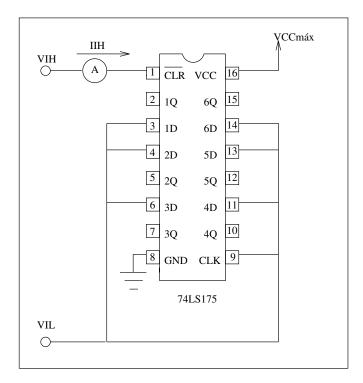

#### 3.3.4 Medição de IIH

Semelhante à medição de IIL, a medição de IIH é realizada forçando-se VIH na entrada desejada e medindo-se a corrente desta entrada com as demais entradas em nível lógico baixo, para o *chip* alimentado com VCC ou VDD máximo, sem carga na saída. Quando se utiliza equipamento automático de teste, este processo é repetido para cada entrada que foi programada para a medição de IIH, ou seja, o micro ou nano amperímetro é colocado em série com a entrada a ser

medida, com um nível de tensão em uma das extremidades de VIH e as demais entradas com nível lógico baixo. O programa vai comutando o micro amperímetro nas entradas onde se deseja medir a corrente e coloca VIH nas demais entradas. A figura 3.3 ilustra o procedimento para a medição de IIH.

Figura 3.3 : Medição de IIH.

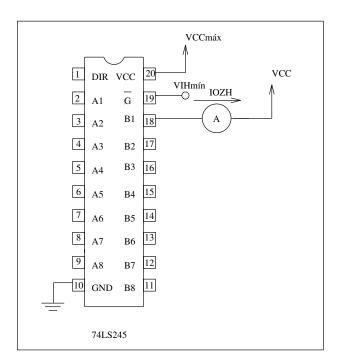

#### 3.3.5 Medição de IOZ

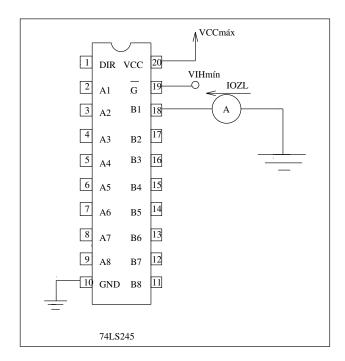

Idealmente, as saídas *Tri-State* são consideradas como circuitos abertos. Na realidade, aparecem como uma alta impedância. A quantidade de corrente que é consumida ou fornecida por cada uma das saídas *Tri-State* é chamada de fuga. Para se medir esta corrente o CI é levado, por um padrão de teste, à condição de *Tri-State*. A corrente de fuga é medida aplicando-se VGND ou VCC e medindo-se a corrente IOZ. São realizadas duas medições desta corrente; IOZH onde é aplicado na saída VCC e IOZL onde é aplicado na saída VGND. Ambas medições são para VCC máximo de alimentação de um *chip* TTL.

Figura 3.4 : Medição de IOZH.

Figura 3.5 : Medição de IOZL.

Tais medições variam um pouco de acordo com a tecnologia do componente. É importante consultar o manual do componente para realizar as medições, colocando-se as mesmas condições de medições especificadas para um dado teste. As figuras 3.4 e 3.5 ilustram as medições de IOZL e IOZH para o CI 74LS245

#### 3.3.6 Medição de VIH E VIL

Estas duas medições determinam o valor real de VIH e VIL que o dispositivo irá operar e são realizadas principalmente na fase de caracterização de um *chip* .São medições lentas feitas por aproximação sucessiva.

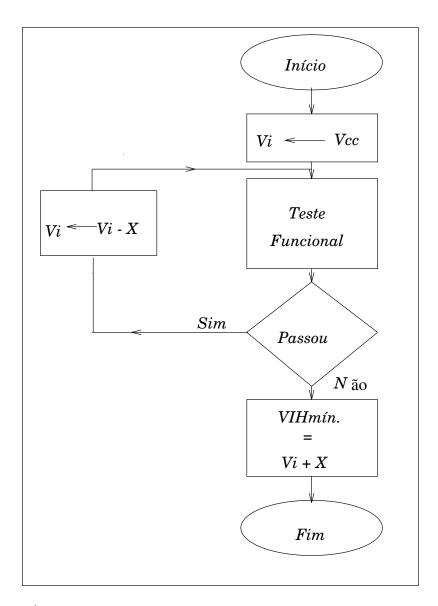

Em uma avaliação funcional de um CI por exemplo, o valor de VIHmín. e de VILmáx., especificado no manual do fabricante do componente, é aplicado às entradas do CI para rodar o padrão funcional. VIL é a tensão máxima que a entrada do dispositivo irá comutar para o estado baixo quando estiver transicionando do estado alto. VIH é mínima tensão na qual a entrada do dispositivo irá comutar para o estado alto quando estiver transicionando do estado baixo. A medição de VIH pode ser feita da maneira indicada no fluxograma da figura 3.6.

Do fluxograma podemos ver que aplica-se VCC na entrada do CI e roda-se um teste funcional com este nível de tensão na entrada do *chip*. Se o componente passar no teste funcional, o valor da tensão de entrada VI é diminuido do valor X e o componente é submetido ao teste funcional novamente. Este processo é repetido até que o componente falhe no teste funcional. Neste ponto o valor de VIHmín. será o valor de VI somado ao valor de X, ou seja, o valor de VI anterior à falha

No valor escolhido para X está a exatidão da medição. Quanto menor for X, mais exata será a medição, mas também será mais demorada. Como na fase de caracterização de um componente o tempo de medição não é crítico, deve-se escolher um valor para X bem pequeno, da ordem de milivolts.

Para se obter resultados mais rápidos não é necessário iniciar a aproximação com o valor VCC aplicado à entrada e sim um valor próximo da tensão de limiar de VIHmín.

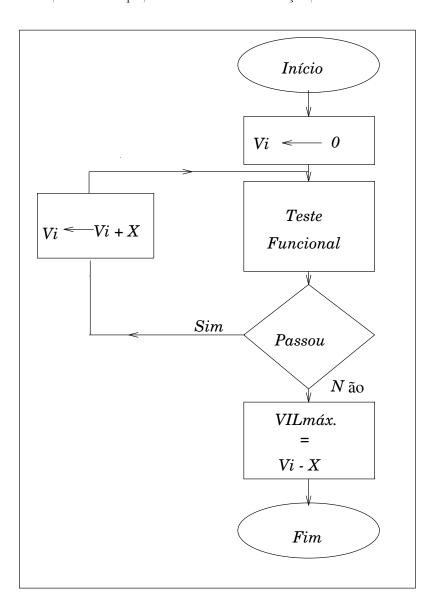

Para a medição de VILmáx., o procedimento é semelhante ao de VIHmín.. O fluxograma da figura 3.7 ilustra este procedimento.

Inicia-se a medição colocando-se zero *volts* em VI (tensão de entrada do componente) e realizando o teste funcional. Se o componente passar, o valor de VI é acrescido de X e o componente é submetido ao teste funcional novamente. Este processo é repetido até que o componente falhe no teste funcional. Assim, o valor de VILmáx. será o valor de VI menos o valor de X, ou seja, o valor de VI anterior à falha.

Figura 3.6 : Fluxograma para a medição de VIH.

Igualmente à medição de VIH, a exatidão da medição está ligada ao valor de X. Quanto menor for este valor, maior será a exatidão da medição. A mesma consideração anteriormente citada para o tempo de medição vale aqui também, ou seja, a estimativa para realizar esta medição é lenta, mas o tempo, na fase de caracterização, não é crítico.

Figura 3.7 : Fluxograma para a medição de VIL.

#### 3.3.7 Medição de VOH E VOL

Nas medições de tensão uma corrente é forçada ao componente, e a tensão é medida. No caso de VOH, por exemplo, IOHmáx. é forçado no componente e o nível da tensão no pino de saída do CI é medido e comparado com o valor limite do manual.

Para se medir VOL, é forçado ao componente o valor de IOLmáx, mede-se a tensão de saída e compara-se o resultado com a referência do manual.

É importante salientar que, para medir VOH, deve-se ter a condição de saída em nível lógico "1". Isto é conseguido geralmente executando-se um padrão funcional que coloque as saídas do componente em nível lógico "1". O mesmo ocorrendo para VOL, deve-se rodar um padrão de teste funcional que coloque as saídas do componente em nível lógico "0". Somente depois deste passo é que a corrente é forçada e a tensão é medida.

Figura 3.8 : Medição da tensão VOL.

Nos equipamentos automáticos de teste o voltímetro e as correntes de cargas, IOHmáx. ou IOLmáx. são comutadas automaticamente para cada saída programada para ser medida. Para ambas medições, o *chip* é alimentado com VCC mínimo. As figuras 3.8 e 3.9 mostram as

medições de VOH e VOL.

Figura 3.9 : Medição da tensão VOH.

#### 3.3.8 Medição de IDD ou ICC

A quantidade de corrente que um componente consome pode variar, dependendo da freqüência do sinal que é aplicado nas entradas do *chip*, principalmente se a tecnologia do dispositivo for CMOS.

O consumo estático de um componente (ICC) é medido com o *chip* alimentado com VCC máximo, com as entradas em um determinado nível fixo de tensão e com as saídas em aberto.

Nos manuais TTL são apresentadas duas correntes de consumo chamadas de ICCH e ICCL. O ICCH é medido em série com o pino de alimentação, com o *chip* alimentado com VCC máximo, com as entradas em níveis de tensão de acordo com a tabela 3.1. A medição de ICCL é semelhante a de ICCH, mas com a condição de entrada diferente (veja a diferença na tabela 3.1).

Para CI's CMOS não existe no manual ICCH e ICCL e sim ICC ou IDD. Esta medição é realizada com as entradas do componente em VCC ou em 0V para o CI alimentado com a

tensão máxima.

| FUNÇÃO | CONDIÇÕES DE ENTRADA P/ ICCH       | CONDIÇÕES DE ENTRADA P/ ICCL      |

|--------|------------------------------------|-----------------------------------|

| NAND   | Todas as entradas em GND           | Todas as entradas com $4.5V$      |

| AND    | Todas as entradas em 4,5V          | Todas as entradas em GND          |

| NOR    | Todas as entradas em GND           | Uma entrada em 4,5V,demais em GND |

| OR     | Uma entrada em 4,5V, demais em GND | Todas as entradas em GND          |

Tabela 3.1 :Condições de entrada para a medição de ICCH e ICCL.

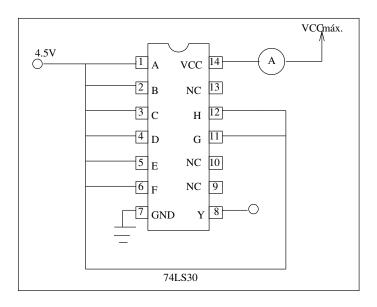

Para circuitos integrados tipo flip flop, as condições de entrada para a medição de ICC são outras, diferentes destas especificadas na tabela 3.1 e estão apresentadas no manual do componente. A figura 3.10 ilustra a medição de ICCH para o CI 74LS30, uma porta E de oito entradas.

Figura 3.10: Medição da corrente de consumo estático

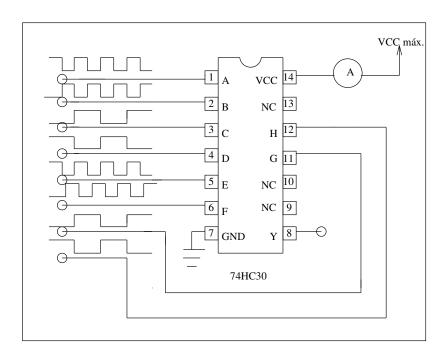

A medição de corrente de consumo dinâmica de um componente é realizada com um padrão de teste, ou seja, uma seqüência de "0" e "1" aplicados às entradas do componente; isto é, o nível lógico de cada entrada fica alternando em uma determinada freqüência . As saídas são mantidas em aberto e o *chip* é alimentado com VCC ou VDD máximo. A figura 3.11 ilustra este procedimento.

Figura 3.11: Medição da corrente de consumo dinâmico.

#### 3.3.9 Medição de IOS

Para realizar esta medição coloca-se uma ponta do microamperímetro na saída que se deseja medir e a outra ponta é no terra. Como a resistência ôhmica do microamperímetro é muito pequena, tem-se praticamente um curto-circuito da saída do componente para o terra. Antes de se inserir o microamperímetro é necessário colocar nas entradas do componente uma condição tal que as saídas vão para nível lógico "1". Somente depois que a saída vai para "1" é que a corrente é medida. Este procedimento deve ser rápido, para não danificar o componente.

Este teste deve ser realizado no final do programa de teste, pois aquece o componente, podendo alterar os valores das outras medições.

O chip é alimentado com VCC máximo. A figura 3.12 ilustra a medição de IOS. A tabela 3.2 apresenta as condições de medição da corrente de curto-circuito para as portas AND, NAND, OR, NOR .

Figura 3.12 : Medição da corrente de Curto-Circuito.

| FUNÇÃO          | CONDIÇÃO DE ENTRADA                  |

|-----------------|--------------------------------------|

| NAND            | Todas as entradas em GND             |

| AND             | Todas as entradas em $4.5\mathrm{V}$ |

| NOR             | Todas as entradas em GND             |

| OR              | Todas as entradas em $4.5\mathrm{V}$ |

| AND-OR-INVERTER | Todas as entradas em GND             |

| AND-OR          | Todas as entradas em $4.5\mathrm{V}$ |

Tabela 3.2 :Condições de entrada para a medição de IOS.

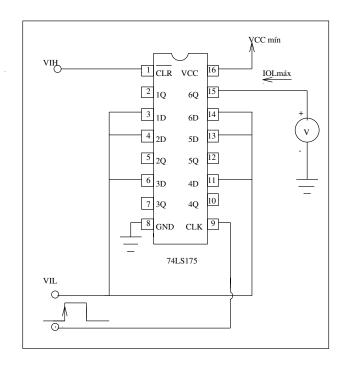

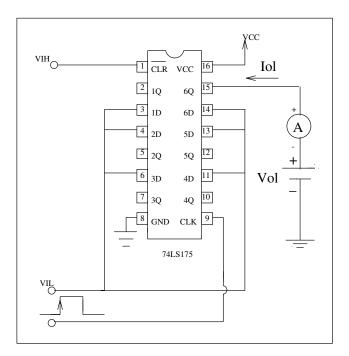

#### 3.3.10 Medição de IOL

Esta corrente geralmente não é medida nos testes elétricos mais comuns. Seu valor máximo, fornecido pelo manual do fabricante do componente, é utilizado como corrente de carga para a realização do teste funcional e para a medição de VOL. A corrente IOL deve ser medida na fase de caracterização, forçando-se uma tensão de VOL na saída do componente e medindo-se a corrente resultante. Obviamente, o *chip* deve ser levado à condição de saída de nível lógico baixo. A figura 3.13 ilustra este procedimento.

Figura 3.13 : Medição da corrente IOL.

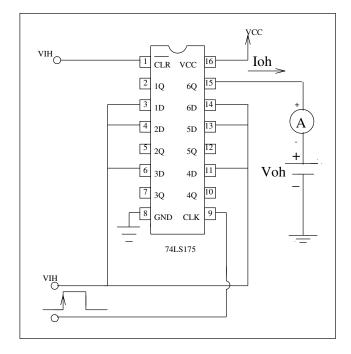

Figura 3.14 : Medição da corrente IOH.

#### 3.3.11 Medição de IOH

Esta corrente geralmente não é medida nos testes elétricos mais comuns. Seu valor máximo, fornecido pelo manual do fabricante do componente, é utilizado como corrente de carga para a realização do teste funcional e para a medição de VOH. A corrente IOH deve ser medida na fase de caracterização, forçando-se uma tensão de VOH na saída do componente e medindo-se a corrente resultante. Obviamente, o *chip* deve ser levado à condição de saída de nível lógico alto, como mostra a figura 3.14.

## 3.4 PARAMÉTRICO AC

As medições paramétricas AC, ou o teste paramétrico AC, nome geralmente dado para o teste/medições de tempos, são medições mais complexas de serem realizadas que as medições paramétricas DC. Estão relacionadas com os tempos de comutação dos transistores internos ao circuito integrado. Requerem equipamentos mais precisos, necessitam de uma atenção especial na montagem da *interface* que conecta o componente ao testador e gastam um tempo grande de teste.

Geralmente estas medições são realizadas na fase de caracterização do circuito integrado. A finalidade destas medições é assegurar que mudanças de estados lógicos (edges) ocorram em um determinado espaço de tempo. A medição paramétrica AC pode precisamente quantificar os valores exatos destas mudanças.

Em um programa de teste para produção, os parâmetros AC não são medidos, pois estas medições são lentas, mas são verificados durante a execução do teste funcional.

Os principais parâmetros AC especificados para a operação funcional do dispositivo são:

- tPHL Tempo de atraso de propagação do nível lógico alto para o nível lógico baixo.

- tPLH Tempo de atraso de propagação do nível lógico baixo para o nível lógico alto.

- ullet  $\mathbf{tPHZ}$  Tempo para desabilitar uma saída  $\mathit{Tri-state}$  do nível lógico alto .

- tPLZ Tempo para desabilitar uma saída Tri-state do nível lógico baixo.

- tPZH Tempo para habilitar uma saída Tri-state para o nível lógico alto.

- tPZL Tempo para habilitar uma saída Tri-state para o nível lógico baixo.

- tTLH Tempo de transição do nível lógico baixo para o nível lógico alto.

- tTHL Tempo de transição do nível lógico alto para o nível lógico baixo.

- tSU Tempo de setup.

- tH Tempo de hold.

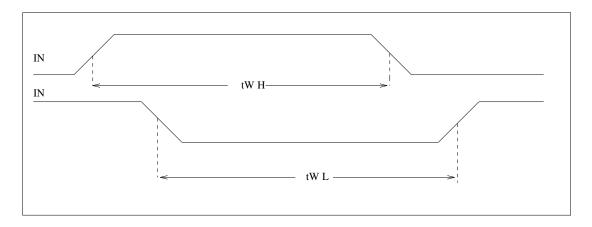

- tW Tempo de duração do pulso.

- fmax Freqüência máxima

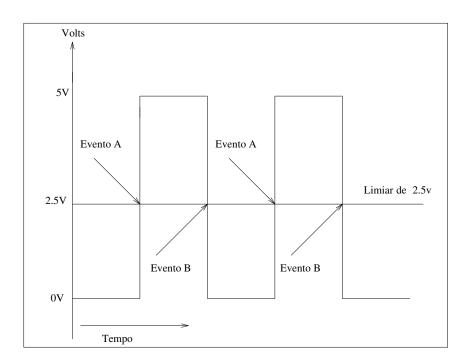

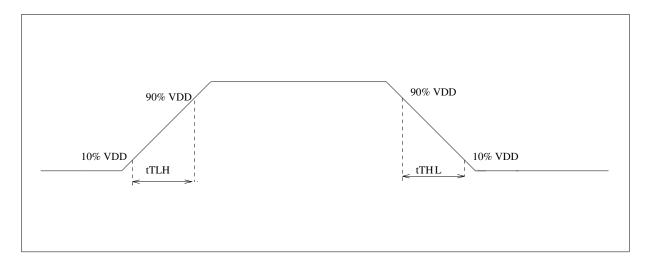

#### 3.4.1 Evento

Um evento é definido como a ocorrência de uma transição de tensão através de um nível especificado, o LIMIAR (threshold), em uma dada direção (slope), como mostra a figura 3.15. Geralmente as medições de tempo utilizam como referência estes limiares de tensão.

Figura 3.15 : Ocorrência de um evento.

#### 3.4.2 Atraso de propagação

A tensão de saída de uma porta lógica nunca responde instantaneamente às variações de entrada. Há sempre um certo atraso associado à porta lógica. Este atraso é característica de qualquer sistema real e, no caso específico dos circuitos integrados, ele ocorre devido, principalmente, às diversas capacitâncias associadas aos componentes discretos contidos na pastilha. As medidas comuns do tempo de atraso de propagação são:

- Tempo de propagação entre dados de entrada e dados de saída. Para o caso de lógica combinacional e buffers.

- Tempo de propagação entre o sinal de habilitar saída (enable) e a alteração no sinal de saída.

Para o caso dos circuitos com saídas tri-state.

- Tempo de propagação entre o sinal de relógio (clock) e a alteração no sinal de saída. Para o caso dos flip-flops e dos latches.

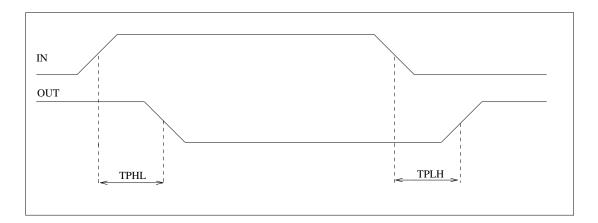

A figura 3.16 mostra as formas de onda de entrada e saída de uma porta inversora TTL, e os tempos de atrasos envolvidos.

Figura 3.16 : Tempos de propagação tPHL e tPLH.

#### 3.4.3 tPHL

É o tempo de propagação do estado lógico "1" para o estado lógico "0". Este tempo é medido entre pontos de referência de tensão especificados sobre as formas de ondas de entrada e de

saída, com a saída variando de um nível lógico alto definido para um nível lógico baixo definido.

#### 3.4.4 tPLH

É o tempo de propagação do estado lógico "0" para o estado lógico "1". Este tempo é medido entre pontos de referência de tensão especificados sobre as formas de ondas de entrada e de saída, com a saída variando de um nível lógico baixo definido para um nível lógico alto definido.

#### 3.4.5 tPD

O tempo de atraso de propagação tPD é medido entre pontos específicos de referência nas formas de onda de entrada e de saída , com a saída variando de um nível lógico definido (alto ou baixo) para outro nível lógico definido (baixo ou alto).

O atraso de propagação é um fator que limita a aplicação de um CI, principalmente nas freqüências mais elevadas. Se a freqüência do sinal de entrada de um dado CI variar muito rápido, em um tempo menor que o atraso de propagação, a saída do circuito integrado não conseguirá responder às variações da entrada, ocasionando um erro no funcionamento do circuito.

O conhecimento dos tempos de atraso é muito importante no projeto prático do circuito. A fim de se evitar o aparecimento de pulsos espúrios indesejáveis, ou de ter o conhecimento de onde eles ocorrem deve-se fazer, pelo menos em esquemas complexos, o chamado "diagrama de tempo", que consiste em se desenhar as formas de onda afetadas pelos diversos tempos de propagação.

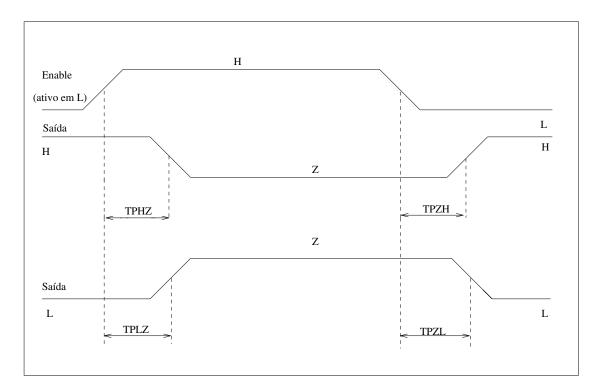

#### 3.4.6 tPHZ

É o tempo gasto para a saída transicionar do nível lógico "1" para o estado de alta impedância, isto é, o tempo gasto para desabilitar uma saída tri-state que estava anteriormente com nível lógico "1". É medido entre pontos específicos de referência nas formas de onda de entrada (sinal de enable) e de saída, com a saída tri-state variando de um nível lógico "1" para o estado de alta impedância.

#### 3.4.7 tPLZ