Galdenoro Botura Junior

Engenheiro Eletricista, INATEL, 1980

"PROJETO DE UM MULTIPLICADOR CHAVEADO"

Dissertação apresentada à Faculdade de Engenharia de Campinas, UNICAMP, como requisito parcial para obtenção do título de "Mestre em Engenharia Elétrica"

Orientador: Prof. Dr. Alberto Martins Jorge

Universidade Estadual de Campinas

Faculdade de Engenharia de Campinas

Departamento de Engenharia Elétrica

Laboratório de Eletrônica e Dispositivos

Junho de 1985

TUNICAMP

BIBLIOTECA (ENTRAL

Este trabalho contou com apoio das seguintes entidades:

- CAPES através do PROGRAMA INSTITUCIONAL DE CAPACITAÇÃO DE DOCENTES PICD.

- FINEP através do contrato nº B/72/81/409/00/00

- FAPESP através do contrato nº 84/2194-2

Este sumple ennesponde a redação final da tere defendida por GALDENORO BORRA

TR. e represenda pula Crimssão pelegadora

em 19/06/85

all to hat fre

Aos meus pais, GALDENORO BOTURA e JANDIRA GALLO BOTURA.

#### **AGRADECIMENTOS**

Prof. Alberto Martins Jorge, que com sua orientação clara e objetiva, proporcionou-me a segurança necessária na realização deste trabalho.

Prof. Carlos Reis, pelas preciosas sugestões ofereci das, que acabaram por influenciar

não só este trabalho mas também minha formação como um todo.

Prof. José Antonio S. Dias, pelas observações e críticas que ajudaram a direcionar não só o proje

to, como também todo o trabalho rea

lizado.

Carlos Pimentel, pelas proveitosas discussões durante nossa convivência.

Daniel Roseno da Silveira, pelo inestimável auxílio prestado, no desenvolvimento do trabalho de computação.

Claudia Mariana Antonialli, pelo precioso auxílio nas realiza ções das medidas.

Maria Auxiliadora Mazotini, pela eficiência e capricho nos desentos e nhos realizados.

Célia de Oliveira, pela paciência, dedicação e esmero no trabalho de datilografia.

Enfim, a todos que deram indiretamente alguma contribuição para o conteúdo deste texto, a gratidão do autor.

# SUMÁRIO

| Apresentação        |                                     | 1  |

|---------------------|-------------------------------------|----|

| Capítulo I - SISTEM | A DE MODULAÇÃO POR CÓDIGO DE PULSO  | 3  |

| 1.1 1               | ntrodução                           | 3  |

| I.2 T               | ransmissão Digital                  | 4  |

| I.3 C               | constituição de um Sistema MCP      | 5  |

| I.4 Q               | puantização                         | 6  |

| I.5 S               | ubsistema Decodificador (Lei A-128) | 10 |

| 1.6 E               | studo de Tempo no Decodificador     | 13 |

| Capítulo II - BLOCO | MULTIPLICADOR DO SISTEMA MCP        | 16 |

| II.1                | Introdução                          | 16 |

| II.2                | Características Necessárias para    |    |

|                     | o Circuito Multiplicador Proposto   | 17 |

|                     | II.2.1 Características Impostas     |    |

|                     | pela Malha Decodificadora.          | 17 |

|                     | II.2.2 Erro de Linearidade          | 19 |

|                     | II.2.3 Relação Sinal/Ruído (S/R).   | 22 |

|                     | II.2.4 Variação da Saida com a      |    |

|                     | Temperatura                         | 23 |

|                     | II.2.5 Resposta em Frequência do    |    |

|                     | Circuito                            | 23 |

| •                   | II:2.6 Taxa de subida para execu-   |    |

|                     | ção do Chaveamento - "Slew          |    |

| •                   | Rate"                               | 24 |

|                     | II.2.7 Resumo das Características   |    |

|                     | Exigidas                            | 24 |

| 11.3                | Princípio de Multiplicação Utili-   |    |

| •                   | 7240                                | 25 |

| 11.4 Comportamento Logaritmico de uma              |    |

|----------------------------------------------------|----|

| Junção PN Diretamente Polarizada                   | 26 |

| Capítulo III - Projeto do Multiplicador Chaveado   | 36 |

| III.l Desenvolvimento de uma Estrut <u>u</u>       |    |

| ra Adequada                                        | 36 |

| III.2 Configurações Desenvolvidas                  | 38 |

| III.2.1 Multiplicador Chaveado                     |    |

| Versão 01                                          | 39 |

| III.2.2 Multiplicador Chaveado                     |    |

| Versão 02                                          | 49 |

| III.2.3 Multiplicador Chaveado                     |    |

| Versão 03                                          | 53 |

| III.2.4 Multiplicador Chaveado                     |    |

| Versão 04                                          | 59 |

| III.3 Multiplicador Chaveado - Ver -               |    |

| são Final                                          | 60 |

| III.3.1 Modificações Introduzi                     |    |

| das                                                | 60 |

| III.3.2 Problemas Verificados                      |    |

| na Célula Multiplicado                             |    |

| ra                                                 | 65 |

| III.3.3 Configuração Final                         | 72 |

| Capítulo IV - TESTE E VERIFICAÇÃO DE DESEMPENHO DO |    |

| CIRCUITO PROJETADO                                 | 75 |

| IV.1 Construção do Protótipo                       | 75 |

| IV.1.1 Determinação dos Transis-                   |    |

| tores                                              | 75 |

| IV.1.2 Determinação dos Resisto-                   |    |

| res                                                | 77 |

|                     | IV.1.3 Fontes de Corrente                  | 81  |

|---------------------|--------------------------------------------|-----|

| . IV.2              | Desempenho do Circuito de Compens <u>a</u> |     |

|                     | ção e Célula de Saída                      | 84  |

|                     | IV.2.1 Circuito de Compensação             | 84  |

|                     | IV.2.2 Célula de Saída                     | 91  |

| iv.3                | Testes e Resultados Obtidos no ci <u>r</u> |     |

|                     | cuito Protótipo                            | 9 3 |

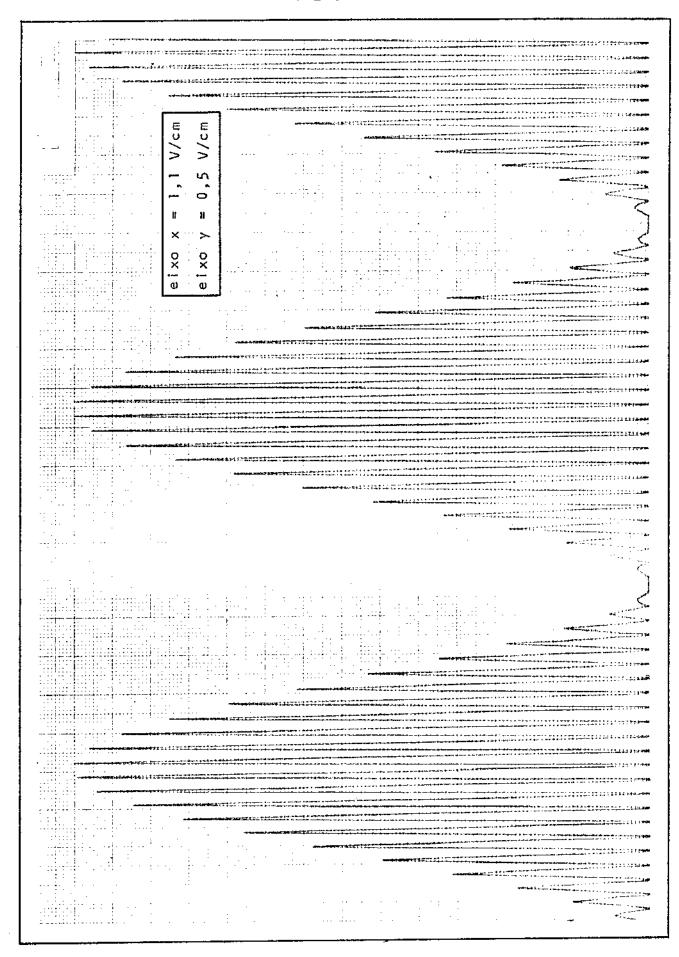

|                     | IV.3.1 Teste de Linearidade                | 93  |

|                     | IV.3.2 Relação Sinal-Ruido                 | 96  |

|                     | IV.3.3 Variação de Saída com a Te <u>m</u> |     |

|                     | peratura                                   | 97  |

|                     | IV.3.4 Variação do Sinal de Saída          |     |

|                     | com a Freqüência                           | 100 |

|                     | IV.3.5 Taxa de Subida                      | 103 |

| IV.4                | Aplicação do Circuito Protótipo em         |     |

|                     | um MCP                                     | 104 |

| IV.5                | Utilização do Circuito Multiplica-         |     |

|                     | dor de um Modo Geral                       | 106 |

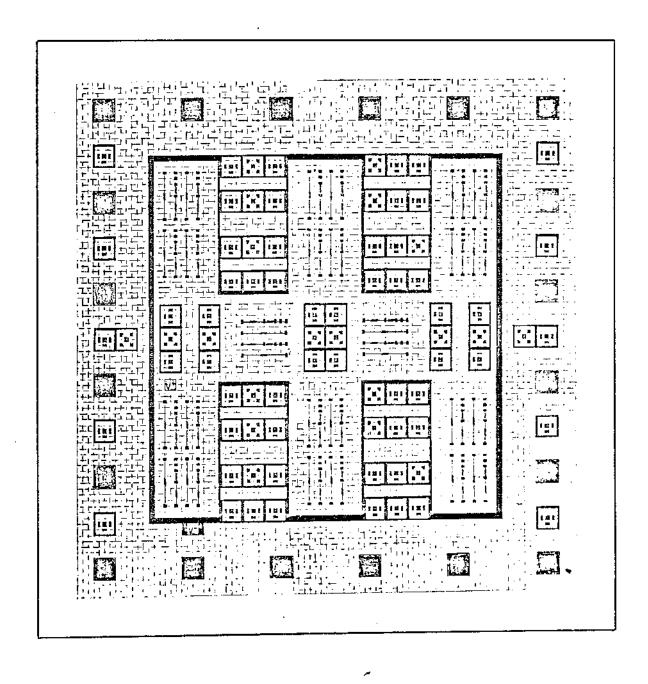

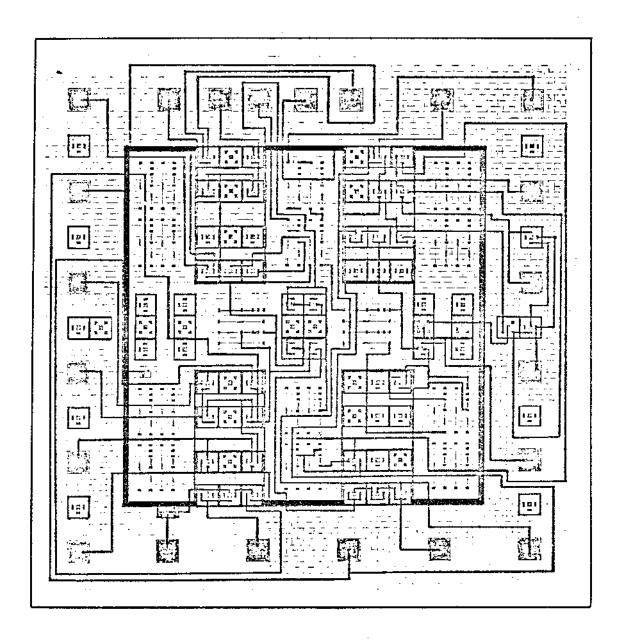

| Capftulo V - INTEGR | AÇÃO DO DISPOSITIVO                        | 114 |

| V.1 D               | efinição das Máscaras                      | 114 |

| V.2 C               | omentários Finais e Conclusão              | 119 |

| APÊNDICE A          |                                            | 121 |

|                     |                                            | 128 |

|                     | RĀFICAS                                    | 129 |

|                     | 1                                          |     |

#### GLOSSÁRIOS DE SÍMBOLOS

- A Relação de área entre os emissores dos pares internos e externos da célula multiplicadora de Gilbert

- P. Fonte de corrente de número "n"

- a Índice de modulação

- a<sub>n</sub> Indice de modulação da célula multiplicadora de número "n"

- a' Indice de modulação da célula multiplicadora de número "n", com seus desvios associados

- B "Bit" da palavra digital com "n" indicando a sua respectiva posição dentro da palavra

- B Negação do "bit" de número "n"

- b Indice de modulação

- Cico Capacitância de junção de coletor com polarização zero

- c Capacitância de junção de emissor com polarização zero

- $D_{\rm A}$  Desvio associado ao descasamento entre os transistores

- Desvio associados ao descasamento entre transistores da célula de número "n"

- d Razão entre Is e Io

- d' Razão entre Is e Io com os desvios associados

- db decibel

- E Erro máximo

- f Frequência

- $f_{rr}$  Frequência de corte

- I Corrente

- La Corrente gerada na malha decodificadora que indica o ni vel de sinal dentro do segmento

- IB Corrente na base do transistor

- IB<sub>N</sub> Corrente na base de transistor "n"

- Th Corrente gerada na malha decodificadora que indica o n $\underline{\acute{u}}$  mero de ordem do segmento onde se encontra a amostra

- Ic Corrente no coletor do transistor

- I Corrente no coletor do transistor "n"

- I<sub>E</sub> Corrente de referência dos pares internos da célula multiplicadora

- I<sub>e</sub> Corrente no emissor

- I Corrente no emissor do transistor "n"

- I<sub>M</sub> Corrente de saída da célula multiplicadora versão 02

- $\text{I'}_{\text{M}}$  Corrente complementar em relação à  $\text{I}_{\text{M}}$

- Io Corrente de referência a ser multiplicada por  $\mathbf{I}_{\mathbf{b}}$

- I' Corrente de referência antes de ser espelhada

- I Corrente de polarização da fonte de número "n"

- I<sub>R</sub> Corrente de referência dos pares externos da célula multiplicadora

- I'R Corrente de referência antes de ser espalhada

- I'R Corrente de referência do multiplicador "n"

- I<sub>S</sub> Corrente de saída da célula multiplicadora versão final

I<sub>Sn</sub> - Corrente de saturação do transistor n

$I_{So}$  - Corrente de saída da célula multiplicadora desconside rando o efeito de  $\beta$  finito

I, - Corrente de saída da célula multiplicadora - versão 02-

Iw - Corrente constante no conversor I/V

J - Densidade de corrente

J<sub>S</sub> - Densidade de corrente de saturação

K - Constante de proporcionalidade

KI - Constante que relaciona Io, IR<sub>1</sub>, IR<sub>2</sub>

K¹ - Constante de multiplização

ln - Logarítmo neperiano

Mn - Célula Multiplicadora de número "n"

m - Constante próxima à unidade

m<sub>A</sub> - Miliampere

M<sub>c</sub> - Coeficiente de junção de coletor

Ma - Coeficiente de junção de emissor

n - Número natural

p - Potencial de junção de coletor

P - Potencial de junção de emissor

Q<sub>b</sub> - Carga armazenada na base

on - Transistor de número "n"

q - Carga do eletron

R - Resistor

RB - Resistor limitador de corrente

Resistência de emissor associada aos pares externos da célula multiplicadora

R<sub>c</sub> - Resistor de Conversão I/V

Resistência de emissor associada aos pares internos da célula multiplicadora

R<sub>n</sub> - Resistor de número "n"

R - Resistor de polarização

$T_{f}$  - Tempo de transito direto

$T_S$  - tempo de subida

V - Tensão

v - Tensão aplicada externamente à junção

Vcc - Tensão de polarização

V - Tensão de polarização

Vm - Tensão máxima de saída

Vms - Tensão máxima de saída do segmento

v - Tensão de saída

V<sub>R</sub> - Tensão de referência

$V_{m}$  - Tensão termodinâmica

T - Temperatura em Kelvin

α - Ganho de corrente em base comum

$\beta$  - Ganho de corrente em emissor comum

$\Delta$  - Relação entre  $\beta$  , IR e IE

Δρ - Intervalo de tempo entre dyas palavras digitais

- Δv Intervalo de tensão entre dois níveis

- δ Desvio total da célula multiplicadora

- ØB Queda de potencial na resistência ohmica associada aos emissores externos da célula multiplicadora

- ØE Queda de potencial na resistência ohmica associada aos emissores internos da célula multiplicadora

# APRESENTAÇÃO

Durante os anos 70 foi estabelecido um convênio de pesquisa e desenvolvimento de equipamentos de comunicações en tre o Departamento de Engenharia Elétrica da UNICAMP e a Tele bras (Telecomunicações Brasileiras S/A). Deste convênio, surgiu um trabalho denominado "Ensaio no Projeto e Construção de um Decodificador D/A, com Técnica I<sup>2</sup>L", que teve como objetivo primordial a construção e o estudo dos elementos básicos de um bloco de decodificação dos sinais digitais em analógios para um sistema de modulação por código de pulso (MCP)Lei -A, sendo este bloco na forma monolítica e constando de geradores de sinais de pesos binários, portas lógicas e registradoras de deslocamento. A este bloco, neste trabalho, passamos a chamar de "Malha Decodificadora".

O presente trabalho se propõe a dar continuidade ao estudo do decodificador MCP Lei-A, a partir da malha decodificadora realizada, procurando desenvolver um projeto que venha a ser o bloco final do decodificador.

O estudo deste bloco final nos mostrou que o circuito necessário para completar o sistema era um dispositivo'

que multiplicasse as correntes binárias geradas e, recebendo

o pulso de polaridade, definisse o potencial de saída do sinal.

A técnica proposta para a realização desta multiplicação baseia-se no "Princípio Translinear", um princípio '

conhecido internacionalmente e que foi a base de projetos de

circuitos multiplicadores encontrados comercialmente e na literatura especializada.

Procurou-se colocar os capítulos e também os assuntos por eles abordados com uma distribuição linear no que se refere ao desenvolvimento do trabalho efetuado, tentando assim, caracterizar o esforço desenvolvido e o grau das dificuldades encontradas em um projeto desta natureza.

## CAPITULO I

SISTEMA DE MODULAÇÃO POR CÓDIGO DE PULSO (MCP)

#### I.l Introdução

É inegável na história da Humanidade, a grande preocupação que o Homem sempre teve em conseguir comunicar-se de uma forma segura e precisa, sem que alterações nas informações modificassem o significado ou a intelegibilidade final de seu pensamento. Com a invenção do telefone por Graham Bell no século XIX, o seu grande sonho começou a se tornar realidade, com a possibilidade de se fazer ouvir a uma distância em que an teriormente somente se fazia entender através de mensagens en viadas por telégrafo.

A evolução da telefonia passou por várias etapas que <u>i</u> nicialmente ofereciam barreiras quase que intransponíveis, de vido ao estágio de desenvolvimento tecnológico reinante até então. A medida que esta tecnologia foi se superando, a intelegibilidade foi se acentuando e novas formas de transmissão foram sendo pesquisadas.

Nos dias de hoje, existe uma tendência cada vez maior de se trabalhar com o sinal, na sua forma digital, através da codificação por pulsos da informação. Este meio, por permitir a reconstituição e a correção do sinal transmitido, tornou-se de grande interesse, e pesquisas vêm se acentuando para tornar este sistema cada vez mais eficiente, compacto e barato.

### I.2 Transmissão Digital

Transmissão digital é a técnica de troca de informações por meio de sinais codificados digitalmente. A procura uma forma eficiente de codificar a informação em pulsos, posteriormente decodificá-la para se obter novamente o sinal analógico original, encontra sua origem muito antes de inven ção do telefone por Alexandre Graham Bell. Sabe-se que. primeiras pesquisas nesta área datam de 1837 (17) e a partir daí vários métodos foram desenvolvidos, de forma a permitir' uma membrana abrir e fechar um circuito através das vibra ções recebidas. Porém, o estágio tecnológico não estava sufi cientemente desenvolvido, de modo que estas pesquisas tivessem sucesso. Novamente voltou-se a pesquisar a transmissão ' digital, quando se sentiu a grande dificuldade que se tinha para transmitir canais múltiplos, principalmente devido diafonia existente e a grande complexidade nas estruturas dos filtros exigidos.

Uma particularidade da transmissão digital é aumentar a facilidade de se conseguir a multiplexagem temporal, isto é, a transmissão de várias mensagens intercaladas no tempo.

Em 1937, A.H. Reeves, membro do Laboratório da ITT francesa, propôs um tipo de codificação digital onde se varia a largura dos pulsos, de acordo com a amplitude do sinal a ser codificado, e que ficou conhecido como modulação por largura do pulso (MLP). Porém, Reeves não havia ainda conseguido o seu intento inicial, que consistia em obter uma codificação onde apenas a existência ou não do pulso, seria o suficiente para conseguir a reconstituição das informações.

Deste modo, em 1937, adveio o sistema de modulação por código de Pulso (MCP), com conceitos diferentes aos existentes na época, sendo amplamente aclamado e difundido. Porém, a ine - xistência de componentes adequados não permitiu a sua evolu - ção.

A partir da 2ª Grande Guerra, mais propriamente com a invenção do transistor, um grande avanço se deu na eletrônica, permitindo uma maior complexidade de um sistema, com um número cada vez menor de dispositivos.

Atualmente, a grande maioria dos sistemas telefônicos que estão entrando em vigor utilizam esta técnica de transmissão, e a tendência é um crescimento na demanda destes siste mas.

# I. 3 Constituição de um Sistema MCP

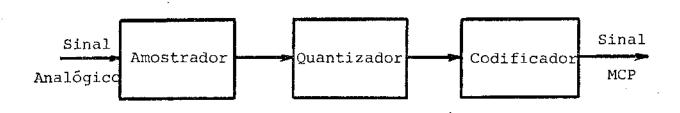

Basicamente, um sistema MCP é composto de um subsistema codificador, onde se faz a transformação do sinal analógico em um sinal digital correspondente e um decodificador, onde 'se efetua a conversão da palavra digital recebida em níveis a nalógicos. Por ser composto de um codificador e um decodificador, este sistema é geralmente chamado de CODEC (COdificador + DECodificador).

O diagrama em blocos representa as diversas partes que compõem um CODEC

Fig. I.1 - Diagrama em blocos representativo de um CODEC

A partir deste item passaremos a analisar minuciosamente o bloco referente ao decodificador e as possíveis in fluências originadas da codificação, que possam de algum mo do influenciar seu desempenho.

### I.4 Quantização

O objetivo do codificador MCP é transformar a mensagem analógica em mensagem digital codificada, e do decodificador o de restabelecer o sinal original a partir da palavra em código.

Na codificação do sinal analógico, surge um ruído ir removível, conhecido como Ruído de Quantização, e que somente seria eliminado, caso codificassemos o sinal em um número infinito de "bits".

Alguns dos métodos de minimização deste ruído, desen

senvolveram-se a partir de estudos onde se levou em consideração as características dos sinais de voz em um ser humano, e da característica de codificação.

Verificou-se que, quando se faz uma quantização linear, ou seja, estabelece que o nível analógico variará entre + V e - V e divide-se em espaços iguais com número finito de elementos, entre estes extremos ( + V e - V), os níveis fracos de sinais correspondentes a um único passo de quantização terão um erro de meio passo ou seja, um erro por centual de 50% para o "bit" menos significativo. Caso o sinal a ser codificado permaneça durante muito tempo em níveis fracos, a relação sinal ruído será muito baixa.

Uma forma de atenuar este problema é fazer uma divisão do espaço entre + V e - V de maneira não linear, ou seja, faz-se o espaço que corresponde aos níveis fracos de sinais, com um número maior de divisões do que os correspondentes aos níveis fortes.

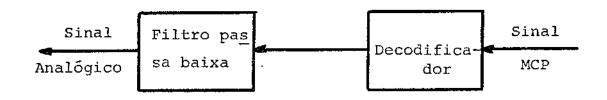

Um método clássico que utiliza uma codificação não linear, e muito bem analisado por Kaneko (3), é o método denominado "Lei de Compressão Logarítmica com A = 87,6" e da qual passaremos a tratar a seguir.

A "Lei A", de acordo com a CCITT, é definida para níveis de sinal expandido (y) e comprimido (x), normalizados segundo a seguinte relação, abaixo,, e na referência (3) ' é feita uma análise onde se demonstra que maximização da relação sinal ruído (S/R) ocorre com a função log x:

$$x = \frac{1 + \frac{\log_k Ay!}{1 + \log_k A}} \text{ para } \frac{1}{A} \leq y \leq 1$$

(1.2)

$$x = \frac{Ay}{1 + Log_k A} \quad para \quad 0 \leq y \leq 1 \quad (1.3)$$

Sendo: k = e (base do logaritmo neperiano) A = 87,6

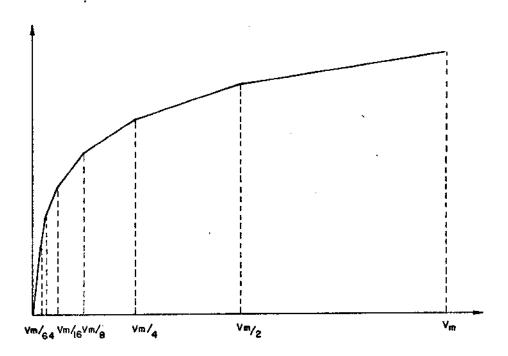

e pode ser representada graficamente pela figura abaixo:

Fig. I.2 - "Lei-A" para A = 67,6

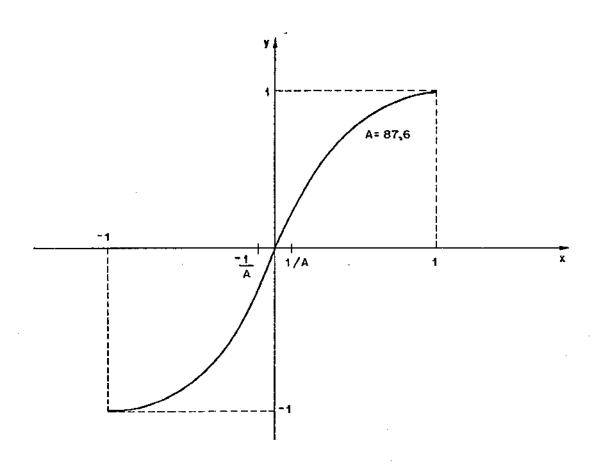

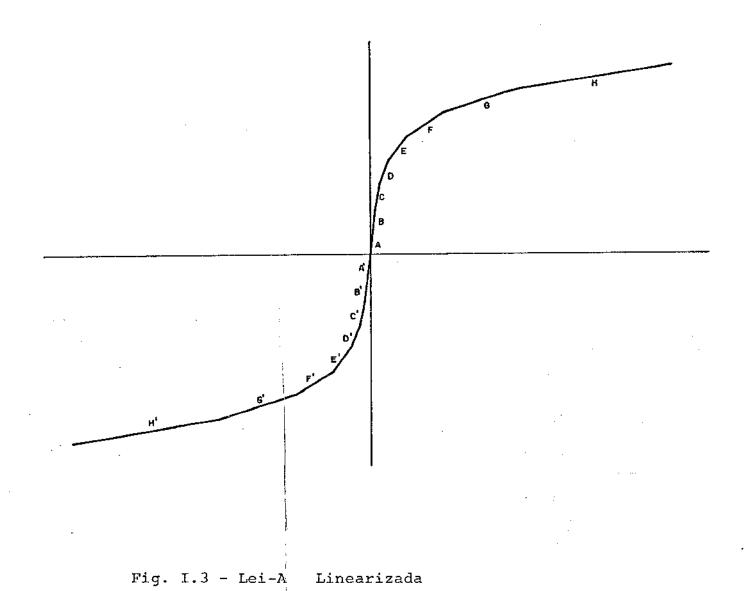

Se tomarmos 8 bits de codificação como referência para um rápido estudo sobre esta lei, pode-se aproximar esta curva por uma característica linear por partes. Para se realizar esta linearização, divide-se cada uma das suas partes (positiva e negativa) em 16 segmentos e faz-se coincidir o 19 segmento com o 29 em cada quadrante. A curva final ficará conforme mostrado abaixo.

Deste modo, teremos 13 inclinações diferentes.

Em-cada ponto de mudança de direção do segmento, a inclinação muda por um fator de 2. Nos dois primeiros seg - mentos, A e B, tem-se um produto que corresponde a uma codificação linear por 12 bits, o segmento C a 11 bits e as - sim sucessivamente, até o segmento H que corresponde a uma codificação Linear por 6 bits.

Esta mesma análise também é válida para a parte ne gativa da curva (A', B', C' .....H').

A Lei A = 87,6 sendo linearizada por partes, utilizando para isto 16 segmentos, de acordo com a figura I.3, passa a ser chamada "Lei A - 128" indicando os 128 níveis 'possíveis de ocupação de sinal amostrado em cada uma de suas partes (positiva e negativa).

Obviamente na demodulação a característica logarí<u>t</u> mica de quantização deve ser levada em consideração para se obter o sinal analógico decodificado sem distorções.

# I.5 Subsistema Decodificador (Lei A- 128)

Uma vez recebido o trem de pulso, torna-se necessário decodificá-lo para novamente obter-se a informação original.

Sabe-se que em um sistema MCP a codificação em função dos "bits" acontece com a seguinte metodologia:

|                |                |                |                |    | ,              |                |

|----------------|----------------|----------------|----------------|----|----------------|----------------|

| B <sub>1</sub> | <sup>E</sup> 2 | В <sub>3</sub> | <sup>B</sup> 5 | В6 | В <sub>7</sub> | В <sub>8</sub> |

- B<sub>1</sub> → indica a polaridade da amostra do sinal, se o mesmo se encontra na parte superior ou inferior da curva de compressão.

- B<sub>2</sub>, B<sub>3</sub>, B<sub>4</sub> → indica em qual segmento a amostra se encontra. Com 3 "bits" pode-se representar os 8 segmentos da curva de compressão.

- $B_5$ ,  $B_6$ ,  $B_7$ ,  $B_8$   $\rightarrow$  indica em qual nível dentro do segmento se encontra a amostra. Com 4 "bits" pode -se representar os 16 níveis existentes dentro de cada segmento.

Uma vez recebido este trem de pulso, e baseado na proposta formulada na referência (2), o "bit" B<sub>1</sub> é enviado para um circuito de polaridade, que atuará no multiplica - dor chaveado na saída do circuito. Ao mesmo tempo,os "bits" B<sub>2</sub>, B<sub>3</sub>, B<sub>4</sub> são enviados para uma malha lógica que processa rá o sinal digital e o entregará a um conversor D/A, que fornecerá em sua saída, um valor de corrente proporcional ao número do segmento em que se encontra a amostra. À corrente referente aos "bits" analisados chamaremos doravante por Ib. Neste mesmo intervalo de tempo os bits B<sub>5</sub>, B<sub>6</sub>,B<sub>7</sub>, B<sub>8</sub> são enviados a um outro conversor D/A, que tem por fina lidade fornecer em sua saída um sinal em corrente proporcional ao nível da amostra dentro do segmento e a esta corrente referente a essa operação passaremos a chamar de Ia.

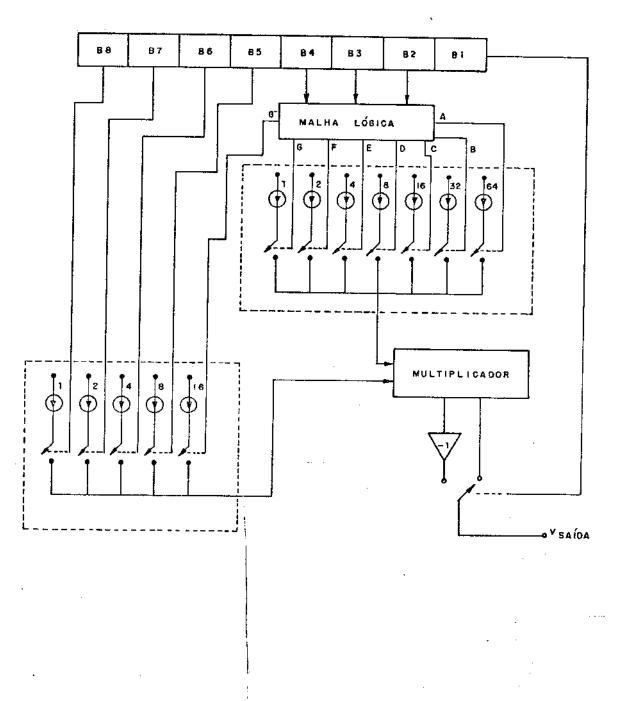

Na referência (4) encontramos um diagrama em bloco que representa o descrito acima de uma forma bastante ' clara; devido a isto, achamos por bem reproduzí-lo aqui.

Fig. I.4 - Constituição de um conversor D/A Ref. (4)

#### I.6 Estudo de tempo no Decodificador

Obviamente, o estudo de tempo de um decodificador de penderá fundamentalmente do número de canais pertencentes 'ao CODEC. Porém, para elucidar este item, tomaremos como e xemplo um sistema com capacidade de transmitir e receber 30 canais telefônicos mais 2 canais de sincronismo, sinaliza -ção e supervisão, com frequência de amostragem de 8 KHZ para cada canal. Estas amostras são comprimidas e quantizadas em 256 níveis e em seguida codificadas em palavras de 8 dígitos. Para este sistemas podemos dizer que a frequência máxima de transmissão ao longo da linha será:

$$f = (8 \text{ digitos}) \times (8 \text{KHZ}) \times (32 \text{ Canais}) = 2048 \text{ KHZ}$$

(I.4)

Para este caso, uma palavra digital chegară se - quencialmente ao decodificador em:

$$\Delta P = \frac{1}{8KHZ \times 32} = \Delta P = 3,9 \mu s$$

, (I.5)

ou seja, o decodificador deverá receber, armazenar e processar cada palavra de código, constituída de 8 dígitos em aproximadamente 3,9  $\mu$ s.

Os dígitos que chegam sequencialmente são armazena dos em registrador de deslocamento e, na metade final do 8º "bit", transferidos para uma memória. Uma vez a palavra digital armazenada na memória, é iniciado o processo de decodificação deste sinal, e durante este mesmo tempo o registrador

de deslocamento se carregará novamente, dando assim continuida de à decodificação.

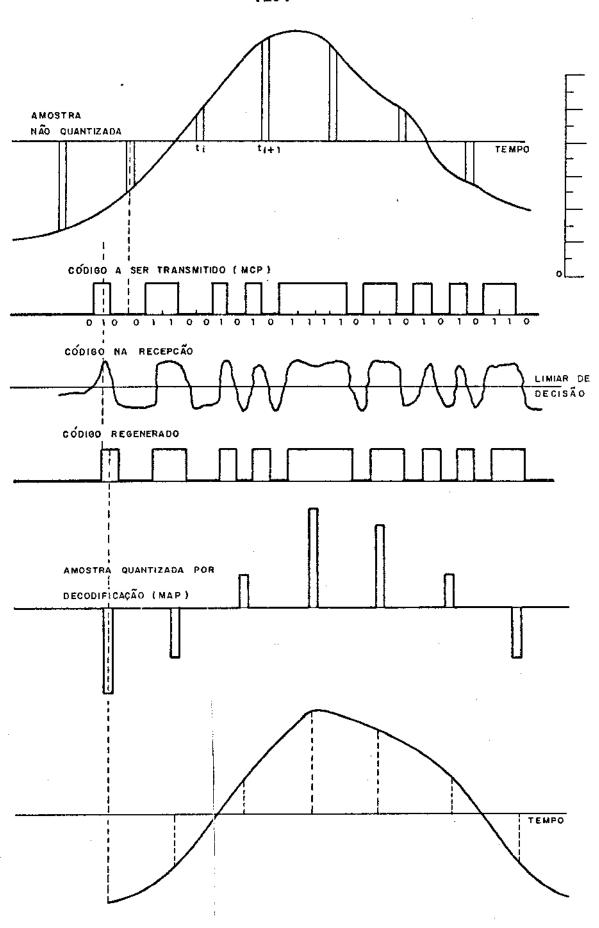

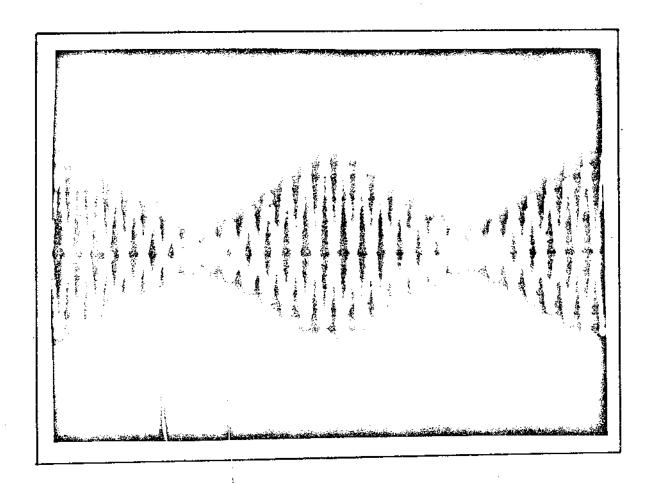

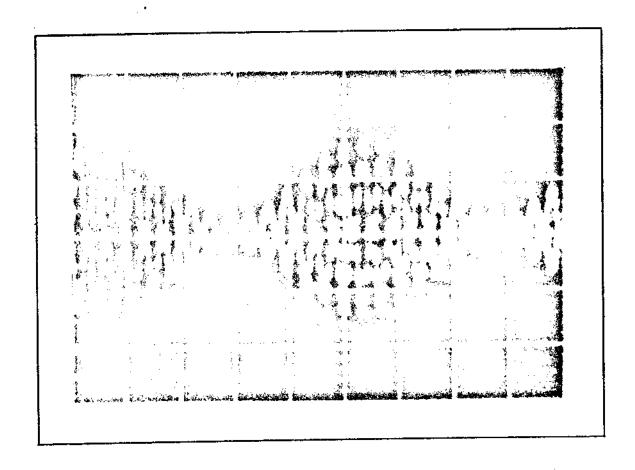

Finalmente, para encerrarmos esta breve visão de um sistema MCP e mais especificamente do subsistema decodifica - dor, achamos de grande importância reproduzir uma breve análi se de um sinal analógico transmitido e recebido por um CODEC, que se encontra na referência (5) (Fig. I.5).

Podemos perceber que uma das grandes vantagens des te sistema é poder, na recepção do sinal digital, reconstituí — lo integralmente na sua forma codificada originalmente, e que uma de suas desvantagens é a não reconstituição do sinal decodificado de acordo com a sua forma original. Porém, este pequeno problema torna-se ínfimo, se compararmos suas distorções com a de um sinal analógico transmitido normalmente.

•

Ref.

Fig. I.5 - Transmissão de um sinal em um sistema MCP

(5)

# CAPITULO II

#### BLOCO MULTIPLICADOR DO SISTEMA MCP

#### II.l Introdução

É comum observar, em sistemas eletrônicos, estágios onde se verifica a necessidade do produto de dois sinais.

Este produto poderá vir a ser aplicado a estágios posteriores ou anteriores, por intermédio de uma realimentação qual quer; ou mesmo ser o objetivo final do sistema projetado.

Assim, podemos observar sistemas onde o uso de um circuito multiplicador facilitou, melhorou, ou mesmo tornou-se im prescindível no seu desempenho. Deste modo, pode-se constatar, atra vés da literatura especializada, os fatos acima mencionados, em sistemas tais como: moduladores, osciladores controlados por ten são, detetores de FM, circuitos quadradores, geradores de valo - res RMS, circuitos de aplicação em computação analógica, etc. En fim, este dispositivo possui uma gama de aplicações bastante ele vada e não é o intuito deste trabalho levantá-las em sua totalidade, visto que é bastante simples colocar-se em contato com elas

Pode-se observar na referência (2), onde desenvolveu-se o projeto da malha decodificadora, que esta consta de dois conversores D/A e de uma malha lógica. Porém, não era a preocupação 'dos autores da citada referência desenvolver o último dos blocos do sistema MCP, o bloco multiplicador.

o presente trabalho se propõe ao desenvolvimento do projeto de um circuito multiplicador que seja inteiramente compativel com a malha decodificadora (2) existente, completando-a e constituindo deste modo, um subsistema decodificador MCP.

# II.2 <u>Características necessárias para o circuito multipli-</u> cador proposto

# II.2.1 Características Impostas pela malha decodifi cadora

Como o dispositivo em projeto servirá fundamentalmente como bloco final do CODEC, as suas características fundamen - tais serão determinadas pelos estágios que o precederam.

Assim, podemos nos basear na referência citada, verificam do que a malha decodificadora tem o seu funcionamento limitada a um único quadrante, fornecendo em seus terminais dois valores de correntes, designados a partir deste ponto com Ia e Ib, e um valor de tensão, referido, como  $B_1$ .

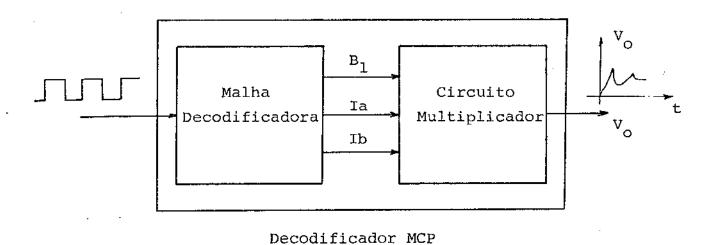

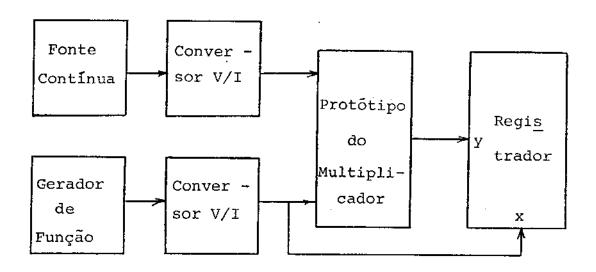

É conveniente, que um sistema MCP tenha seu sinal de saída em tensão. Deste modo, podemos montar um diagrama em blo co que mostrará o subsistema decodificador por inteiro.

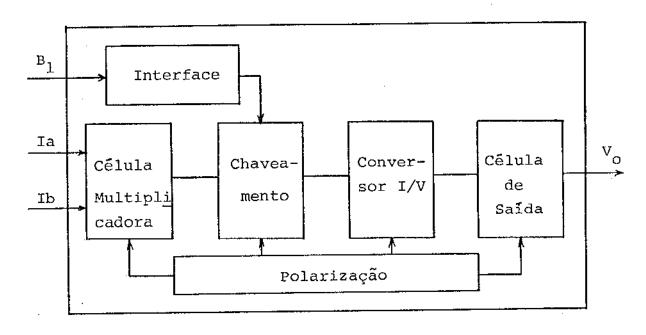

Fig. II.1 - Constituição de um decodificador MCP

A tensão da saída  $V_{O}$  pode ser enquadrada na segui $\underline{n}$  te expressão:

$$V_O = K Ia Ib (B_1 - \overline{B}_1)$$

(II.1)

onde:

- K = constante de proporcionalidade que permite a conversão do sinal de corrente em tensão;

- Ta = sinal em corrente gerado na malha decodificado :

ra que indica o nível do sinal dentro do seg mento;

- Ib = sinal em corrente gerado na malha decodificado

ra que indica o número de ordem do segmento on

de se encontra a amostra;

- B<sub>1</sub> = sinal em tensão, digital, pertencente à pala vra digital recebida pelo decodificador.

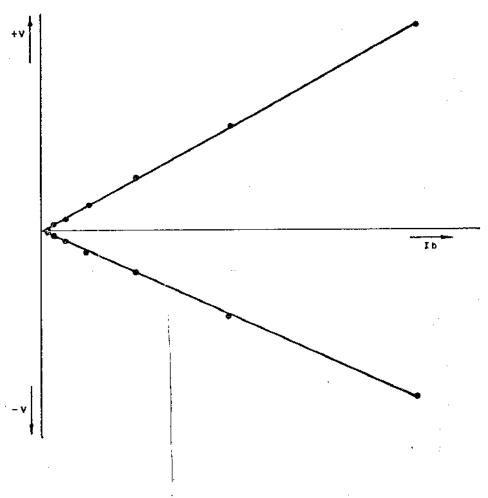

Sabe-se que la varia entre l $\mu$ a e 32 $\mu$ a , Ib entre l $\mu$ a e 64 $\mu$ a e o pulso de B $_1$  de tensão entre "0" e + 3V. Logo, o produto em corrente variará entre l $\mu$ a e 2048 $\mu$ a. Assim, podemos dizer que os níveis de tensão de saída em função às correntes' na entrada do dispositivo variarão segundo a lei abaixo:

$$K \cdot 1\mu A \leq V_O \leq K \cdot 2048 \mu A$$

(II.2)

considerando Ia e Ib variando entre:

O valor da constante de proporcionalidade K será de finido posteriormente em função das exigências do projeto em questão.

#### II.2.2 Erro de Linearidade

A não linearidade de um multiplicador, ou erro de linearidade, é definido (21) do seguinte modo:

"A máxima diferença entre a saída atual e a curva ideal teórica para todos os pares de valores de entrada X e Y. Este valor é especificado como 'uma porcentagem do fundo de escala."

ou seja, para uma dada especificação de  $\pm$  1% em um dispositivo multiplicador com  $\pm$  10 V de variação de saída, significa que esta saída não desviará mais que  $\pm$  100 mv da curva ideal para o máximo desvio de qualquer uma das entradas, com a outra mantida constante.

Em um sistema decodificador e, de acordo com o estabelecido nos itens precedentes, devem existir 256 níveis lógi cos, distribuidos simetricamente em torno do zero.

Defineremos como Vm o valor máximo de Vo, e de accordo com a "Lei A", adotada, teremos entre  $\frac{\rm Vm}{2}$  e Vm, l6 níveis equidistantes; entre  $\frac{\rm Vm}{4}$  e  $\frac{\rm Vm}{2}$ , também l6 níveis equidistantes; e assim por diante, até os intervalos de  $\frac{\rm Vm}{2}$  a zero. Esta distribuição está representada na figura II.2.

Fig. II.2 - "Lei-A" linearizada parte positiva Ref. (10)

Podemos estabelecer que o erro máximo admissível para um sinal analógico decodificado seja tal que o deslocamento do nível em um dado segmento seja a metade do valor do degrau definido para este segmento. Assim, definiremos o máximo erro, da forma que se segue.

O valor máximo de tensão em cada segmento vale:

$$Vms = \frac{Vm}{2^{n-1}}$$

(II.3)

onde:

$n = n\tilde{u}mero de ordem do segmento (1,2,3...7);$

Vm = tensão máxima de saída;

Vms = tensão máxima do ségmento.

O intervalo entre 2 níveis é dado por:

$$\Delta V = \left( \begin{array}{ccc} Vm \\ 2^{j} \end{array} - \begin{array}{ccc} Vm \\ 2^{j+1} \end{array} \right) \cdot \frac{1}{16}$$

(II.4)

onde:

$$j = (n-1)$$

e valerá  $(0,1,2,3,...6)$

Logo:

$$\Delta V = \frac{Vm}{2^{j+5}}$$

(II.5)

Em relação ao valor máximo do segmento, temos que o erro valerá:

$$E = \frac{\Delta V}{2} \cdot \frac{1}{Vms}$$

(II.6)

finalmente, para qualquer segmento teremos um erro máximo de linearidade de:

$$E\% = \left(\frac{\sqrt{m}}{2(2^{j+5})} \cdot \frac{2^{n-1}}{\sqrt{m}}\right) \times 100 \quad (II.7)$$

$$E\% = \frac{100}{2^{6}} \quad (II.8)$$

que corresponderá a um erro de linearidade de 1,5% em um multiplicador especificado para utilização na "Lei A".

# II.2.3 Relação Sinal/Ruido (S/R)

Como a especificação para o menor ruído presente na saída, tomaremos o menor degrau do sinal. Neste caso, te mos o sinal que ocorre entre níveis contínuos do segmento existente entre "o" e  $\frac{\text{Vo}}{128}$ ; como existem 16 níveis, este degrau vale:

$$V = \frac{Vo}{128} \cdot \frac{1}{16} = V = \frac{Vo}{2048}$$

(II.9)

Calculando então a relação Sinal/Ruido máximo, teremos:

$$\frac{S}{R} = \frac{Vo}{Vo/2048} \tag{II.10}$$

$$\frac{S}{R} = 2048$$

em decibéis teremos:

$$\frac{S}{R}$$

(db) = 20 Log 2048 (II.11)

$$\frac{S}{R}$$

(db) = 66,2 db (II.12)

Assim, deveremos obter uma relação sinal ruído para excursão máxima de sinal, superior a 66,2 db, para o cir cuito proposto.

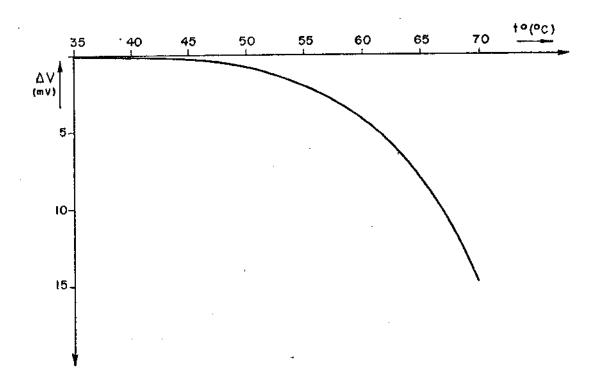

# II.2.4 Variação da saída com a temperatura

Novamente, tomaremos meio degrau menos significati

vo como a variação máxima do sinal de saída com a temperatura ,

somente que agora o relacionaremos com o valor máximo de saída

obtido. Tendo por base o equacionamento desenvolvido no item

2.2 deste capítulo, podemos dizer que o erro máximo valerá:

$$E = \frac{\Delta V}{2} \cdot \frac{1}{Vms}$$

(II.13)

que corresponde a um erro permitido de ± 1,5%.

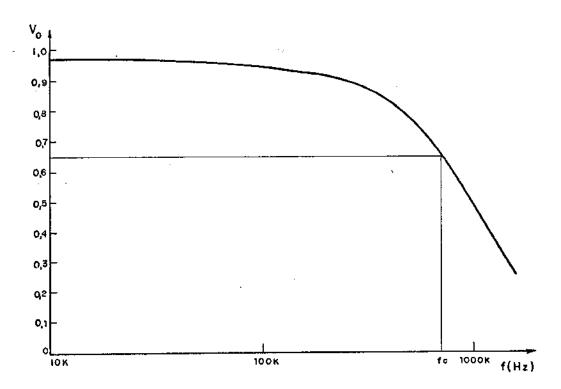

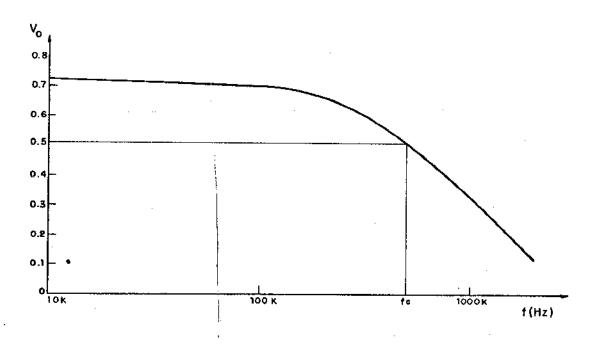

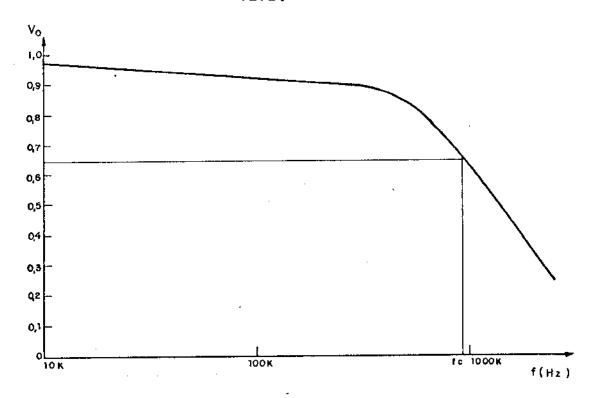

# II.2.5 Resposta em frequência do circuito

De acordo com o projeto desenvolvido e construído pelos autores na referência (2), a malha decodificadora é proposta para realizar a decodificação de um sistema de 32 canais, com frequência de amostragem de 8KHZ por canal. O item' I.5 do capítulo I é desenvolvido, tendo como exemplo um sistema semelhante ao proposto, e de acordo com a equação I.5, uma palavra digital chegará sequencialmente ao decodificador com um intervalo de tempo de aproximadamente 3,9 µs. Este fato estabe lece que a frequência de desempenho será no mínimo de 256 KHZ.

$$f = \frac{1}{3.9 \mu s}$$

(II.12)

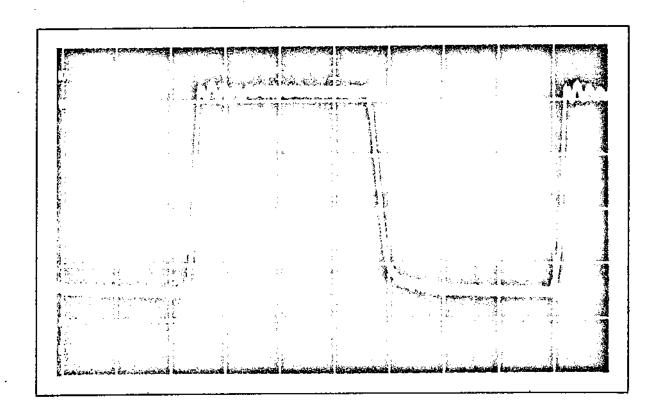

# II.2.6 Taxa de subida para a execução do chaveamento "Slew Rate"

A taxa de subida do sinal para a execução do cha - veamento está fortemente relacionada com o tempo entre uma palavra digital e a seguinte. Como sabemos,o intervalo entre estas palavras é de aproximadamente 3,9μs. Porém, em sua saída, o decodificador terá um circuito demultiplexador. Assim, o sinal gerado pelo conversor deve se estabilizar em 1,5μs, para que possa ser amostrado e passado pelo filtro passa-baixas da recepção nos 2,4μs restantes.

Logo, podemos definir a taxa de subida em:

$$Ts = \frac{Vo}{1.5\mu s}$$

(II.15)

# Resumo das características exigidas II.2.7 K x 2048 $k \times 1$ Variação de sinal Erro máximo de linearidade 1,5% 66db Relação Sinal/Ruído mínimo ±1,5% em relação ao Variação de saída com a temp. valor tido como cor reto a 359C 256 KHZ Resposta em frequência ·V/µs Taxa de subida

# II.3 Princípio de multiplicação utilizado

Devido às características bastante peculiares exigidas pelo circuito, foi realizado um trabalho de pesquisa bibli

ográfica onde se verificou a existência de uma variedade bastante'

grande de técnicas de multiplicação.

Dentre todas, uma chamou a atenção de nossa par te, exatamente pela afinidade com as necessidades técnicas do circuito em questão. Deste modo, passaremos a fazer um breve comentário sobre a técnica de projeto adotada.

A característica logarítmica da função de um dio do, ou mesmo da função base emissor de um transistor bipolar é bas tante conhecida. Há cerca de mais de duas décadas atrás, este efei to já era utilizado (11) para se realizar as operações de multiplicação e divisão. Porém somente em 1975, Gilbert (12), reuniu todas as informações a respeito e propôs uma nova classe de circuitos que denominou "circuitos translineares", apesar dele mesmo (Gil-bert) já haver projetado e publicado várias informações sobre circuitos que utilizam o efeito de junção de um diodo (07), (13), (14). Assim, classificou-se de "circuitos translineares" uma classe de dispositivos onde se trabalha somente no domínio de corrente, explorando o comportamento logarítmico de uma junção PN diretamente polarizada no processamento dos sinais e que utilizando pares de junções PN monolíticas, torna o dispositivo pouco sensível à tempe ratura.

# II.4 Comportamento logarítmico de uma Junção PNdiretamente polarizada

Sabe-se que a relação corrente-tensão em uma fun - ção diretamente polarizada pode ser expressa por:

$$\frac{J}{Js} = e \frac{qv}{mkT} - 1 \qquad (II.16)$$

onde:

J = densidade de corrente direta, na Junção;

Js = densidade de corrente de saturação reversa;

v = tensão aplicada externamente na Junção;

q = carga do elétron;

k = constante de Boltzman;

m = constante próxima à unidade (16)

T = temperatura em Kelvin

considerando que:  $\frac{mkT}{q} \cong V_T$ , que é cerca de 26 mV à tempe ratura 300 K, que a junção utilizada será entre a base e emis sor de um transistor bipolar, e se em níveis reais de corrente desprezarmos o valor "um" em (II.16), cometeremos o erro menor que o de uma parte em um milhão, a expressão pode ser reduzida a:

$$\frac{J}{Js} \stackrel{\text{e}}{=} e^{\frac{Vbe}{V_T}}$$

(II.17)

ou ainda:

$$\frac{\text{Vbe}}{\text{V}_{\text{T}}} \stackrel{\cong}{=} 1n \frac{\text{J}}{\text{Js}}$$

(II.18)

Assim, por intermédio de (II.18) podemos verificar que a tensão através da junção base-emissor de um transistor' bipolar é proporcional ao logarítmo da razão entre as densidades de correntes, direta e a de saturação, desta junção. Is to nos leva a concluir que uma soma de tensões de junções PN, diretamente polarizadas, será a soma dos logarítmos : da razão entre as densidades de correntes envolvidas e que esta soma de logarítmo coincidirá com a multiplicação das correntes' que fluem por estas mesmas junções.

Um modo de esclarecer melhor o fato mencionado  $\underline{a}$  cima  $\tilde{\mathbf{e}}$  apresentar um pequeno exemplo, onde este conceito seja aplicado em um circuito com transistores ideais.

Suponha que se deseje conhecer o valor da corrente I, no circuito abaixo.

Fig. II.3 - Circuito translinear

Sabe-se que:

$$- Vbe_1 + Vbe_4 - Vbe_3 + Vbe_2 = 0$$

(II.19)

ou

$$Vbe_{4} + Vbe_{3} = Vbe_{1} + Vbe_{2}$$

(II.20)

Aplicando-se (II.18) em (II.20) tem-se:

$$V_{T4} l_n \frac{J4}{Js4} + V_{T2} l_n \frac{J2}{Js2} = V_{T1} l_n \frac{J1}{Js1} + V_{T3} l_n \frac{J3}{Js4}$$

(II.21)

Considerando os transistores em um circuito monolítico, e próximos uns dos outros, podemos fazer as seguintes 'considerações:

$$V_{T4} = V_{T2} = V_{T1} = V_{T3}$$

(II.22)

$$Js_4 = Js_2 = Js_1 = Js_3$$

(II.23)

Assim, a equação II.22 pode ser simplificada para:

$$\ln J_4 + \ln J_2 = \ln J_1 + \ln J_3$$

(II.24)

ou:

$$\ln \frac{I_4 \cdot I_2}{A_4 \cdot A_2} = \ln \frac{I_1 \times I_3}{A_3 \times A_1}$$

, (II.25)

finalmente:

$$I_4 = \frac{I_3 \cdot I_1}{I_2} \times \frac{A_4 A_2}{A_3 A_1}$$

(II.26)

Se as áreas forem feitas iguais, pode-se dizer que I4 dependerá somente das correntes Il, I3 e I4, valendo deste modo:

$$I_4 = \frac{I_3 I_1}{I_2}$$

(II.27)

A técnica descrita acima será a utilizada no projeto do circuito multiplicador proposto.

Baseando-nos então na referência (7), uma eficiente célula de multiplicação será descrita e analisada a seguir.

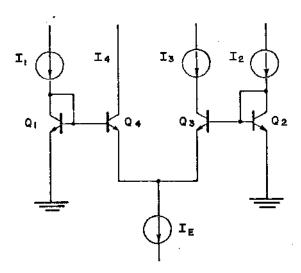

Fig. II.4 - Célula de multiplicação proposta por B. Gilbert Ref. (7)

A figura II.4 pode ser considerada como a de um amplificador diferencial, no qual as tensões de base são derivadas a partir de um par de junções que estão recebendo duas correntes (sinais de entrada) e que são da forma:

$$I_{b1} = x \cdot I_b \tag{II.28}$$

$$I_{b4} = (1 - x) I_{b}$$

(II.29)

onde:

x = indice de modulação da corrente de polarização  $I_{\rm b}$ , variando entre 0 < x < 1. Deste modo, desconsiderando os efeitos não ideais dos transistores tais como: diferença nas áreas dos emissores, beta finito, resistência ohmica , etc... e aplicando o 'princípio translinear, obtemos:

$$v_{T} \ln \frac{xI_{b}}{Is_{1}} - v_{T} \ln \frac{aI_{E}}{Is_{2}} - v_{T} \ln \frac{(1-x)^{-1}b}{Is_{3}} +$$

$$+ V_{T} \ln \frac{(1-a)^{T}E}{Is_{4}} = 0$$

(II.30)

A solução desta equação nos leva a concluir que a = x.

Assim, a corrente de saída será:

$$Ic2 = xIE$$

(II.31)

$$Ic3 = (1-x)IE ;$$

(II.32)

para  $x = \frac{Ibl}{I_b}$ , teremos:

$$Ic2 = \frac{Ib1}{Ib} . IE (II.33)$$

$$Ic3 = (1 - \frac{Ibl}{Ib}) IE$$

(II.34)

Teremos, portanto,  $Ic_2$  como o produto das correntes Ibl e IE. entre si e ainda pelo fator  $\frac{1}{Ib}$ . Para a corrente  $Ic_3$  teremos o complementar em relação a IE.

É interessante fazermos um análise qualitativa dos efeitos não ideais no desempenho do circuito sob análise.

### a) Efeito do descasamento de area

Pode-se definir uma variável "  $\gamma$  " onde:

$$\gamma = \frac{\text{Is2} \cdot \text{Is4}}{\text{Is1} \cdot \text{Is3}}$$

(II.35)

Reavaliando II.30 para se incluir γ , analizandoa de modo a se verificar o desvio em relação à curva ideal, ob teremos:

$$\frac{da}{dx} = \frac{\gamma}{\left[1 + (\gamma - 1) \ \overline{x}\right]^2}$$

(II.36)

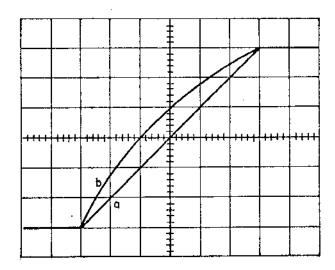

Deste modo, um descasamento de área pequeno tal que  $\gamma$  seja em torno de "1", causa uma variação linear dos pontos da curva de transferência, com os extremos x=0 e x=1 valendo y=1 respectivamente. Uma correção pode ser efetuada introduzindo uma tensão na malha translinear, como mostra a figura abaixo, retirada da referência citada.

- a curva restaurada por uma aplicação de ten são

- b distorção causada por um descasamento de área.

Figura II.5 Ref. (7)

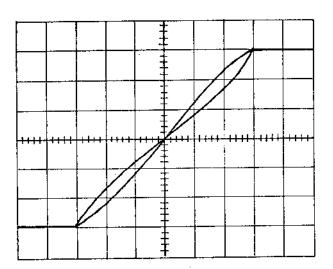

### b) Resistência ohmica

Vários efeitos parasitas são encontrados em um transistor, que podem ser colocados sob a forma de elementos resistivos, podendo também, todos esses elementos serem referenciados no emissor do transistor para efeito de análise.

Assim, incluindo-se esses elementos dentro do circuito da figura II.4, encontraremos, conforme mostrado na citada referência

$$V_{T}^{+} Log \{ \frac{x(1-a)}{(1-x)} \} = R_{i} \{ Alb (1-2x)-IE(1-2a) \}$$

(II.35)

onde:

A = relação de área entre os emissores dos pa res internos e externos.

As distorções causadas por este efeito na curva de transferência podem ser observadas na figura abaixo.

Distorções causadas pela resistência ohmica

Figura II.6 Ref. (7)

# c) Efeitos de beta finito

Na presença de beta finito, haverá uma modifica ção nas correntes relativas aos pares de junções externas.Uti

lizando agora estas modificações, a equação referente à curva de transferência se apresenta do seguinte modo:

$$\frac{\{xI_b - (1-\alpha) \text{ aIE }\} (1-a) \text{ IE}}{\{(1-x)I_b - (1-\alpha)(1-a) \text{ IE }\} \text{ aIE} } = 1$$

(II.37)

onde a = ganho de corrente de base comum.

Se considerarmos  $\beta$  em torno de 100 como  $\beta$  típico, o erro na curva de transferência será de 1%.

### d) Conclusão

Muitos outros efeitos parasitas podem ser analisa - dos aqui: resistência de saturação de coletor, efeitos térmicos, etc. Porém nos restringimos apenas a alguns,os quais julga - mos de maior impacto no projeto em questão.

Através da análise do circuito proposto por Gilbert, podemos perceber que este servirá como uma boa alternativa para a inicialização do projeto do circuito que se propõe neste trabalho, conseguindo com a estrutura al resentada, características que se enquadram dentro do desempenho exigido por nos.

# CAPITULO III

### PROJETO DO MULTIPLICADOR CHAVEADO

# III.1 Desenvolvimento de uma estrutura adequada

Pelos problemas apresentados nos capítulos anteriores, verifica-se facilmente que o circuito pretendido deverá possuir características bastante peculiares, que o colocam deslocado em relação às estruturas clássicas encontradas na litera tura até então.

Deste modo, terminamos por concluir que uma boa estrutura que englobará cada uma das células do dispositivo, pode ser representada pela figua III.l.

Circuito Multiplicador

Fig. III.1 - Diagrama em bloco do circuito multiplicador

Pode-se, deste modo, definir as funções de cada um dos blocos da forma que se segue:

### a) Célula Multiplicadora

Tem a finalidade de realizar a multiplicação propriamente dita. Recebe as duas correntes geradas na malha decodificadora e em sua saída deverá fornecer um sinal em corrente que seja proporcional ao produto das correntes recebidas.

### b) Célula de Chaveamento

Recebendo o sinal B<sub>1</sub> já convertido a níveis adequados <u>pe</u> la célula de interface, a célula de chaveamento tem a incumbência de chavear as correntes recebidas da célula multiplicadora. Este chaveamento definirá a polaridade de 'saída do sinal analógico.

#### c) Interface

O sinal B<sub>1</sub> chega ao circuito multiplicador em nível TTL.

Desta forma, torna-se necessário convertê-lo em níveis compatíveis com o nível de entrada da célula de chaveamento. A interface realiza esta função.

### d) Conversor I/V

O sinal será processado em corrente. Portanto, torna-se 'necessário convertê-lo em nível de tensão. Esta célula preenche esta necessidade.

# e) Célula de Polarização

Tem a finalidade de estabelecer os níveis de tensão neces sários para o funcionamento do dispositivo.

### f) Célula de saída

Fornece a baixa impedância exigida na saída do circuito. Como o multiplicador em projeto possui uma finalidade específica, neste dispositivo esta célula não será necessária, visto que o sinal de saída do dispositivo será ainda manipulado por um filtro passa-baixas.

Logo, o sinal não necessitará de uma potência que venha exigir a inclusão deste estágio.

# III.2 Configurações desenvolvidas

O projeto de um circuito é uma criação extremamente dinâmica, onde uma idéia que solucionará um problema surgido em um determinado instante pode ser rapidamente suplantada ' por uma outra, para resolver o mesmo problema em uma época posterior.

Deste modo, as configurações foram se sucedendo, visando sempre solucionar os problemas surgidas nos circuitos anteriores, assim como, otimizar em termos de circuitos as estruturas realizadas até então.

Neste tópico apresentamos uma breve retrospectiva 'dos circuitos elaborados, apresentando de uma forma rápida os problemas que nos levaram a alterá-los, bem como as solu-

ções propostas, até chegarmos ao dispositivo final.

# III.2.1 Multiplicador chaveado - versão 01

Sendo esta versão a primeira tentativa do circuito em projeto, foi necessário definirmos a configuração de cada uma das células. Assim, passaremos a descrever cada célula em separado, terminando por apresentar o esquema final da versão 01, assim como os problemas verificados.

# - Célula Multiplicadora

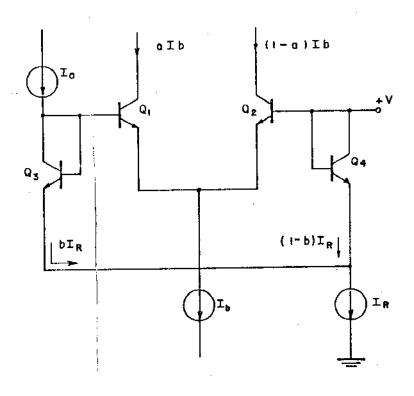

Esta célula foi baseada totalmente na estrutura proposta por Gilbert (7), reproduzida na figura III.2, e explicada com maiores detalhes no item II.4

Fig. III.2 - Célula Multiplicadora proposta

onde

$$a = b = \frac{Ia}{IR}$$

(III.1)

Baseados no princípio translinear, podemos afirmar que a equação III.l é verdadeira.

Sendo Ia e Ib as correntes a serem multiplica - das, obteremos diretamente duas correntes:

$$I_1 = alb$$

(III.2)

$$I_2 = (1-a) Ib \qquad (III.3)$$

ou ainda

$$I_1 = \frac{Ia \cdot Ib}{IB}$$

(III.4)

$$I_2 = (IR - Ia) \cdot \frac{Ib}{IR}$$

(III.5)

A polarização "+V" permite que flua uma corrente por  $Q_4$ , quando esta for exigida; não deixando que ocorra corte deste transistor.

As correntes Ia e Ib, na malha decodificadora são geradas através do coletor de um transistor PNP com a base em terra.

Assim, torna-se necessário que a estrutura '

proposta seja referenciada em um potencial abaixo da terra

(negativo).

A corrente IR, também gerada na malha decodificadora ( e não referida até aqui por não se tratar de sinal) juntamente com Ib, são refletidas para os emissores de  $\mathbb{Q}_3$   $\mathbb{Q}_4$  e  $\mathbb{Q}_1\mathbb{Q}_2$  através de espelhos de correntes, conseguindo deste modo uma alta estabilidade com a temperatura.

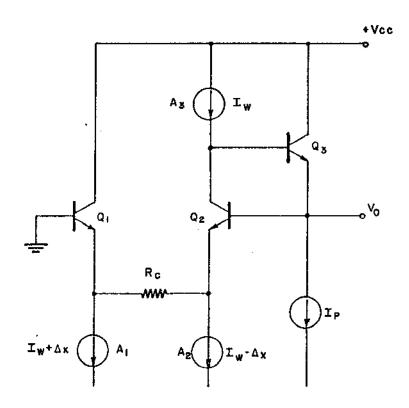

# - Conversor I/V

Baseando-se na célula proposta por Blauschild

(18) o conversor se apresenta do modo apresentado na figura

III.3

Fig. III.3 - Conversor I/V proposto

As correntes IW+  $\Delta x$  e IW -  $\Delta x$  sendo definidas pela célula multiplicadora atuam nos emissores de  $Q_1$  e  $Q_2$  respectivamente. A fonte de corrente  $A_3$  atua no coletor de

$Q_2$ , garantindo desta forma que "IW" flua por este transistor. Como por  $A_2$  flui somente IW -  $\Delta x$ , o excesso de corrente en - tre a corrente fornecida por  $Q_2$  (IW) e a exigida por  $A_2$  (IW-  $\Delta x$ ), passará por Rc convertendo-se em tensão. A fonte  $A_1$  recebendo  $\Delta x$ , exige somente IW do transistor  $Q_1$ .

Como as correntes em  $\mathbb{Q}_1$  e  $\mathbb{Q}_2$  são iguais, ter-se-á o mesmo valor de tensão base-emissor em  $\mathbb{Q}_1$  e  $\mathbb{Q}_2$ . Deste modo, podemos concluir que o valor de tensão sobre Rc será o valor de  $\mathbb{V}_0$ .

### - Célula de chaveamento e interface

Baseados nas características do conversor I/V escolhido, podemos notar que uma inversão nas correntes das fontes  $A_1$  e  $A_2$  na figura III.3 ocasiona uma inversão de polaridade na saída do sinal  $V_0$ . Ou seja, se fizermos com que  $A_2$  seja conectado no emissor de  $Q_1$  e  $A_1$  no emissor de  $Q_2$ , o excesso de corrente fluirá no sentido de  $Q_1$  para  $Q_2$ , inverten do portanto a polaridade do sinal de saída.

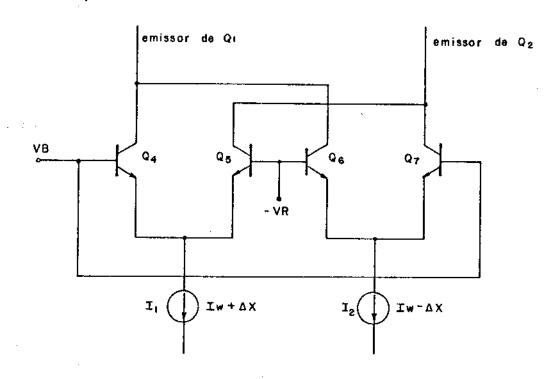

Para realizar essa inversão de fontes, esco - lhemos uma estrutura de topologia bastante conhecida conforme mostra a figura III.4

Fig. III.4 - Circuito de Chaveamento proposto

Quando o sinal  $V_B$  for suficientemente grande para conduzir  $Q_4$  e  $Q_7$ , as correntes  $I_1$  e  $I_2$  irão para os emissores de  $Q_1$  e  $Q_2$  respectivamente, no conversor I/V, já que  $Q_5$  e  $Q_6$  estarão cortados. Quando  $V_R$  for maior do que " $V_B$ " o suficiente para cortar  $Q_4$  e  $Q_7$  e conduzir  $Q_5$  e  $Q_6$ , a inversão ocorrerá com a corrente  $I_1$  indo para o emissor de  $Q_2$  e a corrente  $I_2$  para o emissor de  $Q_1$ , invertendo assim a polaridade do sinal de saída.

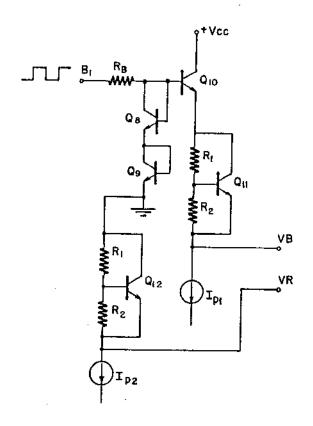

Torna-se necessário então compatibilizar o sinal  ${}^{'}V_{B}{}^{"}$  com o "bit" de polaridade "B<sub>1</sub>" recebido pelo dispositivo. Para que isto seja feito, foi desenvolvida a interface 'mostrada na figura III.5.

Fig. III.5 - Circuito de interface proposto

Caso o sinal  $B_1$  seja "1" ( $\Xi$  + 3 V) teremos o transistor  $Q_{10}$  conduzindo e no seu emissor haverá uma ten - são de aproximadamente Veb em relação à terra. Assim a ten são " $V_B$ " será:

$$V_B = V_{BE} + V_R$$

(III.5)

Sendo  $V_R$  a tensão gerada a partir de multiplicadores de  $V_{BE}$ , cada um deles composto por um transistor ' ( $Q_{11}$  e  $Q_{12}$ ) e por resistores  $R_1$  e  $R_2$ , idênticos entre si. Caso o sinal  $R_1$  seja zero (~ OV) teremos os

transistores  $Q_8$  e  $Q_9$  cortados e no emissor de  $Q_{10}$  haverá uma tensão de aproximadamente -  $V_{\rm BE}$  em relação à terra. Assim a tensão VB será:

$$v_B = -v_{BE} + v_R$$

(III.6)

Pode-se perceber que a tensão  $V_{\rm B}$  será  $\pm$  VBE em relação a  $V_{\rm R}$ , sendo suficiente para que o chaveamento se realize.

O resistor RB serve somente como limitador de corrente.

Os demais circuitos exigidos no dispositivo 'multiplicador chaveado serão discutidos na configuração final da versão 01.

A configuração final da versão 01, se apresenta conforme mostrado na figura III.6.

Na estrutura apresentada, pode-se distinguir 'claramente cada uma das células discutidas até então.

Deste modo, passaremos a tratar das funções dos transistores que surgem pela primeira vez.

Os transistores  $Q_{11}$ ,  $Q_{12}$ ,  $Q_{13}$ ,  $Q_{14}$ ,  $Q_{18}$ ,  $Q_{19}$ ,  $Q_{20}$ ,  $Q_{22}$  formam os espelhos com a incumbência de refletir a corrente Ib para a célula multiplicadora e para a célula conversora.

Os transistores  $Q_{15}$ ,  $Q_{16}$ ,  $Q_{17}$  formam o espetitho de corrente referente a  $T_{\rm R}$  e à polarização do conversor.

Fig. III.6 - Esquema da versão 01 do circuito multiplicador

O transistor  $Q_{13}$  fornece a corrente necessária, de modo que tenhamos nos emissores de  $Q_3$  e  $Q_4$  "I +  $\Delta x$ "e não somente  $\Delta x$  conforme mostra a equação III.2.

Como o conversor trabalha com "I +  $\Delta x$ " este transistor foi incluído.

0 transistor  $\mathbf{Q}_{17}$  serve para a compensação de  $\alpha$  da corrente acima mencionada.

# - Problema verificado com a versão 01

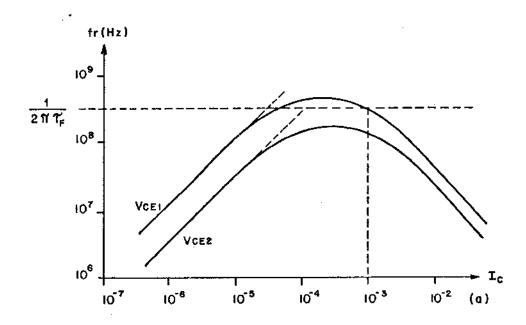

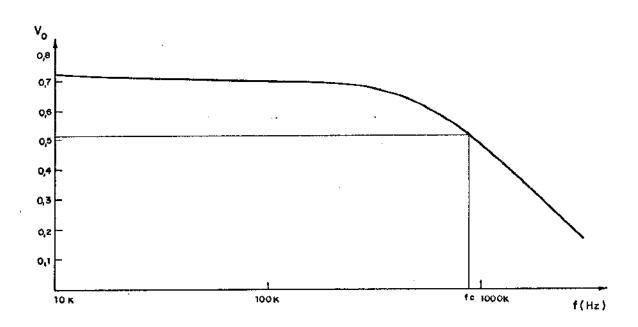

O principal problema surgido com esta versão do circuito ocorreu no que se refere à sua resposta em fre quência.

Como os níveis de correntes utilizados são muito baixos, Ia = 32  $\mu$ A e Ib = 64  $\mu$ A, a frequência de corte dos transistores utilizados caiu demasiadamente, não 'permitindo assim que o circuito apresentasse a frequência exigida. Este efeito pode ser verificado utilizando para isto o modelo utilizado no programa SPICE 2. Assim:

$$f_{T} = \frac{1}{2 \pi \text{ Tf (efetivo)}}$$

(III.5)

sendo:

$$T_{f(efetivo)} = \tau_{f} Q_{b} + \frac{V_{T}}{I_{C}} \left\{ \frac{cjeo}{\left[1 + \frac{V_{BE}}{Pe}\right]} \right\}^{me} \frac{Cjco}{\left[1 - \frac{V_{BC}}{Pc}\right]^{mc}}$$

(III.6)

### Onde:

$T_{\rm f}$  = tempo de trânsito direto

Q<sub>b</sub> = carga armazenada na base

Cjeo = capacitância de junção de emissor com polarização zero

Cjco = capacitância de junção de coletor com polarização zero

V<sub>BE</sub> = tensão entre base-emissor

V<sub>DC</sub> = tensão entre base-coletor

Pe = potencial da junção de emissor

Pc = potencial da junção de coletor

me = coeficiente de junção de emissor

mc = coeficiente de junção de coletor

Assim, um aumento em Ic permitirá maiores respostas de frequência, como pode ser verificado pelas equa ções acima e pela figura III.7 abaixo.

Fig. III.7 - Frequência de corte do transistor em função da corrente de coletor - Ref. (19)

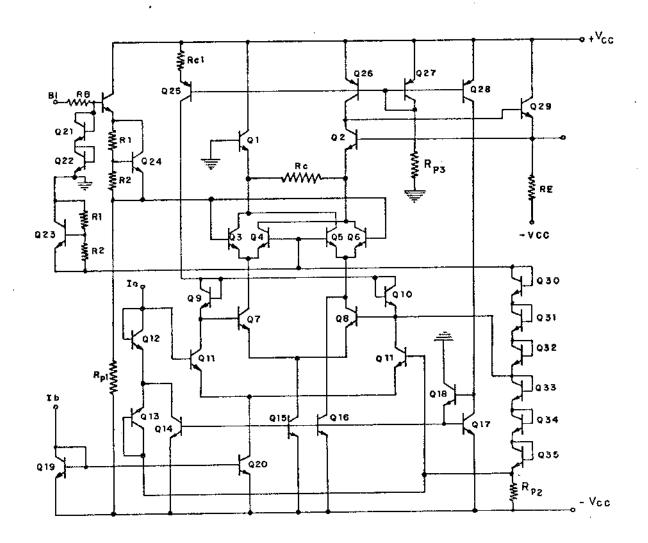

# III.2.2 Multiplicador chaveado - versão 02

Basicamente, a modificação introduzida visou um aumento no valor da corrente multiplicada, de modo a aumentar o f<sub>T</sub> dos transistores. Assim, a primeira idéia surgida, nos levou a uma alteração na célula multiplicadora, determinando assim, uma nova configuração do circuito com esta topologia apresentada na figura III.8.

Fig. III.8 - Esquema da versão 02 do circuito multiplicador

Como pode ser verificado a única célula que <u>a</u> presentou modificação, foi a relacionada à multiplicação. Portanto, passaremos a analisá-la separadamente para melhor esclarecimento.

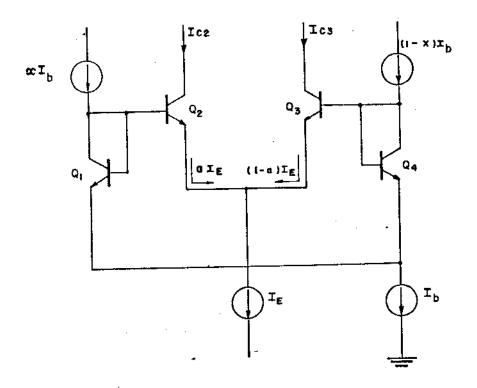

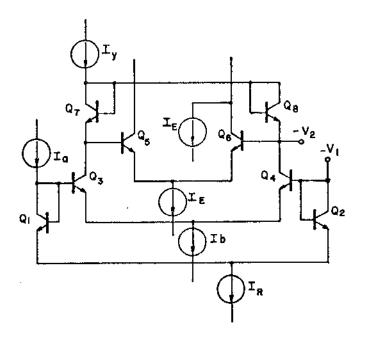

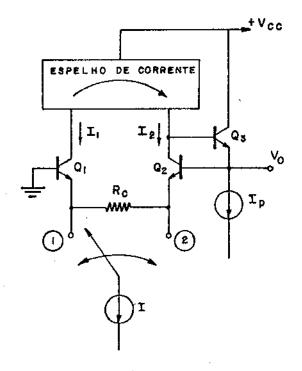

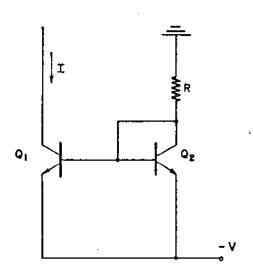

Uma boa forma de se entender o princípio de funciónamento da célula multiplicadora, é através da análise da sua estrutura simplificada apresentada abaixo.

Fig. III.9 - Célula multiplicadora da versão 02 - esquema simplificado

A corrente la fluindo através de  $\mathbf{Q}_1$  , definirá no coletor de  $\mathbf{Q}_3$  uma corrente:

onde

$$Ic_3 = a \cdot Ib$$

$$a = \frac{Ia}{I_R}$$

No coletor de  $Q_4$ , teriamos:

$$Ic_4 = (1-a) Ib$$

(III.8)

Estas duas correntes, quando passarem por  $\,^{Q}_{7}\,^{e}$  e  $\,^{Q}_{8}$ , definirão nos coletores de  $\,^{Q}_{5}$  e  $\,^{Q}_{6}$  os seguintes valores

de correntes:

$$Ic_5 = (1 - y) I_E$$

(III.9)

$$Ic_6 = Y \cdot I_E$$

(III.10)

onde:  $y = \frac{a.Ib}{I_y}$

Deste modo teremos:

$$Ic_5 = (1 - \frac{Ia \cdot Ib}{I_R \cdot I_y}) \cdot IE$$

(III.11)

$$Ic_6 = \frac{Ia \ Ib}{I_R \cdot I_y}$$

. IE (III.12)

Para se obter no coletor de  $Q_6$ ,  $1+\Delta x$ , necessário, devido à configuração adotada do conversor I/V, deve-se ainda, somar uma corrente  $I_E$  à corrente de  $Ic_6$ .

Caso fizermos com que o valor de  $I_E$  seja muito maior que IR e Iy, o fator multiplicativo  $\frac{I_E}{I_R.\,I_y}$  da equa - ção III.ll e III.l2 será grande o suficiente para aumentar o valor de  $f_p$  dos transistores.

# - Problemas verificados na versão 02

Vários foram os problemas verificados nesta 'versão, o que nos levou a modificar a sua estrutura. Podemos desta forma, citar:

- Geração das correntes I $_{

m Y}$  e I $_{

m E}$

- Aumento de complexidade de Lay-Out

- Problemas de compensação de  $\alpha$

- Problemas devido a β finito

Dentre todos os citados, o mais sério é o que diz respeito a  $\beta$  finito do transistor. Sem dúvida, a modificação da estrutura do circuito da versão 01, tinha como objetivo um aumento no nível da corrente multiplicada. Isto só é possível na versão 02, através do aumento do valor de IE. Como o nível das correntes em  $Q_7$  e  $Q_8$  é muito baixo ( 64  $\mu A$  quando a = 1), a corrente na base de  $Q_5$  para altos valores de IE, seria em ordem de grandeza, altamente significativa. Assim a corrente mínima que fluirã pelo transistor  $Q_7$ , será a corrente injetada na base de  $Q_5$ . Devido a este fato , sempre uma corrente atravessará o transistor  $Q_7$ , e pelo principio translinear, um fator relacionado a esta aparecerá multiplicando a corrente  $I_E$ .

Assim, surgirá um "off set" de tensão na saída do dispositivo, irremovível, com esta configuração de multiplicador.

# III.2 3 Multiplicador chaveado - versão 03

Uma nova forma de se aumentar o valor de corrente multiplicada, de modo a subir a frequência de corte do

transistor e consequentemente a frequência de corte de todo

o circuito tem de ser formulada. Assim, uma nova topologia

foi desenvolvida e esta estrutura apresentada na figura

III.10, sendo feita a seguir uma breve análise de seus problemas; uma discussão envolvendo maiores detalhes é encontr<u>a</u> da na referência (20)

Fig. III.10 - Esquema da versão 03 do circuito multipl $\underline{i}$  cador

Pode-se notar pela figura acima que não só a célula multiplicadora sofreu modificação, mas também o conversor I/V se alterou. A seguir, passaremos a avaliar e discutir ca da uma das modificações apresentadas.

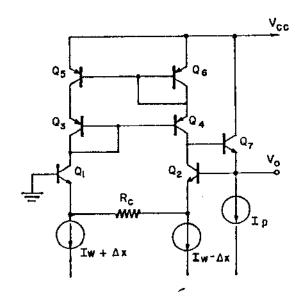

### Conversor I/V

Esta nova topologia do conversor I/V, mostrada em detalhe na figura III.ll,tornou possível a eliminação de transistores que tinham por objetivo manter uma corrente constante no coletor do transistor  $Q_2$  (ver figura III.3), diminuindo, com isto, não só a complexidade final do circuito e de seu "Lay out", mas também os erros inerentes surgidos devido aos espelhos de correntes necessários na operação da geração da fonte IW (Fig. III.3). Estes erros são os responsáveis pela 'diferença no valor da corrente nos coletores de  $Q_1$  e  $Q_2$ , produzindo com isto um desbalanceamento nas tensões base-emissor dos transistores e gerando um "off set" de tensão na saída do dispositivo.

A figura III.ll apresenta a configuração na sua forma final, e utiliza um espelho de corrente com quatro transistores. Devido a esta montagem, conseguiu-se eliminar o efeito do  $\beta$  dos transistores PNPs laterais no conversor.

Fig. III.11 - Nova topologia do conversor I/V

A configuração acima mostrada soluciona este problema, com a vantagem da simplificação da estrutura.

Um modo de visualizarmos a validade da afirmação acima, é equacionarmos o funcionamento da célula proposta.

Assim temos:

$$no 1 = IW + \Delta X = I_2 + I_1$$

(III.13)

$$n\tilde{o} 2 = IW - \Delta x = I_3 - I_1$$

(III.14)

onde:

I<sub>1</sub> = corrente que atravessa o resistor Rc;

$I_2$  = corrente que flui no transistor  $Q_1$ ;

$I_3$  = corrente que flui no transistor  $Q_2$ .

O espelho nos garante que  $I_2 = I_3$  (III.15)

Somando-se III.13 e III.14 temos:

$$2IW = I_2 + I_3$$

(III.16)

baseado em III.15, vemos que  $IW = I_3$  (III.17)

Ou seja, podemos garantir que as correntes nos coletores de  $Q_1$  e  $Q_2$  são iguais entre si e também igual a IW. Assim, temos que em Rc passa somente  $\Delta x$ .

# Célula Multiplicadora

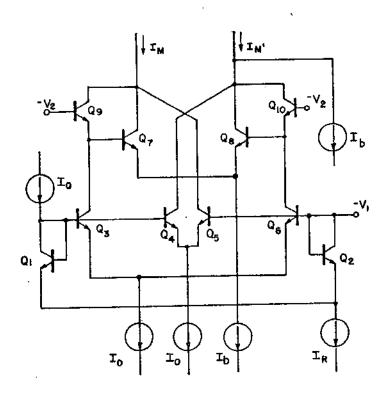

Uma representação mais detalhada é mostrada na figura III.12.

Fig. III.12 - Célula multiplicadora da versão 03 ( esquema simplificado )

A corrente Ia, entrando no coletor de  $Q_1$ , aparece rá no emissor de  $Q_3$  e  $Q_4$ , como a razão entre Ia e a corrente IR multiplicada por Io. O mesmo raciocínio é válido para os transistores  $Q_1$ ,  $Q_2$ ,  $Q_5$  e  $Q_6$ .

A corrente nos coletores de Q $_5$  e Q $_6$  serã o compl $\underline{e}$  mento em relação à Io.

Deste modo:

$$Ic_3 = Ic_4 = \frac{Ia}{I_R}$$

. Io (III.18)

$$Ic_5 = Ic_6 = (1 - \frac{Ia}{IR})$$

. Io (III.19)

chamando  $x = \frac{Ia}{I_R}$ , teremos:

$$Ic_3 = Ic_4 = xIo (III.20)$$

$$Ic_5 = Ic_6 = (1-x)Io$$

(III.21)

Estas correntes aparecerão nos emissores de Q $_7$ , Q $_8$ , Q $_9$  e Q $_{10}$ .

Com raciocínio análogo à primeira multiplicação, podemos verificar que no emissor de  $Q_8$  surgirá o produto entre a relação "x.Io" definida anteriormente em  $I_{c3}$ ,  $I_{c4}$ , e Ib.

No emissor de  $\mathbb{Q}_7$  aparecerá o valor complementar da corrente de  $\mathbb{I}_{E8}$  em relação à Ib. Equacionando todas as correntes, teremos na saída desta célula os seguintes valores:

$$I_{M} = -xIb + Io + Ib \qquad (III.22)$$

$$I_{M}^{\dagger} = + xIb + Io + Ib$$

(III.23)

Chamando:

$$\Delta x = xIb$$

(III.24)

$$I = I_O + I_D \qquad (III.25)$$

teremos:

$$I_{M} = I - \Delta x \qquad (III.26)$$

$$I_{M}^{t} = I + \Delta x \qquad (III.27)$$

Que nos permitirá convertê-las em tensão confo $\underline{r}$  me o esquema de conversor proposto.

Podemos notar que o problema surgido na versão 02, se soluciona com esta nova configuração sugerida, já que o erro devido a beta finito, tendo em mente a aplicação a que se destina, restringe a apenas 0,8%, conforme mostrado' na referência citada.

Porém, apesar da menor complexidade do novo conversor I/V proposto, o circuito em sua totalidade tornou-se muito mais complexo.

Assim, uma nova topologia foi desenvolvida de modo a simplificar a existente até então.

# III.2.4 Multiplicador chaveado - versão 04

Este circuito, pela simplicidade obtida, foi con siderado como sendo a configuração otimizada para o projeto em questão e assim, tomada como a versão final do circuito' proposto.

No item seguinte passaremos a fazer uma análise detalhada desta estrutura, bem como de seus problemas, e das soluções sugeridas.

# III.3 Multiplicador chaveado - Versão Final

### III.3.1 Modificações introduzidas

Um novo enfoque é dado a esta versão do dispositivo. Até o presente instante, houve a necessidade de se conseguir correntes diferenciais (IW + Δx e IW - Δ x) na célula multiplicadora, visto que o conversor I/V proposto as sim exigia. Uma modificação é sugerida na estrutura do conversor I/V de modo que possa trabalhar apenas com uma corrente não diferencial.

Esta pequena modificação, porém de fundamen tal importância, é a responsável pelas alterações que leva - ram a simplificações que permitiram a diminuição da complexidade do dispositivo.

### - Conversor I/V

O conversor I/V proposto, é idêntido na sua topo logia ao conversor da figura III.9.

A modificação mencionada, se relaciona apenas a forma de se utilizar o conversor.

Fig. III.13 - Novo conceito de utilização do conversor proposto

Como se pode ver, a estrutura do conversor é idêntica à estrutura apresentada na figura III.ll. Somente que neste esquema a corrente entrará ou pelo nó "l", ou pelo nó "2". O nó pelo qual entra a corrente, define a polaridade de saída do sinal.

Para o equacionamento do funcionamento do conversor, conectaremos a fonte de corrente "I" ao nó "1". Assim 'teremos:

$$I = I_1 + I_2 \tag{III.28}$$

onde:

I = corrente gerada na célula multiplicadora

$I_1$  = corrente que flui por  $Q_1$

$I_2$  = corrente que flui por  $Q_2$

O espelho nos garante que:

$$I_2 = I_1 \tag{III.29}$$

Logo:

$$I = 2I_2 \tag{III.30}$$

$$I_2 = I_1 = \frac{I}{2} \tag{III.31}$$

O mesmo raciocínio é válido para a corrente I conectada ao nó "2".

Pode-se concluir portanto que a corrente que 'passará por "Rc" será proporcional à corrente multiplicada, ou seja a corrente valerá  $\frac{\mathrm{I}}{2}$ — e defirá uma tensão de saída sendo:

$$vo = \frac{I \cdot Rc}{2} \quad (III.32)$$

# b) <u>Célula Multiplicadora</u>

Não possuindo mais a incumbência de gerar correntes diferenciais para o conversor I/V, modificou-se novamente a estrutura desta célula, tendo sua configuração mostrada na figura abaixo.

Fig. III.14 - Celula multiplicadora do circuito proposto

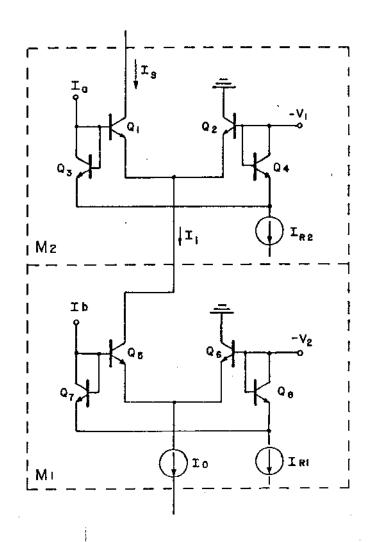

Esta célula multiplicadora é composta por dois multiplicadores,  $M_1$  e  $M_2$ , em cascata, e que obedecem o principio translinear clássico.

A corrente Io, sendo feita de valor elevado pos sibilita que se desloque ovalor final da corrente multiplicada, quando os índices de modulação forem iguais a "l", para um valor tão grande quanto se queira.

Como este dispositivo é destinado a uma função es pecífica, e sabendo-se que apenas no primeiro segmento do 'MCP os valores chegarão ao nível inferior (Ia = 1 μA), visto que do segundo ao sétimo segmento a corrente Ia variará en tre 16 μA e 32 μA, no global,a corrente multiplicada so frerá um aumento considerável, deslocando assim a frequência de corte dos transistores e aumentando a resposta em frequência do dispositivo.

Deste modo a corrente I2 será dada por:

$$I_1 = \frac{Ib \cdot Io}{IR_1}$$

(III.33)

$$r_{S} = \frac{\text{Ia. Ib. Io}}{\text{IR}_{1} \cdot \text{IR}_{2}}$$

(III.34)

Assim podemos dizer que a corrente de saída da célula multiplicadora será:

$$I_{S} = K_{1} \cdot Ialb \qquad (III.35)$$

Para:

$$K_{1} = \frac{Io}{IR_{1} \cdot IR_{2}}$$

(III.36)

onde:

Io = corrente de referência de valor elevado que será multiplicada por Ib e Ia IR<sub>1</sub> = corrente de referência do multiplicador "l"

IR<sub>2</sub> = corrente de referência do multiplicador "2"

As correntes  $\ensuremath{\text{IR}}_1$ ,  $\ensuremath{\text{IR}}_2$  e Io são geradas na malha decodificadora.

## III.3.2 Problemas verificados na célula multiplicadora

A definição dos valores de  $IR_1$ ,  $IR_2$  se tornaram bastante simples, visto que desejamos que o transistor trabalhe com a maior faixa dinâmica possível. Deste modo fizemos com que  $IR_1$  fosse igual ao valor máximo de Ia, e  $IR_2$  igual ao máximo Ib.

Desta forma fazemos com que os indices de modulação variassem entre "zero e um".

A escolha de Io porém não foi feita de um modo tão simples. Para definirmos o seu valor levamos em consideração' os níveis mínimos de corrente no espelho, composto por transistores PNPs laterais, bem como o efeito das resistências parasitas referenciadas no emissor dos transistores (ver item 'II.4.b), ambos os efeitos produzindo uma não linearidade indesejada.

Assim, fizemos com que Io valesse 1024  $\mu A$  que é um valor múltiplo de 64 (valor original de Ib). Desta forma, para valores máximos de saída da célula multiplicadora teremos '512  $\mu A$  fluindo através dos transistores PNPs e 0,25  $\mu A$  para o caso mínimo.

Convém lembrarmos que o valor mínimo somente ocor rerá no primeiro degrau do primeiro segmento, onde o erro 'permitido é máximo (50%). O problema da não linearidade devido a resistência do emissor será discutida tendo como base as curvas obtidas, no próximo capítulo.

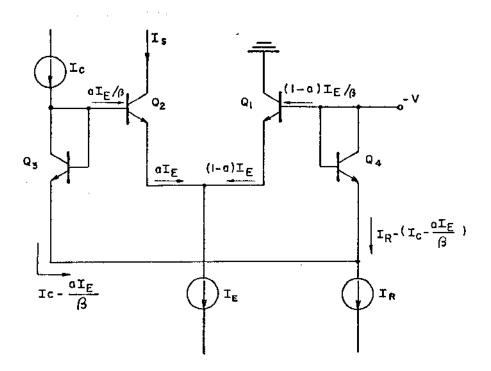

Com os valores de  $IR_1$ ,  $IR_2$  e Io definidos, pode - mos identificar o problema surgido devido a  $\beta$  finito do transstator. Baseado na célula multiplicadora, podemos escrever:

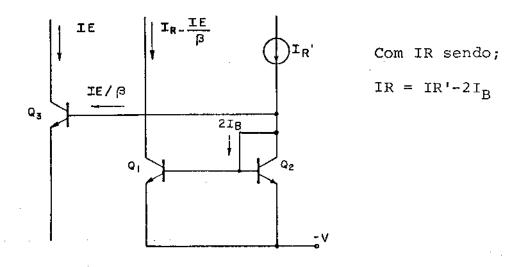

Fig. III.15 - Célula multiplicadora sob análise

A corrente na base de Q2 valerá

$$IB_2 = \frac{aI_E}{\beta}$$

(III.37)

Onde:

a = o valor do índice de modulação do esquema sob análise;

$\mathbf{I}_{\mathrm{E}}$  = corrente que será multiplicada, e que atua nos emissores do par interno de transistores;

Ic = corrente a ser multiplicada, que atua nos pa res externos de transistores, e define junta mente com IR o valor do índice de modulação;

I<sub>S</sub> = corrente multiplicada na saída da célula.

A corrente no emissor de Q<sub>1</sub>, será dada por:

$$I_{Q3} = Ic - \frac{aI_E}{\beta}$$

(III.38)

$$(Ic - \frac{aI_E}{\beta}) \cdot (1-a)I_E = \left[IR - (Ic - \frac{aI_E}{\beta})\right]$$

. ale (III.39)

de onde se tira que:

$$a = \frac{Ic}{IR + \frac{I_E}{\beta}}$$

(III.40)

Se tomarmos o valor de "a" ideal, teríamos, da equação III.1:

$$a = \frac{Ia}{I_R}$$

(III.1); em relação a figura III.15, poderia reescrever este valor pada

$$a = \frac{Ic}{I_R}$$

(III.41)

Devido a III.40 e III.39, o erro no índice de modulação será dado por:

$$\varepsilon = \frac{1}{1 + \Delta}$$

(III.42)

onde

$$\Delta = \frac{\beta I_R}{I_E}$$

(III.43)

Analisando separadamente para cada um dos multiplicadores cascateados da figura III.12 temos a análise que se segue.

#### a) Multiplicador Ml

O valor da corrente Io é constante, logo o erro será apenas um deslocamento para menos no valor máximo alcançado.

Assim, para  $I_E = 1024~\mu A$  ,  $I_R = 64~\mu A$  e considerando  $\beta$  como sendo igual a 100, temos o erro igual a 13,79% do valor máximo.

# b) Multiplicador M2

Neste caso, teremos a corrente " $I_E$ " variando entre zero e 882,75  $\mu A$  (86,2% de 1024) e  $I_R$  valendo 32  $\mu A$ .

Porém, o erro agora é variável e podemos escreve-lo da seguinte forma:

$$\varepsilon = \frac{1}{1 + \frac{1}{\kappa^* \times}}$$

(III.44)

Sendo x feito variar entre 0 e 1 conforme o índice de modulação.

Sendo K'x uma equação de reta com K'valendo:

$$K' = \frac{I_E}{\beta I_R}$$

(III.45)

Para  $\beta$  ,  $\boldsymbol{I}_{R}$  e  $\boldsymbol{I}_{E}$  constantes. `

A corrente de saída da célula multiplicadora será então função deste erro, visto que o valor do índice de modu lação de "M2" é diretamente proporcional a este.

Assim, podemos escrever que a corrente de saída será dada por

$$I_S = I_{So} - \epsilon \cdot I_{So}$$

(III.46)

onde:

I = corrente de saída desconsiderando βfinito

$\varepsilon$  = erro devido a  $\beta$  finito

Assim:

$$I_S = I_{SO} (1 - \epsilon)$$

(III.47)

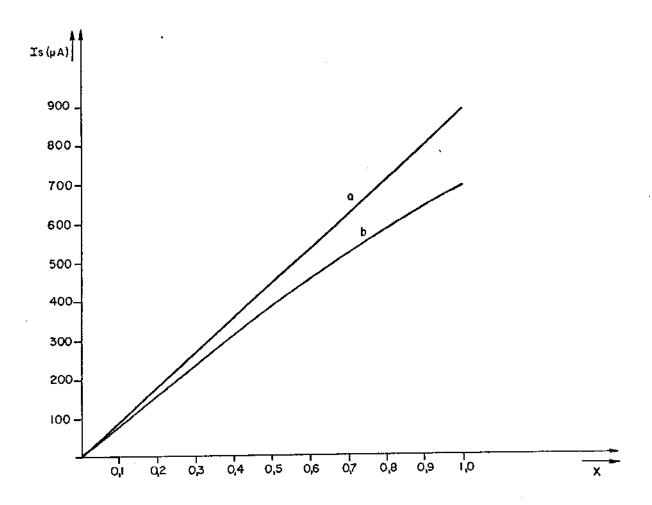

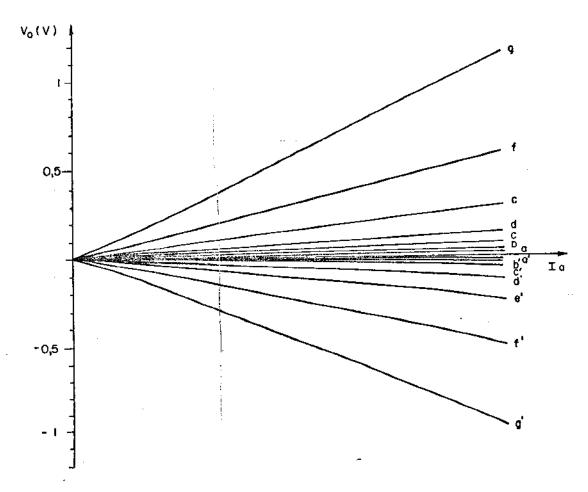

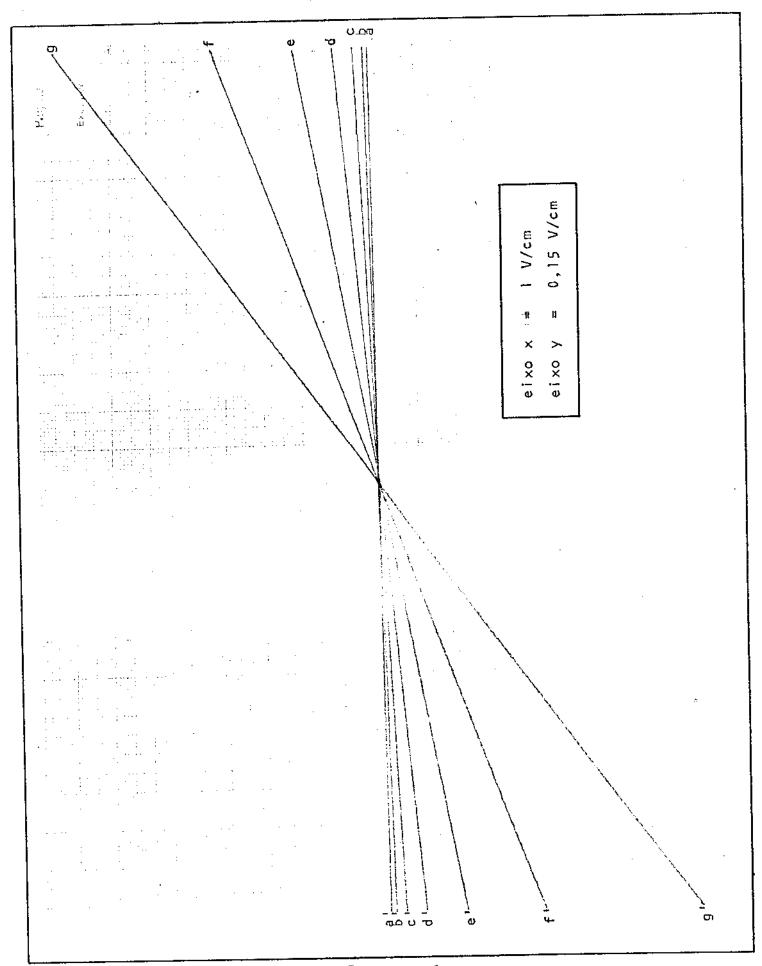

Assim, plotando o valor de  $I_S$  em função do índice de modulação, com este índice variando linearmente, teremos:

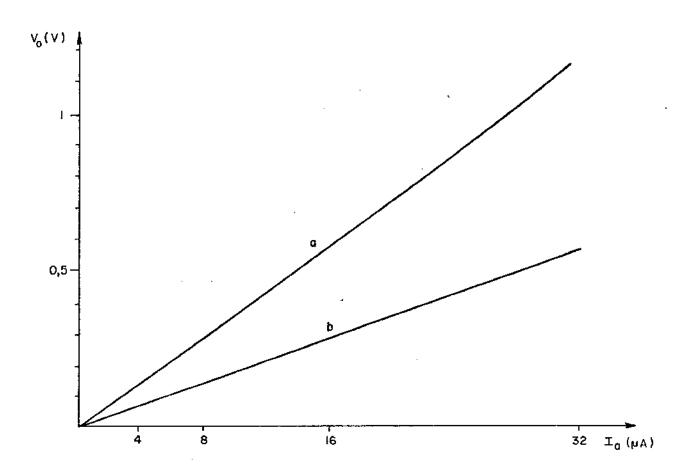

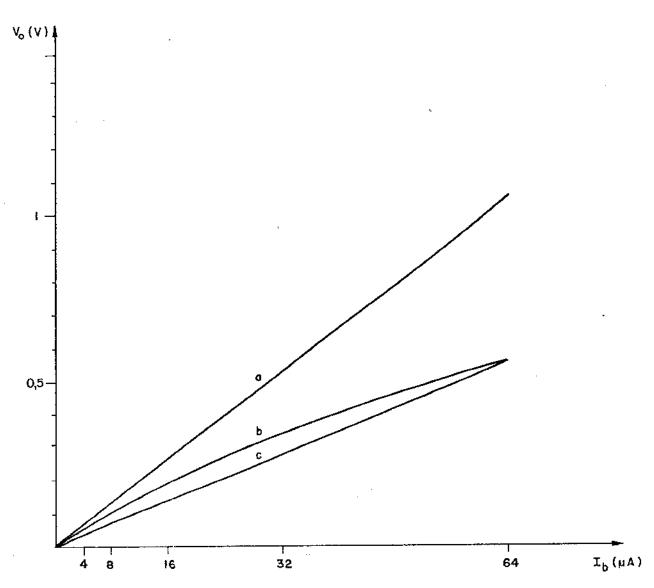

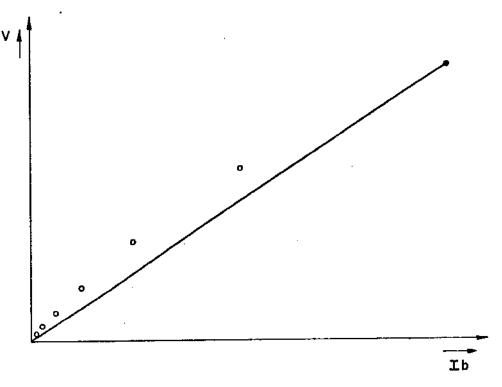

- a = Curva ideal da corrente de saída.

- b = Curva considerando o efeito de  $\beta$  finito.

Fig. III.16 - Curvas de saída em função do indice de modu lação

Como pode ser verificado pela figura III.37 além de uma diminuição no valor da corrente de saída, haverá ainda uma ' não linearidade proveniente da variação do sinal. Baseado no exposto acima, foi necessário o desenvolvimento de uma forma de compensar o efeito apresentado.

Analisando a equação III.39 e comparando com III.40, verificamos que o termo que introduz o erro no indi de modulação vale  $\frac{I_E}{\beta}$ . Então, témos que:

$$a = \frac{IC}{IR + \frac{IE}{\beta}}, \qquad (III.40)$$

quando o valor ideal seria

$$a = \frac{Ic}{IR}$$

(III.41)

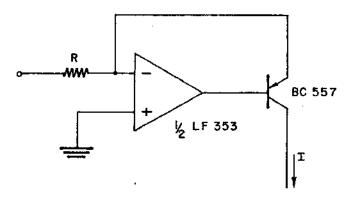

Baseando-se no exposto acima, verificou-se que o circuito mostrado abaixo realiza de forma eficiente uma compensação deste efeito.

Fig. III.17 - Circuito de compensação de β proposto

Ou seja, se subtrairmos o valor de  $\frac{\mathrm{Ib}}{\beta}$  da corrente de referência recebida da malha decodificadora, a corrente que servirá como referência para os pares externos de transistores da figura III.15 será menor do que o valor de  $\mathrm{I}_R$ . Quando o valor de  $\mathrm{I}_E$  variar, a referência também variará mantendo a razão entre  $\mathrm{Ic}$  e  $\mathrm{I}_R$  constante.

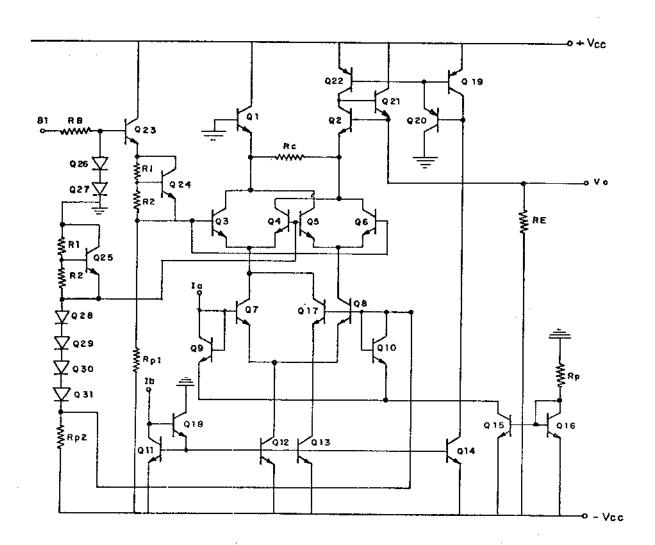

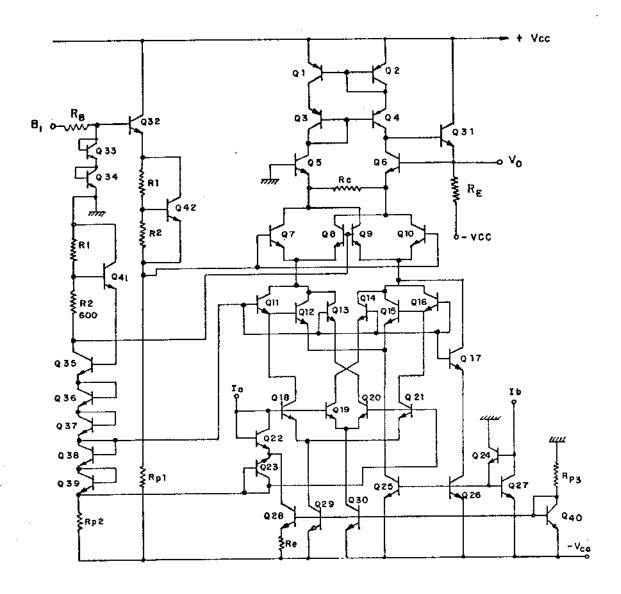

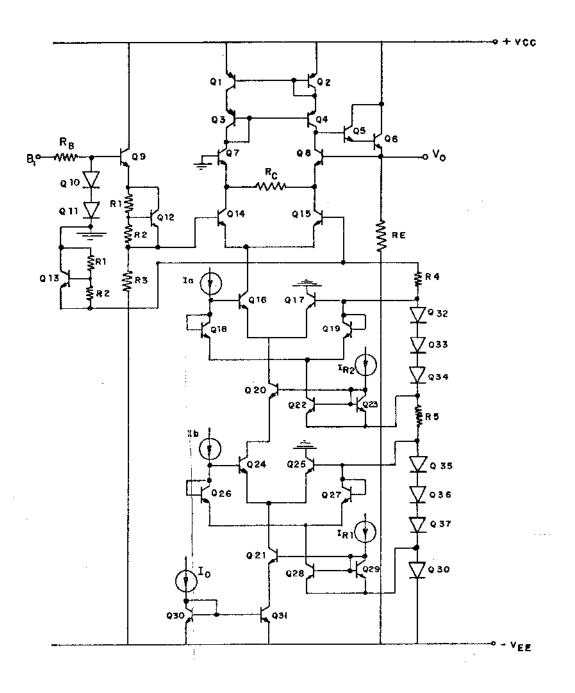

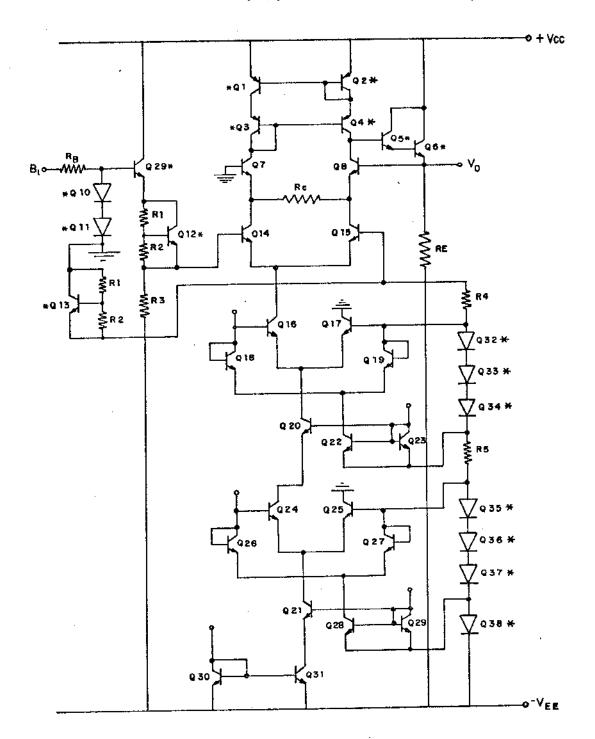

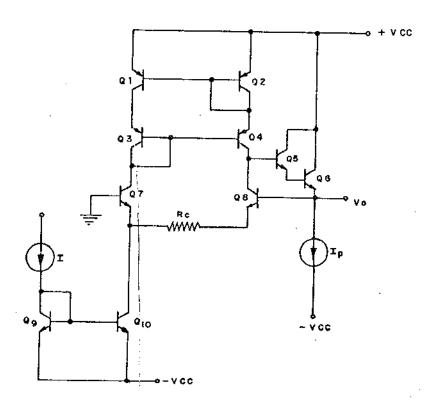

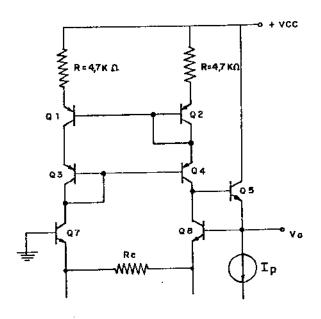

### III.3.3 Configuração final

A configuração final do dispositivo se apresenta conforme a figura abaixo. Pode-se notar a grande simplicidade e elegância deste esquema em relação às outras versões apresentadas, constituindo assim a nossa opção final de projeto.

Fig. III.18 - Configuração final do circuito multiplicador

As fontes Ia, Ib, Io, IR<sub>1</sub> e IR<sub>2</sub> são geradas na ma lha decodificadora, sendo que as mesmas são apresentadas 'na figura III.16 apenas como um modo de mostrar o circuito com todas as suas entradas ocupadas.

Os diodos Q<sub>10</sub>, Q<sub>11</sub>, Q<sub>32</sub>, Q<sub>33</sub>, Q<sub>34</sub>, Q<sub>35</sub>, Q<sub>36</sub>, Q<sub>37</sub> e Q<sub>38</sub> são na realidade transistores com a base coletor connectadas juntos e estão no esquema III.16 desenhadas como diodos apenas por uma facilidade de representação na definição das funções destes elementos.

Baseados nas equações III.32 e III.34, e despre - zando o efeito de  $\,\alpha$  dos transistores temos:

$$V_{O} = \frac{Ia \cdot Ib \cdot Io}{2 \cdot IR_{1} \cdot IR_{2}} \cdot R_{C}$$

(III.48)

ou seja:

$$V_{O} = KIb \cdot Ia$$

(III.49)

onde:

K = constante de proporcionalidade que converte corrente em tensão e vale:

$$K = \frac{Io R_{C}}{2 \cdot IR_{1} \cdot IR_{2}}$$

(III.50)

finalmente, levando em consideração a célula de chaveamento, obteremos a expressão II.1, ou seja:

$$V_O = K \text{ Ia Ib } (B_1 - \overline{B}_1)$$

(III.51)

Assim, podemos ver que a célula multiplicado ra proposta apresentará em sua saída um sinal em tensão proporcional ao produto das correntes Ia e Ib e ao bit de polaridade B1.

# CAPÍTULO IV

TESTE E VERIFICAÇÃO DE DESEMPENHO DO CIRCUITO PROJETADO

# IV.1 Construção do Protótipo

## IV.1.1 Determinação dos transistores

Para teste de funcionamento e verificação de d $\underline{e}$ sempenho do circuito projetado e apresentado na figura III.16, procurou-se levar em consideração que este dispositivo em sua versão final será totalmente integrado. Assim, na construção' do protótipo tentou-se aproximar o mais possível das características que este dispositivo apresentará nesta versão. Utili zaram-se assim, transistores integrados encontrados no comércio, como os circuitos integrados 3046 fabricados pela RCA, pa ra os transistores NPN. Não se conseguiram transistores grados PNP de modo a simular as características dos PNPs late rais utilizados na integração. Devido a este fator foram utilizados transistores discretos do tipo BC 557. Em posições on de o efeito translinear não era fundamental e o descasamento' das áreas e de tensão base emissor ( $V_{

m BE}$ ) não influenciaram no desempenho do circuito, utilizou-se transistores NPN discre tos do tipo BC 239.

Assim, para melhor compreensão, a figura IV.l 'detalha com clareza o exposto acima.

Fig. IV.1 - Localização dos transistores discretos no circuito proposto

Todos os transistores acompanhados de asteriscos (\*) são transistores discretos.

#### IV.1.2 Determinação dos Resistores

Para a polarização do circuito protótipo utilizou-se ± 8V e denominou-se estas fontes de VCC e VEE. As - sim temos:

$$VCC = + 8 V$$

(IV.1)

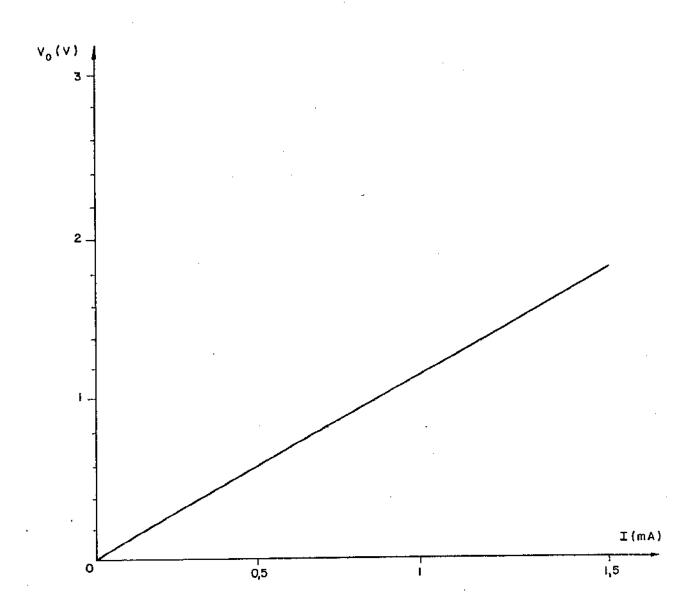

$$VEE = -8 V \qquad (IV.2)$$

A resistência R<sub>C</sub> representada na figura IV.1 e integrante do conversor I/V do circuito proposto, é fundamental na determinação do valor de tensão de saída, visto 'que o seu valor, juntamente com outros parâmetros definidos nos capítulos anteriores, determinarão a constante de conversão de corrente em tensão "K", constante esta, significativa para se atingir o objetivo proposto e previamente definido, como pode ser observado na equação II.1 do capítulo 2. Deste modo, o valor do resistor R<sub>C</sub> torna-se de suma importância na determinação da saída "Vo" do circuito.

Outro problema que pode ser observado, diz 'respeito ao funcionamento do circuito proposto em função da tensão de saída. Nota-se facilmente que uma tensão proporcio nal a "Vo" estará no terminal do resistor "Rc", conectado ao emissor de  $Q_8$ , e valerá:

O sinal mais ou menos ( $\pm$ ) encontrado em Vo de penderá da polaridade definida pelo pulso de tensão "B<sub>1</sub>".Con vém salientar que o valor encontrado na equação IV.3 é em relação ao emissor de Q<sub>7</sub>. Porém como a tensão base emissor de Q<sub>7</sub> é idêntica a tensão base emissor de Q<sub>8</sub>, para facilidade de

raciocínio tomaremos a tensão no emissor de Q<sub>8</sub> em relação à terra. Assim:

$$Ve_8 = \pm Vo$$

(IV.4)

Os coletores de  $Q_{14}$  e  $Q_{15}$  também estão conectados aos terminais de  $R_{\rm C}$ , verificando-se que, devido a is to, no instante em que se tiver uma tensão de saída negativa no coletor de  $Q_{15}$ , esta valerá:

$$v_{c_{15}} = -v_o$$

(1v.5)

O potencial na base de  $Q_{15}$  é fixo e definido pelo multiplicador de  $V_{\rm BE}$  formado por  $Q_{13}$ ,  $R_1$  e  $R_2$ . Portanto "Vo" não poderá atingir valores que sejam negativamente mai ores que esta tensão de base, pois polarizará a função base emissor reversamente, cortando este transistor. Assim, devese limitar "Vo" a um valor máximo negativo que não permita a tensão de saída atingir níveis que coloquem em perigo o funcionamento previsto do transistor  $Q_{15}$ . Este mesmo fato não o correrá com o transistor  $Q_{14}$ , visto que seu coletor sempre ' estará  $V_{\rm BE7}$  abaixo da terra.

Baseado no fato acima mencionado, limita- se "Vo" a um valor de lV.

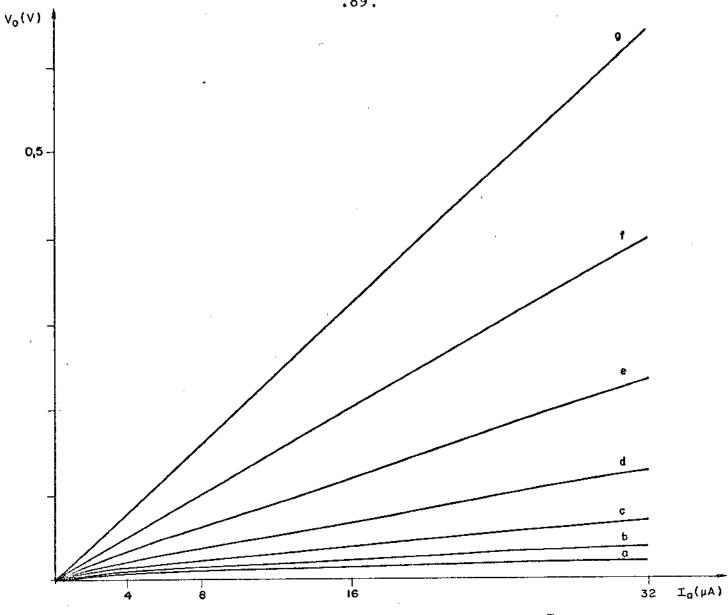

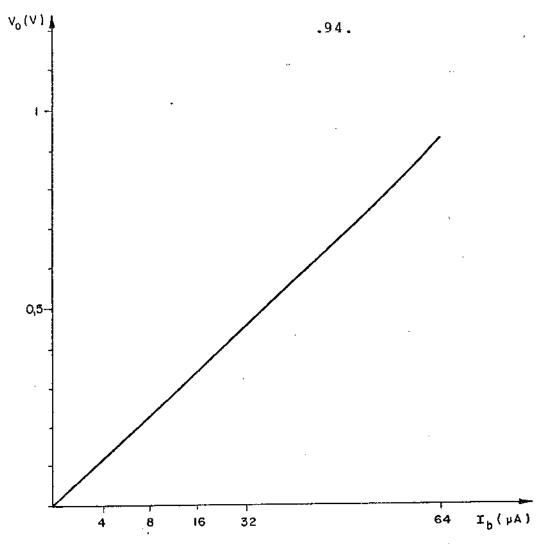

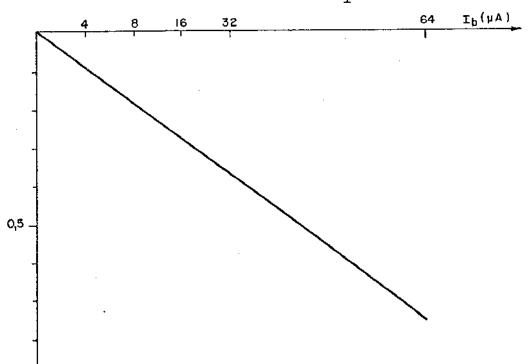

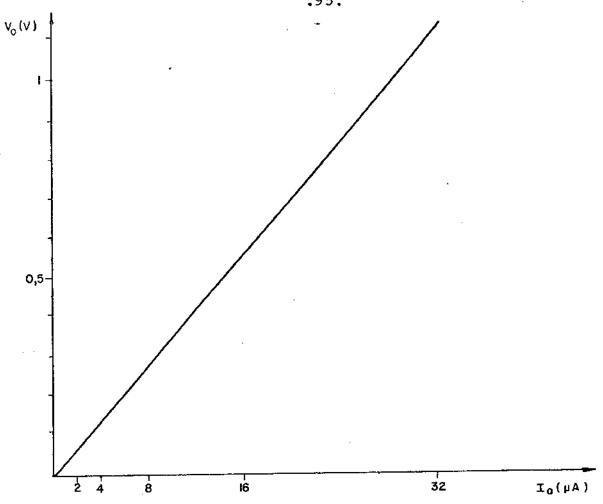

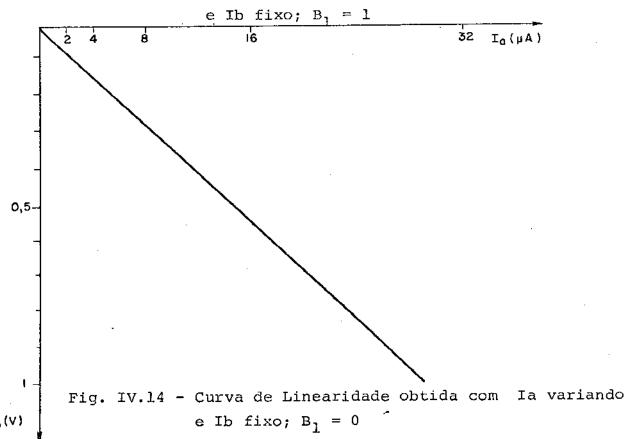

Utilizando a equação III.48 temos: