# Universidade Estadual de Campinas - UNICAMP Faculdade de Engenharia Elétrica - FEE Departamento de Microeletrônica

# Equacionamento, Simulação e Análise de Transcondutores que utilizam o Transistor MOS operando na Região de Saturação

Luiz Antônio Razera Júnior

Orientador:

Prof. Dr. Wilmar Bueno de Moraes

DEMIC / FEE - UNICAMP

Este exemples corresponde à eleção final da lese

defendida our LUIZ ANTONIO RAZERA JUNIOR Dissertação apresentada à Faculdade de

defendida our LUIZ ANTONIO RAZERA JUNIOR Dissertação apresentada à Faculdade de

Engenharia Elétrica da Universidade

Estadual de Campinas - FEE / UNICAMP

como requisito parcial à obtenção do título

ide Mestre em Engenharia Elétrica

WILMAR BUENO DEMONAES TENTEDOR

Campinas, Junho de 1995

| Dedico este trabalho                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                            |

| aos meus Pais, <i>Luiz Antonio Razera</i> e <i>Eidil Aparecida Milani Razera</i> , Doutores pela Vida, sábios Conselheiros, que por todo o meu caminho sempre me apoiaram e incentivaram. Que sous ensinamentos me acompanhem para sempre. |

| centivaram. Que seus ensinamentos me acompanhem para sempre.                                                                                                                                                                               |

|                                                                                                                                                                                                                                            |

# Agradecimentos

Gostaria de agradecer a todas as pessoas que, de uma maneira ou de outra, com maior ou menor intensidade, me ajudaram no processo de elaboração deste trabalho, em especial ...

... aos amigos do Centro Tecnológico para a Informática - CTI, particularmente ao *Eng. Frank Herman Behrens*, meu ex-chefe, e ao *Eng. Saulo Finco*, pela amizade, apoio, compreensão e estímulo recebido;

... ao *Eng. Luciano S. Fernandes*, colega e amigo, pelas conversas e discussões, e pelo gentil fornecimento do programa "Sspice", de grande importância para o desenvolvimento deste trabalho;

... ao *Prof. Dr. Wilmar Bueno de Moraes*, meu orientador e amigo, por tudo o que me transmitiu, inclusive os conhecimentos científicos;

... à família Charry Sierra, por todo o apoio e incentivo, pelas sábias opiniões, pelo carinho e compreensão de todos;

... aos meus pais, *Luiz Antônio e Eidil*, e à minha irmã, *Renata*, pelo estímulo, carinho e amor;

... à minha futura esposa, Ximena, pela paciência, incentivo e apoio.

Agradeço, de maneira preeminente, Àquele sem o qual nada disso seria possível.

# Agradeço a Deus.

# Algumas Palavras ...

"Uma coisa permanece. Há uma fórmula famosa - talvez a mais compacta e famosa de todas as fórmulas - desenvolvida por Euler, partindo da descoberta do matemático francês De Moivre:  $e^{i\pi} + 1=0$ . Elegante, concisa e cheia de significação, podemos apenas reproduzi-la, mas não devemos parar para perguntar suas implicações. Ela interessa tanto ao místico quanto ao cientista, ao filósofo, ao matemático. Para cada um deles tem um significado. Embora conhecida por mais de um século, a fórmula de De Moivre pareceu a Benjamin Peirce, um dos maiores matemáticos de Harvard do século XIX, algo como uma revelação. Tendo descoberto a fórmula um determinado dia, ele dirigiu aos seus alunos uma observação que encerra, em qualidade dramática e apreciação, o que lhe falta em conhecimento e sofisticação: "Senhores", disse ele, "isso é certamente verdade, é absolutamente paradoxal; não podemos entendê-lo, e não sabemos o que significa, mas provamo-lo e, portanto, sabemos que deve ser a verdade".

Quando tanta humildade e tanta visão existirem por toda parte, a sociedade será governada pela ciência e não por seus componentes mais espertos."

> Matemática e Imaginação Edward Kasner e James Newman pag. 107.

Sspice é marca registrada de "Michigan State University Board of Trustees".

Mathematica é marca registrada de "Wolfram Research, Inc."

PSpice é marca registrada de "MicroSim Corporation".

# ÍNDICE

| Dedicatória                                                                               | l              |

|-------------------------------------------------------------------------------------------|----------------|

| Agradecimentos                                                                            | II             |

| Algumas Palavras                                                                          | 111            |

| Índice                                                                                    | V              |

| Resumo                                                                                    | VII            |

| Abstract                                                                                  |                |

| Introdução                                                                                |                |

| Capítulo I - Transcondutores com Par Diferencial                                          |                |

| 1.1 Introducão                                                                            | 4              |

| 1.2 Par Diferencial Simples                                                               | 5              |

| 1.2.1 Não-Linearidade                                                                     | 6              |

| 1.2.2 Distorção Harmônica                                                                 | 10             |

| 1.2.3 Resposta em Frequência                                                              | 1              |

| 1.2.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação                    | 14             |

| 1.3 Par Diferencial Cruzado com Fontes de Corrente Independentes                          | CI             |

| 1.3.1 Aumento da Linearidade através de Diferença de Correntes                            | 10             |

| 1.3.2 Distorção Harmônica                                                                 | 13<br>20       |

| 1.3.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação                    | 21             |

| 1.4 Par Diferencial Cruzado com Fonte de Corrente Comum                                   | 21             |

| 1.4.1 Não-Linearidade                                                                     | 22             |

| 1.4.2 Distorção Harmônica                                                                 | 25             |

| 1.4.3 Resposta em Freqüência                                                              | 25             |

| 1.4.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação                    | 26             |

| 1.5 Par Diferencial com Célula em Modo Corrente                                           | 27             |

| 1.5.1 Linearidade através de Diferença de Correntes                                       | 27             |

| 1.5.2 Distorção Harmônica                                                                 | 31             |

| 1.5.3 Resposta em Freqüência                                                              | 32             |

| 1.5.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação                    | 34             |

| 1.6 Conclusões                                                                            | 35             |

| Capítulo II - Transcondutores com Polarização Adaptativa                                  | 0.0            |

| 2.1 Introdução                                                                            | პნ             |

| 2.2 Princípios Básicos da Polarização Adaptativa                                          | 37             |

| 2.3 Par Diferencial em Polarização Adaptativa com circuito quadrador de dois transistores | 5 OT           |

| 2.3.1 Linearidade                                                                         | 4ህ<br>ለር       |

| 2.3.2 Distorção Harmônica                                                                 | 42<br>ለር       |

| 2.3.3 Resposta em Freqüência                                                              | 42<br>15       |

| 2.3.4 EXCUISÃO DO SINAI DE ENTRADA EM TEIAÇÃO AS FUNES DE MIMENTAÇÃO                      | 40<br>A6       |

| 2.4 Par Diferencial em Polarização Adaptativa com Célula Quadradora Cruzada               | <del>7</del> € |

| 2.4.   LIIICAIIUAUC                                                                       | 0              |

| 2.4.2 Distorção Harmônica                                              | 51  |

|------------------------------------------------------------------------|-----|

| 2.4.3 Resposta em Freqüência                                           | 52  |

| 2.4.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação | 54  |

| 2.5 Conclusões                                                         | 54  |

|                                                                        |     |

| Capítulo III - Transcondutores em Classe AB                            |     |

| 3.1 Introdução                                                         | 55  |

| 3.2 Princípios Básicos de Circuitos em Classe AB                       | 55  |

| 3.3 O Par CMOS                                                         | 57  |

| 3.4 Quadrador Duplo Cruzado                                            | 58  |

| 3.4.1 Linearidade                                                      | 61  |

| 3.4.2 Distorção Harmônica                                              | 64  |

| 3.4.3 Resposta em Freqüência                                           | 65  |

| 3.4.4 Excursão do Sinal de Entrada em Relação às Fontes de Alimentação | 72  |

| 3.5 Par Duplo CMOS                                                     | 73  |

| 3.5.1 Linearidade                                                      | 75  |

| 3.5.1.1 Transistores em Poços Independentes                            | 75  |

| 3.5.1.1 Transistores em Poços independentes                            | 77  |

| 3.5.1.2 Transistores canal N com substrato comum                       |     |

| 3.5.2 Distorção Harmônica                                              | oo  |

| 3.5.3 Resposta em Freqüência                                           |     |

| 3.5.3.1 Par CMOS M1-M2                                                 | 04  |

| 3.5.3.2 Par CMOS M2-M3                                                 |     |

| 3.5.3.3 Circuito Completo                                              | d8  |

| 3.5.4 Excursão do Sinal de Entrada em Relação às Fontes de Alimentação |     |

| 3.6 Conclusões                                                         | 91  |

|                                                                        |     |

| Capítulo IV - Transcondutores Projetados no DEMIC/FEE-UNICAMP          |     |

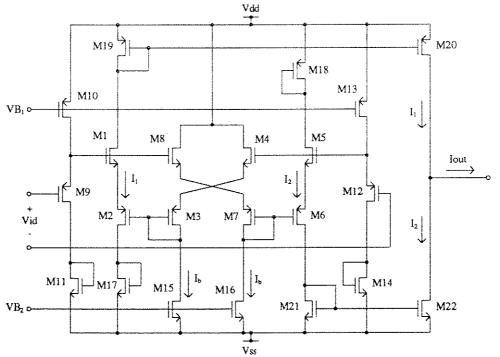

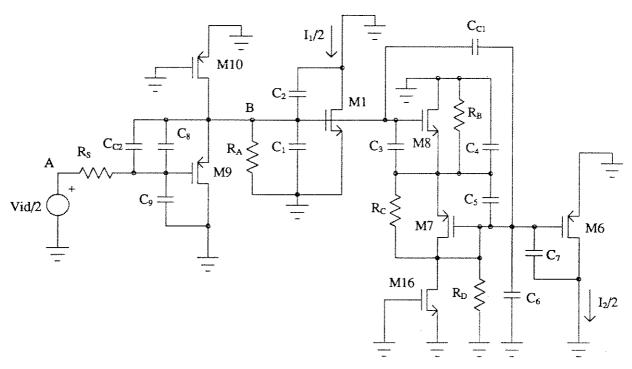

| 4.1 Introdução                                                         | 92  |

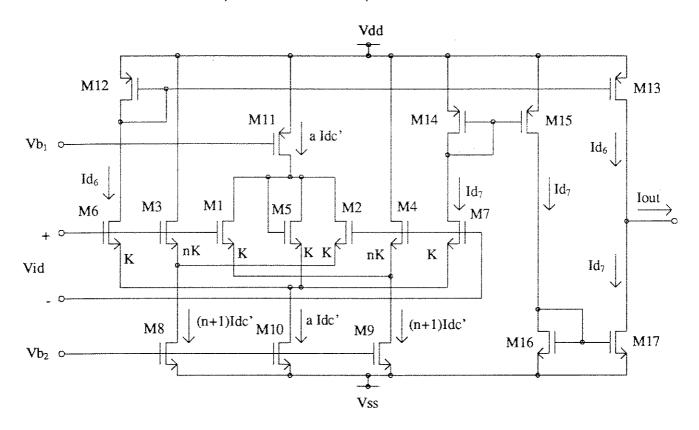

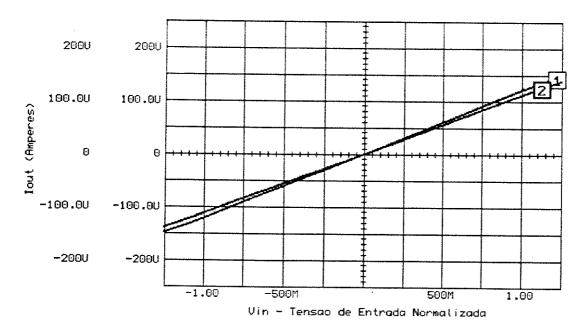

| 4.2 Circuito 1                                                         | 92  |

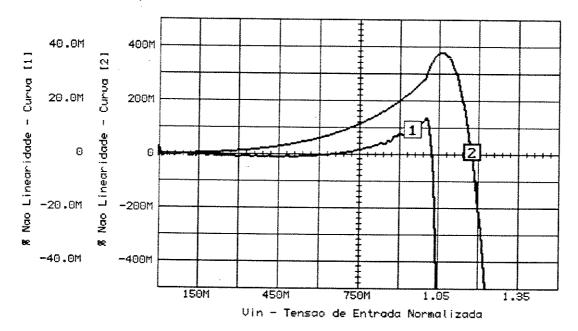

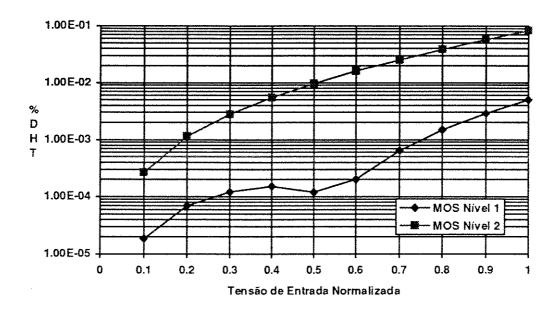

| 4.2.1 Linearidade                                                      | 93  |

| 4.2.2 Resultados Obtidos                                               | 94  |

| 4.3 Circuito 2                                                         | 94  |

| 4.3.1 Linearidade                                                      | 95  |

| 4.3.2 Resultados Obtidos                                               | 96  |

| 4.4 Conclusões                                                         | 96  |

|                                                                        |     |

| Conclusões Gerais                                                      |     |

| Considerações Iniciais                                                 | 97  |

| Contribuições do Trabalho                                              | 97  |

| Sumário dos Resultados Obtidos                                         | 98  |

| Proposições para Trabalhos Futuros                                     | 99  |

| Proposições para Trabalitos Futuros                                    |     |

|                                                                        | 100 |

| Referências Bibliográficas                                             | 100 |

|                                                                        |     |

| Apêndice A - O transistor MOS em Regime de Saturação                   | 102 |

| Apêndice B - Equacionamento DC e AC do Par Diferencial Simples         | 105 |

| Apêndice C - Exemplos de Arquivos de Simulação                         | 110 |

#### **RESUMO**

Este trabalho apresenta o equacionamento matemático, as simulações e análises detalhadas do comportamento DC, distorção harmônica, resposta em freqüência e excursão do sinal de entrada de dez conversores tensão-corrente, ou *transcondutores*, que utilizam transistores MOS operando na região de saturação.

Estes transcondutores estão subdivididos em quatro grupos, correspondentes aos quatro capítulos do trabalho. São eles:

- Transcondutores com Pares Diferenciais;

- Transcondutores com Polarização Adaptativa;

- Transcondutores em Classe AB;

- Transcondutores Projetados no DEMIC/FEE-UNICAMP.

São tecidos comentários acerca de cada circuito, enfatizando seus pontos positivos e negativos, além de comparações entre os transcondutores de um mesmo grupo. Sugestões e propostas de melhorias também são realizadas, além da verificação das mesmas através de simulações.

#### **ABSTRACT**

This work presents the mathematical equations, simulations and detailed analysis of DC behavior, harmonic distortion, frequency response and input signal excursion of ten V-I converters, or *tranconductors*, that use MOS transistors on the saturation region of operation.

Those transconductors are divided into four groups, which corresponds to the four chapters of the thesis. They are:

- Transconductors with Differential Pairs;

- Transconductors with Adaptative Biasing;

- Transconductors Designed at DEMIC/FEE-UNICAMP.

Comments are done on each circuit, enhancing their positive and negative aspects, besides comparisons among transconductors of a same group. Suggestions and enhancement proposes are also realized, besides their verification by simulations.

Introdução 1

# Introdução

Desde a invenção do transistor, em 23 de dezembro de 1947, por John Bardeen, Walter Brattain e William Shockley, nos Laboratórios Bell, os rumos do desenvolvimento tecnológico sofreram uma revolução sem precedentes. Deste então, a Eletrônica e, a seguir, a Microeletrônica, têm desempenhado um papel fundamental na evolução da humanidade. Presente, porém nem sempre percebida e valorizada, é esta ciência a responsável por feitos que vão desde atos simples e antigos, como a marcação do tempo, até atos praticamente inimagináveis por nossos antepassados, como a comunicação via satélite, a conquista do Espaço e a previsão de safras agrícolas, entre outros.

Historicamente, os primeiros transistores disponíveis (transistores bipolares) substituíram as antigas válvulas com inúmeras vantagens. Eram menores e mais leves, não tinham necessidade de filamentos que provocavam perda de calor, eram mais resistentes e eficientes, uma vez que absorviam menos energia, não necessitavam de tempo de aquecimento, podendo ser utilizados a qualquer instante e exigiam menores tensões de operação. Os Circuitos Analógicos, que até então utilizavam válvulas, foram rapidamente se ajustando de modo a utilizar este novo dispositivo. Desde então, dispositivos cada vez menores, mais baratos e confiáveis têm sido largamente empregados em inúmeras aplicações. Amplificadores, filtros, moduladores e demoduladores, e, mais recentemente, conversores A/D e D/A são apenas alguns exemplos destas aplicações, que se inserem num contexto ainda maior, como as comunicações, a radiodifusão e o processamento de sinais em uma forma geral.

A evolução do computador digital tem atuado de forma profunda do desenvolvimento da microeletrônica. Através da necessidade de componentes cada vez menores e mais rápidos, novas tecnologias têm sido continuamente desenvolvidas. Dentre várias disponíveis, a tecnologia CMOS tem ocupado posição de destaque na atualidade. Mais de 60% do mercado atual de microeletrônica, incluindo aplicações digitais e analógicas, é dominado por esta tecnologia. Circuitos digitais de crescente complexidade, como microprocessadores, microcontroladores e processadores digitais de sinais têm utilizado cada vez mais esta tecnologia, devido à altíssima capacidade de integração de componentes que a mesma oferece, fazendo com que circuitos que utilizem milhões de transistores possam ser realizados numa pastilha de silício de alguns milímetros quadrados.

Sendo assim, o desenvolvimento de circuitos analógicos com transistores MOS tem sido cada vez mais uma necessidade, de forma a compatibilizar, num mesmo circuito, funções analógicas e digitais, de modo a se obter um sistema integrado único, com maior confiabilidade e menor custo.

A evolução da capacidade de processamento de computadores, principalmente equipamentos pessoais, de baixo custo e alto desempenho, também proporcionou o desenvolvimento de programas cada vez mais poderosos e úteis, atuando como ferramentas de trabalho de profissionais das mais diversas áreas.

Na área de projetos de circuitos, os programas de maior utilidade têm sido simuladores. Baseados em parâmetros elétricos e parâmetros de construção de dispositivos, estes implementam as funções matemáticas que descrevem seu comportamento. Desta maneira, o projetista pode observar o desempenho de seu circuito, antes mesmo de fabricá-lo. Na árera de microeletrônica, um destes programas tornou-se praticamente um padrão: SPICE, que quer dizer "Programa de Simulação com Ênfase em Circuitos Integrados". Desta maneira, comportamento DC, análises da resposta transiente e de freqüências, análises de ruído e distorção harmônica de um circuito são algumas das capacidades que se têm hoje em dia nestes simuladores.

Outros programas, desenvolvidos nos últimos anos, também têm servido como ferramentas preciosas nas mãos de projetistas de circuitos. Pacotes matemáticos que possuem tratamento simbólico têm ajudado projetistas a resolver e formular, de maneira literal, as equações de seus circuitos. O programa *Mathematica* é um exemplo.

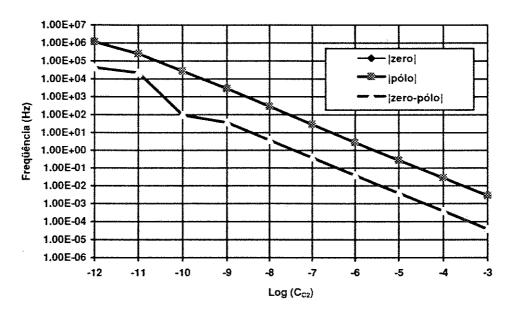

Após o surgimento deste tipo de programa, que possui tratamento simbólico, surgiram simuladores simbólicos de circuitos, como o programa *Sspice*. Desta forma, os comportamentos DC e AC de um circuito podem ser dados, não mais apenas sob a forma de um gráfico, obtido numericamente, mas através de funções matemáticas. A possibilidade de se ter, matematicamente, a expressão de uma função de transferência em função de parâmetros do circuito, como condutâncias e capacitâncias e ganhos associados, abre uma nova forma de se resolverem problemas anteriormente solucionados através da intuição e experiência de projetistas. No caso da resposta em freqüência de um circuito, por exemplo, um capacitor de compensação pode ter seu valor exatamente determinado, de modo a aumentar a faixa de operação. A utilização deste tipo de programa, que fornece uma expressão matemática do funcionamento do circuito, em conjunto com pacotes matemáticos, que resolvem equações, de maneira numérica e simbólica, estão se tornando, para o projetista de circuitos, ferramentas análogas ao processador de textos para um escritor.

De posse destes programas, juntamente com um computador de alta capacidade e velocidade de processamento, a realidade de um projetista de circuitos integrados é bastante diferente daquela encontrada nos primórdios da microeletrônica. A tarefa de projeto, hoje, se resume praticamente a um trabalho realizado sob o auxílio dos programas mencionados, num computador. A fabricação e teste de protótipos; etapa essencial para a verificação da idéia, vêm apenas confirmar os resultados esperados. Embora estes programas tenham auxiliado de maneira importantíssima o projeto de um circuito, a criação e idéias para a solução otimizada dos problemas são ainda méritos que cabem exclusivamente ao projetista.

Esta tese trata, sob o ponto de vista do equacionamento matemático, verificação computacional do comportamento (simulação) e análise dos resultados obtidos, de circuitos que realizam a conversão de sinais sob a forma de tensão elétrica para corrente elétrica.

O Conversor Tensão-Corrente, ou *Transcondutor*, é um bloco analógico básico para a implementação de sistemas de processamento de sinais analógicos mais complexos, tais como integradores, resistores flutuantes, giradores, filtros ativos e multiplicadores analógicos, entre outros. Na atualidade, circuitos de grande complexidade, como conversores A/D e D/A, necessitam de transcondutores de alta precisão para realizarem suas funções adequadamente.

Uma nova vertente na eletrônica analógica tem sido o processamento de sinais sob forma de corrente. Esta abordagem, chamada "modo corrente", tem demostrado algumas vantagens em relação ao modo tensão. Dentre elas, destacam-se o aumento da banda de freqüências e seu uso apropriado para sistemas em baixa tensão (3.3V ou 5 V), uma vez que, sendo o sinal em forma de corrente, não é necessário o uso de grandes variações de tensão. O processamento em modo corrente quase sempre leva a projetos mais simples e menor consumo de potência, aumentando portanto a densidade, reduzindo-se o custo em área de material semicondutor. Porém, para a manutenção da compatibilidade entre sistemas existentes em modo tensão, é necessário o uso de transcondutores na entrada de Sistemas de Processamento de Sinal em Modo Corrente.

No caso de ser necessário o uso de tais conversores, estes são uma parte delicada no projeto global, uma vez que podem limitar a linearidade, a resposta em freqüência e a imunidade a ruídos. Deste modo, qualquer transcondutor que seja utilizado na entrada de um sistema de processamento de sinal em modo corrente deve satisfazer os seguintes atributos:

- alta linearidade para sinais de relativa amplitude;

- baixo ruído:

- alta frequência de operação;

- baixo consumo:

- alta transcondutância.

O objetivo principal deste trabalho é enfatizar os aspectos mais importantes na análise e projeto de transcondutores que utilizam o transistor MOS operando na região de saturação. São apresentados dez circuitos, divididos em quatro categorias:

- Transcondutores com Par Diferencial 4 circuitos;

- Transcondutores com Polarização Adaptativa 2 circuitos;

- Transcondutores em Classe AB 2 circuitos:

- Transcondutores Projetados no DEMIC/FEE-UNICAMP 2 circuitos.

A não ser nos dois últimos circuitos, cuja análise detalhada pode ser encontrada em trabalhos de tese apresentados na própria faculdade, todos os outros oito circuitos foram minuciosamente equacionados, simulados e analisados, com algumas propostas de melhoramentos e inovações.

É importante ressaltar que foram dadas ênfases a aspectos relativos ao transcondutor em si. Problemas como a geração de tensões de polarização e melhorias nas respostas DC e AC de espelhos de corrente não foram analisados. Cada um destes problemas pode resultar em outros temas de tese, dada a sua complexidade.

O equacionamento DC de cada circuito foi realizado manualmente, tendo sido verificado com o auxílio do programa *Mathematica*. As expressões obtidas nas análises AC de cada circuito foram obtidas pelo programa de simulação simbólica *Sspice*. Todos os resultados teóricos foram verificados através da utilização do programa de simulação *PSpice*, versão 4.05, baseado no *Spice*.

# Capítulo I

# Transcondutores com Par Diferencial

# 1.1 Introdução

Dentre a grande variedade de transcondutores existentes, os mais utilizados são aqueles que empregam *Pares Diferenciais*. E não é difícil saber o porquê. Dentre as vantagens, pode-se citar a simplicidade de projeto, o baixo consumo de potência, a alta resposta em freqüência, a alta transcondutância, a alta impedância de entrada e o baixo ruído.

Porém, uma das grandes desvantagens de circuitos que utilizam Pares Diferenciais como transcondutores é a sua *não-linearidade* inerente para sinais de entrada de relativa amplitude, o que reduz sensivelmente a faixa de tensões de entrada. Devido a este fator existem muitas propostas de circuitos que se baseiam no Par Diferencial Simples e, através de diferentes técnicas de linearização, conseguem melhorar significativamente a linearidade, aumentando a faixa de excursão do sinal de entrada.

Outra característica indesejável é o fato de o sinal de saída ser diferencial, necessitando de espelhos de corrente adicionais que conduzam a corrente de saída a um ramo único. Estes espelhos exercem também a função de levar a saída a um ponto de tensão nula, uma vez que, sendo os sinais de entrada referenciados ao terra, a própria topologia de circuitos que utilizam pares diferenciais como elementos transcondutores faz com que, inerentemente, a tensão de saída possua um alto "offset". Porém, a inclusão destes elementos (espelhos de corrente) faz com que haja uma alta degradação na resposta em freqüência dos circuitos, limitando a largura de faixa de operação.

Este capítulo trata de quatro circuitos que utilizam pares diferenciais. São eles:

- Par Diferencial Simples [1];

- Par Diferencial Cruzado com Fontes de Corrente Independentes [2];

- Par Diferencial Cruzado com Fonte de Corrente Comum;

- Par Diferencial com Célula em Modo Corrente [3];

O primeiro circuito mostra todas as características inerentes de um par diferencial. A não-linearidade intrínseca é a principal desvantagem, o que reduz sensivelmente a faixa de tensões de entrada do circuito. Após é mostrado que, utilizando-se dois Pares Diferenciais Simples completos com relações de geometria e correntes apropriadas, é possível obter um cancelamento parcial das não-linearidades, o que resulta numa melhora significativa da linearidade e da faixa de tensões de entrada utilizável pelo circuito. O terceiro circuito é uma simplificação do segundo, com apenas uma fonte de corrente utilizada de modo comum pelos dois pares de transistores. É mostrado que não existe nenhuma vantagem em operação de grandes sinais, em relação ao Par Diferencial Simples. Existe, entretanto, uma melhora na resposta em freqüência, com a possibilidade de eliminação de um zero da função de transferência. O último circuito apresenta uma recente proposta de linearização através do uso de uma célula em modo corrente, na qual é mostrado que um cancelamento completo dos termos não lineares pode ser obtido, resultando em um circuito com alta linearidade. Porém, a resposta em freqüência deste circuito é inferior aos circuitos anteriores, limitando a faixa de freqüências de operação.

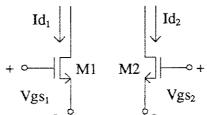

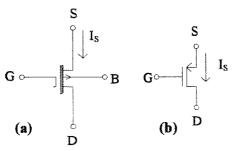

# 1.2 Par Diferencial Simples

O transcondutor mais simples e mais comumente utilizado é o Par Diferencial Simples. Além de sua simplicidade, este circuito oferece baixo ruído, baixo "offset" em corrente e alta resposta em freqüência. Porém, devido à sua não-linearidade, a faixa de tensão de entrada utilizável e eficiência (máxima corrente linear de saída / corrente total) são reduzidas [1].

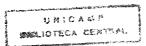

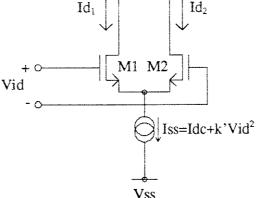

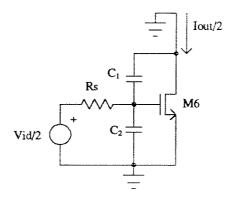

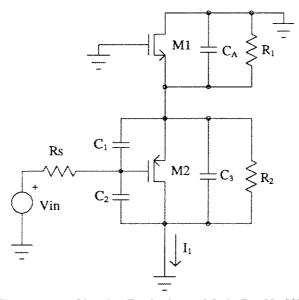

Figura 1.1 - Par Diferencial Simples

(a) - Implementação Ideal

(b) - Implementação Real

A análise topológica dos circuitos da figura acima mostra claramente que o sinal de saída deve ser tomado como a diferença entre as correntes Id<sub>1</sub> e Id<sub>2</sub>. Além disso, em aplicações usuais, a tensão nos drenos destes transistores, com uma tensão de modo comum de entrada igual a zero, possui um alto "offset".

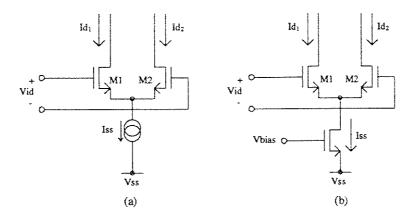

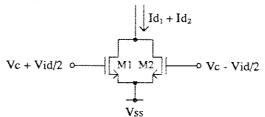

Esta situação é muito comum em vários transcondutores. O esquema abaixo representa uma forma genérica de se conseguir uma saída em corrente única, num ponto de baixo "offset" de tensão.

Figura 1.2 - Esquema para saída única e baixo "offset"

Desta forma, utilizando espelhos de corrente simples, o circuito completo que utiliza um Par Diferencial Simples como elemento transcondutor é representado na figura 1.3.

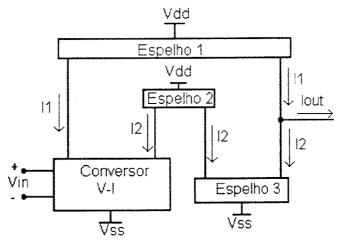

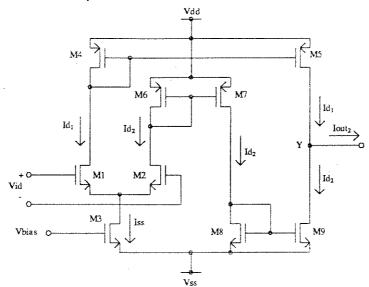

Figura 1.3 - Circuito Completo com Par Diferencial Simples

No circuito acima, os transistores M4-M5, M6-M7 e M8-M9 são, respectivamente, os espelhos 1, 2 e 3 representados na figura 1.2. Note que a transcondutância do circuito pode ser alterada variando-se as relações W/L dos espelhos de corrente.

Todas as simulações realizadas sobre o Par Diferencial Simples foram feitas levando-se em consideração o circuito da figura 1.3. Foram utilizados os seguintes parâmetros:

- → Vdd = Vss = 5 V

- Iss = 200 μA

- (W/L)<sub>M1,M2</sub> = 20μ/5μ

- (W/L)<sub>M3</sub> = 100μ/5μ

- $\Psi$  (W/L)<sub>M4,M5,M6,M7</sub> =  $40\mu/5\mu$

- (W/L)<sub>M8,M9</sub> = 12.6μ/50μ

- $\mathcal{F}$  Rout = 50  $\Omega$ , Rs = 50  $\Omega$

Nos parâmetros acima, Rout é a resistência de carga no nó de saída simples (nó Y da figura 1.3), por onde flui a corrente lout<sub>2</sub>, e Rs é a impedância da fonte geradora de sinal. Além disso, as relações W/L dos transistores representam suas dimensões, em micras. Foram utilizados valores não inteiros na geometria dos transistores M8 e M9 para se ajustar o "offset" de tensão no nó de saída.

#### 1.2.1 Não-Linearidade

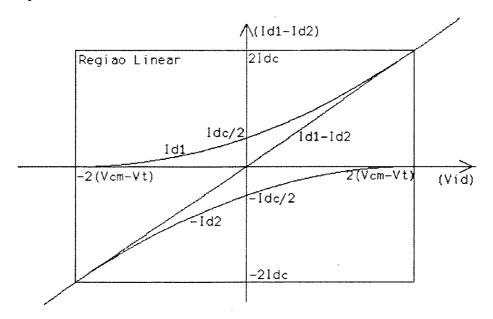

Através de uma análise de grandes sinais da figura 1.1-a, utilizando o modelo simplificado do transistor MOS (Apêndice A), pode-se mostrar que a corrente de saída (ld1 - ld2) do Par Diferencial Simples é dada pela equação 1.1.

$$Iout = Id_1 - Id_2 = \begin{cases} \sqrt{2Iss \, K} \, Vid \, \sqrt{1 - \frac{K}{2Iss}} Vid^2 & \longrightarrow |Vid| \le \sqrt{\frac{Iss}{K}} & (a) \\ Iss \, \operatorname{sgn}(Vid) & \longrightarrow |Vid| \ge \sqrt{\frac{Iss}{K}} & (b) \end{cases}$$

$$(1.1)$$

onde

$$K = \frac{\mu C_{ox}}{2} \frac{W_{eff}}{L_{eff}}$$

.

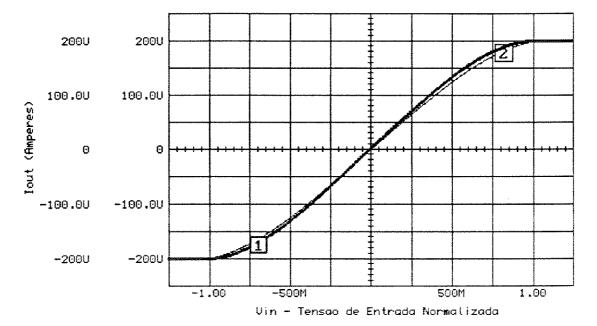

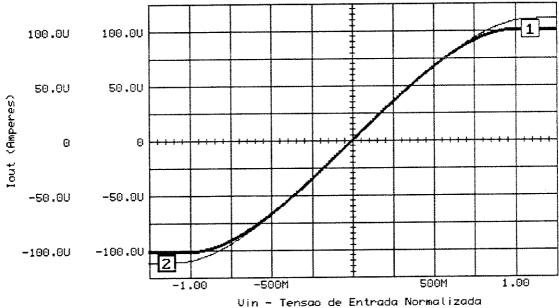

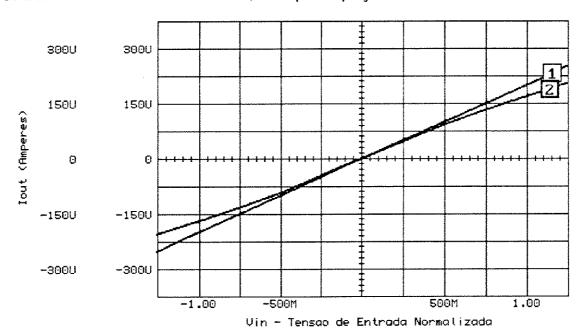

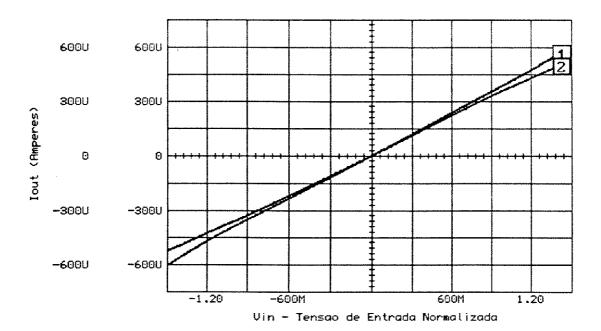

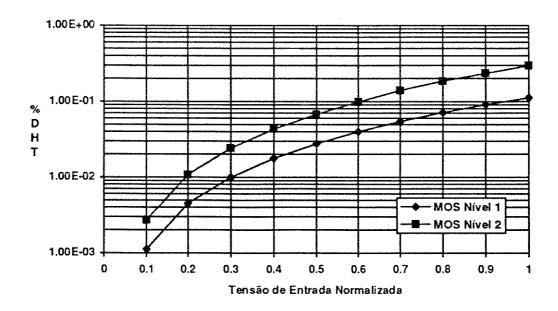

Pela observação da equação 1.1 vê-se que a saída é inerentemente não linear. A figura 1.4 apresenta a curva de transferência do Par Diferencial Simples. Foram utilizados os modelos de simulação fornecidos para o processo CMOS 1.2 μm da "foundry" AMS [4] (modelo MOS de nível 2 - casos típicos), para a obtenção de resultados mais realistas, e modelos de nível 1 extraídos a partir dos modelos fornecidos, para a verificação do equacionamento realizado. O apêndice A apresenta a descrição dos dois modelos utilizados.

As diferenças observadas entre o caso "ideal" (nível 1) e o caso "real" (nível 2) se deve, principalmente, pelo fato de o nível 1 de simulação não contemplar a variação da mobilidade com o campo elétrico gerado pela tensão porta-fonte do transistor, e efeitos de modulação de canal.

Figura 1.4 - Curva de Transferência do Par Diferencial Simples (1) - Simulação com Modelo MOS nível 1 (2) - Simulação com Modelo MOS nível 2

O eixo "x" da figura acima corresponde a uma tensão de entrada normalizada, dada por:

$$Vin = \frac{Vid}{\sqrt{\frac{Iss}{K}}}$$

(1.2)

No gráfico, lout corresponde à diferença entre as correntes  $Id_1$  e  $Id_2$  da figura 1.1. A variação percentual entre a corrente  $Iout_2$  da figura 1.3 e a corrente de saída mostrada na figura 1.4 foi de no máximo, 3.18%, no ponto de tensão normalizada igual a 1. Isto se deve ao aumento nas correntes dos espelhos em relação às correntes de entrada, devido a efeitos de modulação de canal. Esta diferença pode ser minimizada aumentando-se o L dos transistores do espelho.

Pela análise da equação 1.1 e da figura 1.4, a corrente de saída é linear apenas numa pequena faixa de excursão da tensão de entrada. Esta não-linearidade causa distorção harmônica em sinais de grande amplitude. Além disso, a transcondutância  $g_m$  do circuito diminui com o aumento da tensão de entrada, fazendo com que a mesma possua a indesejável característica de ser função da mesma.

A expressão da transcondutância do circuito pode ser obtida derivando-se a equação 1.1-a com respeito a Vid, para sinais de entrada menores que  $\left|\sqrt{Iss/K}\right|$ . Após este valor, a corrente de saída assume valor constante de módulo igual a lss. Deste modo, a transcondutância do circuito cai a zero.

$$gm = \frac{\sqrt{2 Iss K} \left(1 - \frac{K Vid^2}{Iss}\right)}{\sqrt{1 - \frac{K Vid^2}{2 Iss}}}$$

(1.3)

De modo geral, pode-se definir a corrente ideal de um transcondutor como o produto da tensão de entrada pela transcondutância, sendo esta última calculada no ponto em que Vid é igual a zero. Neste caso, sendo a transcondutância dada pela equação 1.3, tem-se:

$$I_{iinear} = \sqrt{2 Iss K} Vid \tag{1.4}$$

O método aqui utilizado para reportar a não-linearidade é a variação percentual da corrente de saída em relação à corrente linear, dada por:

$$Var(\%) = \frac{Iout - I_{linear}}{I_{varies}} \cdot 100 \tag{1.5}$$

Utilizando 1.1-a e 1.4, tem-se que:

$$Var(\%) = \left(\sqrt{1 - \frac{K}{2 \, Iss} Vid^2} - 1\right) \cdot 100 \tag{1.6}$$

Para que a variação desejada fique abaixo de 1%, utilizando 1.6, a faixa de variação da tensão de entrada, nos casos de tensão diferencial absoluta e tensão normalizada, segundo a equação 1.2, é restrita a:

$$-0.20\sqrt{\frac{Iss}{K}} \le Vid \le 0.20\sqrt{\frac{Iss}{K}}$$

(a)

$-0.20 \le Vin \le 0.20$  (b)

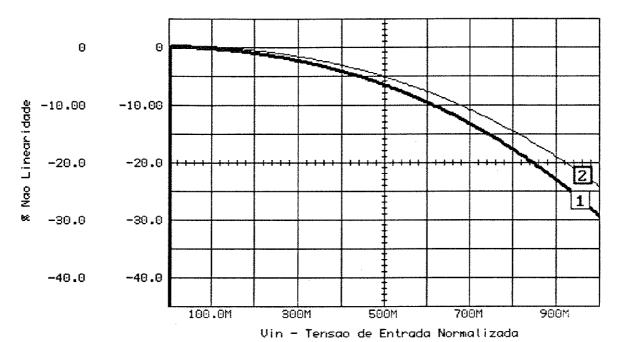

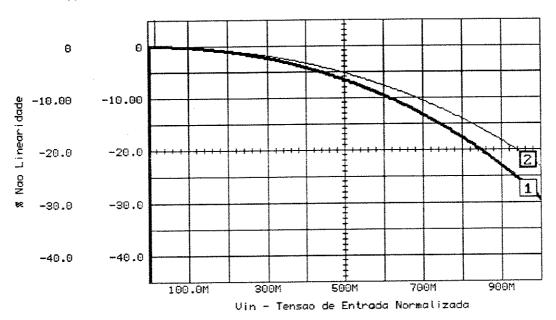

De acordo com as relações geométricas e modelos de simulação utilizados, a transcondutância máxima teórica ( $\sqrt{2 Iss K}$ ) é igual a 237.2 µA/V. Este foi o valor utilizado na equação 1.4 para a obtenção da curva 1 da figura 1.5. Devido principalmente ao efeito de redução da mobilidade pelo campo elétrico gerado pela tensão porta-fonte, a transcondutância do circuito simulado, utilizandose o modelo MOS nível 2 fornecido pela "foundry", foi de 219.8 μΑ/V. Este foi o valor utilizado na equação 1.4 para a obtenção da curva 2 na mesma figura. É esta a razão pela qual a nãolinearidade é menor que o caso teórico para maiores tensões, uma vez que as curvas de transferências de ambas as simulações (figura 1.4) se encontram em Vin igual a 1.

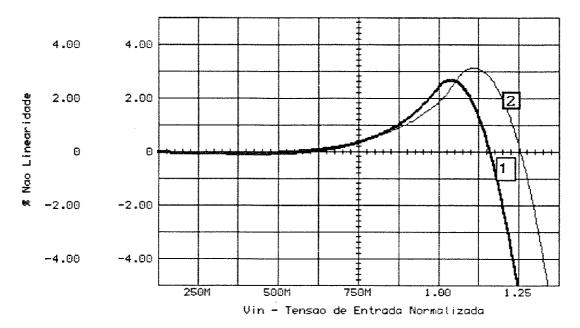

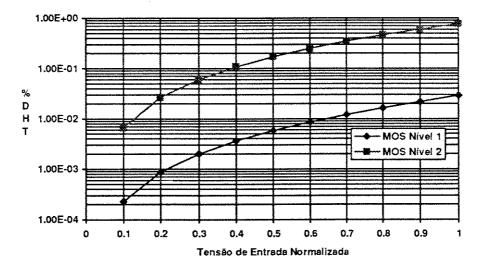

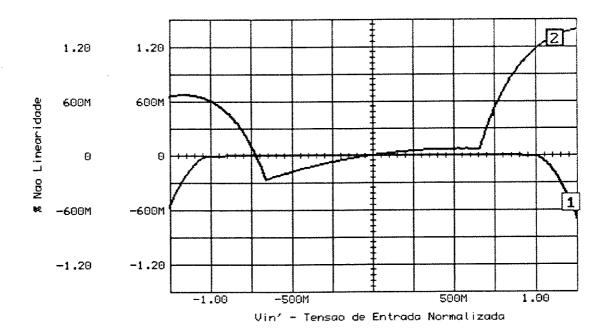

A figura abaixo representa a variação percentual da corrente de saída (ld1 - ld2) em relação à corrente linear observada, segundo a equação 1.5.

Figura 1.5 - Não-Linearidade do Par Diferencial

(1) - Simulação com Modelo MOS nível 1

(2) - Simulação com Modelo MOS nível 2

Pela análise da figura 1.5 também se pode comprovar a equação 1.7, sendo a faixa de excursão linear do circuito apenas 20% da faixa de excursão total, resultando em baixa eficiência (máxima corrente linear / corrente total). No circuito simulado, a faixa linear se restringe a |Vid| < 238 mV. Pode-se melhorar a faixa dinâmica utilizável aumentando-se a corrente de polarização, o que aumenta a potência consumida, ou reduzindo-se a relação W/L, o que implica um aumento de Vgs, acarretando deterioração na mobilidade. Estes fatores limitam a faixa de melhora possível do circuito.

Este circuito foi simulado para duas situações de tensões de entrada, uma em que a mesma é balanceada, e outra em relação ao terra, aplicada em apenas um dos transistores. Em ambos os casos pode ser mostrado que a tensão Vgs dos transistores é a mesma, o que leva a resposta a grandes sinais ser idêntica, ou seja, as equações aqui deduzidas e a figura 1.2 retratam a resposta do circuito para ambos os casos. Porém, esta situação acarreta uma variação maior na tensão Vds do transistor M3 (fonte de corrente), o que leva a uma maior variação na corrente lss em função de efeitos de modulação de canal.

### 1.2.2 Distorção Harmônica

Distorção Harmônica de ordem n (DH<sub>n</sub>) é a relação entre a amplitude da n-ésima harmônica e a amplitude da harmônica fundamental. É um importante parâmetro de análise de um circuito. Embora a linearidade seja freqüentemente utilizada como forma de se avaliar o comportamento de um circuito, esta não fornece nenhuma informação com respeito à intermodulação de sinal existente.

Para se avaliar a Distorção Harmônica, expande-se a função de transferência de grandes sinais em torno do ponto de operação (série de Taylor). Como no caso o ponto de operação central é igual a zero, uma vez que a tensão de entrada é diferencial, a série obtida é também chamada série de Maclaurin. Portanto, expandindo 1.1-a, tem-se:

$$Iout = \sqrt{2 Iss K} Vid - \frac{1}{2\sqrt{2}} \frac{K^{\frac{3}{2}}}{\sqrt{Iss}} Vid^{3} - \frac{1}{16\sqrt{2}} \frac{K^{\frac{3}{2}}}{Iss\sqrt{Iss}} Vid^{5} - \dots$$

(1.8)

Nota-se que, devido à topologia diferencial do circuito, os termos de ordem par são eliminados, reduzindo-se a distorção harmônica. De uma maneira geral, a equação 1.8 pode ser expressa da seguinte forma:

$$Iout = a_1 Vid + a_3 Vid^3 + a_5 Vid^5 + \dots = \sum_{n=0}^{\infty} a_{2n+1} Vid^{2n+1}$$

(1.9)

Para se determinar a porcentagem de distorção harmônica, seja Vid um sinal cossenoidal da seguinte forma:

$$Vid = Vp\cos(\omega t) \tag{1.10}$$

Substituindo (1.10) em (1.9) resulta em:

$$Iout = a_1 V p \cos(\omega t) + \frac{a_3}{4} V p^3 [3\cos(\omega t) + \cos(3\omega t)] + \dots$$

(1.11)

Para pequenas distorções, os termos de ordem superior a 3 podem ser desprezados, sem grandes perdas. Desta maneira a distorção harmônica total (DHT) pode ser aproximada pela distorção harmônica de ordem 3, ou seja:

$$DHT \approx DH_3 \approx \left(\frac{a_3}{4a_1 + 3a_3Vp^2}\right)Vp^2$$

(1.12)

Substituindo os termos de (1.8) em (1.12) resulta:

$$DHT \approx DH_3 \approx \left(\frac{K}{16Iss - 3KVid^2}\right)Vid^2$$

(1.13)

Utilizando o resultado acima e substituindo a tensão Vid pela tensão normalizada Vin (equação 1.2), para se ter uma DHT menor que 1%, tem-se:

$$-0.3941 \le Vin \le 0.3941 \tag{1.14}$$

A faixa de excursão do sinal de entrada praticamente dobrou em relação ao critério da nãolinearidade. Embora menos utilizado que o anterior, este critério fornece informações mais relevantes do que o primeiro, sendo suficiente para uma descrição completa do comportamento de grandes sinais de um circuito.

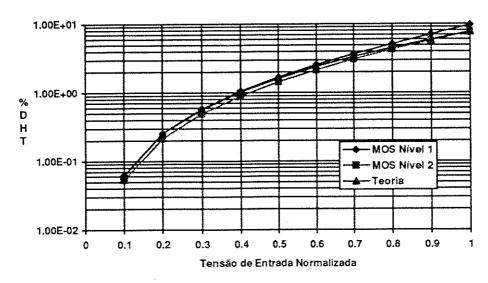

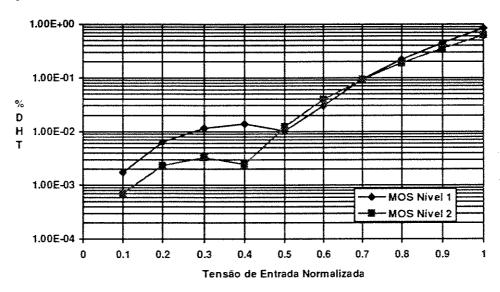

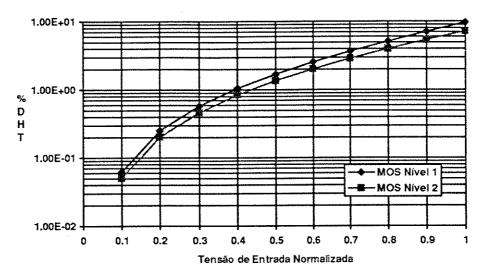

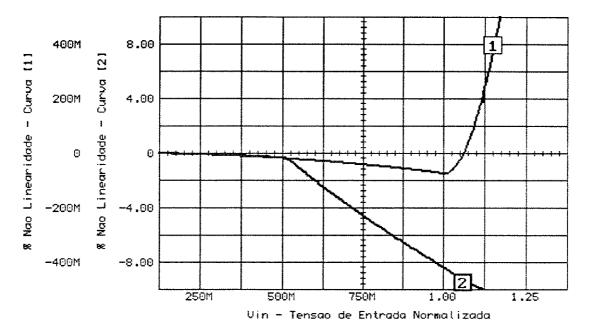

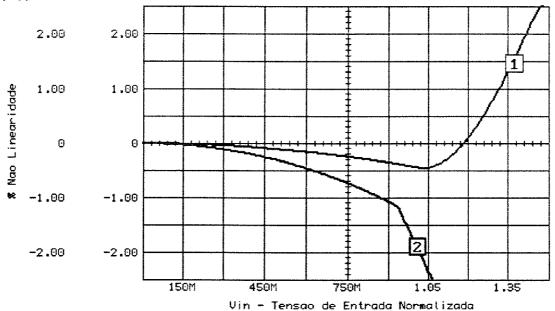

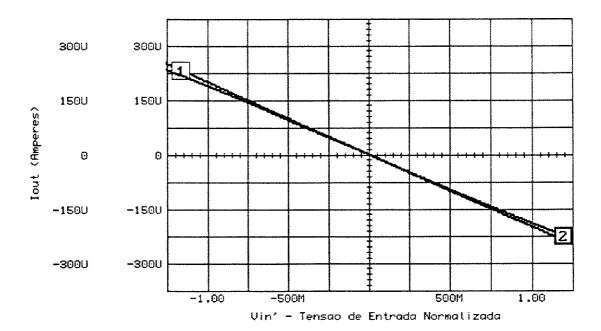

Para verificar este critério, realizaram-se simulações SPICE, com uma análise de Fourier da corrente de saída (Id<sub>1</sub> - Id<sub>2</sub>). Para isso, fez-se um sinal de entrada, normalizado, da forma da equação 1.10, com Vp variando de 0 a 1.0 V, em intervalos de 0.1 V. O resultado obtido é mostrado na figura 1.6.

Figura 1.6 - Distorção Harmônica do Par Diferencial Simples

Pela análise da figura acima vê-se que, para uma DHT menor que 1%, a tensão de entrada normalizada deve situar-se abaixo de 0.4, de acordo com a expressão 1.14. A distorção harmônica total verificada utilizando-se o modelo MOS nível 1 foi maior que o modelo nível 2 pelo mesmo motivo apresentado na análise de não-linearidade. As diferenças observadas entre a curva teórica e a curva obtida utilizando-se o modelo de nível 1 do transistor MOS são devidas ao fato de se ter aproximado a Distorção Harmônica Total pela Distorção Harmônica de 3ª ordem. Esta aproximação é válida para sinais de baixa amplitude. A partir de um certo ponto, as contribuições dos termos de ordem superior a 3 passam a ser significativas.

Os resultados relativos à corrente de saída  $lout_2$  da figura 1.3 e à corrente lout ( $ld_1$  -  $ld_2$ ) para casos em que a entrada é não balanceada pouco diferiram dos resultados apresentados na figura 1.6. As diferenças foram de, no máximo, 0.1%.

Embora os resultados de simulação e teoria predigam baixos níveis de distorção para tensões de entrada de pequena amplitude, deve-se dizer que, na prática, estes níveis são dominados pelo descasamento entre os dispositivos e pelas características intrínsecas dos mesmos [1]. Além da adoção de técnicas de leiaute para minimização do descasamento entre os transistores, o projetista pouco pode interferir neste tipo de problema.

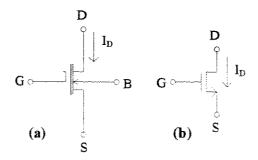

# 1.2.3 Resposta em Freqüência

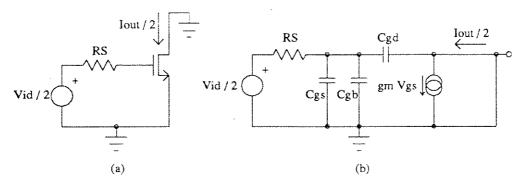

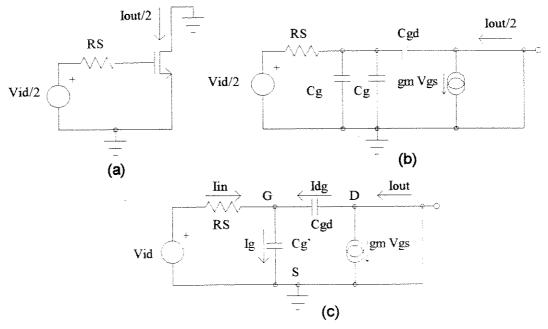

O par diferencial pode ser simplificado para uma análise de pequenos sinais no caso em que o sinal de entrada é balanceado e diferencial. A tensão na fonte dos transistores da figura 1.1 prati-

camente não varia para sinais de entrada de pequena amplitude, podendo ser considerado um terra AC. Deste modo, tanto no caso de o transistor ter o substrato ligado à fonte ou ao ponto mais negativo do circuito (Vss), a análise é a mesma, não existindo efeito de corpo na condição AC. Considerando que a impedância vista pelos drenos dos transistores M1 e M2 seja idealmente zero, também estes são considerados terras AC. Deste modo, a figura 1.7 representa o circuito equivalente AC do par diferencial e o modelo de pequenos sinais correspondente.

Figura 1.7 (a) - Circuito equivalente AC (b) - Modelo de Pequenos Sinais

Através da análise da figura 1.7-b, é possível demostrar que a relação lout/Vid é dada por:

$$\frac{lout}{Vid}(s) = \frac{gm\left(1 - s\frac{Cgd}{gm}\right)}{s\,RS\left(Cgs + Cgd + Cgb\right) + 1} \tag{1.15}$$

Nesta equação, RS é a impedância de saída da fonte de sinal Vid. Note que, sendo a soma das capacitâncias da ordem de picofarads a fentofarads, e RS da ordem de dezenas de ohms, o pólo predito por 1.15 é da ordem de dezenas de gigahertz a dezenas de terahertz, existindo, portanto, uma extensa faixa de freqüências em que o circuito pode ser utilizado sem perdas na transcondutância. Além disso, existe um zero no semiplano direito, formado pelo caminho direto entre a entrada e a saída através de Cgd, correspondente à freqüência na qual a corrente que flui através de Cgd anula exatamente a corrente do gerador *gm Vgs* no nó de saída [5]. Este zero causa um efeito na fase do mesmo modo que um pólo no semiplano esquerdo, existindo uma degradação na mesma.

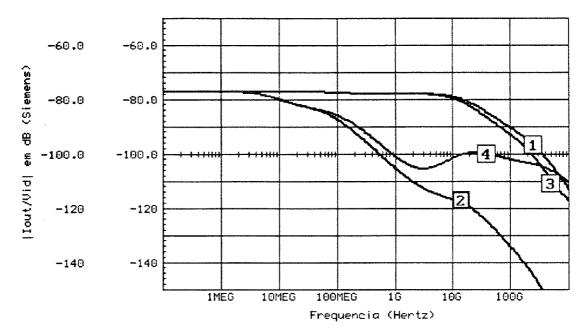

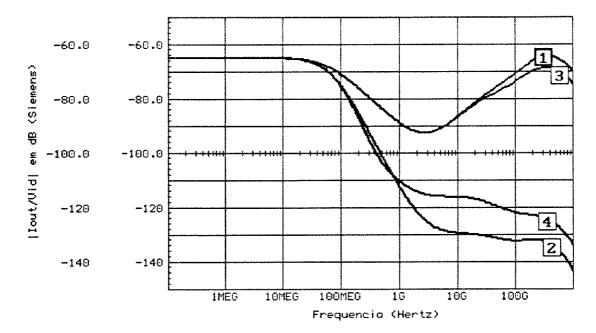

Em aplicações práticas, porém, a impedância nos drenos dos transistores M1 e M2 é finita e são necessários espelhos de corrente para transportar a corrente de saída diferencial para um ponto de tensão nula e saída simples.

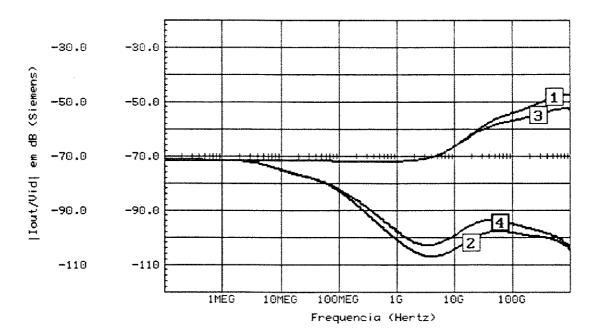

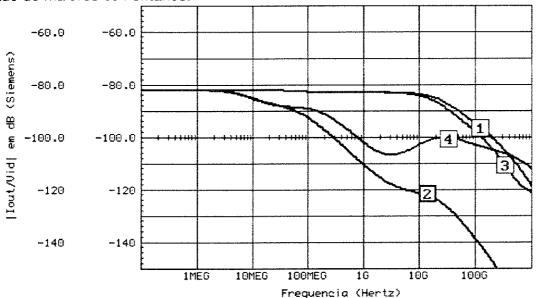

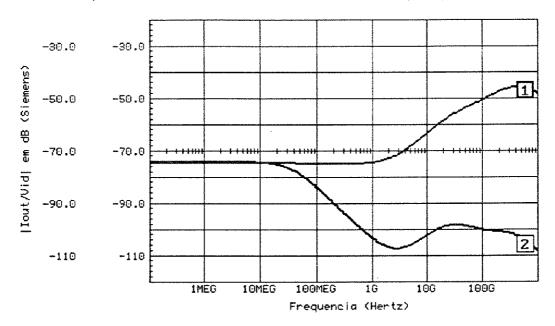

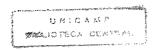

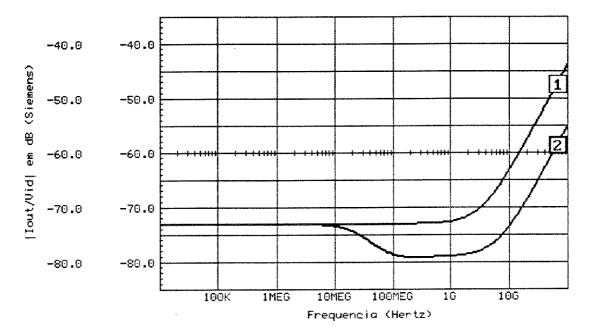

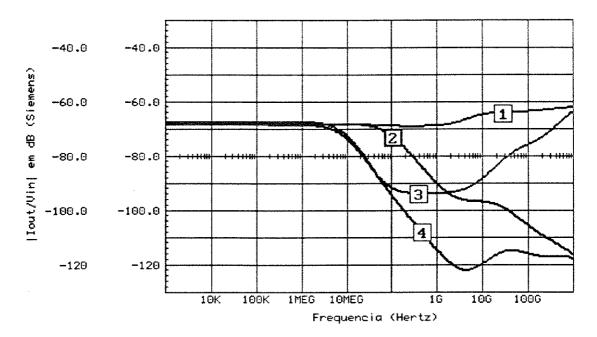

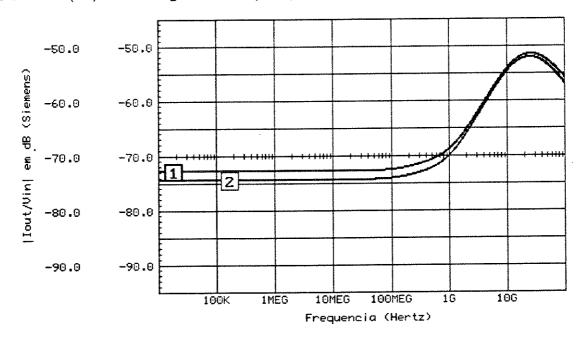

A figura 1.8 ilustra a transcondutância AC do circuito da figura 1.3, com sinais de entrada balanceados e não balanceados. Nas curvas 2 e 4 da figura 1.8 vê-se claramente o efeito dos espelhos de corrente na resposta em freqüência do Par Diferencial Simples. O pólo introduzido é da ordem de 8 MHz, bem inferior à freqüência do zero da saída ideal (curvas 1 e 3), em 6.9 GHz. Deste modo, para que se obtenha uma corrente de saída com bom desempenho em freqüência, devemse estudar as configurações de espelhos de corrente adequadas para tal, já que é este o fator limitante para este tipo de circuito.

Figura 1.8 - Resposta em Freqüência do Par Diferencial Simples

- (1) Transcondutância na saída do Par Diferencial Simples Entrada Balanceada

- (2) Transcondutância na saída dos espelhos de corrente Entrada Balanceada

- (3) Transcondutância na saida do Par Diferencial Simples Entrada Simples

- (4) Transcondutância na saída dos espelhos de corrente Entrada Simples

Se RS for igual a zero, a equação 1.13 prediz que o pólo é efetivamente eliminado. Porém, para valores de RS comparáveis à resistência de canal, o modelo de pequenos sinais não é mais válido. Neste caso, uma análise das resistências de canal e capacitâncias de porta mostra que existe um infinito número de pólos [6], com um pólo não dominante efetivo dado pela equação 1.16.

$$p_{eff} \approx \left[\sum_{i=2}^{\infty} \frac{1}{p_i}\right]^{-1} = 2.5\omega_T \tag{1.16}$$

onde  $\omega_T$  = gm/Cgs. Em processos de fabricação normais nos dias atuais,  $\omega_T$  pode variar de centenas de megahertz a gigahertz. Este desempenho nunca é alcançado na prática, devido à resistência associada à porta do transistor. No entanto, um alto desempenho em freqüência é obtido pelo fato de não existir nenhum nó interno que possa gerar pólos parasitas [1] (figura 1.7-a).

No caso em que a tensão de entrada é aplicada em apenas um dos transistores, estando o outro com a porta ligada ao terra, a análise de pequenos sinais é muito mais complexa, uma vez que, neste caso, a fonte dos transistores não mais pode ser considerada um terra virtual. Isto implica que o circuito é não simétrico, não podendo ser aplicado o teorema da bissecção. Qualitativamente, como existe uma variação de tensão maior na fonte dos transistores do Par Diferencial, ocorrerão efeitos de modulação de canal nos transistores que compuserem a fonte de corrente. Isto ocasionará cargas e descargas de capacitâncias associadas a estes transistores, gerando novos pólos e zeros e, por conseguinte, alterando a resposta em freqüência. No entanto, estes pólos se situam em freqüências muito superiores aos pólos gerados pelos espelhos de corrente (acima de 100 megahertz, segundo as curvas 3 e 4 da figura 1.8), fator limitante da resposta em freqüência. Novamente se vê que, *para uma melhor resposta em freqüência, deve-se melhorar o desempenho dos espelhos*.

# 1.2.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação

Outro importante parâmetro de análise de desempenho de transcondutores é a máxima variação de amplitude do sinal de entrada em relação às fontes de alimentação do circuito. Esta pode ser definida pela equação 1.17

Excursão

$$_{Vin}(\%) = \left(\frac{\left|Vid_{max} - Vid_{min}\right|}{\left|Vdd - Vss\right|}\right) 100$$

(1.17)

É importante salientar que Vin<sub>max</sub> é a tensão a partir da qual um dos transistores do Par Diferencial Simples (M1) conduz toda a corrente lss, e Vin<sub>min</sub> é a correspondente tensão a partir da qual M2 conduz toda a corrente. Portanto, estas *não são as tensões máximas e mínimas necessárias para que os transistores operem na região de saturação*.

O circuito da figura 1.3 ilustra uma situação prática em que está inserido um Par Diferencial Simples. Esta figura é repetida abaixo para facilitar o desenvolvimento deste item.

Supondo que a porta do transistor M2 esteja aterrada, que todo o sinal (Vid) seja aplicado apenas na porta do transistor M1 (entrada simples), e que toda a corrente gerada pelo transistor M3 esteja fluindo através de M1 e M4, a corrente através de M2 é zero, fazendo com que Vgs<sub>2</sub> seja igual a V<sub>T2</sub>. Como a tensão na porta do transistor M2 é zero, a tensão em sua fonte é igual a (-V<sub>T2</sub>). Sendo assim, a tensão máxima de entrada é dada por:

$$Vid_{max} = V_{T1} - V_{T2} + \sqrt{\frac{Iss}{K_1}}$$

(1.18)

Como Iss é a corrente gerada pelo transistor M3, tem-se que:

$$Iss = K_3 \left( Vbias - Vss - V_{T3} \right)^2 \tag{1.19}$$

Substituindo 1.19 em 1.18, a expressão resultante da tensão máxima de entrada é dada pela equação 1.20.

$$Vid_{max} = (Vbias - Vss - V_{T3})\sqrt{\frac{K_3}{K_1}} + V_{T1} - V_{T2}$$

(1.20)

Para se achar a tensão mínima de entrada, assume-se que toda a corrente flui através de M2 e M5. Neste caso, a corrente através de M1 é zero, de modo que  $Vgs_1 = V_{T1}$ . Pode-se, então, mostrar que:

$$Vid_{min} = -(Vbias - Vss - V_{T3})\sqrt{\frac{K_3}{K_2}} + V_{T1} - V_{T2}$$

(1.21)

Substituindo 1.21 e 1.20 em 1.17, e assumindo que  $K_1 = K_2 = K_{1,2}$ , resulta a excursão máxima de entrada em relação à fonte, dada pela equação 1.22

$$Excurs\bar{a}_{Vin}(\%) = \left[ \frac{\left| 2(Vbias - Vss - V_{T3})\sqrt{K_3/K_{1,2}} \right|}{|Vdd - Vss|} \right] \cdot 100$$

(1.22)

Deste modo, para um aumento da excursão do sinal de entrada, deve-se fazer a relação W/L do transistor M3 muito maior que a relação W/L dos transistores M1 e M2. No entanto, alguns problemas devem ser observados. Mantendo-se a tensão Vbias constante, o aumento da relação W/L do transistor M3 (o que implica um aumento da corrente lss) e/ou a redução da relação W/L dos transistores M1 e M2 só podem ser realizados até o ponto em que a tensão em suas fontes (dreno da fonte de corrente - transistor M3) seja suficiente para manter M3 saturado.

Para se ter uma idéia quantitativa, com os valores utilizados para a simulação do circuito da figura 1.3, tem-se uma excursão da entrada em relação às fontes de alimentação de 23.85%. Note que esta é a excursão máxima, sem levar em conta as não-linearidades presentes. Como já visto, para não-linearidades inferiores a 1%, a tensão de entrada deve situar-se abaixo de 20% da tensão diferencial máxima, segundo a equação 1.7. Deste modo, a excursão máxima cai para 4.77% das fontes de alimentação. De acordo com as dimensões utilizadas, fazendo com que as fontes possuam valores mínimos para que os transistores ainda operem em saturação para toda a faixa de excursão de entrada (Vdd = 2.3V, Vss = -2.8V), a excursão de entrada em relação às fontes de alimentação aumenta para 46.76%, aumentando a faixa linear para 9.35%.

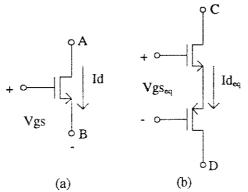

# 1.3 Par Diferencial Cruzado com Fontes de Corrente Independentes

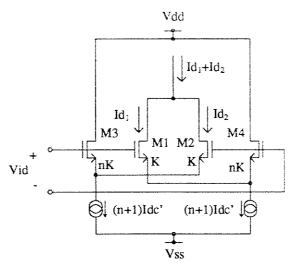

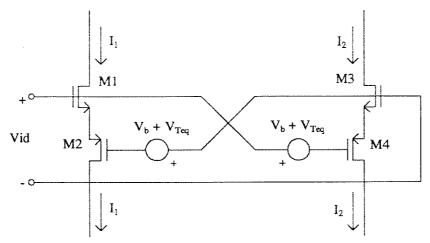

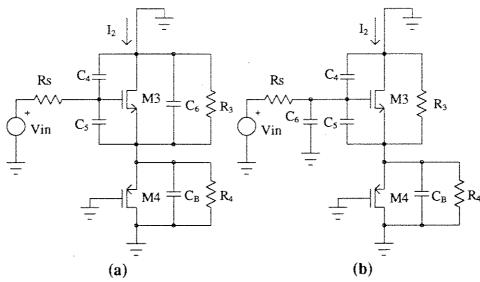

Uma grande melhora na linearidade pode ser obtida cruzando-se as saídas de dois pares diferenciais, obtendo-se na saída a diferença das correntes de cada um deles. Neste caso, utiliza-se uma fonte de corrente independente para cada par diferencial. É mostrado que, através de um escalonamento apropriado das fontes de corrente lss<sub>1</sub> e lss<sub>2</sub> e das relações W/L dos transistores, podese conseguir um cancelamento do termo de terceira ordem da expansão de Maclaurin (equação 1.8). Como este é o termo de maior contribuição para a não-linearidade de circuitos que utilizam pares diferenciais como elementos transcondutores, há uma sensível melhora na linearidade do circuito. A figura 1.9 ilustra o circuito em questão.

Novamente, este circuito apresenta as mesmas limitações em relação à saída, ou seja, a mesma é diferencial e apresenta um alto "offset" de tensão. O esquema da figura 1.2 é apropriado para levar o sinal de saída a um ponto de tomada simples e com baixo "offset".

Figura 1.9 - Pares Diferenciais Cruzados com Fontes de Corrente Independentes

#### 1.3.1 Aumento da Linearidade através de Diferença de Correntes

Utilizando a lei das correntes de Kirchhoff, e fazendo  $lout_1 = ld_1 - ld_2$ ,  $lout_2 = ld_3 - ld_4$ , da figura 1.9 pode-se facilmente deduzir que:

$$Iout = Iout, -Iout,$$

(1.23)

Deste modo, o circuito da figura 1.9 emprega diferença de correntes para conseguir um aumento na linearidade. De acordo com a equação 1.8, se os coeficientes dos termos de terceira ordem de ambos os pares diferenciais forem idênticos, e se as correntes lss<sub>1</sub> e lss<sub>2</sub> forem distintas, assim como as relações W/L de ambos os pares diferenciais, existirá um cancelamento do termo não linear de terceira ordem, sem haver o mesmo com o termo linear. Impondo estas condições, a seguinte relação deve ser satisfeita:

$$\left[\frac{(W/L)_1}{(W/L)_2}\right]^{\frac{3}{2}} = \left[\frac{Iss_1}{Iss_2}\right]^{\frac{1}{2}}$$

(1.24)

É importante ressaltar que ambas as correntes e relações de geometria dos transistores devem ser diferentes. Caso contrário, haveria também um cancelamento do termo linear. Obedecidas as condições aqui descritas, a transcondutância é agora dada por:

$$gm = \sqrt{2Iss_1K_1} - \sqrt{2Iss_2K_2}$$

(1.25)

Utilizando-se o esquema da figura 1.2, o circuito em questão foi simulado para dois níveis de modelamento dos transistores, descritos no apêndice A. Segundo os níveis de corrente Iss1 e Iss2 adotados (200  $\mu$ A e 100  $\mu$ A), segundo a equação 1.24, tem-se que a relação W/L dos transistores M1 e M2 deve ser 26% maior que a relação W/L dos transistores M3 e M4 da figura 1.9. Desta

maneira, foram adotados os seguintes parâmetros para a simulação do circuito utilizando o Par Diferencial Cruzado e espelhos de corrente:

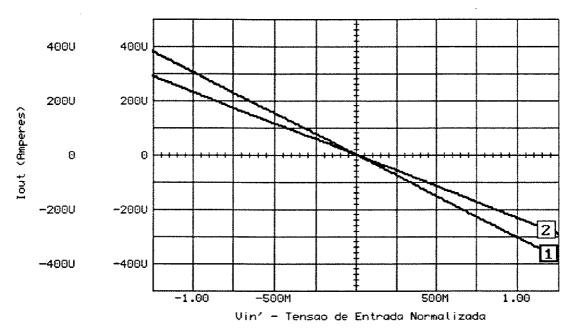

Novamente, valores não inteiros de dimensões dos transistores dos espelhos de corrente foram necessários para se minimizar o "offset" de tensão na saída. A figura 1.10 apresenta a curva de transferência do Par Diferencial Cruzado com Fontes de Corrente Independentes, na qual a tensão de entrada é normalizada por  $\sqrt{Iss_2/K_2}$ .

Figura 1.10 - Curva de Transferência do Par Diferencial Cruzado com Fontes de Corrente Independentes

(1) - Simulação com modelo MOS nível 1

(2) - Simulação com modelo MOS nível 2

É possível notar que a transcondutância da curva 2 da figura 1.10 (traço fino) é menor que a transcondutância da curva 1 (traço grosso). Isto se deve ao fato de o modelo nível 1 utilizado não contemplar a redução da mobilidade com o campo elétrico, gerado pela tensão porta-fonte dos transistores, como o faz o modelo nível 2.

Uma comparação da curva de transferência deste circuito com a curva de transferência do Par Diferencial Simples (figura 1.4) mostra claramente o aumento na linearidade obtido com a supressão do termo não linear de terceira ordem, subtraindo-se as correntes.

Sendo a transcondutância do circuito dada pela equação 1.25, tem-se a corrente de saída ideal, dada pela equação 1.26.

$$I_{linear} = \left(\sqrt{2Iss_1 K_1} - \sqrt{2Iss_2 K_2}\right) Vid \tag{1.26}$$

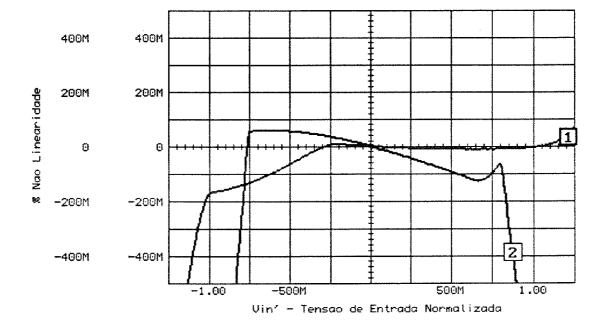

Para uma análise mais precisa, a figura 1.11 mostra a variação percentual da corrente de saída obtida em relação a um transcondutor ideal, de acordo com a equação 1.5, onde l<sub>linear</sub> é dada pela equação 1.26.

Figura 1.11 - Não-Linearidade do Par Diferencial Cruzado (1) - Simulação com modelo MOS nível 1

(2) - Simulação com modelo MOS nível 2

As curvas mostram a variação percentual da corrente de saída em relação a uma corrente linear dada pela equação 1.26. Segundo o modelo adotado e os parâmetros utilizados para simulação, a transcondutância calculada foi de 88.64 µA/V. Foi este o valor utilizado em 1.26 para a obtenção da curva 1, onde adotou-se o modelo nível 1 do transistor MOS. A transcondutância medida na figura 1.10, curva 2, foi de 82.32 µA/V, sendo este o valor utilizado para a obtenção da curva 2.

Nota-se uma significativa melhora de linearidade em relação ao Par Diferencial Simples. De uma variação máxima de 30% em relação a uma situação ideal (figura 1.5), o Par Diferencial Cruzado com Fontes de Corrente Independentes apresenta um desvio máximo em torno de 3%. Pela análise da figura 1.11 nota-se que, para um erro de linearidade menor que 1%, a tensão de entrada deve ser:

$$-0.88\sqrt{\frac{Iss}{K}} \le Vid \le 0.88\sqrt{\frac{Iss}{K}}$$

(a)

$-0.88 \le Vin \le 0.88$  (b)

Comparando a expressão 1.27 com a expressão 1.7, vê-se que houve um aumento na faixa de excursão do sinal de entrada da ordem de 440%. A não-linearidade apresentada é devido ao fato de os termos de ordem superior a 3 terem sidos desprezados na análise. É interessante notar, pela figura 1.11, que mesmo em tensões normalizadas maiores que 1  $(Vid \ge \sqrt{Iss_2/K_2})$ , a não-

linearidade ainda é baixa. Isto ocorre porque os transistores M1 e M2 ainda operam em sua região ativa.

Os resultados acima apresentados são praticamente idênticos aos obtidos para o caso de entrada simples (um dos terminais aterrados, com sinal de entrada pelo outro terminal), uma vez que a tensão Vgs dos transistores M1-M4, em ambos os casos, é a mesma. O problema maior é a variação da corrente de polarização lss, devido a efeitos de modulação de canal nos transistores que formam as fontes de corrente.

### 1.3.2 Distorção Harmônica

Segundo a equação 1.9, e lembrando que este circuito anula o termo de ordem 3, a expressão da corrente pode ser melhor aproximada por:

$$Iout = a_1 Vid + a_5 Vid^5 + \dots = a_1 Vid + \sum_{n=2}^{\infty} a_{2n+1} Vid^{2n+1}$$

(1.28)

Substituindo 1.10 em 1.28 e expandindo os termos de ordem superior, tem-se que:

$$Iout = a_1 V p \cos(\omega t) + \frac{5a_5 V p^5}{8} \left[ \cos(\omega t) + \frac{1}{2} \cos(3\omega t) + \frac{1}{10} \cos(5\omega t) \right] + \dots$$

(1.29)

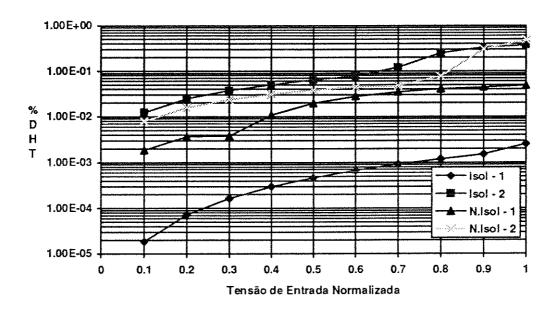

É importante lembrar que, embora haja um cancelamento do termo de ordem 3, isto não acontece com as harmônicas de terceira ordem, como mostra a equação acima. Para se verificar a distorção harmônica total obtida neste circuito, realizaram-se simulações SPICE, da mesma maneira que no item 1.2.2. A figura 1.12 reporta os resultados obtidos.

Figura 1.12 - Distorção Harmônica do Par Diferencial Cruzado com Fontes de Corrente Independentes

É possível notar que a distorção harmônica total se manteve abaixo de 1% para toda a faixa de tensão normalizada de entrada, na qual todos os transistores (M1-M4) operam em sua região ativa. Foi verificado também que componentes de terceira e quinta ordem se sobressaem, havendo um predomínio da distorção harmônica de terceira ordem na distorção harmônica total.

Novamente, deve-se lembrar que, embora as simulações predigam níveis de distorção muito baixos, em situações práticas estes níveis são dominados pelo descasamento entre os dispositivos e características intrínsecas dos mesmos, onde o projetista pouco pode influir.

### 1.3.3 Resposta em Freqüência

Como o circuito em questão é formado essencialmente por dois Pares Diferenciais Simples, e assumindo que o sinal de entrada é diferencial e balanceado, e que a impedância nos drenos dos transistores é muito baixa, segundo a equação 1.15 é possível mostrar que a função de transferência é dada por:

$$\frac{Iout}{Vid}(s) = \frac{gm_1\left(1 - s\frac{Cgd_1}{gm_1}\right)}{sRS_1\left(Cgs_1 + Cgd_1 + Cgb_1\right) + 1} - \frac{gm_2\left(1 - s\frac{Cgd_2}{gm_2}\right)}{sRS_2\left(Cgs_2 + Cgd_2 + Cgb_2\right) + 1}$$

(1.30)

Assumindo que o produto  $RS_1(Cgs_1+Cgd_1+Cgb_1)$  seja exatamente igual ao produto  $RS_2(Cgs_2+Cgd_2+Cgb_2)$ , e este seja igual a  $RS_1(Cgs_1+Cgb_2)$  e seja igual a  $RS_1(Cgs_1+Cgb_1)$  seja exatamente igual ao produto  $RS_1(Cgs_1+Cgb_1)$  seja igual a  $RS_1(Cgs_1+Cgb_1)$  seja exatamente igual ao produto  $RS_1(Cgs_1$

$$\frac{Iout}{Vid}(s) = \frac{gm\left(1 - s\frac{Cgd_1 - Cgd_2}{gm}\right)}{sRSC_T + 1}$$

(1.31)

Deste modo, o zero pode ser efetivamente eliminado se Cgd<sub>1</sub> for igual a Cgd<sub>2</sub>, ou seja, se o W dos transistores forem idênticos [9]. Qualitativamente, isto ocorre porque a corrente através de Cgd<sub>1</sub> é cancelada pela corrente através de Cgd<sub>2</sub>, de igual magnitude e fase contrária. A análise sobre o pólo e freqüência de operação é idêntica ao caso do Par Diferencial Simples, não havendo necessidade de maiores comentários.

Figura 1.13 - Resposta em Freqüência do Par Diferencial Cruzado com Fontes de Corrente Independentes

- (1) Transcondutância na saída do Par Diferencial Cruzado Entrada Balanceada

- (2) Transcondutância na saída dos espelhos de corrente Entrada Balanceada

- (3) Transcondutância na saída do Par Diferencial Cruzado Entrada Simples

- (4) Transcondutância na saída dos espelhos de corrente Entrada Simples

Foram realizadas simulações do circuito para casos em que ocorria uma manutenção de L, com W variável, e casos em que ocorria o contrário. No caso de W variável, notou-se a presença do zero. Quando se fixou o W dos transistores, o zero efetivamente desapareceu, comprovando o resultado predito pela equação 1.31, conforme as curvas 1 e 3 da figura 1.13. A influência de um sinal de entrada não balanceado também foi verificada, mostrando a existência de novos pólos e zeros em freqüências superiores aos pólos e zeros já existentes.

As considerações já realizadas no item 1.2.3 a respeito da influência dos espelhos de corrente na resposta em freqüência também podem ser aplicadas a este caso. Pela análise da figura 1.13, vêse claramente que os espelhos de corrente são o fator limitante da resposta em freqüência. Enquanto o primeiro pólo da curva 2 se situa em aproximadamente 18 GHz, o pólo da curva 1 estabelece-se em 8.5 MHz. Novamente, para um bom desempenho em freqüência, deve-se melhorar a resposta dos espelhos.

#### 1.3.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação.

Uma vez que este circuito apresenta a mesma topologia básica do Par Diferencial Simples, toda a análise realizada no item 1.2.5 pode ser repetida neste caso, não havendo necessidade de maiores detalhes sobre o equacionamento e considerações já realizadas. Deste modo, a equação 1.22 é também válida nesta situação.

Como neste caso o elemento transcondutor é formado por dois pares diferenciais simples completos, dois cálculos de variação percentual do sinal de entrada em relação às fontes de alimentação são possíveis. Neste caso, deve-se tomar o menor valor. Para o circuito simulado, segundo os parâmetros já descritos, a excursão máxima foi de 23.85% para o par diferencial composto pelos transistores M1 e M2 e fonte de corrente lss<sub>1</sub>, e de 19.04% para o par M3-M4 e fonte lss<sub>2</sub>. Sendo assim, a variação percentual máxima do sinal de entrada em relação às fontes de alimentação é de 19.04%. Lembrando-se que para uma não-linearidade abaixo de 1% a tensão de entrada deve situar-se dentro dos limites preditos pela relação 1.27, a excursão máxima cai para 16.75% das fontes de alimentação. Utilizando valores mínimos das fontes de alimentação, com Vdd igual a 2.3V e Vss igual a - 2.8V, a faixa máxima de excursão aumenta para 37.33% e a faixa linear para 32.85% das fontes de alimentação.

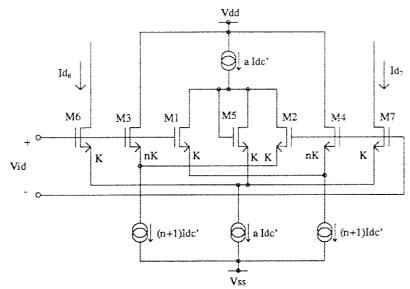

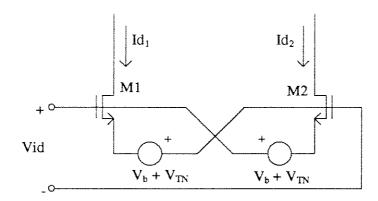

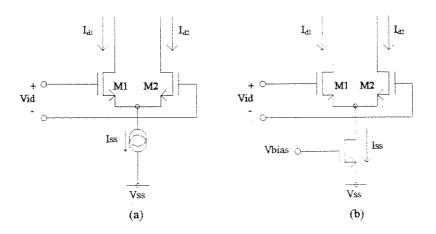

## 1.4 Par Diferencial Cruzado com Fonte de Corrente Comum

Este circuito visa mostrar uma situação em que apenas uma fonte de corrente é utilizada, como uma possível hipótese de simplificação adotada pelo projetista em relação ao Par Diferencial Cruzado com Fontes de Corrente Independentes. A figura 1.14 ilustra o circuito em questão.

É mostrado que, em comportamento de grandes sinais, este circuito se equivale a um Par Diferencial Simples, com baixa linearidade. No entanto, no que tange ao comportamento em freqüência, há uma vantagem em relação ao Par Diferencial Simples, já que é possível o cancelamento do zero presente na equação 1.31, do mesmo modo que o explicado no item 1.3.3.

Novamente, pelo fato de a corrente de saída ser diferencial, o esquema da figura 1.2 é apropriado para se obter uma saída em corrente simples, com baixo "offset" de tensão.

Figura 1.14 - Par Diferencial Cruzado com Fonte de Corrente Comum

#### 1.4.1 Não-Linearidade

O circuito da figura acima é intrinsecamente não linear, como se mostra no equacionamento apresentado neste item. Uma parcela da fonte de corrente lss é utilizada pelos transistores M1 e M2, de modo que a soma de suas correntes seja constante. A outra parcela é utilizada pelo segundo par diferencial, definido pelos transistores M3 e M4. Deste modo, a fonte de corrente lss se comporta como a soma de duas fontes de corrente.

Sejam definidas as seguintes variáveis pela análise do circuito em questão:

$$Iss_1 = Id_1 + Id_2$$

$Iss_2 = Id_3 + Id_4$

$Iout_1 = Id_1 - Id_2$

$Iout_2 = Id_3 - Id_4$  (1.32)

Pode-se mostrar facilmente que a corrente através dos transistores é proporcional à relação W/L dos mesmos. Deste modo, sendo K definido no apêndice A, tem-se:

$$\frac{K_1}{Iss_1} = \frac{K_2}{Iss_2} \tag{1.33}$$

Como a saída do circuito da figura 1.14 é equivalente à do circuito da figura 1.9, a equação 1.23 também é válida neste caso. Utilizando o conjunto de equações 1.32, e substituindo 1.1-a em 1.23, tem-se a equação que descreve o comportamento do circuito em questão:

$$Iout = \left(\sqrt{2 Iss_1 K_1} \sqrt{1 - \frac{K_1}{2 Iss_1} Vid^2} - \sqrt{2 Iss_2 K_2} \sqrt{1 - \frac{K_2}{2 Iss_2} Vid^2}\right) Vid$$

(1.34)

Substituindo 1.33 em 1.34, rearranjando-se os termos e estabelecendo-se os limites de validade, segundo 1.1, tem-se:

$$Iout = \begin{cases} \left(\sqrt{2Iss_1K_1} - \sqrt{2Iss_2K_2}\right)Vid\sqrt{1 - \frac{K_1}{2Iss_1}Vid^2} \longrightarrow |Vid| \le \sqrt{\frac{Iss_1}{K_1}}, \sqrt{\frac{Iss_2}{K_2}} & (a) \\ \left(Iss_1 - Iss_2\right)\operatorname{sgn}(Vid) \longrightarrow |Vid| \ge \sqrt{\frac{Iss_1}{K_1}}, \sqrt{\frac{Iss_2}{K_2}} & (b) \end{cases}$$

$$(1.35)$$

Desta maneira, comparando-se 1.35 com 1.1, tem-se basicamente a mesma equação de comportamento em grandes sinais, com uma redução da transcondutância. Desta forma, a curva de transferência do circuito em questão possui a mesma forma que a figura 1.4, conforme a figura 1.15. Foram utilizados os seguintes parâmetros para a simulação do circuito, utilizando-se de espelhos de correntes para levar a saída diferencial a um ponto de baixo "offset" e tomada única.

- ∀dd = Vss = 5 V

- Iss = 300 μA

- $\mathcal{F}$  (W/L)<sub>M1,M2</sub> =  $20\mu/5\mu$

- $P (W/L)_{M3,M4} = 20\mu/15\mu$

- $\mathcal{P}$  (W/L)<sub>espelho1, espelho2</sub> =  $40\mu/5\mu$

- $P (W/L)_{espelho 3} = 18.4 \mu/50 \mu$

- $\sim$  Rout = 50 $\Omega$ , Rs = 50  $\Omega$

A corrente lout representada no gráfico corresponde à diferença entre as correntes la e lb da figura 1.14. Vin representa a tensão de entrada normalizada, segundo a equação 1.2. Nota-se também que a diferença entre as transcondutâncias observadas nos outros circuitos praticamente desapareceu. Isto se deve ao fato de haver uma certa compensação devido à diferença de correntes.

Figura 1.15 - Curva de Transferência do Par Diferencial Cruzado com Fonte de Corrente Comum (1) - Simulação com Modelo MOS nível 1

(2) - Simulação com Modelo MOS nível 2

A variação percentual da corrente de saída em relação a uma corrente ideal é dada pela equação 1.5 onde, neste caso, a corrente ideal é dada por:

$$I_{linear} = \left(\sqrt{2 Iss_1 K_1} - \sqrt{2 Iss_2 K_2}\right) Vid \tag{1.36}$$

Substituindo 1.35-a e 1.36 em 1.5, a variação percentual resultante pode ser descrita por:

$$Var(\%) = \left(\sqrt{1 - \frac{K_n}{2 Iss_n} Vid^2} - 1\right) 100$$

(1.37)

onde o índice "n" pode ser 1 ou 2, uma vez que, pela relação 1.33, a razão (K/lss) é a mesma. Deste modo, fazendo Vid assumir seu valor máximo descrito pelos limites da equação 1.35, a variação percentual, segundo 1.37, é -29.29%.

A equação acima é idêntica à variação percentual do Par Diferencial Simples, segundo a equação 1.6. Desta maneira, para que a variação percentual fique abaixo de 1%, a faixa de tensão de entrada deve situar-se dentro dos limites preditos por 1.7.

A figura 1.16 mostra a variação percentual da corrente de saída em relação a uma corrente ideal descrita pela equação 1.36. Segundo os valores utilizados em simulação, a transcondutância máxima teórica  $\left(\sqrt{2\,Iss_1K_1} - \sqrt{2\,Iss_2K_2}\right)$  é de 119.96  $\mu$ A/V.

Figura 1.16 - Não-Linearidade do Par Diferencial Cruzado com Fonte de Corrente Comum

(1) - Simulação com Modelo MOS nível 1

(2) - Simulação com Modelo MOS nível 2

É possível verificar que a não-linearidade máxima da curva 1 é aproximadamente 30%, conforme o predito pela teoria. A curva 2 apresentou uma melhora na não-linearidade devido ao fato de, para tensões de entrada normalizadas próximas de 1, a corrente de saída ser maior que a do primeiro caso (figura 1.15). Isto se deve a efeitos de variação da tensão  $V_T$  do transistor devido às suas dimensões [9], que são levados em consideração apenas no modelo MOS de nível 2.

Sendo assim, se se deseja um aumento na linearidade em relação a um Par Diferencial Simples, este tipo de circuito não é apropriado, uma vez que é obtido o mesmo desempenho em grandes sinais, com um aumento de ruído envolvido, uma vez que se adicionam mais componentes.

### 1.4.2 Distorção Harmônica

Utilizando os mesmos procedimentos descritos no item 1.2.2, realizaram-se simulações para a verificação da Distorção Harmônica Total do Par Diferencial Cruzado com Fonte de Corrente Comum.

Pelo equacionamento já mostrado, é de se esperar que a DHT seja equivalente à obtida no Par Diferencial Simples, uma vez que a equação que rege o comportamento em grandes sinais de ambos os circuitos é praticamente a mesma. A figura 1.17 mostra os resultados obtidos utilizandos e modelos de simulação nível 1 e 2.

Figura 1.17 - Distorção Harmônica do Par Diferencial Cruzado com Fonte de Corrente Comum

Para a curva 1, os resultados foram essencialmente idênticos aos obtidos no Par Diferencial Simples, confirmando o acima descrito. A curva 2 mostrou uma melhora na distorção harmônica para sinais de elevada amplitude. Isto se deve ao fato de a porcentagem de não-linearidade ser menor que no primeiro caso, como mostrado na figura 1.16.

Da mesma maneira que o Par Diferencial Simples, para uma Distorção Harmônica Total abaixo de 1%, o sinal de entrada deve situar-se abaixo de 40% da tensão máxima de entrada, conforme a equação 1.14

Novamente se deve ressaltar que, em situações reais, o descasamento entre os dispositivos pode levar a níveis de distorções maiores que os resultados aqui previstos, onde o projetista pouco pode influir.

# 1.4.3 Resposta em Freqüência

A análise de pequenos sinais deste circuito é essencialmente a mesma do circuito que utiliza fontes de corrente independentes para cada par diferencial, uma vez que se assume que o sinal de entrada é diferencial e balanceado. Portanto, as fontes dos transistores podem ser considera-

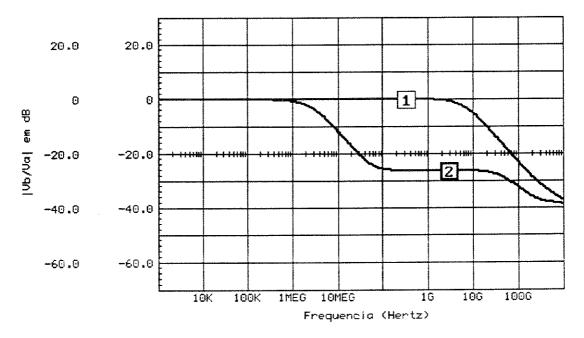

das terras AC, o que leva à mesma situação do circuito Par Diferencial com Fontes de Corrente Independentes. Sendo assim, uma vantagem em relação ao Par Diferencial Simples é a possibilidade de eliminação do zero na função de transferência descrita pela equação 1.31, conforme as condições já comentadas no item 1.3.3. Desta maneira, utilizando-se o mesmo W para ambos os pares diferenciais, a figura 1.18 mostra a resposta em freqüência obtida.

Figura 1.18 - Resposta em Freqüência do Par Diferencial Cruzado com Fonte de Corrente Comum

- (1) Transcondutância na saída do Par Diferencial Cruzado Entrada Balanceada

- (2) Transcondutância na saída dos espelhos de corrente Entrada Balanceada

- (3) Transcondutância na saída do Par Diferencial Cruzado Entrada Simples

- (4) Transcondutância na saída dos espelhos de corrente Entrada Simples

É possível verificar que, com exceção dos valores absolutos de transcondutância, a resposta em freqüência do Par Diferencial Cruzado com Fonte de Corrente Comum é essencialmente a mesma do seu similar, com fontes de corrente independentes (figura 1.13), mostrando que a análise AC de ambos os circuitos é idêntica. Novamente, o desempenho em freqüência dos espelhos de corrente é o fator limitante, uma vez que a corrente obtida na saída dos pares diferenciais praticamente não varia para sinais de entrada na faixa de freqüências de hertz a gigahertz. Sendo assim, deve-se melhorar o desempenho em freqüência dos espelhos para uma operação do circuito em altas freqüências.

As considerações a respeito de sinais de entrada não balanceados realizadas no item 1.3.3 podem ser repetidas aqui, explicando as curvas 3 e 4 da figura 1.18.

#### 1.4.4 Excursão do Sinal de Entrada em relação às Fontes de Alimentação

A mesma análise realizada no item 1.2.5 pode ser utilizada neste caso, uma vez que a topologia dos circuitos envolvidos é a mesma. Sendo assim, a variação máxima de entrada é dada pela equação 1.22.

Para os valores considerados em simulação, a excursão máxima foi de 23.9% das fontes de alimentação. Para uma não não-linearidade abaixo de 1%, este valor cai para 4.8%. Utilizando-se os valores mínimos das fontes de tensão para que todos os transistores operem na saturação, encon-

trou-se Vdd igual a 2.6V e Vss igual a -2.8V. Com estes valores, a excursão máxima aumenta para 44.3% das fontes de alimentação, e a faixa linear aumenta para 8.84%.

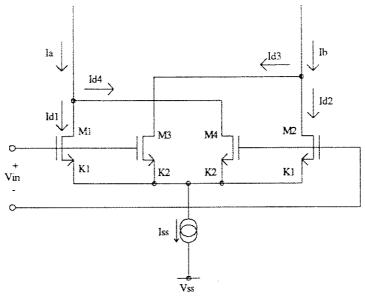

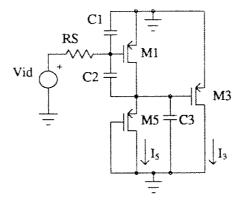

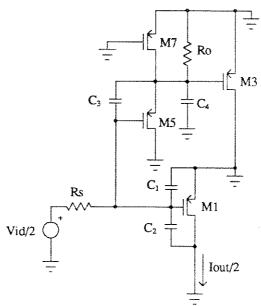

#### 1.5 Par Diferencial com Célula em Modo Corrente

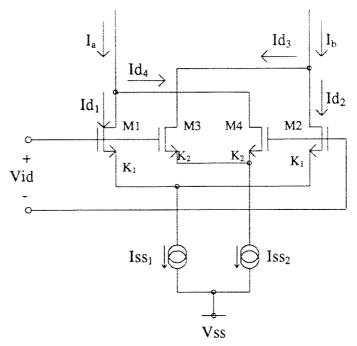

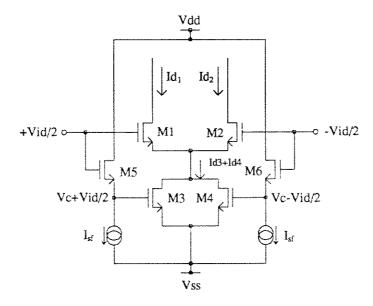

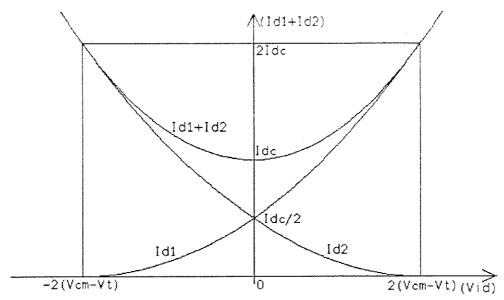

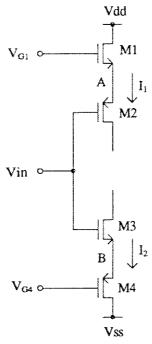

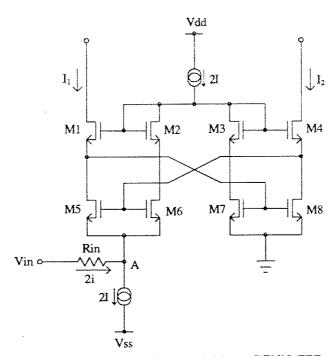

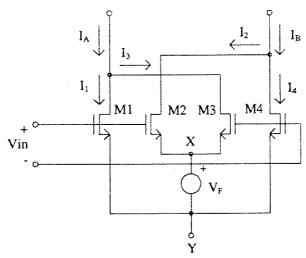

O circuito apresentado neste item apresenta, teoricamente, um cancelamento completo dos termos não lineares. Isto é obtido através da utilização de uma célula em modo corrente, correspondente aos transistores M3-M6 da figura 1.19. A corrente de entrada da célula corresponde à corrente de saída do par diferencial simples, implementado pelos transistores M1 e M2 e pela fonte de corrente. O circuito gera, então, correntes que são subtraídas das correntes de entrada, levando a um cancelamento dos termos não lineares [3].

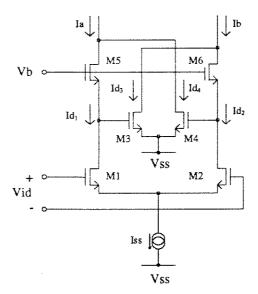

Figura 1.19 - Par Diferencial com Célula em Modo Corrente

Pela topologia do circuito, pode-se também observar que, para uma saída em corrente simples num ponto de baixo "offset" de tensão, espelhos de correntes devem ser utilizados. Neste caso, para uma manutenção da linearidade obtida, espelhos do tipo Cascode ou Wilson, ou ainda outras configurações de espelhos de corrente que apresentem melhores desempenhos, devem ser utilizados [8].

#### 1.5.1 Linearidade através de Diferença de Correntes

Através de uma análise das correntes envolvidas no circuito acima, a corrente de saída pode ser descrita por:

$$Iout = Ia - Ib$$

(a)

$Iout = (Id_1 - Id_2) - (Id_3 - Id_4)$  (b)

Utilizando-se o modelo simplificado do transistor MOS descrito no apêndice A, considerando-se todos os transistores casados, com a mesma tensão de limiar V<sub>T</sub>, operando na região de saturação, pode-se mostrar que as correntes de saída do par diferencial (Id<sub>1</sub>-Id<sub>2</sub>) e da célula em modo corrente (Id<sub>3</sub>-Id<sub>4</sub>) são dadas pelas equações 1.39 e 1.40, respectivamente.

$$Id_{1} - Id_{2} = 2K \left( \frac{Vgs_{1} + Vgs_{2}}{2} - V_{T} \right) Vid$$

(1.39)

$$Id_{3} - Id_{4} = 2K \left( \frac{Vgs_{1} + Vgs_{2}}{2} + Vss - Vb + V_{T} \right) Vid$$

(1.40)

Substituindo as equações acima na equação 1.38-b, tem-se que a corrente de saída é dada por:

$$Iout = 2K(Vb - Vss - 2V_T)Vid$$

(1.41)

Deste modo, há um cancelamento completo dos termos não lineares. Como o circuito possui um par diferencial simples em sua entrada, a faixa de excursão de sinal é a mesma dos circuitos anteriores:

$$-\sqrt{\frac{Iss}{K}} \le Vid \le \sqrt{\frac{Iss}{K}} \tag{1.42}$$

Para se calcular a tensão mínima Vb de modo que todos os transistores operem na saturação, considere-se o pior caso, em que a tensão na porta do transistor M2 da figura 1.19 é zero e a tensão na porta de M1 é igual a  $\sqrt{Iss/K}$ . Neste momento, a corrente que flui através de M1 e M5 é igual a Iss. Considerando estas condições, pode-se mostrar que a tensão Vb deve ser:

$$Vb \ge 2\sqrt{\frac{Iss}{K}} \tag{1.43}$$

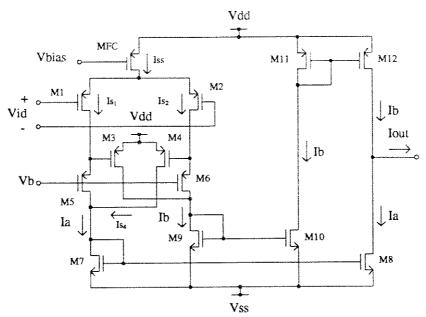

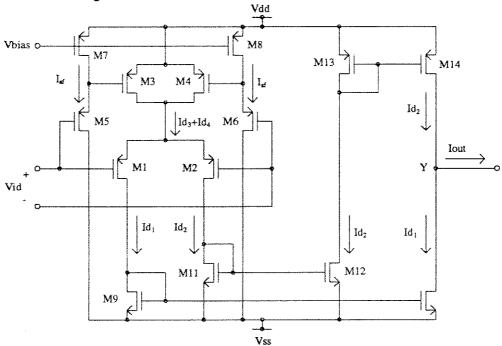

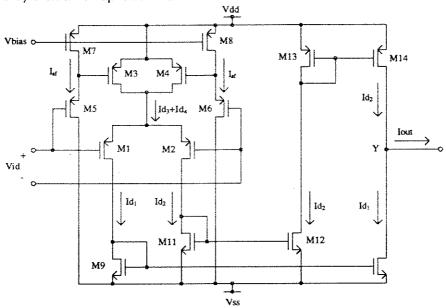

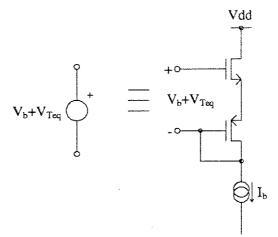

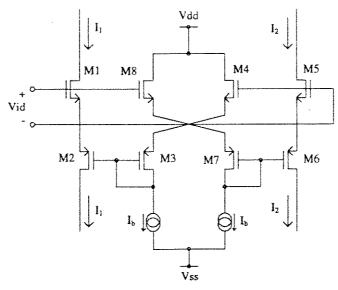

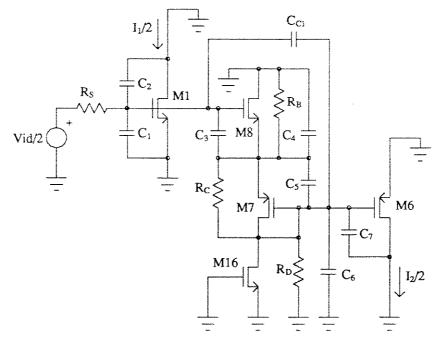

Conforme o equacionamento realizado, para o cancelamento dos termos não lineares, é necessário que todos os transistores sejam casados. Isto significa também que a tensão  $V_T$  dos transistores deve ser a mesma, o que impõe que a fonte de cada transistor deva ser conectada ao substrato. A tecnologia empregada [4] faz com que apenas os transistores canal P possam ter esta característica, uma vez que, sendo o substrato tipo P, poços N podem ser realizados para o isolamento destes transistores. Desta forma, o circuito equivalente completo, com os espelhos de corrente necessários para saída simples, é apresentado na figura 1.20.

A corrente de saída é agora dada por:

$$Iout = Ib - Ia$$

(a)

$$Iout = (Is3 - Is4) - (Is1 - Is2)$$

(b)

Equacionando o circuito do mesmo modo que no caso anterior, pode-se mostrar que a corrente de saída é agora dada por:

$$Iout = 2K(Vdd - Vb - 2|V_{TP}|)Vid$$

(1.45)

Figura 1.20 - Par Diferencial completo com Célula em Modo Corrente utilizando transistores canal P

A faixa de variação da tensão de entrada é a mesma do caso anterior, descrito pela expressão 1.42. Para o cálculo de Vb, faz-se a tensão na porta do transistor M2 igual a zero, como no caso anterior, e a tensão em M1 igual a  $-\sqrt{Iss/K}$ . Deste modo, pode-se mostrar que a tensão Vb deve ser:

$$Vb \le -2\sqrt{\frac{Iss}{K}} \tag{1.46}$$

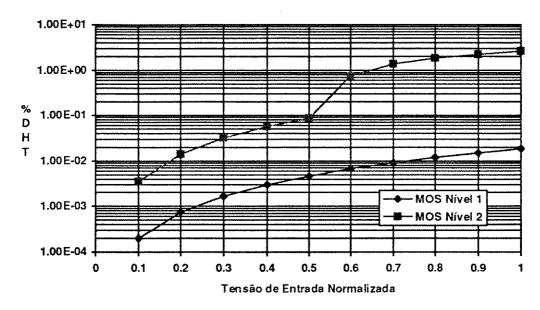

Para se verificarem os resultados preditos, realizaram-se simulações SPICE do circuito proposto na figura 1.20. Foram utilizados modelos MOS de nível 1 e 2. Foram utilizados os seguintes parâmetros:

- Vdd = Vss = 5 V

- ▼ Vb = -3.5 V

- Iss = 100 μA

- $\mathscr{F}$  (W/L)<sub>M1-M6</sub> = 20 $\mu$ /5 $\mu$

- F (W/L)<sub>MFC</sub> = 200 $\mu$ /5 $\mu$

- $\sim$  (W/L)<sub>M11-M12</sub> = 100 $\mu$ /5 $\mu$

- $\sim$  Rout = 50  $\Omega$ , Rs = 50  $\Omega$

Nos parâmetros acima, Rout é a resistência de carga no nó de saída simples, representado pela corrente lout no gráfico, e Rs é a impedância da fonte geradora de sinal. Além disso, as relações W/L dos transistores representam suas dimensões, em micras.

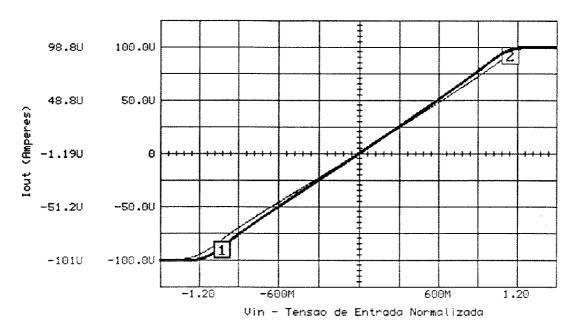

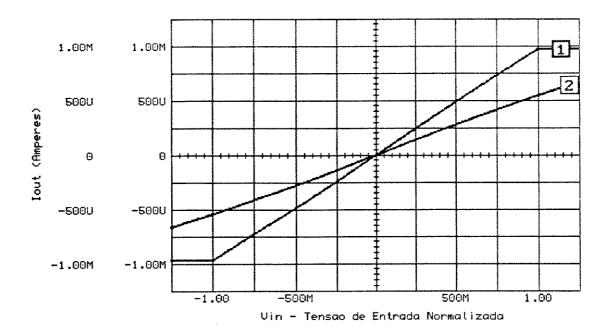

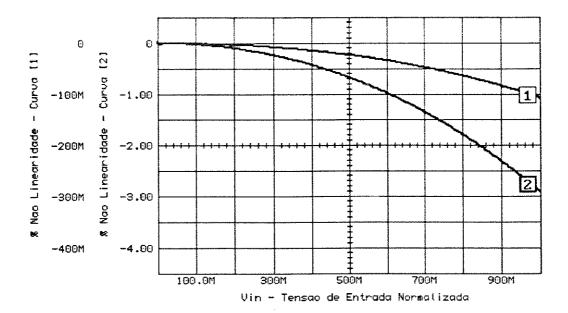

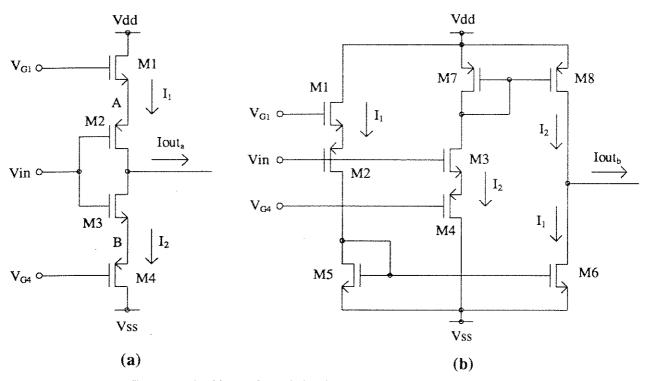

A curva de transferência DC do circuito é mostrada na figura 1.21, para o modelo "ideal" dos transistores (nível 1) e o modelo fornecido pela "foundry"[4]. No eixo "y" tem-se a diferença entre as correntes Ib e la. No eixo "x", tem-se a tensão de entrada normalizada por  $\sqrt{Iss/K}$ , conforme a equação 1.2.

Figura 1.21 - Curva de Transferência do Par Diferencial com Célula em Modo Corrente

(1) - Simulação com Modelo MOS nível 1

(2) - Simulação com Modelo MOS nível 2

A grande diferença observada na transcondutância das curvas 1 e 2 ocorre, principalmente, pelo fato de os transistores M3 e M4 possuírem uma tensão porta-fonte muito alta, fazendo com que o campo elétrico gerado pela mesma provoque uma grande redução na mobilidade dos portadores, diminuindo a corrente de saída destes transistores.

A transcondutância teórica do circuito da figura 1.20, segundo a equação 1.45, é dada por:

$$gm = 2K\left(Vdd - Vb - 2|V_{TP}|\right) \tag{1.47}$$

Com os valores utilizados em simulação, a transcondutância teórica, segundo a equação acima, é de 690.8  $\mu$ A/V, próxima à transcondutância máxima medida para a curva 1 da figura 1.21, que foi de 682.8  $\mu$ A/V. Esta discrepância é devida a pequenas variações na tensão V<sub>T</sub> dos transistores M3 e M4 devido à alta tensão porta-fonte [9]. Já a transcondutância máxima observada na curva 2 da figura 1.21 foi de 393.9  $\mu$ A/V, 57% do valor teórico.