## NOVA TÉCNICA DE CONVERSÃO ANALÓGICA-

DIGITAL NÃO-LINEAR

OSÉAS VALENTE DE AVILEZ FILHO

Compileranos o texte como complete. e aprovado

alltofo

Oséas Valente de Avilez Filho Engenheiro Eletricista, Modalidade Eletrônica - UnB-Brasília 1974 Mestre em Engenharia Elétrica - FEC/UNICAMP - Campinas 1978

# NOVA TÉCNICA DE CONVERSÃO ANALÓGICA-DIGITAL NÃO-LINEAR

Tese apresentada à Faculdade de Engenharia de Campinas como requisito parcial para a obtenção do título de Doutor em Engenharia Elétrica.

Orientador: Prof. Dr. Alberto Martins Jorge

UNIVERSIDADE ESTADUAL DE CAMPINAS

FACULDADE DE ENGENHARIA DE CAMPINAS

DEPARTAMENTO DE ENGENHARIA ELETRICA

SETOR DE ELETRÔNICA E MICROELETRÔNICA

LABORATÓRIO DE ELETRÔNICA E DISPOSITIVOS-LED

JULHO DE 1986

UNICAMP BIBLIOTECA CENTRAL Aos funcionários e pesquisadores do LED;

a outros que, com seu trabalho ou sua amizade, possibilitaram a realização desta tese;

aos amigos que participam da luta cotidiana por uma universida de melhor, mais produtiva, e democrática;

e em especial às pessoas:

Martins, Kretly, José Antonio, Horta, Corinna, Reis, Elnatan, Wilmar, Marilda, Peter, Braga, Mário, Mariano, Mammana, Irene, Paulina.

nossos mais sinceros votos de gratidão e reconhecimento.

.Este trabalho contou com apoio financeiro das seguintes institu<u>i</u> ções:

finep Telebrás

#### RESUMO

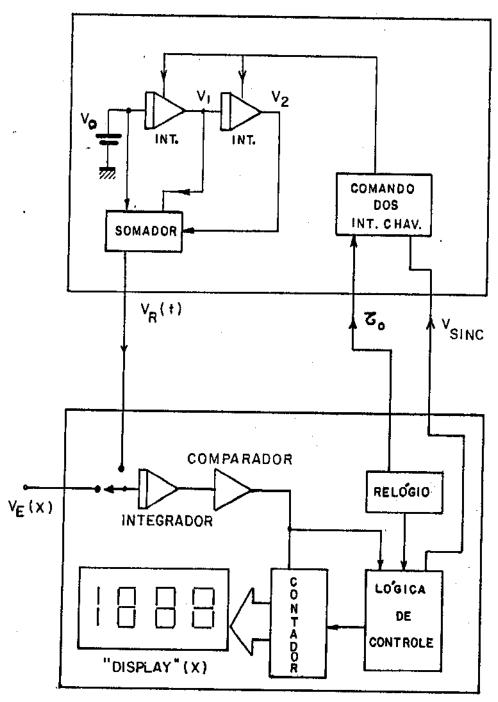

Neste trabalho apresentamos uma nova técnica de conversão A/D não linear, aplicável a conversores do tipo dupla ram pa. O trabalho envolve a generalização da técnica, um estudo particular para linearização de funções polinomiais e o projeto e construção de um conversor. Os resultados obtidos indicam grandes possibilidades de aplicação do conversor desenvolvido na confecção de equipamentos de medida e apontam para a viabilidade de se incorporar as técnicas utilizadas em circuitos integrados com tecnologia MOS.

#### ABSTRACT

A new technique for obtaining nonlinear A/D conversion with convencional dual-slope converter is presented. The work includes the generalization of the conversion method, a particular study for linearization of polinomyal functions, and the realization of a practical converter.

The results showed that the new converter can be largely used in measurement equipment, and the technique can be applied in the design of MOS monolithic A/D converters.

#### . INDICE

#### Introdução

- Capitulo I Conversor A/D Dupla Rampa

- 1.1 Princípios de Funcionamento

- 1.2 Características Principais e Limitações

- Capítulo II Nova Técnica de Conversão A/D Não-Linear

- 2.1 Princípio de Funcionamento

- 2.2 Extensão da Conversão Dupla-Rampa a Conversores Não-Lineares

- 2.3 Requisitos de  $V_{\mathrm{E}}(\mathrm{X})$  e Interpretação Gráfica

- 2.4 Generalização Conversão  $f(X) \rightarrow g(X)$

- 2.5 Geração da Referência Variante

- Capítulo III Aplicação a Funções Polinomiais

- 3.1 Linearização de Funções Polinomiais

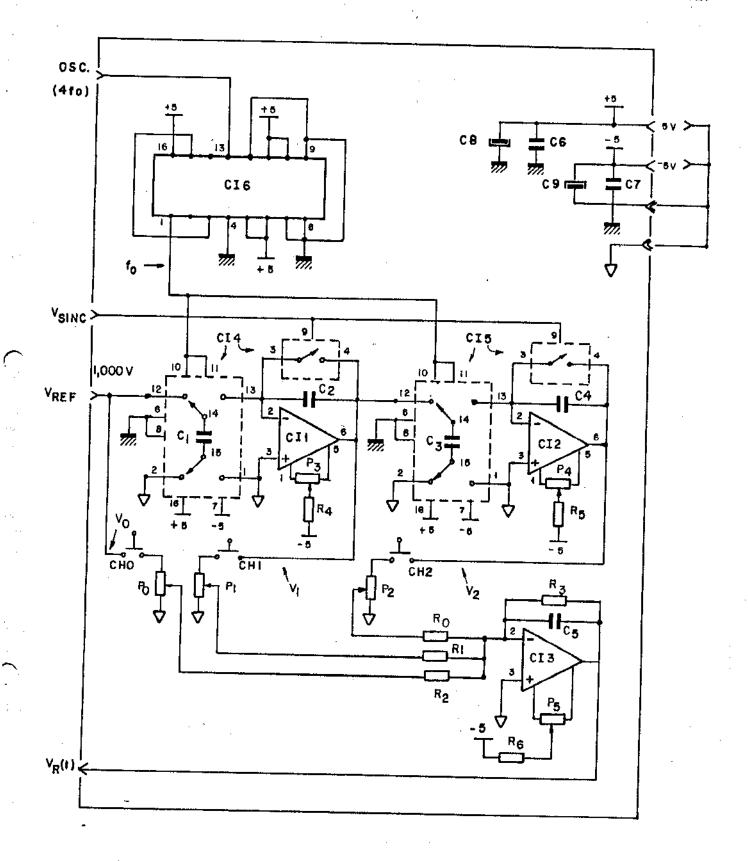

- 3.2 Geração de  $V_R(t)$  com Integradores Chaveados

- 3.3 Análise de Erros

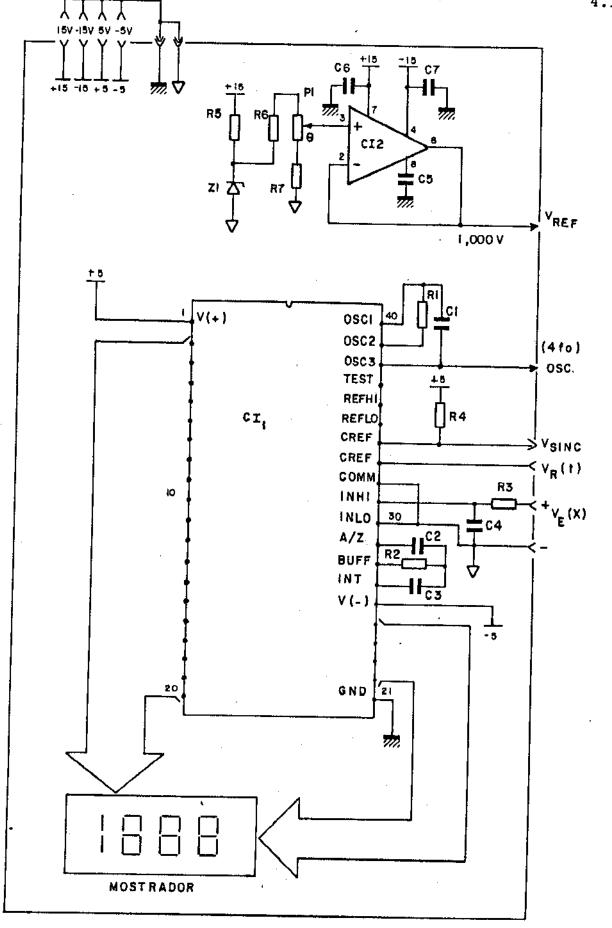

- Capítulo IV Projeto e Construção de um Conversor Não-Linear

- 4.1 Parâmetros Iniciais e Escolha da Função a Linearizar

- 4.2 O Conversor Dupla-Rampa

- 4.3 Circuitos do Conversor Não-Linear

- 4.4 Medidas e Avaliação

- Capitulo V Conclusão

- Apêndice A Referência Bibliográfica

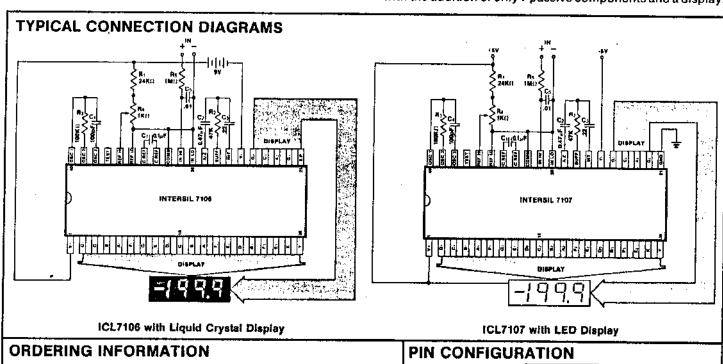

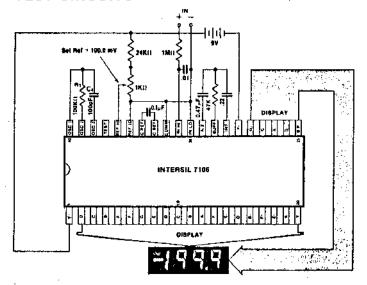

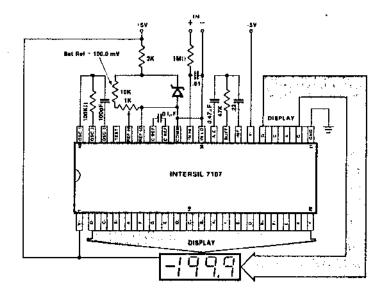

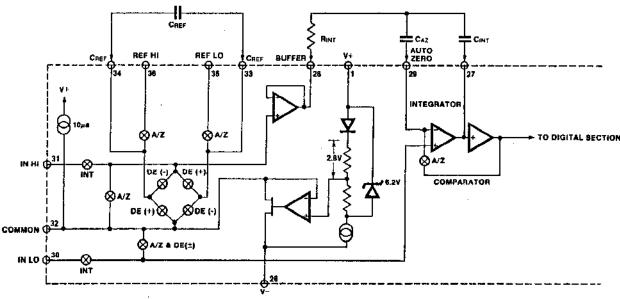

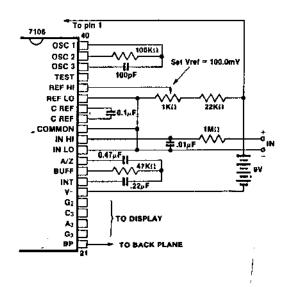

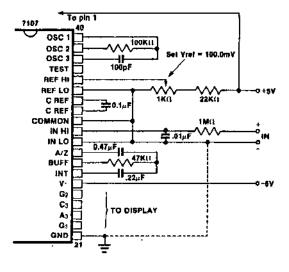

- Apêndice B Dados do Conversor ICL 7107

#### Introdução

Com a crescente utilização de equipamentos eletrôni cos para racionalizar ou ampliar as possibilidades de atividade humana, em quase todas as suas áreas, cresce também o interesse em desenvolver os mecanismos de "tradução", para a eletrônica, de informações a serem transmitidas ou processadas. Assim, dispomos hoje de um conjunto enorme de transdutores, que transformam a informação presente em sistemas físicos ou biológicos em sinais elétricos para processamento em sistemas eletrô nicos. Desta forma, informações da mais variada natureza, como temperatura, pressão, intensidade luminosa, nível, velocidade, som, concentração química, radiatividade, etc., podem ser utili zadas por sistemas eletrônicos que visam desde sua transmissão até sua utilização em sofisticados sistemas de controle. Convem ressaltar que, na maioria dos casos, a informação proveniente destes transdutores se apresenta na forma de sianis elétricos analógicos, ou seja, assumem valores em intervalos contínuos dos números reais.

Com o desenvolvimento recente da Eletrônica, através da Microeletrônica, vem se mostrando cada vez mais conveniente o processamento digital da informação, pelas facilidades que oferece do ponto de vista de armazenamento, confiabilidade e custo, como também das possibilidades de aplicação de novas téc nicas de tratamento de sinais. Nos processadores digitais mo dernos, embora a informação continue sendo de matureza elétrica, as grandezas são representadas através de um código numérico, em geral com dois símbolos (0 e 1), e passam a assumir valo res em intervalos dos números inteiros. É a informação digitalizada, que fez surgir um tipo novo (e amplamente pesquisado) de circuito eletrônico: o conversor analógico digital.

O nosso trabalho situa-se no campo dos conversores analógicos-digitais (A/D), e sua aplicação pode ser compreendida. Ocorre que boa parte dos sinais elétricos provenientes de transdutores elétricos guardam relações não-lineares com as grandezas que representam, ou seja, os gráficos que primem estas relações nem sempre são segmentos de retas. Assim, um sinal elétrico proveniente de um sensor (de temperatura, por exemplo) raramente se relaciona linearmente com a grandeza Daí surgirem métodos de linearização elétricos, que utilizam princípios os mais diversos. Uma técni ca clássica de linearizador é a que se utiliza de componentes não lineares (como diodos ou transistores) em circuitos que "com pensam" a não-linearidade do sinal, seguidos de conversores A/D quando se deseja digitalizar a informação. Outras técnicas baseiam na linearização de sinais já na forma digital, vão desde a simples consulta de tabelas armazenadas em memórias até a implementação de algorítmos numéricos, em processadores ligentes.

Uma forma um pouco menos explorada, talvez por falta de técnicas de uso geral, consiste em projetar conversores A/D cuja relação de conversão possui, intrinsecamente, as não-line aridades desejadas. Tal é o caso dos conversores utilizados para "compressão" de sinais em sistemas de comunicação.

O trabalho que descreveremos aqui constitui uma proposta de generalização da técnica de conversão analógica-digital dupla-rampa. Na técnica de conversão descrita, a relação entre o sinal analógico de entrada e o sinal digital de saída, podendo ser não-linear, permite que as operações de linearização e digitalização possam ser realizadas numa única etapa. Como ve femos também, o conversor desenvolvido permite outros tipos de aplicação, cuja exploração mais detalhada transcende os limites deste trabalho. Além da análise teórica da técnica desen volvida, construimos um equipamento nela baseado, e investiga mos aspectos da integrabilidade do circuito utilizado. Do pon to de vista de sua inserção no amplo espectro da Eletrônica por tanto, este trabalho poderia ser classificado como na interface

entre a Instrumentação Eletrônica e a Microeletrônica, que ten dem cada vez mais a se interpenetrar, pelo desenvolvimento ace lerado de novas tecnologias de integração de circuitos e sistemas.

#### CAPITULO I

#### CONVERSOR A/D DUPLA-RAMPA

## Introdução

Inúmeras são as técnicas de conversão analógico-digital utilizadas atualmente, cada uma delas apresentando características que as tornam mais ou menos adequadas a um dado tipo de aplicação |1|.

De um modo geral, podemos dizer que um compromisso básico se estabelece entre a resolução (número de bits) e o tempo de conversão (velocidade). Assim, conversores destinados a medidas com alta resolução, são em geral mais lentos do que seus equivalentes com menor número de "bits". Este é o caso dos conversores baseados em carga e descarga de capacitores, como o conversor du pla-rampa e seus derivados (rampa tripla, quádrupla, etc) |1|. Amplamente utilizados em instrumentação eletrônica de precisão, estes conversores, apesar de realizarem um pequeno número de conversões por segundo, permitem, por outro lado, alta precisão e alta resolução na conversão de sinais de muito baixa frequência.

Utilizado como base do conversor analógico-digital não linear desenvolvido e, apesar de amplamente conhecido |1|, o conversor dupla-rampa será descrito sucintamente neste primeiro capítulo, tanto para melhor entendimento do trabalho, como para esta belecer a notação adequada.

## 1.1 Princípio de Funcionamento

O conversor dupla-rampa realiza a conversão analógico-f-digital de uma tensão ( $V_E$ ) aplicada a sua entrada, através da comparação deste sinal com uma tensão de referência ( $V_R$ ) que, co mo padrão interno, é responsável pelo grau de acuidade da medida. Neste tipo de conversor, como teremos oportunidade de ver com maio res detalhes, realiza-se uma medida indireta da tensão de entrada através da relação de intervalos de carga e descarga de um capacitor.

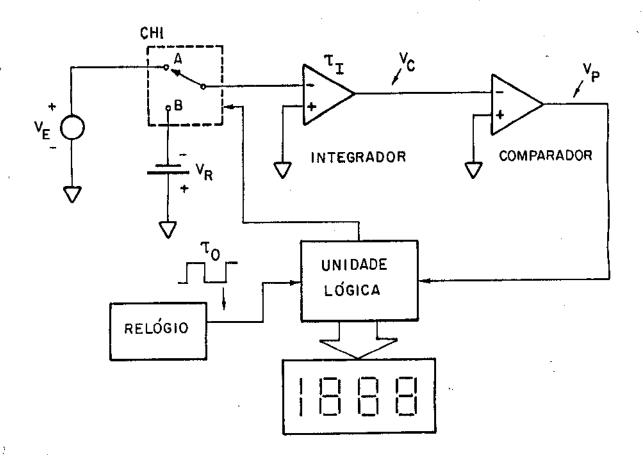

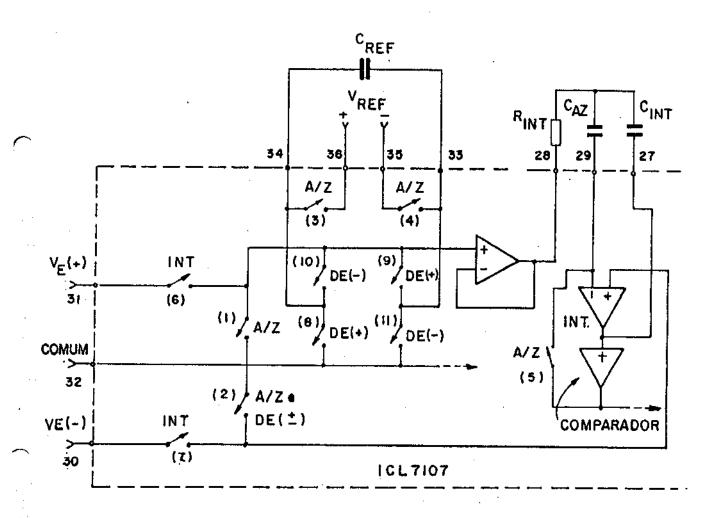

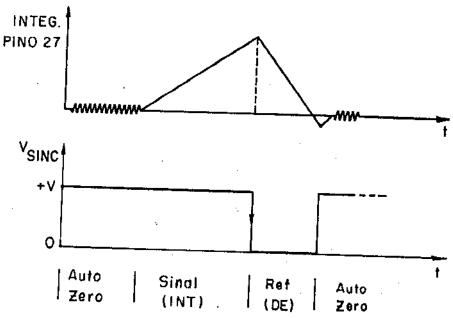

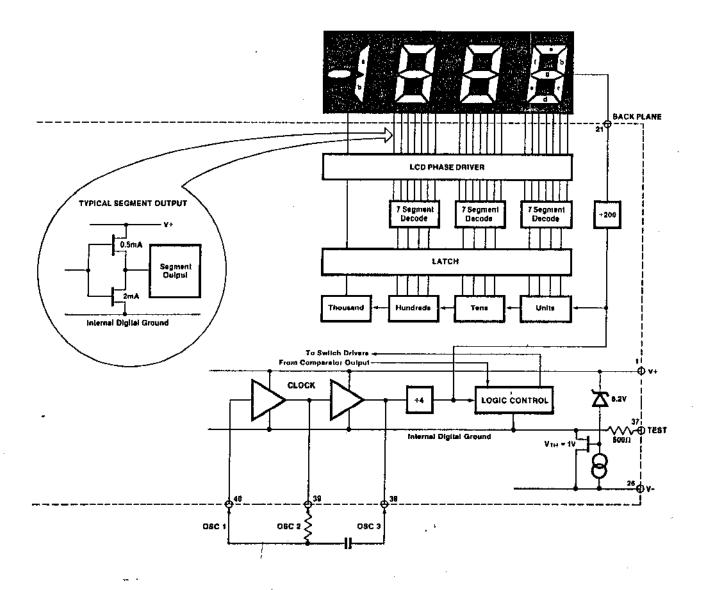

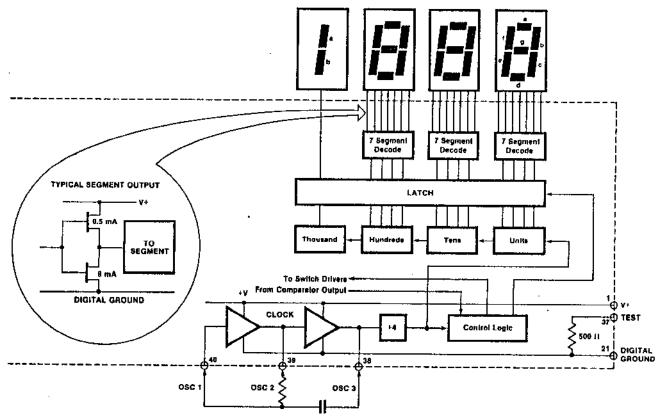

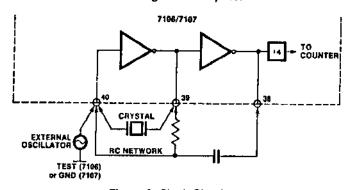

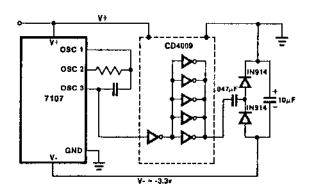

A figura 1.1 ilustra o funcionamento do conversor du pla-rampa a nível de blocos, e servirá para descrever um ciclo completo de conversão, que normalmente é repetido entre duas a cem vezes por segundo.

Para efeito da análise que se segue, os valores da tensão de entrada  $V_{\rm E}$ , bem como da tensão de referência  $V_{\rm R}$ , são admitidos invariáveis durante o intervalo de conversão.

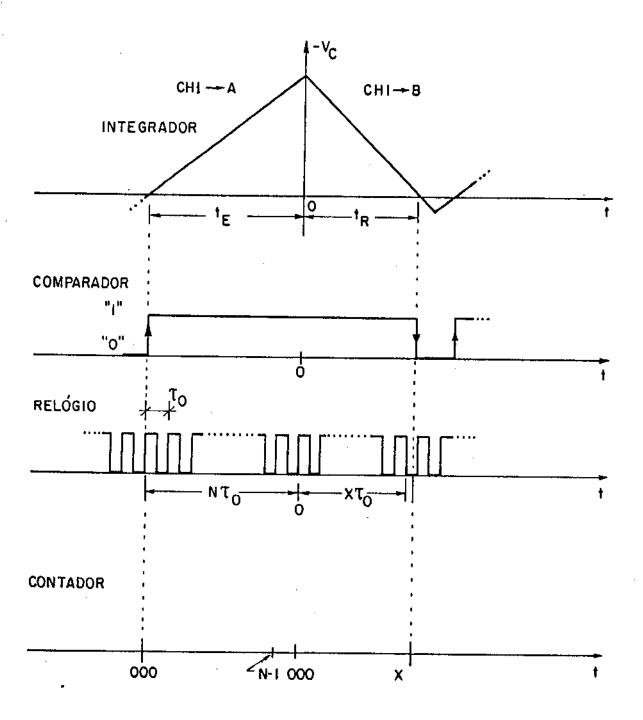

A unidade lógica mostrada na figura 1.1 é composta ba sicamente de um contador lógico e de circuitos digitais para con trole da chave CHl, além de decodificadores para apresentarem, através do "display", o resultado da conversão. Com ajuda do dia grama de tempo, mostrado na figura 1.2, podemos entender com fa cilidade o funcionamento do conversor.

O ciclo de conversão mostrado na figura 1.2 repete-se periodicamente, e inicia-se com o conteúdo do contador igual a zero. Por conveniência, o instante t=0 foi escolhido no meio do ciclo, quando o sinal aplicado à entrada do integrador muda de  $V_{\rm E}$  para  $V_{\rm R}$ , e quando o conteúdo do contador cíclico, depois de N períodos do relógio, volta a ser zero.

Tomemos uma tensão de entrada  $V_E$  positiva, ligada no instante  $t=-t_E$  à entrada do integrador, cuja saída  $V_C$   $(-t_E)=0$ . No intervalo de tempo  $[-t_E,\ 0]$  teremos:

$$V_{C}(t) = -\frac{1}{\tau_{I}} \int_{-t_{E}}^{t} V_{E} d\tau = \frac{-V_{E} \cdot \tau}{\tau_{I}} \Big|_{-t_{E}}^{t}$$

(1.1)

onde assumimos um integrador inversor com constante de tempo  $\tau_{\rm I}$ , normalmente obtida de um produto resistência x capacitância (RC). A equação 1.1 descreve portanto a rampa mostrada na figura 1.2 no intervalo entre t=-t\_E e t = 0. Teremos, portanto, no instante t = 0, uma carga armazenada no integrador, de modo que sua tensão de saída  $V_{\rm C}$  será igual a:

$$V_{C}(0) = \frac{-V_{E} \cdot t_{E}}{\tau_{T}}$$

(1.2)

4

Figura 1.1 - Diagrama funcional do conversor dupla-rampa.

Figura 1.2 - Diagrama de tempos do conversor dupla-rampa.

Como podemos perceber o tempo  $t_E$ , durante o qual o sinal de entrada  $V_E$  faz com que a saída do integrador varie linear mente de  $V_C$  = 0 até o valor  $V_C(0)$ , dado por (1.2), é fixado previamente, e corresponde a um número inteiro (N) de períodos do relógio utilizado como base de tempo, de modo que  $t_E$  = N. $\tau_0$ . Nor malmente, e como faremos neste exemplo, o número N corresponde ao valor máximo de contagens do contador cíclico, que será tam bém o maior resultado possível de uma conversão, ou ainda, o fun do de escala do conversor.

A partir do instante t = 0 (fig. 1.2), a chave CHl passa para a posição B (fig. 1.1), e a tensão de referência é ligada à entrada do integrador. Como esta tensão  $V_R$  possui polarida de oposta a do sinal  $V_E$ , a saída do integrador variará no sentido oposto, também linearmente, até cruzar o zero no instante t =  $t_R$ , como vemos no gráfico de  $V_C$ . No intervalo  $\left[0, t_R\right]$ , por tanto:

$$V_C(t) = V_C(0) - \frac{1}{\tau_I} \int_0^t V_R d\tau$$

(1.3)

Logo, como  $\mathbf{V}_{\mathbf{R}}$  é constante, teremos:

$$V_C(t) = V_C(0) - \frac{V_R \cdot t}{\tau_T} = -\frac{V_E \cdot t_E}{\tau_T} - \frac{V_R \cdot t}{\tau_T}$$

(1.4)

No instante t =  $t_R$ , quando a saída do integrador estiver cruzando o zero, ou seja,  $V_C(t_R) = 0$ , teremos o conteúdo do contador igual a um valor X, onde  $t_R = X.\tau_0$ . Neste momento, a partir da equação (1.4),

$$-\frac{\mathbf{v_E \cdot t_E}}{\tau_{\mathbf{I}}} - \frac{\mathbf{v_R \cdot t_R}}{\tau_{\mathbf{I}}} = 0 ,$$

o que implica:

$$t_{R} = \left(-\frac{t_{E}}{v_{R}}\right) \cdot v_{E} \tag{1.5}$$

De (1.5), como  $t_E$  e  $V_R$  são constantes, podemos ver que o intervalo de tempo  $t_R$ , e portanto o conteúdo do contador (X), são proporcionais à tensão de entrada  $V_E$ . Substituíndo em (1.5) os tempos  $t_E$  e  $t_R$  por seus equivalentes  $N\tau_0$  e  $X\tau_0$ , respectivamente, ficamos com a seguinte equação de projeto:

$$X = -\frac{N}{V_R} \cdot V_E \tag{1.6}$$

Na relação acima, o valor X que representa a medida de  $V_E$  mostrada através do "display", independe tanto da constante de tempo  $\tau_I$  do integrador, como também do período  $\tau_0$  do relógio, desde que constantes durante o período de conversão |1|.

Como exemplo , suponhamos um conversor de 3 1/2 dígitos, ou seja, que utiliza um contador com ciclo de 2000 contagens, e cujo "display" indicará no máximo o valor 1999. Neste caso teremos N = 2000, e se utilizarmos uma tensão de referência  $V_R = -2,000$  Volts, a partir de (1.6) o resultado da conversão será dado por:

$$X = \frac{2.000}{2.000}$$

.  $V_E = 1000 V_E$  ;  $V_E$  (Volts) (1.7)

Assim, para uma tensão de entrada de 1,257V, por exemplo, a leitura será X=1257. Se posicionarmos o ponto decimal do "display" entre os dois dígitos mais significativos, leremos diretamente o valor de  $V_{\rm E}$  em Volts.

#### Escalamento

No exemplo acima, como expressamos  $V_R$  em Volts, obtive mos X = 1000  $V_E$  como resultado da conversão. Se  $V_R$  fosse expresso em milivolts, teríamos uma leitura direta de  $V_E$ , ou seja,  $X = V_E$  (mV), sem necessidade de utilizarmos o ponto decimal. Es

ta mudança de escala, pela simples mudança do ponto decimal, pode ser realizada não só tendo como fator uma potência de dez, mas qualquer outro valor. Isto pode ser visto através da equação (1.6), que mostra que pela escolha da relação  $\rm N/V_R$  podemos mudaro ganho do conversor.

Reescrevendo a relação mostrada em (1.6) podemos dar uma outra interpretação à conversão analógica-digital:

$$V_{E} = -\frac{V_{R}}{N} \cdot X , \qquad (1.8)$$

onde X é o resultado da medida indicada no mostrador e  $V_E$ , o sinal de entrada, é expresso como uma função linear de X. Desta forma, o conversor dupla-rampa converte  $V_E(X) = KX$  em X, onde K é a constante dada por -  $V_R/N$ . Esta abordagem mostra que, se um sinal elétrico se relaciona a algum parâmetro X, através de uma relação de proporcionalidade é possível ajustar o ganho do conversor de modo a obter uma leitura direta de X. No segundo capítulo deste trabalho mostraremos como realizar esta mesma tarefa em casos onde a relação entre  $V_E$  e X não é linear, daí a interpretação, desde logo, do sinal de entrada  $V_E$  como função de X.

## 1.2 Características Principais e Limitações

Para efeito introdutório, como mencionamos anteriormente, analisaremos alguns aspectos do conversor dupla-rampa, uma vez que seu funcionamento, características e limitações são de amplo conhecimento |1| - |3|. Assim, ressaltaremos principalmente os pontos importantes para entendimento e avaliação do conversor não-linear desenvolvido.

## Imunidade a Variações do Relógio

Conforme ressaltamos no item anterior, e como fica evidente na equação (1.6)  $\left[X=-\left(N/V_R\right).V_E\right]$  o valor X, resultado da conversão, independe da freqüência do relógio utilizado, uma vez que o período  $\tau_0$  não aparece na expressão obtida. Embora is

to seja, em geral, verdadeiro do ponto de vista prático, cabe ressaltar que variações ocorridas em  $\tau_0$ , durante um perído de conversão, podem causar erros na relação entre os tempos  $t_E$  e  $t_R$  (fig. 1.2) e, portanto, na conversão realizada. Em geral as variações em  $\tau_0$  são muito lentas, como as resultantes de mudanças na temperatura ambiente, que não acarretam erros perceptíveis na conversão dupla-rampa |1|.

#### Constante de Tempo do Integrador

Da mesma forma que o perido 70, a constante de tempo do integrador  $\tau_T$  não influi diretamente no resultado da são. Dois efeitos, porém, são importantes em relação ao dor utilizado, que envolve em geral um circuito convencional, on de  $\tau_T$  se origina de um produto R.C. O primeiro efeito, que pode afetar tanto R quanto C, diz respeito a variações com a tensão estes componentes, que alteram a taxa de integração e distorcem o sinal de saída do integrador, levando a contagens erradas. segundo efeito, que envolve apenas o capacitor, é a histerese que pode aparecer no processo de carga e descarga, onde a ção ideal Q = C.V se altera, à semelhança da curva de ção de um indutor. A escolha adequada destes componentes permite reduzir a importância destes efeitos, permanecendo porém causas possíveis de não-linearidade, principalmente em converso res com faixa dinâmica larga, ou alta resolução.

#### Resolução e Sensibilidade

A resolução de um conversor A/D depende da capacidade de discernir entre níveis próximos do sinal de entrada, sendo limitada por fatores como ruído interno |1| e deriva nos valores dos componentes. Como vimos, o conversor dupla-rampa possui grande imunidade a variações de componentes, além de ser intrinsecamente pouco ruidoso, por envolver um processo de conversão lento, sem chaveamentos de corrente ou outras fontes internas de ruído. Além disso, o processo de carga e descarga implica em medida dos valores médios, quer do sinal de entrada, quer da referência, eliminando com isso grande parte das interferências causadas por sinais em freqüências elevadas, ou mesmo na freqüência da rede |3|.

J.

A capacidade de detetar e medir sinais muito pequenos, que pode ser chamada de sensibilidade do conversor, depende basicamente dos erros no processo integração do sinal de entrada. Destes o principal é a tensão residual (off-set) do amplificador que normalmente realiza o integrador. O desenvolvimento de amplificadores operacionais de alto desempenho, bem como a utilização da poderosa técnica de auto-zero, tem permitido a conversão direta de sinais da ordem de microvolts, em conversores com resolução de uma parte em cem mil ou mais. Estas técnicas de correção de zero e, portanto, de redução da deriva de zero, têm dado origem a variações do conversor dupla-rampa, envolvendo, quase sem pre, modificações no ciclo de conversão |4| - |10|.

## · Velocidade de Conversão

Talvez a única desvantagem dos conversores dupla-rampa seja a sua baixa velocidade de conversão, o que circunscreve sua utilização à medida de sinais em corrente contínua, ou que vari em muito lentamente, como sensores térmicos e outros. Esta limitação tem sua causa principal no fato de que cada período de conversão envolve um número mínimo de contagens do relógio. O aumento da frequência do relógio, para obter um maior número de conversões por segundo, impõe requisitos severos também ao comparador ("slew-rate"), que determina o início e o fim do intervalo de medida. Para um grande número de aplicações, como voltímetros e medidores em geral, a baixa velocidade não acarreta maiores problemas, o que faz do conversor dupla-rampa um dos tipos mais difundidos comercialmente.

#### Outras Caracteristicas

Um dos fatores decisivos para a ampla utilização de conversores do tipo dupla-rampa foi a possibilidade de integração, em um único circuito, de um conversor completo. Isto vem sendo facilitado pelo desenvolvimento de novas tecnologias de fabricação de circuitos integrados, particularmente com transistores MOS, pois facilitam o uso de amplificadores operacionais e chaves analógicas, o que é fundamental para a correção automática de zero, por exemplo 8.

Uma outra possibilidade importante dos conversores du pla-rampa é a de, através de algumas mudanças no ciclo de conver são, realizar o produto de dois sinais de entrada, simultaneamen te à conversão A/D, o que significa uma ampliação de suas áreas de aplicação no processamento de sinais |11|, |12|.

#### CAPÍTULO II

#### NOVA TÉCNICA DE CONVERSÃO A/D NÃO-LINEAR

#### Introdução

Os circuitos não-lineares encontram grande aplicação no processamento de sinais |13|. Utilizando frequentemente características não-lineares entre tensões e correntes em dispositivos eletrônicos, circuitos não-lineares permitem ampliar muito a possibilidade de realizar operações com sinais analógicos. Assim, se através de circuitos lineares podemos somar e subtrair sinais, amplificar, integrar e diferenciar, com o uso de circuitos não-lineares podemos acrescentar operadores como muitiplicadores, divisores, amplificadores logarítmicos, etc. |13|. Apenas para ilustrar, uma técnica muito conhecida é a que utiliza a característica exponencial de uma junção pn para calcular o logarítmo de um sinal. Somando logarítmos obtém-se o logarítmo do produto, e utilizando-se um circuito antilog podemos extrair o produto de dois ou mais sinais elétricos.

A conversão analógico-digital (A/D), como sabemos, se torna cada vez mais importante no processamento de informações, sendo desnecessário citar exemplos. Em várias aplicações, como medidores e controladores, além da conversão A/D, é também ne cessário processar não-linearmente os sinais. As formas mais i mediatas para resolver tais problemas são divididas entre as que realizam o processamento não-linear com o sinal analógico, através de circuitos não-lineares, e as que compreendem uma digitalização prévia, seguida de processamento digital.

Uma terceira forma, que exploramos neste trabalho, con siste em desenvolver conversores A/D não-lineares. Estes tipos de conversores muitas vezes realizam um tipo particular de conversão não-linear, como é o caso do conversor logarítmico des crito por S. Ben-Yaakov e J. Chen em 1978, |14|, que utiliza a curva de descarga de um circuito paralelo RC em um conversor do

J.

tipo tensão x largura de pulso.

.. 1.

Utilizando conversores dupla-rampa como sistema bás $\underline{i}$  co, devido a sua adequação a medidores de precisão, algumas téc nicas têm sido desenvolvidas, duas das quais mencionamos a seguir.

No termômetro digital modelo 2100A (Fluke) |15|, a li nearização de sinais provenientes de termopares utiliza um con versor dupla-rampa de 4 1/2 dígitos, modificado pela introdução de multiplicadores de frequência (rate-multipliers) e de memõ Este medidor realiza uma linearização por partes do si nal do termopar da seguinte forma: o relogio (clock) que ali menta o contador de pulsos do conversor dupla rampa é obtido através de um circuito multiplicador de frequência, que por vez tem seu fator de multiplicação definido por uma palavra gital armazenada em uma memória apenas de leitura (ROM). te a integração do sinal de entrada, a frequência do relógio mu da de valor, definindo os segmentos da interpolação. alimenta também um contador de segmentos que determina o endere ço da memória cujo conteúdo define a frequência do relógio. Des ta forma, a integração do sinal é realizada de forma não-line ar, programada previamente para os tipos de termopares utiliza Embora de preço elevado, este tipo de conversor bom desempenho quando o sinal a ser convertido possui não-linea ridades "suaves", podendo ser linearizado através de de reta, como é o caso da maioria dos termopares.

Um outro exemplo de utilização do princípio de duplarampa para conversão não-linear aparece em um trabalho de C.H.

Burton e outros divulgado em 1975 |11|. Os autores desenvolve

ram métodos em que, utilizando mais de um integrador no conver

sor, modificando ou criando novos estágios de carga e descarga,

ou ainda utilizando várias referências, pode-se multiplicar

dois sinais de entrada e realizar a conversão A/D do produto

ou, o que é de nosso interesse neste trabalho, realizar conver

sores A/D exponenciais, logarítmicos e ainda a extração de raí

zes de uma equação polinomial, o que equivale à conversão não-

linear de funções polinomiais. Temos neste exemplo um caso em que o processamento do sinal é essencialmente analógico, não em volvendo outras partes digitais além do contador do conversor dupla-rampa. As limitações mais importantes do método proposto por Burton estão em que, além de envolver configurações específicas para cada tipo de conversor não-linear, envolvem uma lógica de controle complexa, para chaveamento de integradores e geração das tensões de referência.

Neste capítulo descrevemos um método de conversão nãolinear que, partindo também de um conversor dupla rampa, se

constitui num método geral. Em adição a um conversor qualquer,

o método desenvolvido envolve a geração de sinais elétricos va

riante no tempo, que substituem a referência constante nos con

versores lineares. São analisadas as restrições à utilização

da técnica bem como situadas as principais características do

conversor, principalmente quando comparado aos conversores du

pla-rampa lineares.

## 2.1. Principio de Funcionamento

No capítulo I vimos que o conversor dupla-rampa realiza a conversão analógico-digital de um sinal de entrada  $V_E$ , for necendo como saída um valor X que se relaciona com  $V_E$  através da equação (1.6), que repetimos aqui para maior clareza:

$$X = \frac{-N}{V_R} \cdot V_E \tag{2.1}$$

onde:

X = Resultado de conversão;

$N = \frac{t_E}{\tau_0} = Fundo de escala do contador;$

$\tau_0$  = Período do relógio utilizado no conversor;

V<sub>D</sub> = Tensão de referência;

$V_{\rm E}$  = Tensão de entrada.

ļ

Rearrumando a equação (2.1) para isolar V<sub>E</sub> temos:

$$v_{\rm E} = \frac{-v_{\rm R}}{v_{\rm R}} \cdot x$$

ou ainda:

$$V_{E}(X) = \frac{-V_{R}}{N} \cdot X \tag{2.2}$$

Da expressão acima vemos que o conversor dupla-rampa (linear) realiza a conversão analógico-digital de  $V_E^{}(X)$  para X quando  $V_E^{}(X)$  é da forma:

$$V_{E}(X) = K.X$$

onde K é constante. Temos portanto uma conversão linear.

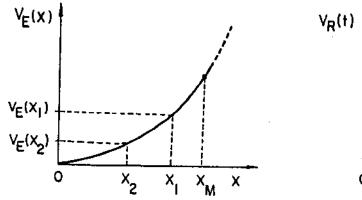

Suponhamos agora que  $V_E$ , a tensão de entrada, se relaciona com o parâmetro X através de uma função  $V_E(X)$ , e que X toma valores no intervalo  $|0,X_M|$ . Suporemos ainda que a função  $V_E(X)$  é derivâvel no intervalo de interesse, o que mais tarde veremos ser condição necessária para que  $V_E(X)$  seja convertida em X através do conversor A/D.

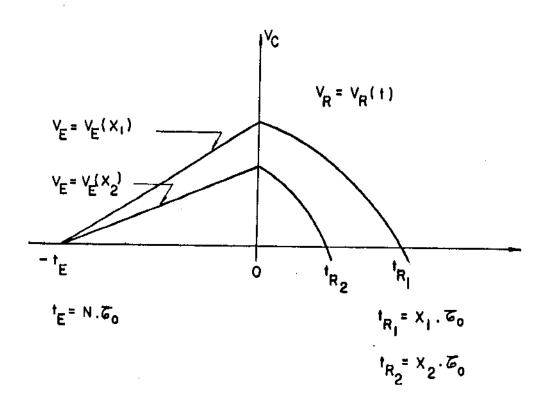

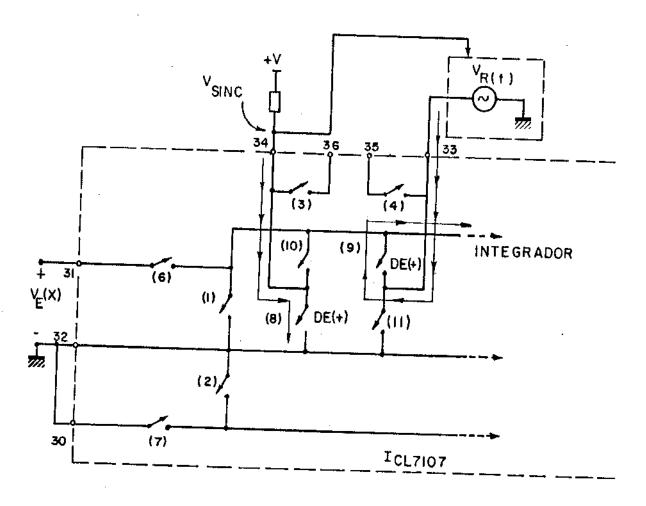

A idéia básica do conversor não-linear desenvolvido é a de que, para  $V_E(X)$  derivável no intervalo  $[0,X_M]$ , é possível converter  $V_E(X)$  em X através do uso de uma tensão de referência  $V_R$  adequada. Neste caso  $V_R$  não será mais constante, mas varia rã no tempo, durante o intervalo de conversão. Assim, a descar ga do integrador mostrada no diagrama de tempo da figura (1.2) deixará de ser uma rampa. A figura (2.1) ilustra qualitativa - mente o funcionamento do novo conversor mostrando, para uma fun ção hipotética  $V_E(X)$  não linear, a curva de carga e descarga do integrador para dois valores da tensão de entrada,  $V_E(X_1)$  e  $V_E(X_2)$ , que são convertidos respectivamente em  $X_1$  e  $X_2$ . Aqui também se supõe que a tensão de entrada se mantém inalterada du rante o período de conversão.

Л

Figura 2.1 - Conversão não-linear de  $V_{\mathsf{E}}(\mathsf{X})$  em  $\mathsf{X}.$

# 2.2. Extensão da Conversão Dupla-Rampa a Conversores Não-Lineares

Partindo da idéia geral descrita no îtem anterior  $v_{\underline{a}}$  mos agora examinar a possibilidade de gerar uma função  $V_{\underline{R}}(t)$  que, utilizada como referência variante no tempo, garanta a exata conversão de  $V_{\underline{E}}(X)$  em X para qualquer valor de X no intervalo  $[0,X_{\underline{M}}]$ . Para simplicidade de notação denominaremos  $V_{\underline{RI}}(t)$  a função integral de  $V_{\underline{R}}(t)$ .

Se repetirmos as duas fases da conversão "dupla-ram pa", utilizando  $V_E(X)$  como sinal de entrada e  $V_R(t)$  como referência, teremos (ver figuras 1.1 e 2.1).

1. Intervalo -  $t_E \leqslant t \leqslant 0$ ; CHl  $\rightarrow$  A,  $V_E(X)$  constante.

$$V_{C}(0) = \frac{-1}{RC} \int_{-t_{E}}^{0} V_{E}(x) dt = \frac{-t_{E}}{RC} \cdot V_{E}(x)$$

(2.3)

$$V_{C}(t) = V_{C}(0) - \frac{1}{RC} \int_{0}^{t} V_{R}(\tau) . d\tau$$

:

$$v_C(t) = v_C(0) - \frac{1}{RC} [v_{RI}(t) - v_{RI}(0)]$$

(2.4)

Para o instante  $t = t_R$ , em que  $V_C(t) = 0$ , teremos:

$$v_{C}(0) - \frac{1}{RC} [v_{RI}(t) - v_{RI}(0)] = 0$$

(2.5)

Substituindo (2.3) em (2.5) temos a seguinte equação:

$$-t_{E} \cdot v_{E}(x) - v_{RI}(t) + v_{RI}(0) = 0$$

(2.6)

Observemos que a equação (2.6), embora assumindo valores diferentes, vale para qualquer valor de  $V_E(X)$  no intervalo  $\begin{bmatrix} 0, X_M \end{bmatrix}$ , desde que  $V_E(X)$  seja constante durante o período de conversão. Derivando agora a equação (2.6) com relação a t, obteremos:

$$-t_{E} \frac{d}{dt} \cdot V_{E}(X) - \frac{d}{dt} V_{RI}(t) = 0 \qquad (2.7)$$

Usando a definição de  $V_{\mbox{RI}}(t)$ , como integral de  $V_{\mbox{R}}(t)$ , ficamos com:

$$v_{R}(t) = -t_{E} \cdot \frac{d}{dt} v_{E}(x)$$

(2.8)

Lembramos aqui que, embora  $V_E(X)$  tenha sido assumida constante no tempo, o instante t na equação (2.8) é o instante em que  $V_C(t) = 0$ , e portanto assumirá um valor diferente para cada valor de  $V_E(X)$ . Se neste momento, quando  $V_C(t) = 0$ , ou se ja  $t = t_R$  na figura (2.1), desejarmos que a relação ente t e  $t_E$  seja proporcional a X, ou seja  $\frac{t}{t_E} = \alpha.X$ , podemos escrever que:

$$v_{E}(x) = v_{E}\left(\frac{t}{\alpha.t_{E}}\right)$$

(2.9)

Logo, para o segundo membro de (2.8) podemos usar:

$$\frac{d}{dt} V_E(X) = \frac{d}{dt} V_E \left(\frac{t}{\alpha.t_E}\right)$$

(2.10)

Substituindo (2.10) em (2.8) podemos encontrar a função  $V_R(t)$  que satisfaz as condições impostas ou seja, que  $\frac{t}{t_E} = \alpha X \text{ quando } V_C(t) = 0:$

$$V_{R}(t) = -t_{E} \cdot \frac{d}{dt} V_{E} \left( \frac{t}{\alpha \cdot t_{E}} \right)$$

(2.11)

Lembrando que  $t_E$  ê medido em termos do período  $\tau_0$  do relótio ( $t_E = N.\tau_0$ ), escolhendo a constante  $\alpha = \frac{1}{N}$ , chegamos a uma expressão mais útil para projeto de um conversor no qual  $\frac{t_R}{\tau_0} = X$ :

$$V_{R}(t) = -N.\tau_{0} \cdot \frac{d}{dt} V_{E}(\frac{t}{\tau_{0}})$$

(2.12)

Resumindo, se a tensão de entrada do conversor está relacionada com um parâmetro X através de uma função derivável  $V_E(X)$ , podemos obter uma <u>leitura direta de X</u> se utilizarmos a tensão de referência variante no tempo dada pela equação (2.12). Nesta expressão, a função  $V_E$  é aplicada ao argumento  $(\frac{t}{\tau_0})$  e derivada no tempo, para obtenção de  $V_R(t)$ .

Exmplo 2.1 - Caso linear

$$V_E(X) = -\frac{V_R}{N} \cdot X$$

$$\begin{split} \mathbf{V}_{\mathrm{R}}(\mathrm{t}) &= -\,\mathbf{N} \cdot \boldsymbol{\tau}_{0} \cdot \, \frac{\mathrm{d}}{\mathrm{d} \mathrm{t}} \,\, \mathbf{V}_{\mathrm{E}} \,\, (\frac{\mathrm{t}}{\boldsymbol{\tau}_{0}}) &= -\,\mathbf{N} \cdot \boldsymbol{\tau}_{0} \,\, \frac{\mathrm{d}}{\mathrm{d} \mathrm{t}} \,\, \left( \frac{-\mathbf{V}_{\mathrm{R}}}{\mathbf{N}} \cdot \frac{\mathrm{t}}{\boldsymbol{\tau}_{0}} \right) = \\ &= -\,\mathbf{N} \cdot \boldsymbol{\tau}_{0} \,\, \left( \frac{-\mathbf{V}_{\mathrm{R}}}{\mathbf{N}} \,\, \cdot \, \frac{1}{\boldsymbol{\tau}_{0}} \right) \,\, = \,\, \mathbf{V}_{\mathrm{R}} \qquad , \quad \text{como seria de} \end{split}$$

se esperar.

Exemplo 2.2 -  $V_E(x) = x^3 + x$

$$V_{R}(t) = -N.\tau_{0} \frac{d}{dt} \left[ \left( \frac{t}{\tau_{0}} \right)^{3} + \left( \frac{t}{\tau_{0}} \right) \right] = -N. \left[ \frac{3t^{2}}{\tau_{0}^{2}} + 1 \right].$$

No exemplo acima vemos que, para linearização de uma função polinomial de grau 3, necessitamos gerar no tempo um polinomio de grau 2.

Cabe observar que  $V_{\rm R}(t)$ , no desenvolvimento realizado, deve ser ligada à entrada do integrador no instante t=0 ,

a cada ciclo de conversão, tendo portanto que estar sincronizada com a chave CHl (fig. 1.1), que desliga o sinal e liga a referência.

## 2.3. Requisitos de V<sub>F</sub>(X) e Interpretação Gráfica

Analisaremos agora as características necessárias à função  $V_E(X)$  para que se possa utilizar o conversor não-linear desenvolvido. No Item 2.2 trabalhamos com  $V_E(X)$  definida num intervalo  $\left[0,X_{\rm M}\right]$  onde  $X_{\rm M}$ , como resultado de uma contagem de pulsos, é um número <u>inteiro</u> positivo. Analisaremos também os casos em que o gráfico de  $V_E(X)$  se situa fora do primeiro qua drante, e faremos uma interpretação gráfica da conversão não-li near que permitirá seu melhor entendimento.

# $V_{E}(X)$ para X = 0

Seja  $V_E(X)$  derivâvel no intervalo  $[0,X_M]$ , tal que  $V_E(0) = V_{E0}$ . Lembramos novamente que o intervalo de integração do sinal é dado por  $t_E = N\tau_0$ , onde  $\tau_0$ , o período do relógio, é a unidade de tempo utilizada.

Utilizando a referência variante no tempo:

$$V_R(t) = -N.\tau_0.\frac{d}{dt} \cdot V_E(\frac{t}{\tau_0})$$

, teremos:

$$V_{RI}(t) \stackrel{\Delta}{=} \int V_{R}(t) dt = -N.\tau_{0} \int \frac{d}{dt} V_{E} \left(\frac{t}{\tau_{0}}\right) dt$$

(2.13)

Como  $V_R(t)$  será aplicada a entrada do integrador no instante t=0, a integral definida de  $V_R(t)$  terá como limite inferior t=0. Logo, (2.13) pode ser reescrita em termos dos valores 0 e t como limites de integração, de modo que:

$$V_{RT}(t) = -N.\tau_0 \left[ V_E \left( \frac{t}{\tau_0} \right) - V_E(0) \right]$$

(2.14)

onde  $V_E(0) = V_{E0}$ .

Da equação (2.6), no instante  $t = t_R$  em que  $V_C(t) = 0$ , temos:

$$V_{RI}(t_R) - V_{RI}(0) = -t_E \cdot V_E(X)$$

(2.15)

Substituindo t =  $t_R$  em (2.14) e substituindo em (2.15) temos:

$$-N.\tau_{0}\left[V_{E}(\frac{t_{R}}{\tau_{0}})-V_{E0}\right]=-t_{E}V_{E}(X)=-N.\tau_{0}.V_{E}(X) \quad (2.16)$$

o que implica que:

$$v_{E} \left(\frac{t_{R}}{\tau_{0}}\right) - v_{E0} = v_{E}(x)$$

(2.17)

Da equação (2.17) vemos que, para que  $\frac{t_R}{\tau_0} = X$ , devemos  $\underline{\text{ter }} V_{E0} = 0$ . Esta imposição não oferece problemas para efetuar a conversão quando  $V_{E0} \neq 0$ , pois podemos subtrair previamente o valor  $V_{E0}$  de  $V_{E}(X)$ , gerando uma nova função  $V_{EC}(X) = V_{E}(X) - V_{E0}$ , de modo que  $V_{CE}(0) = 0$ . Utilizando a mesma referência  $V_{R}(t)$ , teremos como resultado da conversão  $t_{R} = X\tau_{0}$ , ou  $\frac{t_{R}}{\tau_{0}} = X$ .

# Comportamento de V<sub>E</sub>(X)

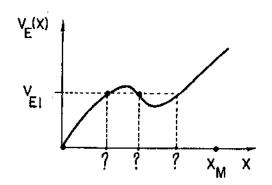

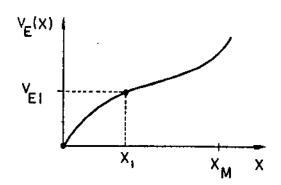

Considerando ainda uma função  $V_E(X)$  definida no intervalo  $[0,X_M]$ , com  $X_M$  positivo, além da restrição vista acima de que  $V_E(0)=0$ , uma outra restrição pade ser percebida com facilidade. É a de que, para cada valor de  $V_E(X)$  corresponda um único valor no intervalo de definição  $[0,X_M]$ , ou ainda, que  $V_E(X)$  seja biunívoca. Esta é uma decorrência do tipo de conversor (dupla-rampa) utilizado, e se estende à maioria dos conversores analógico - digitais. Neste caso, é fácil perceber que se a única informação fornecida ao conversor é um valor de  $V_E(X)$ , por exemplo  $V_{E1}$ , só existe possibilidade de obter como saída um único valor  $X_1$  tal que  $V_E(X_1)=V_{E1}$ , como ilustrado na figura

#### 2.2(a) adiante.

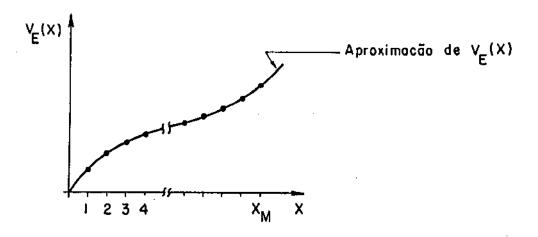

Um outro aspecto que cabe ressaltar, diz respeito fato de  $V_{\rm E}({\rm X})$  ter sido assumida inicialmente como uma função  ${\rm de}$ rivavel. De fato, como utilizamos uma referência variante tempo que é proporcional à primeira derivada de  $V_{\rm E}(X)$  , se, à primeira vista, que  $V_{\mathrm{E}}(\mathrm{X})$  deva possuir tal derivada. outro lado, se tivermos uma função  $V_{E}(X)$  e com  $V_{E}(0) = 0$ , nida apenas para valores inteiros entre 0 e X<sub>M</sub>, através de tabela por exemplo, não teria sentido deixar de realizar a versão não-linear, uma vez que apenas valores inteiros entre 0 e X<sub>M</sub> podem resultar de uma conversão A/D. Em princípio portanto, não há necessidade que  $V_{\mathrm{E}}(\mathrm{X})$  seja contínua, menos ainda deriv $\underline{ ilde{a}}$ vel, sendo suficiente encontrar uma função  $v_R^{}(t)$ , que, utiliza da como referência variante no tempo, permita a conversão  $V_{\rm E}({\rm X})$  em X para os valores em que  $V_{\rm E}({\rm X})$  é definida. Como  $V_{\rm R}({\rm t})$ será integrada no processo de conversão, será necessário apenas que sua função integral  $V_{RI}$ (t) satisfaça a equação (2.6), ou se ja, para qualquer  $X \in [0, X_M]$ :

$$-t_E V_E(X) - V_{RI}(t) + V_{RI}(0) = 0$$

,

com t no intervalo  $[0,t_M]$  onde  $t_M=\tau_0.X_M$ . Isto pode ocorrer para um conjunto não unitário de funções  $V_R(t)$ . As equações (2.7) e (2.8) e finalmente a equação (2.10), que expressam  $V_R(t)$  como função da derivada no tempo de  $V_E(\frac{t}{\tau_0})$ , foram obtidas através da derivação da equação (2.6), o que representa um artificio matemático, mais do que uma imposição de que  $V_E(X)$  seja de fato derivável.

Na realidade, se existir uma função derivâvel que coincida com  $V_E(X)$  nos pontos onde esta é definida, e cuja derivada seja fácil de calcular e sintetizar, sem dúvida esta função poderâ ser utilizada como aproximação de  $V_E(X)$  para gerar a referência (fig. 2.2(b)). Em termos de sintese do conversor, e da simplicidade da análise, é bem mais simples trabalhar com  $V_E(X)$  derivâvel. Convêm ainda ressaltar que  $V_E(X)$  biunívoca e derivã

Figura 2.2 - Requisitos de  $V_E(X)$  e  $V_R(t)$ .

vel em  $[0,X_{\rm M}]$ , com  $V_{\rm E}(0)=0$ , implica que a derivada é finita em  $[0,X_{\rm M}]$ , e que não muda de sinal neste intervalo. Suporemos ainda que  $V_{\rm E}(X)$  possui derivadas à esquerda e à direita nos pontos extremos 0 e  $X_{\rm M}$ . Como pode ocorrer que  $V_{\rm E}(X)$  seja infinita em 0 ou  $X_{\rm M}$ , como para  $V_{\rm E}(X)=+$   $X^{1/2}$ , nestes casos a referência  $V_{\rm R}(t)$  a ser gerada deve ser uma aproximação da função calculada.

Uma observação semelhante vale também para a referência variante no tempo  $V_R(t)$ . Como a referência  $V_R(t)$  será ligada à entrada do integrador, o único requisito que se impõe é que seja integrável. Como veremos mais adiante, uma forma conveniente de gerar  $V_R(t)$  é através de circuitos chaveados, que forne cem valores discretos como saída, como ilustrado na figura 2.2(c).

## $V_{\rm E}$ (X) Fora do 19 Quadrante

Até o momento trabalhamos com uma função  $V_E^{}(X)$  biunívoca definida no intervalo  $\left[0,X_M^{}\right]$  tal que  $V_E^{}(0)=0$ . Isto significa que, se  $V_E^{}(X)$  for crescente, como na figura 2.2(a), seu gráfico se situará no primeiro quadrante. Do que foi deduzido, a referência de tensão variante no tempo utilizada para converter  $V_E^{}(X)$  em X será dada por (eq. 2.12).

$$V_{R}(t) = -N.\tau_{0} \cdot \frac{d}{dt} V_{E} (\frac{t}{\tau_{0}})$$

(2.18)

Da expressão de  $V_R(t)$  vemos que, caso  $V_E(x)$  seja crescente, a derivada em (2.18) será positiva e a tensão de referência será sempre negativa. Como nenhuma restrição além de  $V_E(0) = 0$  e da biunivocidade foi imposta a  $V_E(x)$ , temos também a possibilidade de ter seu gráfico situado no 4º quadrante, ou seja, de  $V_E(x)$  ser decrescente. Neste caso sua derivada será sempre negativa. Estes dois casos podem ser ilustrados pelos exemplos a seguir, cujos gráficos de  $V_E(x)$  e  $V_R(t)$  são mostra dos na figura 2.3.

Figura 2.3 - Exemplos de  $V_{E}(X)$  no 19 e 49 quadrantes.

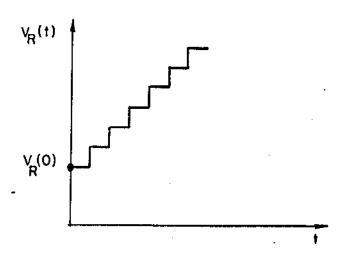

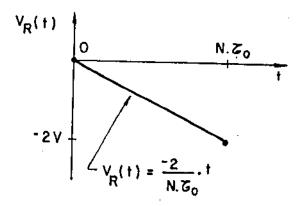

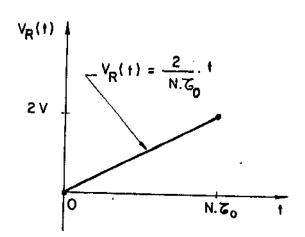

Exemplo 2.3 -

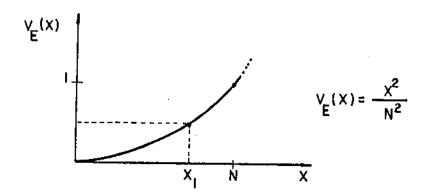

$$V_E(X) = \frac{X^2}{N^2}$$

;  $X_M = N$ ;  $V_E(Volts)$ .

De (2.18) teremos:

$$V_{R}(t) = -N.\tau_{0} \frac{d}{dt} \left(\frac{t^{2}}{N^{2}\tau_{0}^{2}}\right) = \frac{-2}{N.\tau_{0}} \cdot t \leq 0$$

(2.19)

O maior valor absoluto de  $V_R(t)$  ocorrerá para  $X = X_M$ , ou ainda para  $t_M = X_M \cdot \tau_0 = N \cdot \tau_0$ , e será:

$$v_R(t_M) = v_R(N.\tau_0) = \frac{-2}{N.\tau_0} \cdot N.\tau_0 = -2 \text{ Volts.}$$

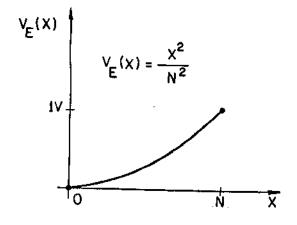

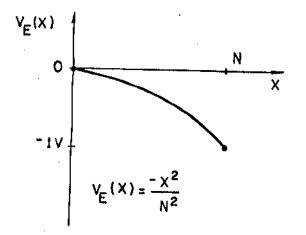

Exemplo 2.4 -

$$V_E(X) = \frac{-X^2}{N^2}$$

;  $X_M = N$ ;  $V_E$  (Volts)

:

$$V_R(t) = -N.\tau_0 \cdot \frac{d}{dt} \left( \frac{-t^2}{N^2.\tau_0^2} \right) = \frac{2}{N.\tau_0} \cdot t \ge 0 \quad (2.20)$$

E ainda:

$$V_R(t_M) = \frac{2}{N \cdot \tau_0}$$

$\cdot N \cdot \tau_0 = 2 \text{ Volts.}$

Os outros casos a analisar são aqueles em que  $V_E(X)$  é definida para valores negativos de X, ou no intervalo  $\begin{bmatrix} 0, -X_M \end{bmatrix}$ , sempre com  $V_E(0) = 0$ . Estes casos são também simples, e atra vés de (2.18) podemos ver que, para  $V_E(X) \geqslant 0$ :

- a) Se  $V_{E1}(-X) = V_{E}(X)$ , para  $X \ge 0$  ( $V_{E1}$  no 29 quadrante), teremos  $V_{R1}(t) = V_{R}(t)$ ;

- b) Se  $V_{E1}(-X) = -V_{E}(X)$ , para  $X \ge 0$  ( $V_{E1}$  no 30 quadrante), teremos  $V_{R1}(t) = -V_{R}(t)$ .

No segundo caso acima, bem como para o caso de  $V_E^{(X)}$  no 4º quadrante, deve-se utilizar o sinal de menos (-) ao apresentar o resultado da conversão em um "display", ou ainda acresentar ao conversor um "bit" de polaridade.

# $\underline{\mathbf{v}}_{E}(\mathbf{X})$ definida no intervalo $[-\mathbf{X}_{M}, \mathbf{X}_{M}]$

Como acabamos de verificar,  $V_E(X)$  pode ser definida para valores positivos ou negativos de X, sendo possível em quaisquer dos casos realizar a conversão não-linear, desde que  $V_E(0) = 0$  e que a função seja monotônica.

Os casos que estudaremos agora são aqueles em que o gráfico  $V_E(X)$  passa pela origem, do 3º parao 1º quadrante ou do 2º para o 4º quadrante. Como a referência  $V_R(t)$ , pelo próprio mecanismo de conversão, é ligada à entrada do integrador em t=0, nos casos em que  $V_E(X)$  assume valores positivos e negativos temos que dotar o conversor de um mecanismo de decisão. Se em t=0 a tensão de saída do integrador indicar que  $V_E>0$ , liga-se uma referência negativa. No outro caso, se  $V_E<0$ , uma referência positiva será utilizada para realizar a conversão. Se além de biunívoca,  $V_E(X)$  for simétrica com relação a origem, as referências positiva e negativa que mencionamos acima serão  $V_R(t)$  e  $V_R(t)$ , calculadas da forma deduzida anteriormente (eq. 2.8).

## Interpretação Gráfica

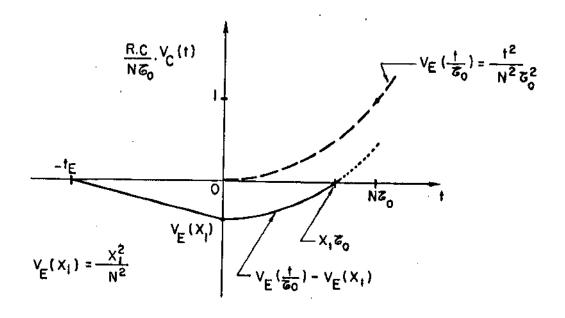

Utilizando  $V_E(X)$  biunívoca, com  $V_E(0) = 0$ , ilustrare mos um caso de conversão não-linear com  $V_E(X)$  no primeiro qua drante. Lembrando o processo de conversão, do instante  $t = -t_E = -N \cdot \tau_0$  até t = 0 temos o sinal  $V_E(X)$  ligado à entrada do integrador, de modo que:

$$V_{C}(0) = \frac{-N \cdot \tau_{0}}{RC} \cdot V_{E}(X)$$

(2.21)

Para t > 0 teremos a referência  $V_R(t)$  conectada ao integrador, que terá como saída:

$$V_C(t) = V_C(0) - \frac{1}{RC} \int_0^t V_R(\tau) d\tau, \quad t > 0$$

(2.22)

Como conhecemos  $V_R(t)$ , podemos utilizar:

$$\int V_{R}(t) dt = \int -N.\tau_{0} \frac{d}{dt} \cdot V_{E}(\frac{t}{\tau_{0}}) dt = -N.\tau_{0}.V_{E}(\frac{t}{\tau_{0}})$$

(2.23)

Como  $V_E(0) = 0$ , das equações (2.21) e (2.22) temos:

$$V_{C}(t) = \frac{-N.\tau_{0}}{RC} \cdot V_{E}(X) + \frac{N.\tau_{0}}{RC} \cdot V_{E}(\frac{t}{\tau_{0}})$$

(2.24)

ou ainda, reescrevendo:

$$\frac{RC}{N \cdot \tau_0} \cdot V_C(t) = V_E(\frac{t}{\tau_0}) - V_E(X)$$

(2.25)

Da expressão acima vemos que, como  $V_E(X)$  é constante durante o período de conversão, o segundo termo de (2.25) exprime uma função no tempo cujo grâfico reproduz o gráfico de  $V_E$  deslocado do valor  $V_E(X)$ , para cada valor de X. Esta interpretação gráfica está mostrada na figura 2.4, onde a função utilizada é a mesma do exemplo (2.3), qual seja,  $V_E(X) = \frac{X^2}{N^2}$ .

Figura 2.4 - Interpretação gráfica:  $V_E(X) = \frac{X^2}{N^2}$ ;  $0 \le X \le N$ .

### 2.4 - Generalização-Conversão f(X) → g(X)

A conversão não-linear estudada até aqui se aplica basicamente ao caso em que o sinal de entrada do conversor A/D precisa ser linearizado com relação a um parâmetro X. Assim, vimos como modificar um conversor dupla-rampa de modo a converter uma função biunívoca  $V_E(X)$  em X, o que equivale dizer que tal conversor opera a aplicação inversa de  $V_E(X)$ . Lembramos aqui que a condição necessária para existência da função inversa é que a função em questão seja biunívoca.

Utilizando o mesmo princípio de conversão, trataremos agora do caso geral onde uma função "aplicada" à entrada do conversor será transformada em uma outra função na saída. Para este caso, denominaremos f(X) o sinal de entrada, g(X) o sinal de saída, sendo f(X) e g(X) funções biunívocas definidas no intervalo  $[0,X_M]$  de modo que f(0) = g(0) = 0.

Repetindo os ciclos de conversão, com f(X) como sinal de entrada e  $V_R(t)$  como referência teremos (ver fig. 1.1):

1. Intervalo -  $t_E \le t \le 0$ ; CH1  $\rightarrow$  A;  $V_E = f(X)$ .

$$v_C(0) = -\frac{t_E}{RC} \cdot f(X)$$

(2.26)

2. Intervalo 0  $\leq$  t  $\leq$  t<sub>R</sub>; CH1 + B; V<sub>R</sub> = V<sub>R</sub>(t)

$$V_C(t) = V_C(0) - \frac{1}{RC} [V_{RI}(t) - V_{RI}(0)],$$

(2.27)

onde  $V_{RI}(t)$  é a função integral de  $V_{R}(t)$ .

Em t =  $t_R$ , quando  $V_C(t)$  = 0, queremos que o conteúdo do contador, que exprime o resultado da conversão, seja igual ag(X), ou ainda  $\frac{t_R}{\tau_0}$  = g(X). Utilizando ainda  $t_E$  = N. $\tau_0$ , a partir de (2.27) teremos:

$$-N.\tau_0.f(X) - V_{RI}(t) + V_{RI}(0) = 0$$

(2.28)

Como g(X) é biunívoca podemos definir  $g^{-1}(X)$  como a função inversa de g(X), de modo que:

$$g^{-1}[g(X)] = g^{-1}(\frac{t}{\tau_0}) = X$$

(2.29)

Utilizando (2.29) para reescrever f(X) ficamos com:

$$f(X) = f\left[g^{-1}\left(\frac{t}{\tau_0}\right)\right] \tag{2.30}$$

Substituindo f(X) acima em (2.28) e derivando com relação a t podemos obter  $V_R(t)$  como:

$$V_{R}(t) = -N.\tau_{0} \cdot \frac{d}{dt} f. \left[g^{-1}(\frac{t}{\tau_{0}})\right], \qquad (2.31)$$

que é uma expressão geral, à semelhança da equação (2.12) que vínhamos utilizando até agora.

Exemplo 2.5:

$$f(X) = \frac{X^2}{N^2}$$

;  $g(X) = X$

Temos aqui o mesmo caso do exemplo (2.3), onde queremos transformar f(X) em X, ou seja, linearizar f(X). A inversa de g(X) serā:

$$g^{-1}(X) = X : g^{-1}(\frac{t}{\tau_0}) = \frac{t}{\tau_0}$$

, e (2.32)

$$f\left[g^{-1}(\frac{t}{\tau_0})\right] = \frac{t^2}{N^2 \cdot \tau_0^2}$$

Logo:

$$v_{R}(t) = -N.\tau_{0}. \frac{d}{dt} \left(\frac{t^{2}}{N^{2}.\tau_{0}^{2}}\right) = \frac{-2t}{N.\tau_{0}}$$

que é a mesma referência do exemplo (2.3).

Exemplo 2.6:

$$f(x) = \frac{x}{N}$$

;  $g(x) = \frac{x^2}{N^2}$

$$g^{-1}(X) = N X^{1/2} : g^{-1}(\frac{t}{\tau_0}) = N \cdot (\frac{t}{\tau_0})^{1/2}$$

$$\therefore f\left[g^{-1}(\frac{t}{\tau_0})\right] = (\frac{t}{\tau_0})^{1/2}, \text{ de onde podemos calcular:}$$

$$V_R(t) = -N.\tau_0 \frac{d}{dt} \left(\frac{t}{\tau_0}\right)^{1/2} = -\frac{N}{2} \cdot \left(\frac{t}{\tau_0}\right)^{1/2}$$

(2.33)

$$V_{RI}(t) = -N.\tau_0^{1/2}.t^{1/2}$$

(2.34)

Utilizando (2.28) para  $t = t_R$  teremos:

$$-N.\tau_0.\frac{X}{N}+N.\tau_0^{1/2}.t_R^{1/2}=0$$

$$\frac{t_R}{\tau_0} = \frac{x^2}{N^2} = g(X), \text{ como esperado.}$$

Escolhemos as funções do exemplo acima para mostrar, além do caso geral de conversão de f(X) em g(X), um caso em que  $V_R(t)$  tende para infinito para t=0, como pode ser observado em (2.33). Neste caso, como já mencionamos deve-se escolher uma função  $V_R(t)$  que seja uma boa aproximação da função calculada, tende do-se em conta que sua integral entre 0 e té que determinarão o instante  $t_R$  onde termina o ciclo de conversão. Assim, vemos que em (2.34), para  $\frac{t}{\tau_0}=1$  temos  $V_{RI}(\tau_0)=-N.\tau_0$ , o que implica que podemos usar uma função  $V_R(t)$  cuja integral entre 0 e  $\tau_0$  seja dada por (2.34), sem necessariamente tender a infinito para t=0.

### O caso $X \rightarrow g(X)$

Além da linearização de funções, uma aplicação que merece

destaque  $\tilde{e}$  a geração de uma função não-linear, que aparece aqui como caso particular da conversão  $f(X) \rightarrow g(X)$ , em que f(X) = X. De (2.30) temos:

$$f\left[g^{-1}(\frac{t}{\tau_0})\right] = g^{-1}(\frac{t}{\tau_0}).$$

Logo, para f(X) = X utilizamos a referência:

$$V_{R}(t) = -N.\tau_{0} \frac{d}{dt}.g^{-1}(\frac{t}{\tau_{0}})$$

(2.35)

#### Escalamento

Em muitos casos as limitações de tensão de entrada de um conversor A/D nos obrigam a atenuar o sinal a ser convertido. Para os conversores lineares este escalamento é realizado através da tensão de referência  $V_R$ , que estabelece o ganho do conversor (lembrar da eq. (1.6) que  $X=\frac{-N}{V_R}$ ,  $V_E$ ). Em um conversor não-linear, não só o sinal de entrada deve ser mantido dentro de limites, como também a referência variante no tempo  $V_R$ (t) deve ser tal que possa ser sintetizada com facilidade. Este não é o caso quando a função f(X) possui derivada muito elevada, necessitando portanto de  $V_R$ (t) com valores também elevados. Analisaremos aquio caso em que uma função  $f_1$ (X) se relaciona porporcionalmente com f(X), de modo que:

$$f_1(x) = \frac{f(x)}{\kappa}$$

, onde K é constante.

A conversão  $f_1(X) \rightarrow g(X)$  utilizará a referência obtida a partir da equação (2.31), ou seja:

$$\nabla_{R_1}(t) = -N \cdot \tau_0 \cdot \frac{d}{dt} f_1 \left[ g^{-1} \left( \frac{t}{\tau_0} \right) \right] = \frac{-N \cdot \tau_0}{K} \cdot \frac{d}{dt} \cdot f \left[ g^{-1} \left( \frac{t}{\tau_0} \right) \right],$$

o que mostra que, para  $f_1(x) = \frac{f(x)}{K}$ , temos:

$$V_{R_1}(t) = \frac{V_R(t)}{K}$$

(2.36)

Vemos a partir de (2.36) que o mesmo fator de escala aplicado a f(X) deve ser aplicado à referência  $V_R(t)$ . O mesmo não acontece quando aplicamos um fator de escala à função de saida g(X), como veremos a seguir. Suponhamos  $g_1(X)$  uma função tal que  $g_1(X) = \frac{g(X)}{K}$ , onde g(X) é biunívoca com g(0) = 0. Sendo  $g_1^{-1}(X)$  a inversa de  $g_1(X)$ , podemos escrever:

$$g_1[g_1^{-1}(X)] = X.$$

(2.37)

Da definição de  $g_1 (= \frac{g}{K})$  vem:

$$\frac{g\left[g_1^{-1}(X)\right]}{K} = X \Longrightarrow g\left[g_1^{-1}(X)\right] = KX \tag{2.38}$$

Aplicando  $g^{-1}$  de ambos os lados de (2.38) chegamos a:

$$g_1^{-1}(X) = g^{-1}(KX)$$

. (2.39)

Como na conversão de f(X) em  $g_1(X)$  utilizaremos a inversa de  $g_1$  (ver 2.35), o escalamento de g(X) por um fator  $\frac{1}{K}$  levarã à referência:

$$V_{R_1}(t) = -N.\tau_0.\frac{d}{dt} f[g^{-1}(KX)].$$

(2.40)

## 2.5 Geração da Referência Variante

Como foi visto no capítulo I (ítem 1.2), uma das principais vantagens da técnica de conversão dupla-rampa é realizar a comparação entre duas tensões pela medida da razão entre dois intervalos de tempo ( $t_E$  e  $t_R$ ), sem contudo utilizar um padrão pre

ciso de unidade de tempo. Esta característica, denominada imunidade ao relógio, não é tão simples de ser obtida em um conversor não-linear, uma vez que a referência variante no tempo deve ter um comportamento bem definido e sua variação no tempo depende de  $\tau_0$ . No caso da conversão de f(X) em X, como vimos, teremos  $V_R(t)$  dada por (da eq. 2.31):

$$V_{R}(t) = -N.\tau_{0} \cdot \frac{d}{dt} f(\frac{t}{\tau_{0}}),$$

(2.41)

onde  $\tau_0$  é o período do relógio utilizado para contagem de tempo. Podemos ver claramente que, dada uma função f(X), e escolhido um valor para  $\tau_0$ ,  $V_R(t)$  deve ser gerada exatamente como em (2.41), in dicando a dependência da conversão com o período do relógio. Vere mos isto com mais nitidez através do exemplo a seguir:

Exemplo 2.7:

$$f(X) = (1 - e^{\frac{-X}{N}})$$

(Volts)

De (2.41) podemos obter:

$$V_{R}(t) = -N.\tau_{0} \frac{d}{dt} (1 - e^{-t}) = (1 - e^{-t}) - 1 \text{ (Volts)}$$

(2.42)

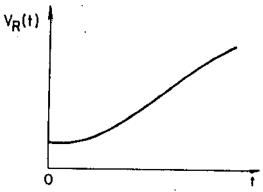

A exponencial obtida em (2.42) deve ser gerada periodicamente, em cada ciclo de conversão, a partir do instante t=0 (ver fig. 2.1). Esta função pode ser facilmente obtida pela carga de um capacitor C através de um resistor R de modo que o produto RC seja igual à constante de tempo  $\tau=N.\tau_0$  da exponencial. Subtraindo uma tensão constante da tensão sobre o capacitor obtemos a função calculada em (2.42). Como vemos, utilizando o produto RC fixo e igual a  $N.\tau_0$ , se houver alguma variação na frequência do relógio a conversão se alterarã, ocasionando erros no resultado.

A solução mais aparente para este problema consistiria em utilizar um relógio estável, obtido por exemplo de um oscila dor a cristal. Além do evidente aumento de custo e complexidade do circuito, para modificar a taxa de conversão necessitaríamos

recalcular a referência variante e modificar valores de componentes. Optamos por uma técnica diferente, que utiliza funções no tempo geradas a partir de circuitos a capacitores chaveados, cujo princípio de funcionamento está descrito sucintamente no capítulo 3. Desta forma, como veremos no decorrer do trabalho, é possível gerar uma referência variante  $V_R(t)$  que se adapta automaticamente no caso de ocorrerem variações na frequência do relógio. No capítulo VI mostraremos também que esta técnica torna o conversor não -linear passível de integração, o que o torna muito conveniente em algumas aplicações.

Para concluir este capítulo, veremos no item a seguir a aplicação desta técnica à conversão da função utilizada no exemplo anterior (exemplo 2.7).

### Utilização de Circuitos a Capacitores Chaveados

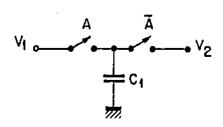

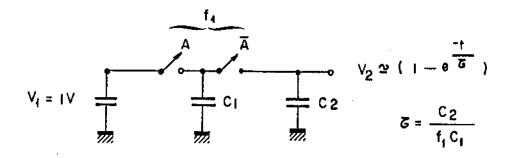

Vimos no exemplo 2.7 que, para realizar a conversão de f(X) em X será necessário gerar a exponencial mostrada em (2.42), cuja constante de tempo  $\tau = N.\tau_0$  depende claramente a frequência  $f_0$  (= 1/ $\tau_0$ ) do relógio principal do conversor. Para ilustrar a geração de  $V_R$ (t) utilizando capacitores chaveados utilizaremos o circuito mostrado na figura 2.5(a), cujo princípio de funcionamento resumiremos a seguir.

As chaves analógicas mostradas na figura fecham e abrem alternadamente, comandadas pelos sinais A e  $\overline{A}$  numa frequência que chamaremos  $f_1$ . Quando a chave da esquerda está fechada, o capacitor  $C_1$  é carregado com  $V_1$ . A seguir o estado das chaves é invertido e  $C_1$  se descarrega por  $V_2$ . A quantidade de carga que flui para (ou de)  $V_2$  será então |16|:

$$Q = C_1 (V_2 - V_1)$$

(2.43)

Se as chaves são ligadas e desligadas a cada  $T_1$  segundos, onde  $T_1 = 1/(f_1)$ , a corrente (carga por unidade de tempo) que flui de  $V_1$  para  $V_2$  serã dada por:

(a) "Resistor" a capacitor chaveado.

(b) Geração de exponencial.

(c) Geração de  $V_R(t)$ .

Figura 2.5 - Referência com Capacitores Chaveados.

$$i = \frac{C_1 (V_2 - V_1)}{T_1}$$

(2.44)

A função desempenhada pelo capacitor e pelas chaves an<u>a</u> logicas  $\ddot{e}$  a de um "resistor" ligado entre  $v_1$  e  $v_2$ , com valor equ<u>i</u> valente a:

$$R = \frac{T_1}{C_1} = \frac{1}{f_1 C_1}$$

(2.45)

Esta aproximação é válida para  $f_1$  bem maior que as frequências de interesse presentes em  $V_1$  e  $V_2$ . Utilizando o "resistor" da figura 2.5(a) podemos gerar uma exponencial utilizando o circuito da figura 2.5(b), onde teremos:

$$v_2(t) = (1 - e)$$

(2.46)

Substituindo R pelo valor mostrado em (2.45) obtemos a constante de tempo  $\tau = RC_2$  que, como vimos, deve ser iguala N. $\tau_0$ , ou seja:

$$\tau = R.C_2 = \frac{C_2}{f_1.C_1} = N.\tau_0 = \frac{N}{f_0}$$

(2.47)

De 2.47 podemos ver que, se o sinal de controle das chaves for derivado do relógio principal, de forma que  $f_1 = f_0 \cdot \alpha$ , on de  $\alpha$  é constante, a equação de projeto passará a ser:

$$\frac{C_2}{C_1} = \alpha.N, \qquad (2.48)$$

que independe de  $f_0$  (e de  $\tau_0$ ). Assim, se  $f_0$  variar, a frequência  $f_1$  de comando das chaves variará proporcionalmente, mantendo sem pre válida a igualdade expressa em (2.48), e portanto gerando a exponencial adequada à conversão de f(X) em X.

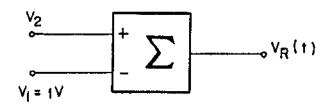

A partir do sinal  $V_2$ , e utilizando um circuito simples para subtrair l volt de  $V_2$ , chegamos a referência variante da equação (2.42), o que aparece ilustrado na figura 2.5(c). Convém observar que, no circuito da figura 2.5(b), será necessário mais uma chave analógica para descarregar  $C_2$  antes do início da conver são, uma vez que o sinal de referência  $V_R$ (t) deverá ser gerado a cada ciclo de medida.

Como resultado importante do que vimos até aqui, além da técnica de conversão em si, aparece portanto a possibilidade de, utilizando circuitos a capacitores chaveados, manter a <u>imunidade ao relógio</u> para conversores não-lineares, mantendo assim uma das principais características do conversor dupla-rampa. No próximo capítulo mostraremos uma aplicação da técnica desenvolvida à conversão de funções polinomiais, de grande interesse no processa mento de sinais elétricos.

### CAPÍTULO III

### APLICAÇÃO A FUNÇÕES POLINOMIAIS

### Introdução

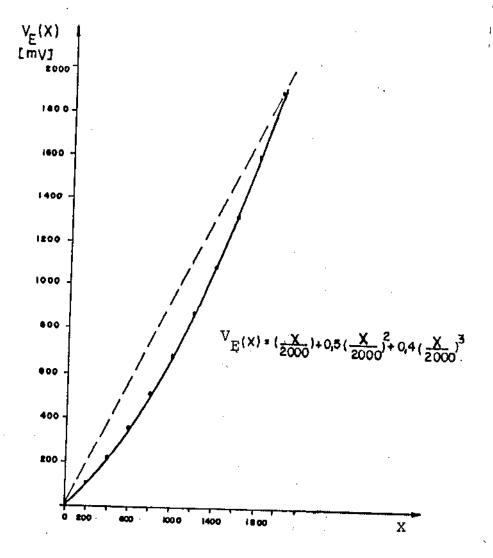

A conversão A/D de sinais elétricos provenientes de sensores ou transdutores é talvez a área de maior aplicação de conversores não-lineares. Neste caso, temos em geral uma relação não-linear entre o sinal elétrico medido e a grandeza que representa, e o conversor não-linear pode, ao mesmo tempo, realizar as tarefas de linearização e digitalização do sinal. Para que se possa projetar um conversor não-linear para este fim é necessário conhecer uma função que aproxime satisfatoriamente a curva do sensor. A partir desta função f(X) é possível, como vimos no capítulo anterior, obter X como resultado da conversão, desde que f(X) obedeça a determinadas condições, como f(X) = 0 para X = 0 e ainda f(X) biunívoca.

Dentre as funções utilizadas para aproximar relações não-lineares, as funções polinomiais tem sido as mais utiliza das, quer pela facilidade com que podem ser sintetizadas, quer pela simplicidade de métodos de aproximação como mínimos quadra dos. Para alguns sensores, como é o caso de termopares, existem aproximações polinomiais já bastante conhecidas |17|.

Dedicamos este capítulo ao estudo da linearização através do conversor desenvolvido, de funções polinomiais de qual

quer ordem, apresentando um circuito para geração da referência

variante no tempo que poderá ser utilizado para funções deste

tipo. Apresentamos também equações de projeto que facilitam a

síntese de conversores para funções polinomiais; analisan

do as principais fontes de erro para o circuito proposto.

## 3.1. Linearização de Funções Polinomiais

Como caso particular da conversão não-linear estudada no capítulo 2, estudaremos a conversão de f(X) em X onde f(X)

é dada por:

$$f(x) = A_1 x + A_2 x^2 + ... + A_m x^m,$$

(3.1)

Convēm notar que o termo constante do polinômio acima é nulo, o que garante f(0)=0. Assumiremos ainda que os coeficientes  $A_1,\ A_2,\ \ldots,\ A_n$  são tais que f(X) é biunívoca no intervalo  $\left[0,X_{\underline{M}}\right]$  de interesse. Para efeito deste capítulo, trabalha remos com f(X) no primeiro quadrante, sem com isso limitar os resultados, como foi visto no ítem 2.3. Utilizaremos um conversor com fundo de escala de N contagens, comandado por um relógio na frequência  $f_0$  (=  $1/\tau_0$ ).

De acordo com a equação (2.41) a referência variante a ser utilizada para converter f(X) em X serã:

$$V_{R}(t) = -N \cdot \tau_{0} \cdot \frac{d}{dt} f(\frac{t}{\tau_{0}}) =$$

$$= -N \cdot \tau_{0} \frac{d}{dt} \left[ A_{1} \left( \frac{t}{\tau_{0}} \right) + A_{2} \left( \frac{t}{\tau_{0}} \right)^{2} + \dots + A_{m} \cdot \left( \frac{t}{\tau_{0}} \right)^{m} \right]$$

$$= -N \cdot \tau_{0} \left[ \frac{A_{1}}{\tau_{0}} + \frac{2A_{2}t}{\tau_{2}} + \dots + \frac{m \cdot A_{m}}{\tau_{m}} \cdot t^{m-1} \right]$$

$$= -\left[ N \cdot A_{1} + \frac{2NA_{2}}{\tau_{0}} + \dots + \frac{m \cdot N \cdot A_{m}}{\tau_{0}^{m-1}} \cdot t^{m-1} \right]$$

(3.2)

Podemos reescrever  $V_R(t)$  como:

$$V_{R}(t) = a_{0} + a_{1} \cdot t + \dots + a_{m-1} \cdot t^{m-1},$$

(3.3)

onde:

$$a_{0} = -N.A_{1}$$

$$a_{1} = \frac{-2.N.A_{2}}{\tau_{0}}$$

$$a_{m-1} = \frac{-m.N.A_{m}}{\tau_{0}^{m-1}}$$

(3.4)

Vemos portanto que, para linearizar um polinômio de grau m devemos gerar uma referência polinomial (no tempo) de grau m-l. A expressão para  $V_{\rm R}(t)$  vista em (3.3) pode ainda ser expressa como somatória dos termos de um polinômio:

$$V_R(t) = a_0 + \sum_{j=1}^{m-1} a_j \cdot t^j, \quad 0 \le t \le N \cdot \tau_0$$

(3.5)

onde:

$$a_{j} = \frac{-(j+1).N.A_{j+1}}{\tau_{0}^{j}}$$

(3.6)

Para gerar a referência  $V_R(t)$  podemos utilizar integra dores em cascata para obter termos em  $t^1$  que, ponderados ade quadamente, fornecerão o sinal de referência. Como cada coeficiente  $a_1$  em (3.6) depende de  $\tau_0$ , utilizaremos integradores cha veados para preservar a imunidade ao relógio.

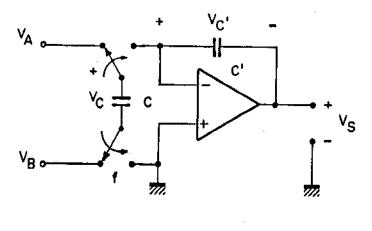

# 3.2. Geração de V<sub>R</sub>(t) com Integradores Chaveados

Utilizaremos como bloco integrador o circuito mostra do na figura 3.1(a), que será analisado assumindo que a frequên cia de comutação das chaves é muito maior que a do sinal a ser integrado. As chaves mostradas na figura são ligadas alternada mente aos sinais de entrada e à entrada: do amplificador, numa frequência f(=1/T), de modo que o capacitor C se carrega com a diferença  $(V_A - V_B)$  e transfere sua carga para o capacitor C' a

$$V_{S} = \frac{fC}{C'} \int_{0}^{t} (V_{B} - V_{A}) dt + V_{S}(0)$$

(a) Circuito básico do integrador chaveado.

(b) Bloco funcional simbolizando o integrador de (a).

Figura 3.1 - Integrador Diferencial a Capacitores Chaveados.

cada T segundos. Quando ambas as chaves estão voltadas para o lado esquerdo, a carga em C serã:

$$Q_C = C.(V_A - V_B)$$

(3.7)

Esta carga, transferida a cada T segundos, implicará numa corrente média fluindo para (ou de C') dada por:

$$i = \frac{C(V_A - V_B)}{T} = f.C(V_A - V_B)$$

(3.8)

A taxa de variação da tensão em C' serã então igual a (1/C'), ou seja:

$$\frac{d.v_{C'}}{dt} = \frac{i}{c'} = \frac{f.C}{c'} \cdot (v_{A} - v_{B})$$

(3.9)

Como a tensão de saída é igual a - V<sub>C</sub>, integrando (3.9) chegamos a seguinte relação entre entradas e saída para o integrador chaveado:

$$v_{S} = \frac{f.C}{C'} \cdot \int_{0}^{t} (v_{B} - v_{A}) \cdot dt + v_{S}(0),$$

(3.10)

o que mostra que o circuito realiza a integral no tempo da diferença entre os sinais  $V_B$  e  $V_A$ . Utilizamos como bloco básico um <u>integrador diferencial</u> para possibilitar seu funcionamento como inversor ou não inversor, dependendo da escolha do terminal para entrada do sinal a ser integrado.

Para facilitar o entendimento dos circuitos da referência variante no tempo, simbolizaremos o integrador diferencial como mostrado na figura (3.1(b), indicando sempre a frequência de comutação das chaves e os valores dos capacitores un tilizados atravês do coeficiente que multiplica a integral em

(3.10). Assumiremos também, exceto quando assinalado em contr<u>a</u>rio, que uma terceira chave analógica garante condição inicial nula ( $V_S(0) = 0$ ) para todos os integradores chaveados.

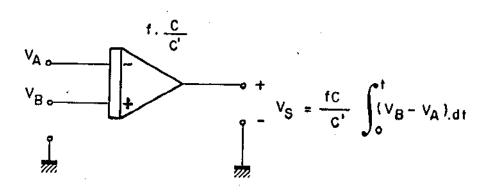

### Circuito Completo da Referência Variante

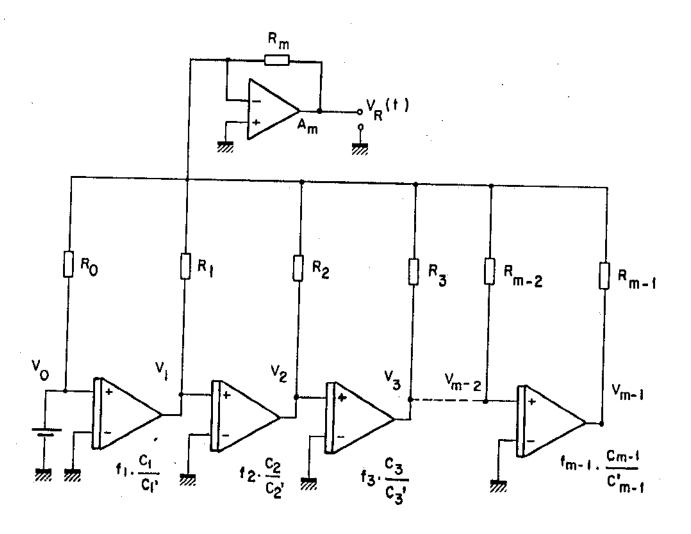

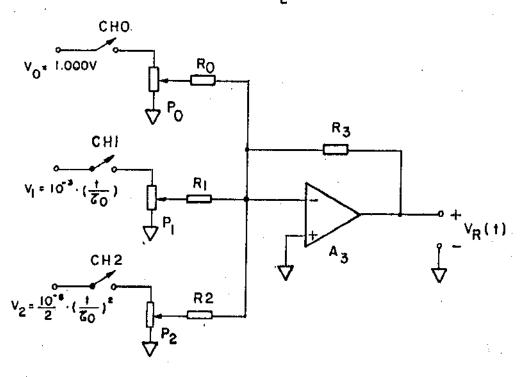

O circuito completo para gerar um sinal de referência capaz de linearizar o polinômio em (3.1) é mostrado na figura 3.2. A partir do cálculo de  $V_R(t)$  da figura, poderemos extrair as relações entre os componentes utilizados e os coeficientes deduzidos anteriormente, indicados em (3.4) e (3.6).

O circuito é composto de uma cascata de integradores não inversores, num total de (m-1) seções, alimentado por uma tensão  $V_0$  de referência. As saídas  $V_1, \, V_2 \dots \, V_{m-1}$ , como mos tramos a seguir, fornecerão os termos dependentes do tempo que, somados atravês do amplificador  $A_m$ , constituirão os termos do polinômio  $V_R(t)$ . Por simplicidade chamaremos  $\alpha_j$  a relação en tre os capacitores do j-ésimo integrador. Assim, utilizando a relação expressa em (3.10) teremos:

$$v_1 = \alpha_1 f_1 \cdot \int_0^t v_0 \cdot dt = \alpha_1 \cdot f_1 \cdot v_0 \cdot t$$

(3.11)

$$v_2 = \alpha_2 f_2 \int_0^t v_1 dt = \alpha_1 \cdot \alpha_2 \cdot f_1 \cdot f_2 \cdot v_0 \cdot \frac{t^2}{2}$$

$$v_3 = \alpha_3.f_3 \int_0^t v_2.dt = \alpha_1.\alpha_2.\alpha_3.f_1.f_2.f_3.v_0.\frac{t^3}{3!}$$

$$v_{m-1} = \alpha_{m-1} f_{m-1} \int_0^t v_{m-2} dt =$$

$$= \alpha_{1} \cdot \alpha_{2} \cdot ... m-1 \cdot f_{1} \cdot f_{2} \cdot ... f_{m-1} \cdot v_{0} \cdot \frac{t^{m-1}}{(m-1)}$$

(3.12)

Figura 3.2 - Geração de  $V_{R}(t)$  para função polinomial.

Como forma reduzida para a saída do j-ésimo integra dor podemos escrever:

$$v_{j} = v_{0} \cdot \left( \prod_{i=1}^{j} \alpha_{i} \right) \cdot \left( \prod_{i=1}^{j} f_{i} \right) \cdot \frac{t^{j}}{j!} ; j = 1, 2, \dots, m-1$$

(3.13)

A salda do somador inversor da figura (3.2) fornecerã, portanto, a soma das tensões  $V_0$  a  $V_{m-1}$  ponderada pelos respectivos ganhos, ou seja:

$$v_{R}(t) = -\left[\frac{R_{m}}{R_{0}} \cdot V_{0} + \frac{R_{m}}{R_{1}} \cdot V_{1} + \dots + \frac{R_{m}}{R_{m-1}} \cdot V_{m-1}\right], (3.14)$$

que, utilizando (3.14) ficará:

$$V_{R}(t) = f_{0} + \sum_{j=1}^{m-1} \frac{R_{m}}{R_{j}} ... V_{j}$$

$$v_{R}(t) = b_{0} + \sum_{j=1}^{m-1} b_{j} \cdot t^{j} ; \quad 0 \leq t \leq N \cdot \tau_{0}$$

(3.15)

onde:

$$\begin{cases} b_{j} = \frac{-v_{0}}{j!} \cdot \frac{R_{m}}{R_{j}} \cdot \left( \prod_{i=1}^{j} \alpha_{i} \right) \cdot \left( \prod_{i=1}^{j} f_{i} \right) \\ b_{0} = -\frac{R_{m}}{R_{0}} \cdot v_{0} \quad ; \quad j = 1, 2, \dots, m-1 \end{cases}$$

Podemos observar que a expressão para  $V_R(t)$  em (3.15) possui a forma desejada, como calculada a partir da expressão de f(X) (eq. 3.5). Portanto as equações de projeto do conversor podem ser obtidas igualando-se os coeficientes dos termos correspondentes nos dois polinômios. Em outras palavras, para que o conversor realize a conversão de f(X) em X temos que ter:

$$a_{j} = b_{j}$$

,  $j = 1, 2, ..., m-1$  (3.16)

$a_{0} = b_{0}$

Utilizando então as expressões para a e b teremos:

$$\begin{cases} a_{j} = \frac{-(j+1) \cdot N \cdot A_{j+1}}{\tau^{j}} = \frac{-v_{0} \cdot R_{m}}{j! R_{j}} \cdot \left( \prod_{i=1}^{j} \alpha_{i} \right) \left( \prod_{i=1}^{j} f_{i} \right) = b_{j} \\ a_{0} = -N \cdot A_{1} = \frac{-R_{m}}{R_{0}} \cdot V_{0} = b_{0} \end{cases}$$

$$(3.17)$$

Dados portanto os coeficientes  $A_1,\ A_2,\dots,A_m$  da função a linearizar, conhecidos o fundo de escala N de conversor e o período  $\tau_0$  do relógio principal, podemos calcular os resisto res  $R_1$  a  $R_m$ , os capacitores  $C_1$  a  $C_{m-1}$  e  $C_1$  a  $C_{m-1}$ , e escolher a tensão de referência  $V_0$  de modo a satisfazer (3.17). Na prātica o que faremos será utilizar as componentes  $V_j$  (saídas dos integradores) com as maiores amplitudes possíveis, para minimizar efeitos residuais dos amplificadores operacionais, deixando a ponderação final por conta dos resistores  $R_1$  a  $R_{m-1}$ .

# Imunidade ao Relógio

A imunidade do conversor a variações no relógio serã obtida se as relações expressas em (3.17) se mantiverem válidas, para qualquer valor de j, mesmo com flutuações no valor de  $\tau_0$ . Como temos na expressão dos coeficientes  $\mathbf{b}_{\mathbf{j}}$  um fator igual ao produto das frequências de comutação das chaves,  $\mathbf{f}_1.\mathbf{f}_2.\mathbf{f}_3,\ldots$ ,  $\mathbf{f}_{\mathbf{j}}$ , a imunidade pode ser alcançada se cada uma destas frequências depender diretamente da frequência  $\mathbf{f}_0 = 1/(\tau_0)$  do relógio, ou seja, se cada frequência  $\mathbf{f}_{\mathbf{i}}$  puder ser descrita por:

$$f_{i} = k_{i} \cdot f_{0} = \frac{k_{i}}{\tau_{0}}$$

, (3.18)

onde k<sub>i</sub> é constante. A forma de obter esta dependência é simples, bastando gerar cada sinal de comutação de chaves bem como o relógio principal a partir de um único sinal, utilizando divisores digitais de frequência (flip-flops). Assim, em (3.17) teremos, considerando apenas os termos relacionados com frequências:

$$\frac{1}{\tau^{j}} \sim \left( \prod_{i=1}^{j} f_{i} \right) \tag{3.19}$$

Utilizando (3.18) ficaremos com:

$$\frac{1}{\tau_0^{j}} \sim \frac{k_1}{\tau_0} \cdot \frac{k_2}{\tau_0} \cdot \cdot \cdot \frac{k_j}{\tau_0} = \frac{k_1 \cdot k_2 \cdot \cdot \cdot k_j}{\tau_0^{j}} , \qquad (3.20)$$

o que nos permitirá concelar de ambos os lados o denominador  $\tau^j$ , chegando assim a uma nova relação que independe de  $\tau_0$ , e portan to do relógio, a saber:

$$-(j+1) \cdot N \cdot A_{j+1} = \frac{-v_0}{j!} \frac{R_m}{R_j} \cdot \left( \frac{j}{j!} \alpha_i \right) \left( \frac{j}{j!} k_i \right) , \quad (3.21)$$

que deve ser respeitada para qualquer j entre 1 e m-1.

A relação mostrada em (3.21) é geral, evidenciando que podemos utilizar relações entre capacitores  $(\alpha_{\bf i})$  bem como as frequências de comutação das chaves dos integradores  $({\bf k_i})$  para ajustar os coeficientes da referência polinomial  ${\bf V_R}({\bf t})$  do conversor não-linear. Como caso particular, que facilitarã tanto a análise de erros que faremos adiante, quanto simplificarã a etapa de projeto e reduzirã o custo do conversor, utilizare mos todas as frequências de comutação iguais a  ${\bf f_0}$ , ou seja, o sistema possuirã um único relógio, o que implica dizer que os coeficientes  ${\bf k_i}$  são todos iguais a 1. Assim podemos substituir

(3.21) por uma equação de projeto ainda mais simples:

$$(j+1) \cdot N \cdot A_{j+1} = \frac{v_0}{j!} \cdot \frac{R_m}{R_j} \cdot \left( \frac{j}{j!} \alpha_i \right)$$

(3.22)

Escolhendo previamente o valor da tensão de referência  $V_0$ , e rearrumando (3.22) para isolar os parâmetros de projeto de um único lado, chegamos a uma nova equação de projeto, a saber:

$$\frac{R_{m}}{R_{j}} \cdot \left( \prod_{i=1}^{j} \alpha_{i} \right) = \frac{(j+1)! N. A_{j+1}}{V_{0}} , \qquad (3.23)$$

que deverá ser respeitada para j entre l e m-l, e que, como que ríamos, independente de  $\tau_0$ .

Garantida a imunidade ao relógio, podemos encerrar es te îtem resumindo os resultados obtidos. Para obter a linearização com conversão A/D da função polinomial

$$f(X) = A_1 X + A_2 X^2 + ... + A_m . X^m,$$

(3.24)

tendo X como resultado da conversão, necessitamos utilizar um sinal de referência  $V_{\rm R}(t)$  dada por:

$$v_R(t) = a_0 + \sum_{j=1}^{m-1} a_j \cdot t^j$$

, (3.25)

onde:

$$a_{j} = \frac{-N.A_{1}}{a_{j}}$$

$$a_{j} = \frac{(j+1).N.A_{j+1}}{\tau^{j}}$$

(3.26)

O sinal de referência gerado através do circuito mos trado na figura (3.2), assumindo todas as frequências de comutação iguais a frequência do relógio principal, nos fornece como saída:

$$v_{R}(t) = b_{0} + \sum_{j=1}^{m-1} b_{j} t^{j}$$

(3.27)

onde:

$$\begin{cases} b_0 = \frac{-R_m}{R_0} \cdot V_0 \\ b_j = \frac{-V_0}{j!} \frac{R_m}{R_j} \cdot \frac{\alpha_1 \cdot \alpha_2 \cdot \dots \cdot \alpha_j}{\tau_0^j} \end{cases}$$

(3.28)

Portanto, para realizar corretamente a conversão, temos que obedecer as seguintes relações:

$$\frac{R_{m}}{R_{0}} = \frac{N \cdot A_{1}}{V_{0}} , (a_{0} = b_{0}) , \qquad (3.29)$$

е

$$\frac{R_{m}}{R_{j}} \cdot (\alpha_{1}, \alpha_{2}, \dots, \alpha_{j}) = \frac{(j+1)! N \cdot A_{j+1}}{V_{0}}$$

(3.30)

#### 3.3. Análise de Erros

Neste item consideraremos apenas as principais fontes de erros causados pela introdução de uma referência variante no tempo a capacitores-chaveados, uma vez que os erros do conversor dupla-rampa propriamente ditos dependem do conversor utilizado. Neste sentido identificamos duas principais fontes de erros. A primeira relacionada com as tensões residuais (offset) dos amplificadores operacionais, a segunda decorrente das aproximações utilizadas para analisar os integradores a capacitores chaveados. Analisaremos estas fontes de erros de modo a avaliar

sua contribuição e indicaremos formas de reduzir seus efeitos.

### 3.3.1. Tensões Residuais

Os integradores representados na figura 3.2 são construidos com amplificadores operacionais, utilizando o circuito da figura 3.1(a). Chamaremos  $\mathbf{A}_1$  o amplificador utilizado para gerar  $\mathbf{V}_1$ ,  $\mathbf{A}_2$  para  $\mathbf{V}_2$ , e assim sucessivamente, sendo  $\mathbf{A}_{m-1}$  o amplificador utilizado para gerar  $\mathbf{V}_{m-1}$ . Denominaremos  $\mathbf{V}_{0Sj}$  a tensão residual (offset) do amplificador  $\mathbf{A}_j$ , e avaliaremos a influência de cada tensão residual sobre os sinais  $\mathbf{V}_1$  a  $\mathbf{V}_{m-1}$ . Para efeito desta análise, suporemos todos os coeficientes  $\alpha_j$  iguais entre si e assumindo o valor típico  $\alpha=\mathbf{N}^{-1}$ , além de utilizar frequências de comutação iguais a  $\tau_0^{-1}=\mathbf{f}_0$ . Desta forma, a saída  $\mathbf{V}_j$  do jesimo integrador será dada por:

$$v_{j} = f_{0} \cdot \alpha \int_{0}^{t} v_{j-1} \cdot dt = \frac{1}{N \cdot \tau_{0}} \int_{0}^{t} v_{j-1} \cdot dt$$

(3.31)

Partindo então do 1º integrador, para condições ini ciais nulas, teremos as saídas:

$$V_{1} = f_{0} \cdot \alpha \int (V_{0} + V_{0S1}) \cdot dt = f_{0} \cdot \alpha (V_{0} + V_{0S1}) t (3.32)$$

$$V_{2} = f_{0} \cdot \alpha \int (V_{1} + V_{0S2}) \cdot dt =$$

$$= (f_{0} \cdot \alpha)^{2} (V_{0} + V_{0S1}) \cdot \frac{t^{2}}{2!} + f_{0} \cdot \alpha \cdot V_{0S2} \cdot t;$$

$$\vdots$$

$$V_{j} = (f_{0} \cdot \alpha)^{j} (V_{0} + V_{0S1}) \cdot \frac{t^{j}}{j!} + (f_{0} \cdot \alpha)^{j-1} \cdot V_{0S2} \cdot \frac{t^{j-1}}{(j-1)!} +$$

$$+ \cdots + f_{0} \cdot \alpha \cdot V_{0Sj} \cdot t;$$

UNICAMP BIBLIOTECA CENTRAL

$$v_{m-1} = (f_0.\alpha)^{m-1} (v_0 + v_{0S1}) \cdot \frac{t^{m-1}}{(m-1)!} + \dots + f_0.\alpha \cdot v_{0S(m-1)} \cdot t.$$

A seguir podemos encontrar  $V_1$  a  $V_{m-1}$  para a maior du ração do intervalo de integração da referência, que ocorre para  $t = N.\tau_0$ . Substituindo  $\alpha = N^{-1}$  e  $f_0 = \tau_0^{-1}$ , as expressões em (3.32) ficam, para  $t = N.\tau_0$ :

Rearrumando a expressão da saída  $V_{m-1}$  do último integrador, de modo a comparar as parcelas dependentes de tensões residuais com a parcela de sinal, temos:

$$V_{m-1} = \frac{1}{(m-1)!} \left[ V_0 + V_{0S1} + (m-1) V_{0S2} + (m-1) - (m-2) V_{0S3} + \dots + (m-1)! V_{0S(m-1)} \right]$$

(3.34)

Em (3.34) percebemos que a tensão residual do último amplificador, A<sub>m-1</sub>, aparece multiplicada por (m-1)!, indicando uma forte dependência dos erros residuais com a ordem do polinômio. Podemos ver também de (3.33) que, para manter os mesmos níveis relativos de erro em cada integrador, os requisitos impostos a cada amplificador são tanto maiores quanto maior a ordem do integrador. Apenas como indicação para projeto, para que os erros aumentem de forma aproximadamente linear podemos impor as seguintes restrições:

$$V_{0S1} = V_{0S}; \qquad (3.35)$$

$$V_{0S2} = \frac{V_{0S1}}{(m-1)} = \frac{(m-2)!}{(m-1)!} \cdot V_{0S};$$

$$V_{0S3} = \frac{V_{0S2}}{(m-2)} = \frac{(m-3)!}{(m-1)!} V_{0S};$$

$$V_{0S4} = \frac{V_{0S3}}{(m-3)} = \frac{(m-4)!}{(m-1)!} V_{0S};$$

$$\vdots$$

$$V_{0S(m-1)} = \frac{V_{0S(m-2)}}{2} = \frac{1}{(m-1)!} V_{0S}.$$

Desta forma, a expressão de  $V_{m-1}$ , a partir de (3.34), fica:

$$V_{m-1} = \frac{1}{(m-1)!} \left[ V_0 + V_{0S} + V_{0S} + \dots + V_{0S} + V_{0S} \right] = \frac{1}{(m-1)!} \left[ V_0 + (m-1) V_{0S} \right], \qquad (3.36)$$

o que mostra que as tensões rediduais pesarão (m-1) vezes mais no último integrador com relação ao primeiro. A título de exem plo, suponhamos m=6, ou (m-1) = 5. Usando (3.35) teremos:

$$v_{0s1} = v_{0s}$$

; (3.37)

$$v_{0S2} = \frac{v_{0S1}}{5} = \frac{v_{0S}}{5}$$

;

$$v_{0S3} = \frac{v_{0S2}}{4} = \frac{v_{0S}}{20}$$

;

$$v_{0S4} = \frac{v_{0S3}}{3} = \frac{v_{0S}}{60}$$

,

$$v_{0S5} = \frac{v_{0S4}}{2} = \frac{v_{0S}}{120} = \frac{v_{0S}}{5!}$$

Utilizando (3.33), os erros relativos podem ser obtidos comparando a parcela dependente de  $V_{0S}$  com  $V_0$ , substituindo os valores obtidos em (3.37), que darão:

$$V_{1} = V_{0} + V_{0S} ; \qquad (3.38)$$

$$V_{2} = \frac{1}{2} (V_{0} + \frac{7}{5} \cdot V_{0S}) ;$$

$$V_{3} = \frac{1}{6} (V_{0} + \frac{19}{10} \cdot V_{0S}) ;$$

$$V_{4} = \frac{1}{24} (V_{0} + \frac{42}{15} \cdot V_{0S}) ;$$

$$V_{5} = \frac{1}{120} (V_{0} + 5 \cdot V_{0S}) ;$$

Do exemplo acima, vemos que utilizando  $\rm V_{0S5}$  120 vezes menor que  $\rm V_{0S1}$  ainda teremos o erro em  $\rm V_5$  cinco vezes maior que

em V<sub>1</sub>. Disto concluimos que as tensões rediduais podem ofere cer sérias limitações, dependendo da resolução desejada no conversor. Um fator atenuante para conversores polinomiais é que os termos de ordem elevada do polinômio possuem coeficientes em geral pequenos, portanto com baixo peso na precisão geral do conversor.

# 3.3.2. Erros de Discretização

O câlculo de  $V_R(t)$  necessâria para realizar a conversão de f(X) em X, com f(X) na forma de (3.1) nos forneceu a referência variante da equação (3.3), que repetimos aqui:

$$V_R(t) = a_0 + a_1 t + a_2 t^2 + \dots + a_{m-1} t^{m-1}$$

(3.39)