#### Veruska Rodrigues Moreira

# Plataforma em hardware reconfigurável para o ensino e pesquisa em laboratório de sistemas digitais a distância

Dissertação de Mestrado apresentada à Faculdade de Engenharia Elétrica e de Computação como parte dos requisitos para obtenção do título de Mestre em Engenharia Elétrica. Área de concentração: Telecomunicações e Telemática.

> Orientador: Prof. Dr. Dalton Soares Arantes Co-orientador: Dr. Fabbryccio Akkazzha Chaves

Machado Cardoso

#### Banca Examinadora:

Prof. Dr. Dalton Soares Arantes (Orientador) - FEEC/UNICAMP

Prof. Dr. Ivan Luiz Marques Ricarte - FEEC/UNICAMP

Prof. Dr. Luciano Leonel Mendes - INATEL

#### FICHA CATALOGRÁFICA ELABORADA PELA BIBLIOTECA DA ÁREA DE ENGENHARIA E ARQUITETURA - BAE - UNICAMP

Moreira, Veruska Rodrigues

M813p

Plataforma em hardware reconfigurável para o ensino e pesquisa em laboratório de sistemas digitais a distância Veruska Rodrigues Moreira. – Campinas, SP: [s.n.], 2009.

Orientadores: Dalton Soares Arantes; Fabbryccio Akkazzha Chaves Machado Cardoso.

Dissertação de Mestrado - Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Ensino a distância. 2. FPGA. 3. Serviços na Web. I. Arantes, Dalton Soares. II. Cardoso, Fabbryccio Akkazzha Chaves Machado. III. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. IV. Título

Título em Inglês: Reconfigurable hardware platform for research and distance learning

on remote laboratories for digital systems

Palavras-chave em Inglês: Distance learning, FPGA, Web services

Área de concentração: Telecomunicações e Telemática Titulação: Mestre em Engenharia Elétrica

Banca Examinadora: Ivan Luiz Marques Ricarte, Luciano Leonel Mendes

Data da defesa: 21/12/2009

Programa de Pós Graduação: Engenharia Elétrica

#### **COMISSÃO JULGADORA - TESE DE MESTRADO**

Data da Defesa: 21 de dezembro de 2009

Título da Tese: "Plataforma em Hardware Reconfigurável para Ensino e Pesquisa em

Laboratório de Sistemas Digitais a Distância"

Prof. Dr. Dalton Soares Arantes (Presidente):

Prof. Dr. Luciano Leonel Mendes: \_

Prof. Dr. Ivan Luiz Marques Ricarte:

#### Resumo

Esta dissertação apresenta a concepção e o desenvolvimento de uma plataforma em hardware reconfigurável denominada REDLART - REconfigurable Digital Laboratory for Advanced Research and Teaching, visando soluções de laboratório a distância aplicadas ao ensino e ao trabalho colaborativo em sistemas digitais. A plataforma é baseada em dispositivos FPGA (Field Programmable Gate Array) para desenvolvimento de circuitos digitais com aplicações em processamento digital de sinais, sistemas de comunicações digitais, sistemas de controle e áreas afins. Além da plataforma de hardware, também foi concebida e implementada uma arquitetura de sistema, composta por um conjunto de softwares cliente-servidor, com o objetivo de viabilizar o acesso remoto através da gerência e da configuração de experimentos desenvolvidos na REDLART. Tal sistema, incluindo a própria REDLART, possibilita o desenvolvimento de novos experimentos e sua disponibilização na Web, resultando em um WebLab reconfigurável para sistemas digitais. Testes foram realizados em nível de hardware e software para a validação da plataforma.

Palavras-chave: Ensino a distância, FPGA, Serviços na Web.

### **Abstract**

This thesis presents a reconfigurable hardware platform called REDLART (REconfigurable Digital Laboratory for Advanced Research and Teaching), designed to enable laboratory applications in distance learning and collaborative work in digital systems. The platform is based on FPGA devices (Field Programmable Gate Array) to develop digital circuit applications for digital signal processing, digital communication systems, control systems and related areas. Besides the hardware platform, a system architecture consisting of a set of client-server software was also designed and implemented in order to enable the remote access through the management and configuration of experiments developed in REDLART. By using the client-server software with the REDLART platform, new experiments can be developed and made available on the Web, resulting in a WebLab for reconfigurable digital systems. Tests were performed at the hardware and software levels for the validation of the platform.

**Keywords**: Distance learning, FPGA, Web services.

## Agradecimentos

A Deus, pela sua presença constante em minha vida.

A toda a minha família, em especial os meus queridos pais Francisco Custódio Moreira e Maria Alice Rodrigues Moreira e ao meu irmão Jefferson Rodrigues Moreira pelo apoio e suporte durante esta jornada. Obrigada por estarem sempre ao meu lado, me apoiando, me incentivando e nunca medindo esforços para que eu pudesse alcançar todos os meus objetivos.

Ao meu orientador Prof. Dalton S. Arantes e ao meu co-orientador Dr. Fabbryccio A. C. M. Cardoso, pelas sugestões e ensinamentos, pela confiança e oportunidade de realizar este trabalho. Eu os considero os meus orientadores tanto para a ciência quanto para a vida.

Aos amigos Cecilio C. Fraguas e Fábio A. G. Lisboa pelas revisões, críticas e sugestões.

A todos os meus amigos, especialmente os amigos do ComLab (Laboratório KyaTera em Comunicações Digitais), da Ujima Software, do DCLab (Laboratório de Comunicações Digitais), da Moradia Estudantil e aos conquistados durante o mestrado. Obrigada pela ajuda constante!

A Roger N. Nascimento, pelo carinho, compreensão e companheirismo.

Aos funcionários da Faculdade de Engenharia Elétrica e Computação (FEEC) da Unicamp pela prestatividade.

À Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES) pelo apoio financeiro.

À Fundação de Amparo à Pesquisa do Estado de São Paulo (FAPESP) pelo apoio ao ComLab.

A todos que contribuíram direta ou indiretamente para a realização deste trabalho, muito obrigada!

"Comece fazendo o que é necessário, depois o que é possível, e de repente você estará fazendo o impossível."São Francisco de Assis

# Sumário

| Lista de Figuras |             |                                                                  | xii |  |  |  |

|------------------|-------------|------------------------------------------------------------------|-----|--|--|--|

| Li               | sta de      | Tabelas                                                          | XV  |  |  |  |

| Gl               | Glossário x |                                                                  |     |  |  |  |

| Tr               | abalh       | os Publicados Pelo Autor                                         | XX  |  |  |  |

| 1                | Intr        | odução                                                           | 1   |  |  |  |

|                  | 1.1         | Visão Geral                                                      | 1   |  |  |  |

|                  | 1.2         | Trabalhos Relacionados                                           | 3   |  |  |  |

|                  | 1.3         | Objetivos                                                        | 4   |  |  |  |

|                  | 1.4         | Motivações e Contribuições                                       | 5   |  |  |  |

|                  | 1.5         | Organização da Dissertação                                       | 7   |  |  |  |

| 2                | Prát        | ica de Laboratório a Distância                                   | 9   |  |  |  |

|                  | 2.1         | Ensino a Distância                                               | Ģ   |  |  |  |

|                  | 2.2         | Laboratório a Distância                                          | 10  |  |  |  |

|                  | 2.3         | Redes de Computadores                                            | 11  |  |  |  |

|                  |             | 2.3.1 Projeto TIDIA-KyaTera                                      | 12  |  |  |  |

|                  |             | 2.3.2 Projeto GIGA                                               | 12  |  |  |  |

|                  |             | 2.3.3 Rede Internet2                                             | 13  |  |  |  |

|                  | 2.4         | Exemplos de Laboratório Remoto                                   | 13  |  |  |  |

|                  | 2.5         | O Trabalho Proposto no Contexto Educacional                      | 14  |  |  |  |

| 3                | Prog        | gramação de Dispositivos FPGA                                    | 17  |  |  |  |

|                  | 3.1         | Introdução a FPGA                                                | 17  |  |  |  |

|                  | 3.2         | Formas de Desenvolvimento e Implementação                        | 21  |  |  |  |

|                  |             | 3.2.1 Linguagem Esquemática                                      | 21  |  |  |  |

|                  |             | 3.2.2 Linguagem de Descrição de Hardware                         | 25  |  |  |  |

|                  |             | 3.2.3 Níveis de abstração HDL                                    | 26  |  |  |  |

|                  |             | 3.2.4 Verilog                                                    | 27  |  |  |  |

|                  |             | 3.2.5 VHDL                                                       | 28  |  |  |  |

|                  |             | 3.2.6 Vantagens de Utilizar a Linguagem de Descrição de Hardware | 28  |  |  |  |

|                  | 3.3         | Fluxo de Projeto para FPGA                                       | 29  |  |  |  |

xii SUMÁRIO

|    |        |                                                                | 20        |

|----|--------|----------------------------------------------------------------|-----------|

|    |        | 3.3.1 Especificação                                            | 29        |

|    |        | 3.3.2 Verificação                                              | 31        |

|    |        | 3.3.3 Implementação                                            | 31        |

|    |        | 3.3.4 Depuração do Sistema                                     | 33        |

|    | 3.4    | Principais Fornecedores                                        | 33        |

| 4  | Arq    | uitetura de Sistema para Aplicações de Laboratório a Distância | 35        |

|    | 4.1    | Introdução a Metodologia de Sistema                            | 35        |

|    | 4.2    | A Arquitetura Proposta para Aplicações de Laboratório Remoto   | 36        |

|    | 4.3    | Aplicação WebLab                                               | 37        |

|    | 4.4    | A camada de <i>Middleware</i>                                  | 38        |

|    |        | 4.4.1 Modelo                                                   | 39        |

|    |        | 4.4.2 Controle                                                 | 45        |

|    |        | 4.4.3 Apresentação                                             | 46        |

|    | 4.5    | A Camada de Infraestrutura de Rede                             | 48        |

| 5  | Plata  | raforma REDLART                                                | 51        |

|    | 5.1    | Especificação de Requisitos                                    | 51        |

|    | 5.2    | Modelagem da Plataforma                                        | 53        |

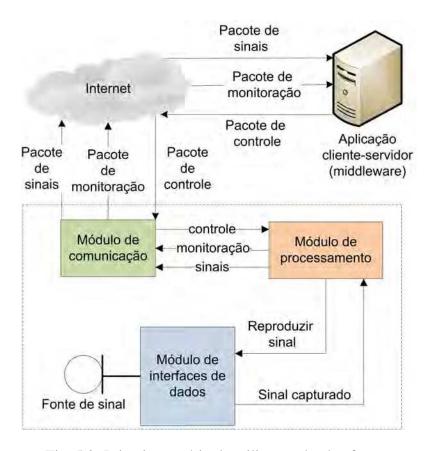

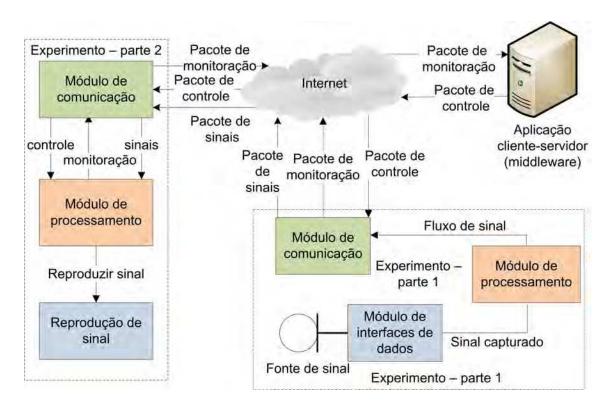

|    |        | 5.2.1 Cenários de Utilização da Plataforma                     | 54        |

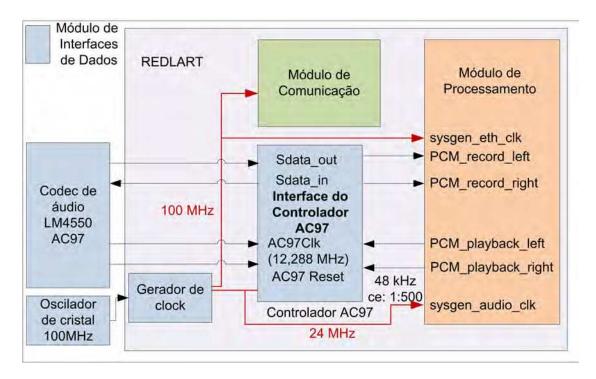

|    |        | 5.2.2 Módulo de Interface de Dados                             | 57        |

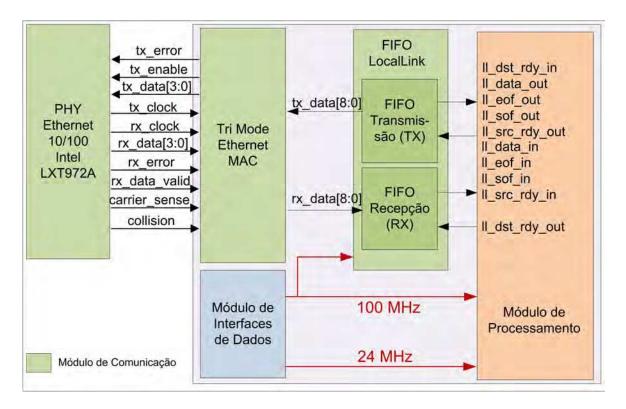

|    |        | 5.2.3 Módulo de Comunicação                                    | 59        |

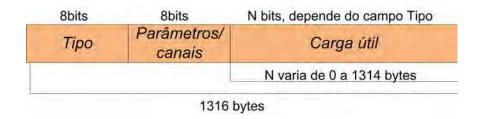

|    |        | 5.2.4 Pilha de Protocolos                                      | 61        |

|    |        | 5.2.5 Detalhamento da Plataforma                               | 64        |

|    | 5.3    | Implementação                                                  | 68        |

| 6  | Vali   | dação da Plataforma                                            | 71        |

| U  | 6.1    | Configuração Sistêmica                                         | 71        |

|    | 6.2    | Teste de Controle e Monitoração                                | 73        |

|    | 6.3    | Teste de Distribuição                                          | 75        |

|    | 6.4    | Teste de Expansão                                              | 77        |

| 7  | Con    | siderações Finais e Conclusão                                  | <b>79</b> |

| Da | .fauên | aning hiblinguéfong                                            | 01        |

| Ne | eren   | ncias bibliográficas                                           | 81        |

| A  | -      | endice With the December being a state of one Local Links      | 85        |

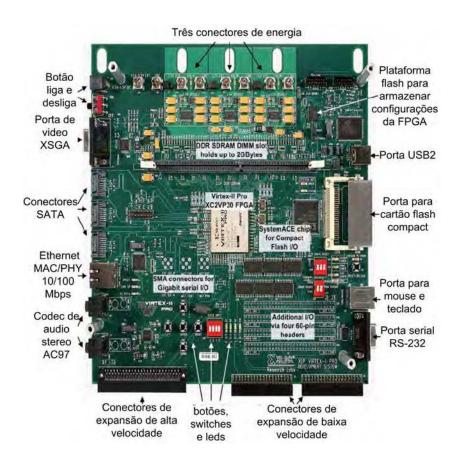

|    | A.I    | Kit de Desenvolvimento e Interface LocalLink                   | 85        |

|    |        | A.1.1 Especificação da interface LocalLink                     | 85        |

|    |        |                                                                |           |

# Lista de Figuras

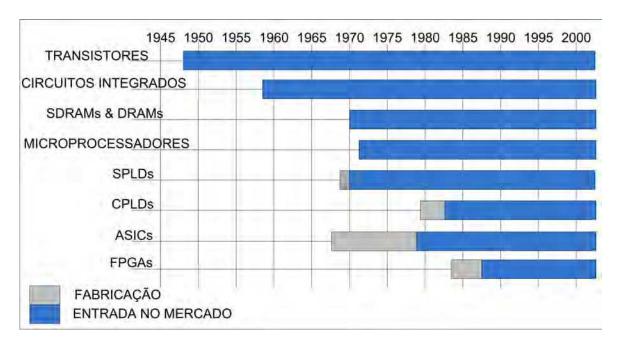

| 3.1  | Cronologia das tecnologias relacionadas com FPGA                                 | 18 |

|------|----------------------------------------------------------------------------------|----|

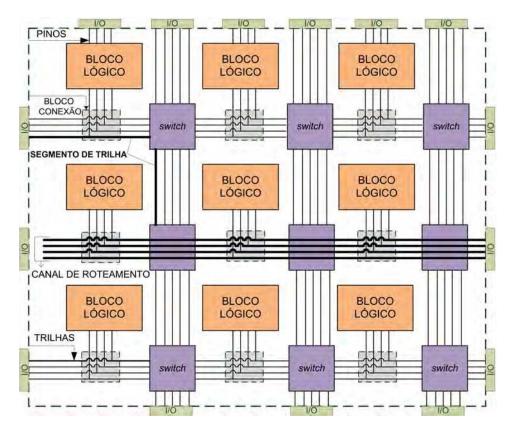

| 3.2  | Visão geral da arquitetura de roteamento de uma FPGA                             | 2  |

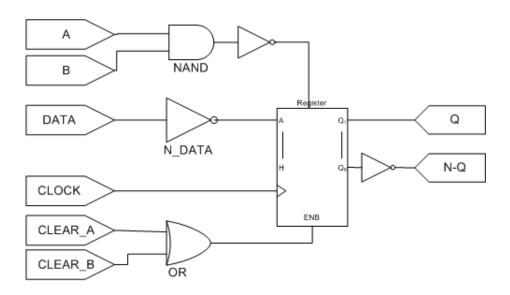

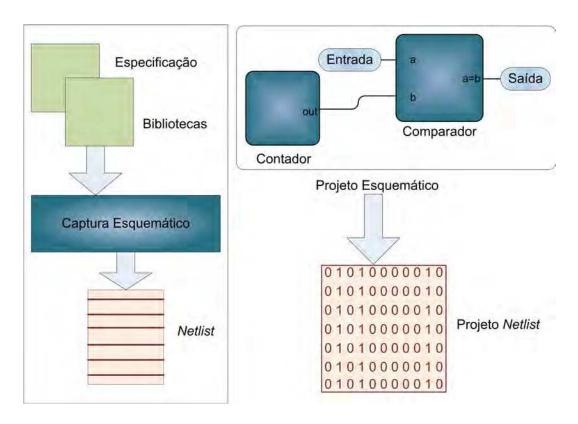

| 3.3  | Diagrama esquemático                                                             | 22 |

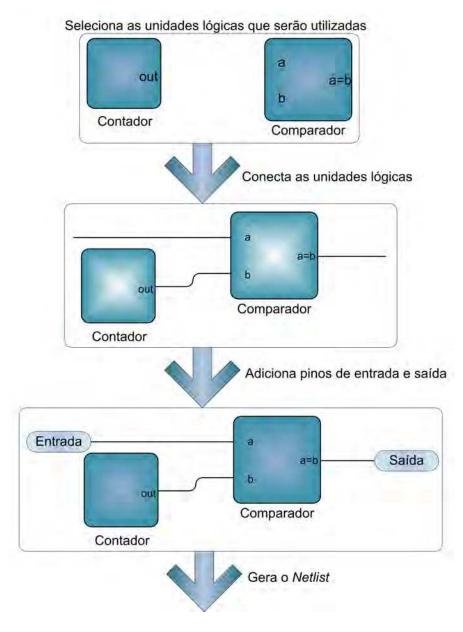

| 3.4  | Processo de captura do esquemático                                               | 23 |

| 3.5  | Especificação do Projeto - Netlist                                               | 24 |

| 3.6  | Projeto esquemático                                                              | 25 |

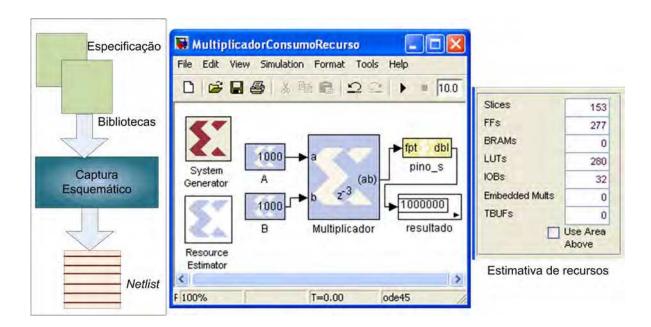

| 3.7  | Projeto multiplicador escrito em HDL                                             | 26 |

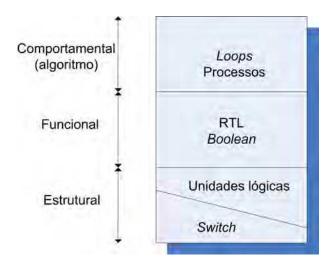

| 3.8  | Diferentes níveis de abstrações                                                  | 27 |

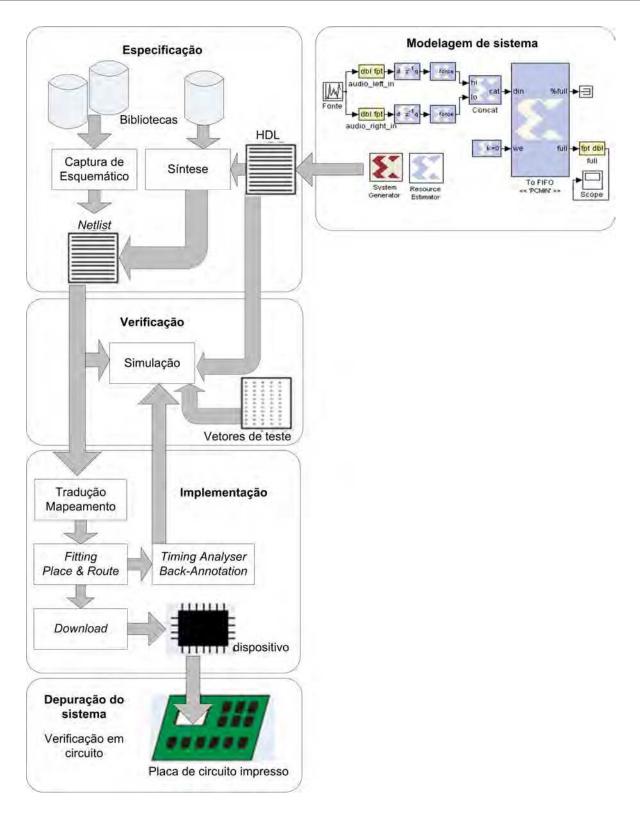

| 3.9  | Fluxo de projeto de uma FPGA                                                     | 30 |

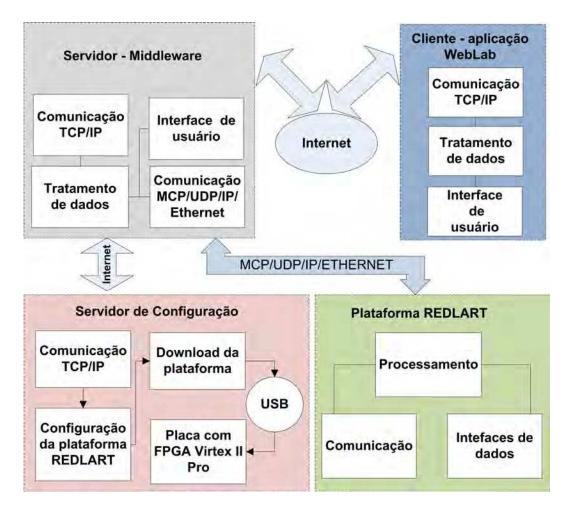

| 4.1  | A arquitetura proposta para aplicações de laboratório remoto                     | 37 |

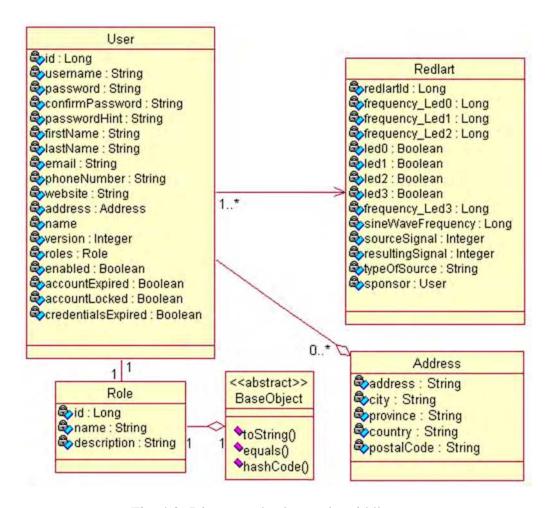

| 4.2  | Diagrama de classes do middleware                                                | 40 |

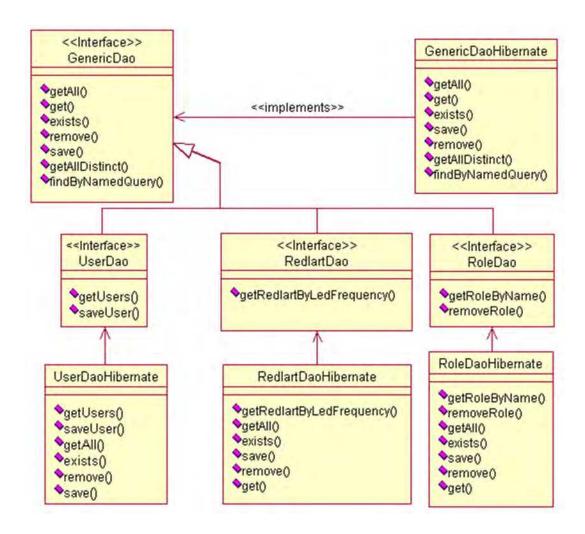

| 4.3  | Representação das classes Daos utilizadas no middleware                          | 42 |

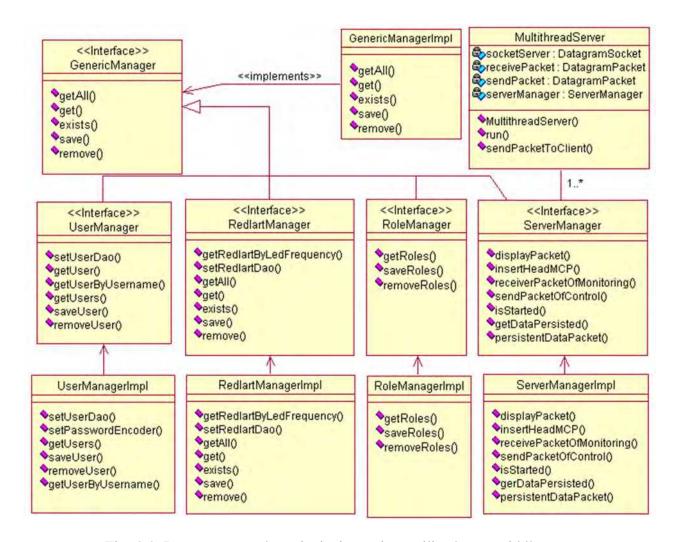

| 4.4  | Representação dos principais serviços utilizados no middleware                   | 43 |

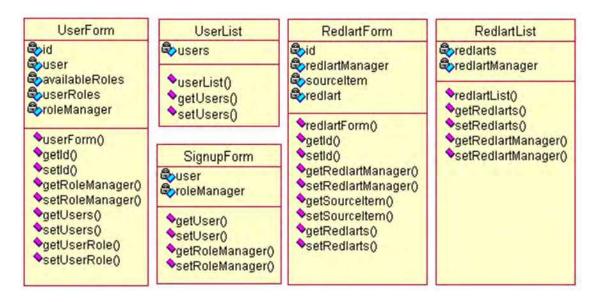

| 4.5  | Diagrama dos beans gerenciáveis utilizados no middleware                         | 46 |

| 4.6  | Interface página principal da aplicação WebLab                                   | 4  |

| 4.7  | Interface do experimento de captura do fluxo de sinais de áudio                  | 48 |

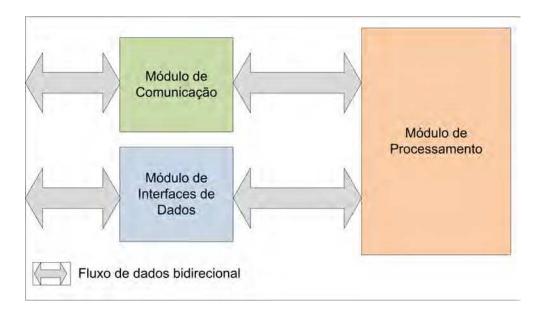

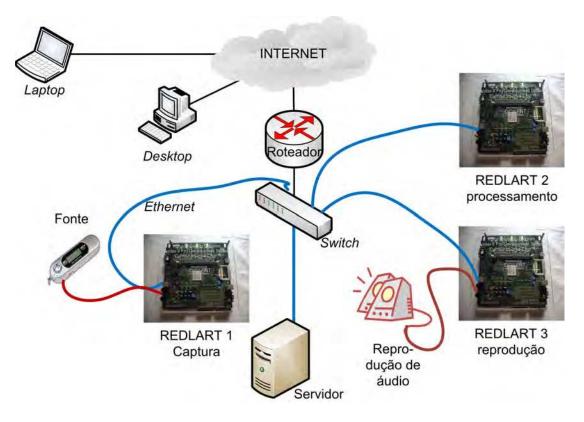

| 5.1  | Visão geral da plataforma REDLART                                                | 54 |

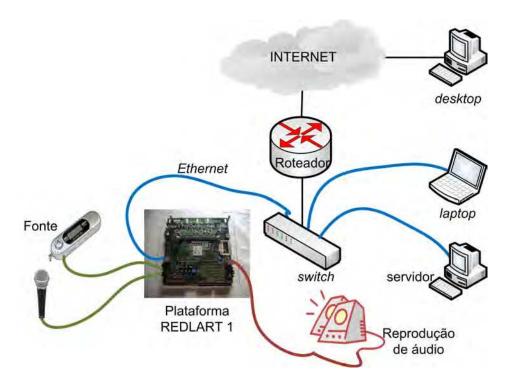

| 5.2  | Primeiro cenário de utilização da plataforma                                     | 55 |

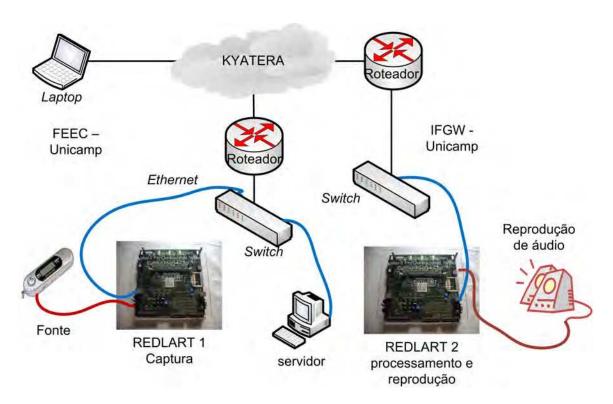

| 5.3  | Segundo cenário de utilização da plataforma                                      | 56 |

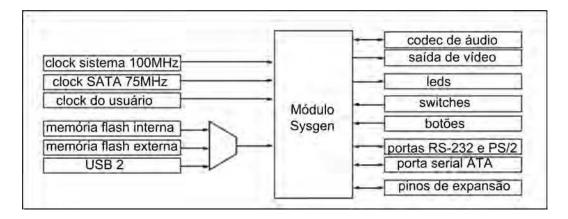

| 5.4  | Diagrama de bloco das interfaces de dados disponíveis                            | 58 |

| 5.5  | Detalhamento do módulo de interfaces de dados                                    | 59 |

| 5.6  | Detalhamento do módulo de comunicação                                            | 60 |

| 5.7  | Estrutura do protocolo MCP                                                       | 6  |

| 5.8  | Estrutura do pacote de monitoração definido no protocolo MCP                     | 62 |

| 5.9  | Estrutura do pacote de sinais definido no protocolo MCP                          | 62 |

| 5.10 | Pilha de protocolos utilizada para fazer a comunicação ente a plataforma REDLART |    |

|      | e o middleware                                                                   | 63 |

|      | Visão detalhada da plataforma REDLART                                            | 6. |

| 5.12 | Composição do componente VHDL de mais alta hierarquia utilizado para integrar    |    |

|      | netlists de componentes desenvolvidos em System Generator e códigos VHDL para    |    |

|      | controladores de dispositivos                                                    | 69 |

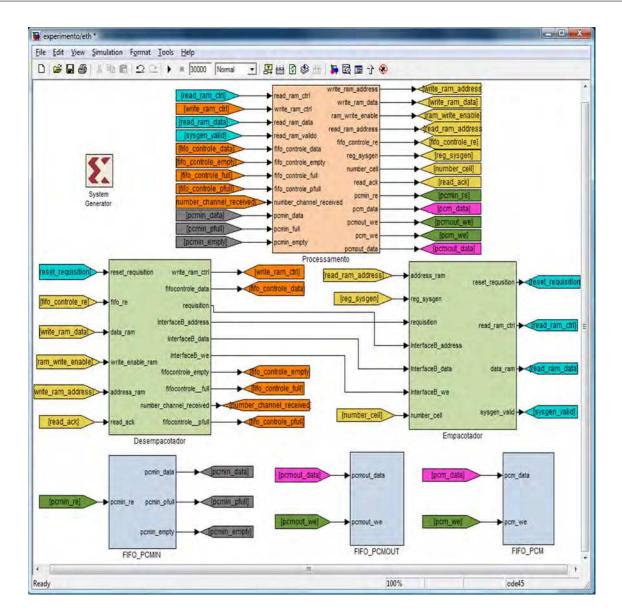

| 5.13 | Top-level da plataforma REDLART utilizando o System Generator                    | 70 |

| xiv | LISTA DE FIGURAS |

|-----|------------------|

|     |                  |

| 6.2<br>6.3 | Configuração sistêmica básica utilizada nas demonstrações | 74<br>75 |

|------------|-----------------------------------------------------------|----------|

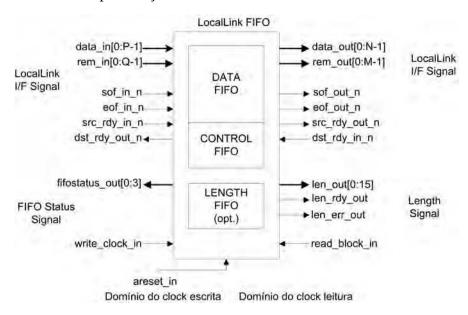

|            | Interface LocalLink FIFO                                  |          |

# Lista de Tabelas

| Principais fabricantes e fornecedores de FPGA |  |

|-----------------------------------------------|--|

| Especificação da Interface LocalLink FIFO     |  |

### Glossário

AD - Analógico Digital

Ajax - Asynchronous Java Script And XML

API - Application Programming Interface

ARP - Address Resolution Protocol

ASIC - Application Specific Integrated Circuits

CDMA- Code Division Multiple Access

CPLD- Complex Programmable Logic Device

DA - Digital Analógico

DAO - Data Access Object

DRAM- Dynamic Random Access Memory

EDA- Eletronic Design Automation

EDIF- Electronic Data Interchange Format

FIFO - First In First Out

FPGA- Field Programmable Gate Array

Gbps- Giga bit por segundo

GSM- Global System for Mobile Communication

HDL- Hardware Description Languages

HPIB - Hewlett-Packard Interface Bus

HQL - Hibernate Query Language

HTTP - HyperText Transfer Protocol

I/O - Input/Output

xviii GLOSSÁRIO

IC- Integrated Circuits

IEEE- Institute of Electrical and Electronics Engineers

IP - Internet Protocol

J2EE - Java 2 Enterprise Edition

JSF - JavaServer Faces

JSP - JavaServer Pages

KyaTera - Kya (rede em Tupi-Guarani) Tera (Terabits por segundo)

LUT - Lookup Table

Mbps - Mega bits por segundo

MCP - Monitoring and Control Protocol

MPEG- Moving Picture Experts Group

MVC - Model-View-Controller

NCF- Netlist Constraints File

NPI - Núcleo de propriedade intelectual

OOP - Object Oriented Programming

PDS - Processamento Digital de Sinais

PLD- Programmable Logic Device

PROM - Programmable Read-Only Memory

RECOLAB- Remote Control Laboratory

REDLART- Reconfigurable Digital Laboratory for Advanced Research and Teaching

RTL- Register Transfer Level

SATA - Serial Advanced Technology Attachment

SPLD- Simple Programmable Logic Device

SQL - Structured Query Language

SRAM- Static Random Access Memory

TCP - Transmission Control Protocol

GLOSSÁRIO xix

TDPR- Timing Driven Place and Route

TIDIA - Tecnologia da Informação no Desenvolvimento da Internet Avançada

UCF- User Constraints File

UDP - User Datagram Protocol

USB - Universal Serial Bus

VHSIC- Very High Speed Integrated Circuit

WCDMA- Wide-Band Code-Division Multiple Access

WiMAX- Worldwide Interoperability for Microwave Access

# **Trabalhos Publicados Pelo Autor**

1. V. R. Moreira, F. A. C. M. Cardoso, D. S. Arantes. "Plataforma reconfigurável para ensino e pesquisa em laboratório de sistemas digitais a distância". *Anais XIX Simpósio Brasileiro de Informática na Educação* (SBIE'2008), Sociedade Brasileira de Computação, Fortaleza, Ceará, Brasil, pg. 542-551, Novembro 2008.

# Capítulo 1

# Introdução

Este capítulo apresenta uma visão geral e os objetivos e motivações para o desenvolvimento de uma plataforma em *hardware* reconfigurável para o ensino e pesquisa em laboratórios de sistemas digitais a distância. Também são apresentados os trabalhos relacionados, as contribuições e a organização do presente trabalho.

#### 1.1 Visão Geral

A educação a distância é uma modalidade de ensino e aprendizado planejado, na qual alunos e professores se encontram em locais diferentes durante a fase de ensino. Por estarem em locais distintos, é necessário fazer uso de alguma tecnologia que proporcione um ambiente interativo de comunicação entre as partes. Nesse contexto, deve-se ter um cuidado especial no processo de criação de um curso a distância, levando-se em conta a instrução e comunicação por meio de várias tecnologias, bem como de disposições organizacionais e administrativas especiais [1].

Atualmente, os professores e as instituições de ensino passaram a incentivar com mais ênfase as atividades práticas extra-classe e extra-curricular de maneira planejada e orientada, com o uso de diversas tecnologias para facilitar a comunicação. As ferramentas de ensino a distância se aproveitaram das tecnologias disponíveis de gerenciamento de recursos, troca de mensagens, e-mails, vídeos, áudio, apresentação de *slides*, entre outras, para aplicar metodologias de ensino e disseminar o conhecimento para além das paredes da Escola e da Universidade. Isso possibilita a difusão da informação, o trabalho colaborativo e a sinergia entre professores e alunos, o que estimula o processo de ensino e promove novas metodologias de aprendizado.

No entanto, cursos que possuem a característica de conciliar o conhecimento teórico com as práticas de laboratório têm demonstrado limitações no que se refere à sua aplicação a distância na educação superior. Um dos grandes desafios na colaboração e no ensino a distância está na viabilização da prática de laboratórios. Apesar de já existir tecnologia disponível para isso, ainda não há uma solução integrada de *software* e *hardware* que emule o ambiente laboratorial e possibilite uma experiência real e de fato produtiva com o laboratório remoto. O laboratório remoto proporciona aos estudantes e usuários interação com experimentos reais via Internet ou rede dedicada [2].

2 Introdução

É importante observar que a experiência com a prática de laboratório deve familiarizar o aluno com o uso de equipamentos e de procedimentos laboratoriais, além de possibilitar o trabalho colaborativo e explorar conceitos teóricos. Esses elementos são importantes para viabilizar a formação de pessoal técnico capacitado para o mercado de trabalho.

Outro desafio que se apresenta reside na linha da pesquisa laboratorial colaborativa. O objetivo é compartilhar recursos e equipamentos entre instituições de ensino e pesquisa através de acesso remoto, com a possibilidade de ampliação da faixa de utilização desses equipamentos, otimizando o uso dos recursos e ampliando o número de alunos e pesquisadores envolvidos no processo.

Apesar de todo o recurso tecnológico existente, ainda não é trivial construir uma solução de acesso remoto laboratorial sobre uma infraestrutura presencial já existente. Entre os requisitos que devem ser atendidos, destacam-se a segurança e a eficiência do acesso remoto ao aparato experimental. É provável que a maior dificuldade esteja no fato de que cada laboratório seja um caso específico que demande soluções específicas, difíceis de serem reaplicadas diretamente a outros laboratórios.

O conceito de laboratório remoto surgiu da necessidade de disponibilizar laboratórios reais a qualquer momento, sem restrição de tempo e espaço. Este conceito exige que seja adotada uma nova abordagem de ensino, permitindo a troca de informações, interação entre alunos, professores e tutores e a flexibilização de local e de tempo de estudo. Idealmente, o objetivo é minimizar os problemas de logística, facilitar o compartilhamento de recursos e possibilitar o trabalho colaborativo. Deseja-se que o meio de desenvolvimento de experiências de laboratório remoto seja um ambiente de aprendizado no qual o aluno possa se envolver remotamente em atividades laboratoriais convencionais, com a mesma eficiência que teria se estivesse presente fisicamente no laboratório real.

Em linhas gerais, a solução padrão para possibilitar o acesso remoto a laboratórios reais consiste em utilizar ferramentas de automação. Essas ferramentas são utilizadas para fazer a aquisição, o controle e a monitoração de dados do experimento. A aquisição e a monitoração são realizadas a partir de equipamentos de teste ou de cartões de aquisição específicos. De forma semelhante, o controle do experimento é possibilitado a partir de equipamentos de teste ou de controladores projetados especificamente para o experimento.

Este trabalho propõe o desenvolvimento de uma plataforma em *hardware* reconfigurável para o ensino e pesquisa a distância denominada REDLART (*REconfigurable Digital Laboratory for Advanced Research and Teaching*). Essa proposta permite que alunos e pesquisadores programem os seus próprios experimentos e os integrem na plataforma, aproveitando assim todos os benefícios de controle, monitoração e distribuição do experimento que a arquitetura da plataforma oferece. Esta plataforma foi projetada para viabilizar o conceito da prática de laboratório a distância, possibilitando a colaboração na pesquisa prática e no ensino de laboratório a distância.

A plataforma é baseada em dispositivos FPGA (*Field Programmable Gate Array*) para desenvolvimento de circuitos digitais com aplicações em processamento digital de sinais, sistemas de comunicações digitais, controle, entre outras. A plataforma foi projetada e desenvolvida para a prototipagem

rápida de laboratórios remotos nas áreas de engenharia, telecomunicações, computação e afins. Além da plataforma de *hardware*, também foi concebida e implementada uma arquitetura de sistema, composta por um conjunto de *softwares* cliente-servidor, para viabilizar o acesso remoto, a gerência e a configuração do experimento. Nesse contexto, a partir de provas de conceito, mostra-se que é possível acessar experimentos remotos que podem ser utilizados na prática de ensino de laboratório a distância. Além disso, mostra-se também que é possível viabilizar o trabalho colaborativo e a sinergia entre laboratórios de pesquisa pelo controle e monitoração de experimentos distribuídos em redes de pacotes de alta velocidade.

#### 1.2 Trabalhos Relacionados

Alguns trabalhos correlatos motivaram de alguma maneira o desenvolvimento desta dissertação. Dentre eles podemos citar a disciplina Simulação, Co-simulação e Prototipagem de Sistemas de Comunicações Digitais (IE344B), a plataforma RECOLAB, o projeto Laboratório em Casa: Kits de *Hardware* para um Laboratório de Projeto Digital e o Laboratório Remoto Aplicado ao Ensino de Engenharia Eletrônica.

O projeto da plataforma REDLART surgiu da prática da disciplina de pós-graduação IE-344B [3] oferecida na Faculdade de Engenharia Elétrica e Computação da Universidade Estadual de Campinas. Essa disciplina aborda os paradigmas de implementação de sistemas de comunicação em *hardware* reconfigurável. Para testar os conhecimentos adquiridos, os alunos são convidados a desenvolver experimentos práticos de sistemas ou subsistemas de comunicações digitais e processamento digital de sinais utilizando FPGA. Durante o oferecimento dessa disciplina, constatou-se não ser necessário especificar uma arquitetura de *software* e de *hardware* que seja totalmente nova para cada novo projeto de experimento a ser desenvolvido. O mais racional neste caso é reutilizar uma infraestrutura básica que possa ser facilmente alterada através de um único componente funcional da arquitetura.

Uma proposta de laboratório remoto de controle denominada RECOLAB (*Remote Control Laboratory*) é apresentada. A plataforma RECOLAB visa proporcionar uma arquitetura geral para a execução remota de sistemas de controle automático de processo, referente à disciplina de engenharia de controle. O objetivo da plataforma é controlar os sistemas físicos de controle de processo em tempo real e de forma remota através da Internet. A plataforma foi desenvolvida utilizando as ferramentas Matlab e Simulink [4]. Através dessa plataforma é possível visualizar as informações associadas ao desempenho da simulação, assim como os gráficos, os dados e os resultados relevantes. Essa plataforma é empregada nos contextos de pesquisa colaborativa e ensino a distância [5]. Neste caso, o RECOLAB é uma plataforma de *software* que possibilita controlar e acessar processos mecânicos automatizados. Por outro lado, a REDLART é uma plataforma de *hardware* que possibilita desenvolver novos experimentos em uma plataforma já automatizada e integrada em um sistema para acesso remoto pela *Web*.

Uma inovadora metodologia de laboratório chamada Laboratório em Casa: Kits de *Hardware* para um Laboratório de Projeto Digital é apresentada para o curso introdutório de projeto digital. O

4 Introdução

conceito de laboratório em casa permite ao estudante executar experimentos reais em sua casa, utilizando kits de *hardware* especialmente desenvolvido para esta finalidade. Os estudantes analisam determinados problemas, desenvolvem as soluções que julgarem mais apropriadas e testam as soluções desenvolvidas nos kits de *hardware*, cada um composto principalmente por uma placa lógica programável [6]. Embora possibilite que o experimento seja executado fora do ambiente do laboratório (em casa), essa metodologia não emprega de fato o conceito de laboratório a distância, não possibilitando uma interação remota com um laboratório real.

Um laboratório remoto interativo para aplicações educacionais na área de engenharia eletrônica é apresentado. O laboratório utiliza o serviço *Web* da Internet como infraestrutura de comunicação, aplicativos para instrumentação baseada em computador e uma placa eletrônica para controle de experimentos reais. O laboratório foi desenvolvido utilizando a ferramenta de automação LabView [7]. O laboratório remoto possibilita ao usuário atuar nos experimentos acionando chaves, potenciômetros digitais, entre outros e obter dados com as medidas de instrumentos comerciais [8]. Neste caso, o laboratório remoto consiste em uma solução de automatização de experimentos e não no desenvolvimento do experimento propriamente dito. É importante destacar que a REDLART possibilita desenvolver novos experimentos a partir de circuitos digitais com foco no problema. Finalizado o desenvolvimento do experimento, o mesmo já está automatizado e pronto para ser integrado no sistema de acesso.

#### 1.3 Objetivos

A proposta desta dissertação consiste no estudo e desenvolvimento de uma plataforma experimental para a prática de laboratório a distância com aplicações em ensino e pesquisa colaborativa. Nesta linha de pesquisa, o objetivo é padronizar uma plataforma em *hardware* reconfigurável denominada REDLART, baseada em dispositivos semicondutores do tipo FPGA que incorpore soluções de controle e monitoração aos módulos de sua arquitetura. A plataforma proposta possibilita a criação de experimentos que possam ser acessados remotamente ou utilizados diretamente no laboratório.

A arquitetura da plataforma REDLART possibilita a criação de experimentos de sistemas digitais a partir de um conjunto de serviços de *software* que isolam completamente a complexidade do *hardware* utilizado. Esses serviços são modularizados e organizados em uma arquitetura genérica e flexível que permite que os experimentos sejam desenvolvidos com foco no problema que se deseja resolver. A plataforma REDLART abstrai os detalhes exaustivos da implementação dos componentes do *hardware*. Essa proposta permite que alunos e pesquisadores implementem os seus próprios experimentos e os integrem à plataforma, aproveitando assim todos os benefícios de controle, monitoração e distribuição do experimento em rede que a arquitetura da plataforma oferece. Distribuir um experimento em rede significa implementar partes do mesmo em locais remotos e integrá-los automaticamente através da comunicação por fluxos de dados de tempo real em redes de computadores. Esse conceito é explorado nesta dissertação para viabilizar a colaboração em pesquisa aplicada.

A plataforma foi projetada e desenvolvida para a prototipagem rápida de novos experimentos em sistemas digitais nas áreas de engenharia, telecomunicações, computação e afins. Exemplos de tais

sistemas são módulos de compressão/descompressão de áudio e vídeo (MPEG, H.264, MP3, etc.), sistemas de transmissão digital para TV Digital, redes sem fio (Wi-Fi, WiMAX, etc.), telefonia celular (CDMA, WCDMA, GSM, etc.), entre muitas outras aplicações. A partir de provas de conceito, mostra-se que é possível utilizar a plataforma proposta como uma ferramenta complementar de auxílio e apoio à prática de ensino de laboratório a distância e ao trabalho colaborativo.

#### 1.4 Motivações e Contribuições

O conceito de laboratório remoto permite que o usuário acesse e interaja com experimentos em tempo real. Os laboratórios remotos têm sido propostos, usualmente, como ferramentas de apoio e suporte ao ensino. Há um grande esforço da comunidade acadêmica nacional e internacional em disponibilizar laboratórios remotos em diversas áreas do conhecimento. Com o advento de novas infraestruturas de redes de alta velocidade para viabilizar o trabalho colaborativo, esses esforços têm se intensificado. Neste trabalho, além da aplicação em ensino, investiga-se também como viabilizar a colaboração na pesquisa aplicada. A solução empregada consiste em que partes do experimento possam ser desenvolvidas remotamente e então integradas, sem a necessidade de deslocamento. A proposta é que tais partes possam se comunicar através de fluxos de dados de tempo real em uma infraestrutura de rede de computadores como a Internet.

Em geral, as soluções apresentadas para prover a automatização dos experimentos são baseadas em *software* cliente-servidor ou em *software* para automação industrial. Existem também algumas propostas que são favoráveis à disponibilização do *hardware* necessário para que o aluno ou pesquisador desenvolva o experimento fora do ambiente da universidade. De modo geral, as propostas que estão relacionadas à aplicação da arquitetura de *software* cliente-servidor no contexto de laboratório remoto estão focadas no gerenciamento do usuário e nas metodologias que podem ser empregadas no aprendizado. Entretanto, possuem limitações no que diz respeito à prática de laboratório remoto. Essas limitações podem ser percebidas através da dificuldade de compartilhar recursos, fornecer o acesso ao experimento em tempo real, integrar novos experimentos ou equipamentos ou alterar os já existentes. Além disso, os experimentos que não são concebidos para serem compartilhados requerem automatização externa para que os usuários possam ter acesso.

A plataforma REDLART investe na questão do acesso em tempo real através da possibilidade de fluxo de dados de tempo real (*streaming*) para monitoração do experimento e para comunicação entre partes do experimento. A possibilidade de alterar um experimento na REDLART se deve à natureza reconfigurável dos dispositivos semicondutores utilizados, neste caso as FPGAs. A integração de novos experimentos é facilitada pela arquitetura sistêmica de *software-hardware-infraestrutura de rede* apresentada neste trabalho. O compartilhamento de recursos é abordado na plataforma não apenas pelo acesso remoto, mas também na possibilidade de reutilização de um experimento remoto para conceber um novo experimento também remoto. Tal abordagem é viabilizada pelo recurso de distribuição em rede do experimento.

De outra maneira, as soluções de automatização de experimentos que são desenvolvidas com base em ferramentas de *software* de automação possuem a característica de serem desenvolvidas através

6 Introdução

da prototipagem rápida. No entanto, como fator limitante, essas soluções necessitam utilizar *software* proprietário no terminal do usuário. Isso pode inviabilizar o custo ou a execução dessa operação. Além disso, as soluções disponíveis até o momento são apresentadas como laboratórios remotos estáticos. Após o experimento estar disponível pouca ou nenhuma alteração pode ser realizada na estrutura ou na arquitetura do experimento. Conforme citado anteriormente, a plataforma utiliza dispositivos semicondutores reconfiguráveis (FPGAs) que possibilitam que o experimento seja recompilado. A arquitetura do sistema, por sua vez, possibilita que o experimento seja recarregado a distância.

A situação ideal, que é abordada neste trabalho, é ter disponível uma plataforma de *hardware* integrada a uma plataforma em *software* que possibilite a experiência de execução de laboratório remoto em condições semelhantes às encontradas em um laboratório presencial. O usuário deverá ter a liberdade de criar ou alterar os experimentos e executá-los sem restrição de tempo ou espaço. Para que a experiência com o experimento remoto emule a experiência com o laboratório presencial é importante que a infraestrutura de rede no qual se encontra o experimento seja robusta e confiável para evitar atrasos e perdas de pacotes. Também é importante que a plataforma de *software* que compõe o laboratório remoto forneça um ambiente amigável para possibilitar a interação entre alunos, tutores e professores. O ambiente de laboratório remoto deve disponibilizar recursos para auxiliar o processo de execução do experimento, como material de apoio, correio eletrônico, grupos de discussão, mural, entre outros.

Um dos esforços deste trabalho foi desenvolver e implementar uma plataforma em *hardware* reconfigurável que possa fornecer suporte para a prática de laboratório a distância, seja no ensino ou na colaboração em pesquisa aplicada. A arquitetura da plataforma proposta possibilita que alunos e pesquisadores desenvolvam seus próprios experimentos e os integrem na plataforma. A plataforma REDLART foi concebida para possibilitar o controle, a monitoração e a distribuição do experimento em rede. Ela foi desenvolvida parte em ambiente Matlab/Simulink através de ferramenta de desenvolvimento de sistemas para FPGA da Xilinx, o *System Generator* [9], parte em linguagem padrão de descrição de *hardware* chamada HDL (*Hardware Description Languages*). É importante destacar que experimentos podem ser concebidos utilizando apenas o ambiente de desenvolvimento sistêmico do *System Generator*.

Como plataforma de *hardware* para desenvolvimento de experimentos, é natural que a REDLART tenha limitações no que se refere a realizar o gerenciamento de usuário, gerenciamento do experimento e fornecer ferramentas que auxiliam na metodologia de ensino, como *chats*, mural, fóruns entre outros. Tais características são típicas de plataformas de *software*. Neste contexto, também é apresentada uma proposta de arquitetura de sistema, utilizando uma plataforma de *software* baseada na arquitetura cliente-servidor, que possibilita o gerenciamento do usuário e do experimento e que fornece uma interface de usuário que seja acessível para a execução do experimento.

A plataforma REDLART possibilita a flexibilização de horários para a execução de experimentos. O laboratório remoto pode ficar disponível 24 horas por dia. Os alunos possuem liberdade para gerenciar o tempo dedicado à prática do experimento, decidir o que praticar e ter a liberdade para cometer erros e aprender com eles, o que estimula a pró-atividade. A plataforma pode motivar os alunos a realizarem experiências práticas laboratoriais a distância, fornecendo a oportunidade de tes-

tar o conhecimento conceitual obtido nas aulas teóricas convencionais. Isso pode aumentar a sinergia entre professores, alunos e tutores em benefício do próprio aluno.

#### 1.5 Organização da Dissertação

Neste capítulo, apresentou-se o tema da dissertação, uma visão geral do contexto no qual pode ser aplicado este trabalho e os trabalhos relacionados. Em seguida, foram descritos os objetivos, as motivações para o desenvolvimento da plataforma REDLART e a contribuição do presente trabalho. Posteriormente, será descrito sucintamente cada capítulo desta dissertação. Este trabalho está estruturado em sete capítulos e organizado da forma descrita a seguir.

O Capítulo 2 inicia apresentando os conceitos de ensino a distância e de laboratórios remotos. Durante o acesso a laboratório remoto, ao enviar um comando para o experimento, espera-se que tal comando tenha um reflexo praticamente imediato. Para que isso ocorra é importante que a rede de computadores, no qual o experimento está sendo executado, seja robusta. Por isso, são apresentadas algumas redes de alta velocidade que estão disponíveis para o ensino e pesquisa colaborativa. Alguns exemplos são apresentados para ilustrar o esforço da comunidade acadêmica nacional e internacional em viabilizar o desenvolvimento e implantação de laboratórios remotos. Para concluir, é apresentado o trabalho proposto no contexto educacional.

O trabalho proposto é baseado em uma plataforma em *hardware* reconfigurável que utiliza dispositivos semicondutores do tipo FPGA. Por isso, o Capítulo 3 inicia apresentando a história do surgimento das FPGAs, assim como os conceitos relacionados a esses dispositivos lógicos programáveis. Em seguida, são apresentadas as formas de desenvolvimento e implementação de um projeto que utiliza esse tipo de dispositivo. Por fim, são apresentados os principais fornecedores e desenvolvedores de ferramentas de *software* para a programação do *chip* FPGA.

O Capítulo 4 apresenta uma proposta de arquitetura de sistema para a aplicação de laboratório remoto. Essa arquitetura é composta por uma plataforma de *software* cliente-servidor que é responsável por fazer o gerenciamento de usuário, o gerenciamento de experimentos e a interação com a plataforma em *hardware* reconfigurável para a execução de experimento reais. A modelagem da arquitetura sistêmica, o desenvolvimento e a implementação da plataforma de *software* cliente-servidor é apresentada neste capítulo.

O Capítulo 5 apresenta a plataforma em *hardware* reconfigurável REDLART. Nesse capítulo são abordados os tópicos referente a especificação de requisitos, a modelagem, os cenários de utilização, o desenvolvimento e a implementação da plataforma REDLART. Para fornecer suporte à troca de informações entre a plataforma de *software* cliente-servidor e a plataforma REDLART foi desenvolvido um protocolo denominado protocolo MCP (*Monitoring and Control Protocol*). A especificação, a modelagem e a implementação desse protocolo também são apresentadas nesse capítulo.

O Capítulo 6 mostra três testes que foram realizados para validar a plataforma REDLART. A pro-

8 Introdução

posta foi desenvolver experimentos de processamento digital de sinais disponibilizados para acesso remoto e no local do laboratório. Tais experimentos foram desenvolvidos utilizando a plataforma REDLART e a plataforma de *software* cliente-servidor para verificar o comportamento dessas plataformas e testar as funcionalidades por elas fornecidas.

Finalmente, o Capítulo 7 mostra um breve resumo dos principais tópicos abordados neste trabalho, assim como as considerações finais e a conclusão. Também são apresentados alguns tópicos que não foram implementados neste trabalho, mas serão estudados e analisados em trabalhos futuros.

# Capítulo 2

### Prática de Laboratório a Distância

O objetivo deste capítulo é introduzir o conceito de laboratório a distância e sua aplicação no ensino e na pesquisa colaborativa. Também é feita uma introdução sobre a infraestrutura necessária para viabilizar a prática de laboratório remoto. Uma revisão sobre exemplos de laboratórios a distância e uma breve descrição de como o trabalho proposto pode ser inserido no contexto educacional são também apresentadas.

#### 2.1 Ensino a Distância

A educação a distância é a modalidade educacional na qual a mediação didático-pedagógica nos processos de ensino e aprendizagem ocorre com a utilização de meios e tecnologias de informação e comunicação, com estudantes e professores desenvolvendo atividades educacionais em lugares ou tempos diversos. Essa definição está presente no decreto 5.622, de 19.12.2005 que regulamenta o Art. 80 da Lei 9394/96 (Lei de Diretrizes e Bases da Educação Nacional).

Recentemente têm surgido diversas discussões políticas e pedagógicas de ação educativa no nível institucional e governamental sobre o tema educação a distância. A proposta de educação a distância surgiu como alternativa para suprir as necessidades de ensino que os métodos convencionais não contemplam. A educação a distância pode atender às necessidades de nivelar desigualdades entre grupos etários, proporcionar treinamento de emergência para públicos-alvo específicos, promover a redução de custos dos recursos educacionais, aumentar as oportunidades de aprendizado e estimular melhorias na qualidade das estruturas educacionais existentes.

Entretanto, cursos que possuem a característica de conciliar o conhecimento teórico com as práticas de laboratório, como engenharias e enfermagem, têm demonstrado limitações no que se refere à sua aplicação a distância na educação superior. Nas atividades laboratoriais convencionais, além da fundamentação teórica, são necessários materiais de leitura e a experiência de fazer (*hands-on*) proporcionada pelos laboratórios. Todos esses elementos em conjunto são vitais na formação de qualidade [10]. Desenvolver o ensino e a pesquisa em ambiente de laboratório fornece aos alunos a oportunidade de testar o conhecimento conceitual, trabalhar colaborativamente, interagir com equipamentos, aprender por tentativa e erro e fazer análises em dados experimentais [11].

A implantação de um curso a distância, com grade curricular mais voltada para a área técnica, pode ser viabilizada quando as disciplinas são realizadas de forma semi-presencial. Entretanto, a realização plena de tais cursos a distância também pode ser possível a partir do acesso remoto a laboratórios reais ou mesmo a partir do uso de laboratórios virtuais. Para alguns cursos, a possibilidade de acesso remoto é uma solução não apenas para viabilizar o ensino da prática a distância, mas também para contornar situações onde há falta de recursos, problemas logísticos, deficiência e risco ou condições perigosas de ambiente que tornam a prática de laboratório difícil [12]. Dessa necessidade de tornar os laboratórios disponíveis para que possam ser acessados a qualquer momento, desvinculando as restrições de tempo e espaço, junto com o desejo de minimizar os problemas logísticos e compartilhar recursos, surgiu o conceito de laboratório a distância.

#### 2.2 Laboratório a Distância

A consolidação do uso da Internet como ferramenta de compartilhamento de informações, o desenvolvimento de ferramentas modernas de controle e aquisição e a distribuição de dados via rede de computadores vêm impulsionando o controle e o acompanhamento de ensaios experimentais remotos [13].

Segundo Casini et al., os laboratórios a distância dividem-se em duas classes: laboratórios virtuais e laboratórios remotos. Os laboratórios virtuais são sistemas que podem executar simulações remotamente com a possibilidade de animação do sistema controlado. Os laboratórios remotos são laboratórios onde os estudantes podem interagir com experimentos reais via Internet. As operações remotas são realizadas através de uma interface *Web* que possibilita alterar os parâmetros de controle, executar o experimento, ver os resultados e obter os dados [2].

Os laboratórios virtuais são formados por um conjunto de modelagem, simulações e visualizações do que seria uma experiência desenvolvida em um laboratório real. De fato, esses laboratórios não existem no mundo físico, real, o que para alguns pesquisadores é motivo de relutar em classificar de laboratório no sentido estrito da palavra. No entanto, eles podem ser desenvolvidos para cumprir alguns requisitos de laboratório e fornecer uma visão geral de como seria a experiência prática desse laboratório. Os laboratórios virtuais podem ser utilizados no sentido de ser mais uma ferramenta para colaboração no ensino de aulas de laboratório e não como substituição da mesma.

O conceito de laboratório remoto une a característica de laboratório real e laboratório virtual, pois permite que usuários remotos acessem experimentos reais. Os laboratórios remotos admitem a execução do experimento passo a passo em tempo real, possibilitam a análise dos dados em equipamentos reais, permitem a flexibilização de horário e local para realizar os experimentos e estimulam o compartilhamento de equipamentos.

Ao prover acesso a experimentos remotos, pode-se atender à demanda existente de ensino do uso de equipamentos técnicos complexos. Além disso, pode-se também suprir a necessidade de se introduzirem práticas consideradas estado da arte na área de estudo e ainda preencher as expectativas do

que é esperado de um profissional qualificado. Ao prover acesso a experimentos envolvendo equipamentos de custo elevado e algumas vezes sensíveis, pode-se ampliar a faixa de utilização desses equipamentos, o que de certo modo proporciona uma economia de escala [14].

A aplicação de laboratório remoto é muito diversificada. Pode ser utilizado no desenvolvimento de um único experimento ou em um conjunto pré-determinado de experiências ou até mesmo para integrar laboratórios remotos de alcance mundial, formados pela conexão de várias instalações menores. Por outro lado, para permitir a integração de vários laboratórios remotos ou simplesmente para executar um único experimento de forma satisfatória, muitas vezes é necessário ter disponível uma boa infraestrutura de rede de computadores, com requisitos de desempenho, como largura de banda, atrasos e perdas de pacotes, suficientes para suportar as aplicações desejadas.

#### 2.3 Redes de Computadores

Durante o acesso a laboratórios remotos, dependendo do experimento, o usuário poderá ter acesso simultâneo a diversos sinais multimídia, tais como fluxo de dados de alta taxa em tempo real, monitoração de sensores, monitoração de equipamentos de teste (osciloscópio, analisador de espectro, etc.) e fluxos de áudio e vídeo. Além disso, o usuário poderá interagir com o experimento através de um aplicativo que enviará sinais de controle a partir de comandos de uma interface gráfica.

Ao enviar um comando para o experimento remoto, espera-se que tal comando tenha um reflexo praticamente imediato nos sinais de tempo real que estão sendo monitorados. Para atender a todos os requisitos mencionados, possibilitando que o usuário tenha uma dinâmica com o laboratório remoto semelhante à do laboratório presencial, é importante que a rede de computadores, na qual o experimento está sendo executado, ofereça largura de banda, confiabilidade, baixo atraso e baixa variação do atraso (*jitter*), de forma que minimize possíveis perdas e atrasos excessivos na transferência de dados.

Em Teitelman and Hanss [15] é definida largura de banda como a taxa de transmissão máxima que pode ser sustentada entre dois pontos. Atraso é o tempo necessário para um pacote percorrer a rede, medido no momento em que é transmitido pelo emissor até ser recebido pelo receptor. *Jitter* é a variação no atraso fim a fim. Quando é utilizado serviço de rede não orientado a conexão, um pacote enviado depois de outro pode chegar primeiro no receptor, caso o *jitter* tenha valores elevados. Isso pode levar a uma recuperação incorreta dos dados enviados.

A recuperação incorreta dos dados não ocorre caso seja utilizado um serviço orientado a conexão. Nesses serviços os pacotes fora de ordem são reordenados quando chegam ao destino. Porém, a operação de ordenar os pacotes pode inserir atrasos na comunicação, dificultando a comunicação em tempo real. Por esse motivo, a comunicação em tempo real geralmente é feita utilizando um serviço não orientado a conexão.

Algumas redes de alta velocidade estão disponíveis para o ensino e pesquisa. Entre elas pode-se citar a rede KyaTera, a rede Giga e a rede Internet2, descritas com mais detalhes a seguir.

#### 2.3.1 Projeto TIDIA-KyaTera

O programa TIDIA (Tecnologia da Informação no Desenvolvimento da Internet Avançada) foi lançado em São Paulo, Brasil, no segundo semestre de 2003. Esse programa é financiado pela FA-PESP (Fundação de Amparo a Pesquisa do Estado de São Paulo) e inclui três programas colaborativos: KyaTera, Aprendizado Eletrônico e Incubadora Virtual.

Os projetos Aprendizado Eletrônico e Incubadora Virtual são responsáveis pela pesquisa e desenvolvimento colaborativo no ensino a distância e na geração de conteúdos, respectivamente, suportados por redes de alta velocidade. O projeto KyaTera tem por objetivo a construção de uma infraestrutura de rede de altíssima velocidade que possa operar como uma plataforma de testes para a pesquisa e desenvolvimento de *WebLabs*, de protocolos avançados e de novas tecnologias em infraestrutura/hardware de rede e em software.

Dentro do programa TIDIA-KyaTera, vale destacar a pesquisa e o desenvolvimento de *WebLabs*. O conceito de *WebLab* foi definido para aqueles serviços *Web* cujo objetivo seja prover acesso remoto a experimentos de laboratórios reais a partir de páginas da *Web*. Esse serviço oferece acesso comum a dados geograficamente distribuídos. Permite que os usuários possam utilizar todos os recursos de um equipamento remoto através de um navegador, sem a necessidade de investir grandes recursos na aquisição de equipamentos laboratoriais [16].

A FAPESP define o projeto KyaTera como um projeto cooperativo que consiste de uma rede de fibras ópticas projetada para a pesquisa e desenvolvimento de conexões de alta velocidade, integrando laboratórios de pesquisa que focam o estudo, desenvolvimento e demonstração de tecnologia e aplicações da Internet avançada.

A rede KyaTera interliga todos os laboratórios participantes por meio de fibras ópticas que chegam diretamente aos laboratórios associados (*fiber-to-the-lab*). Através de um enlace de 1,2 Gbps entre São Paulo e Miami, a rede conecta os pesquisadores do estado de São Paulo com outras redes experimentais de pesquisa no mundo, incentivando colaborações internacionais. Internamente, no estado de São Paulo, essa rede está subdividida em duas: Rede Experimental e Rede Estável.

A rede estável oferece, para cada laboratório, uma taxa de transmissão mínima de 1 Gbps, através de um *backbone*<sup>1</sup> de 10 Gbps que interconecta os três grandes centros concentradores da rede, localizados nas cidades de São Paulo, Campinas e São Carlos. A rede experimental oferece uma quantidade variável de fibras apagadas, monomodo e/ou multimodo, de acordo com as necessidades do laboratório. A rede experimental obteve uma taxa de transmissão máxima de 320 Gbps em testes realizados em abril de 2005 [17].

#### 2.3.2 Projeto GIGA

O Projeto Giga consiste na implementação e no uso de uma rede óptica experimental voltada para o desenvolvimento de tecnologias de rede óptica, aplicações e serviços de telecomunicação associados

<sup>&</sup>lt;sup>1</sup> fornece um caminho para a troca de informações entre redes diferentes.

à tecnologia e banda larga. Também prevê a transferência de tecnologia a empresas brasileiras [18].

A rede do Projeto Giga foi implantada em maio de 2004, com 735 km de extensão e capacidade de 2,5 Gbps, podendo chegar até 10 Gbps. Abrange os municípios de Campinas, São Paulo, São José dos Campos, Cachoeira Paulista, Rio de Janeiro, Niterói e Petrópolis. A rede interconecta 17 universidades e centros de pesquisa do eixo Rio - São Paulo. O projeto Giga é coordenado pela RNP (Rede Nacional de Ensino e Pesquisa) em parceria com o CPqD (Centro de Pesquisa e Desenvolvimento em Telecomunicações). O convênio foi assinado com a FINEP (Financiadora de Estudos e Projetos), em dezembro de 2002.

#### 2.3.3 Rede Internet2

A rede Internet2 fornece aos Estados Unidos pesquisa e ensino em uma comunidade dinâmica, inovadora e com boa relação custo/benefício de uma rede óptica híbrida. A rede foi projetada para proporcionar a produção da próxima geração de serviço, assim como prover uma plataforma para o desenvolvimento de novas ideias e protocolos de rede. A rede Internet2 oferece infraestrutura de tecnologias de alta largura de banda. O *backbone* cruza o país com o apoio do Centro de Operações de Redes e Pesquisa Global e permite o fornecimento de 10 Gbps nos circuitos. A meta é oferecer 100 Mbps de conectividade de rede entre todos os *desktop* ligados à Internet2 [19].

É importante destacar que os laboratórios a distância, em princípio, devem ser projetados para serem acessados através da Internet atual. Como vimos anteriormente, algumas redes acadêmicas estão em processo de implantação e outras estão restritas a uma região de atuação. Por isso, é importante que no momento de projetar novos experimentos a distância os desenvolvedores pensem nas condições físicas da rede onde será executado o experimento. Redes congestionadas podem gerar perdas de pacote de dados e atrasos que prejudicam a interatividade com o experimento em tempo real.

#### 2.4 Exemplos de Laboratório Remoto

Esta seção apresenta uma breve revisão para ilustrar o esforço da comunidade acadêmica nacional e internacional em viabilizar o desenvolvimento e implantação de laboratórios remotos para fins educacionais e de pesquisa colaborativa.

Em 1999 foi apresentado um módulo de curso a distância com aplicação na caracterização de dispositivos semi-condutores. O curso foi desenvolvido seguindo o modelo Cliente/Servidor, constituído de um servidor local no qual estavam instalados equipamentos que se comunicavam por meio do padrão HPIB (*Hewlett-Packard Interface Bus*) [20]. O público alvo do curso eram alunos da graduação e da pós-graduação que acessavam os instrumentos por meio de um navegador *Web* [21].

Casini et al [2] apresentou em 2002 um laboratório de física a distância constituído de sistemas hidráulicos, motores de corrente contínua e de um levitador magnético desenvolvido no ambiente Matlab/Simulink (MathWorks). O material didático foi fornecido para ajudar no aprendizado. Ao término do experimento um conjunto de dados é apresentado. A interação com o aluno ocorre por

meio de um navegador Web.

A *Trinity College Dublin* em parceria com a *Open University in Milton Keynes*, Reino Unido, desenvolveu um sistema chamado PEARL (*Practical Experimentation by Acessible Remote Learning*) que consiste de uma arquitetura genérica para acessar experimentos remotos. O PEARL é utilizado em cursos de visão computacional para inspeção visual e processamento de imagem digital. O sistema tem como base a arquitetura Cliente/Servidor implementado utilizando as tecnologias Java Applet (Sun Microsystems) e Corba (*Common Object Request Broker Architecture*) [22].

No Massachussetts Institute of Technology (MIT) foi desenvolvida uma arquitetura para laboratório remoto denominado iLabs. O iLabs é formado por diversos laboratórios remotos desenvolvidos no MIT nas áreas de microeletrônica, engenharia química, cristalização de polímeros, engenharia estrutural e processamento de sinal. Esses laboratórios remotos são casos de estudo para entender os complexos requisitos de operar experimentos remotos de equipamentos de custo elevado e escalar. Eles são utilizados para grandes grupos de estudantes do MIT e de outras universidades no mundo [23].

Na Universidade de Genova, Itália, foi desenvolvido o ISILab. O ISILab é composto de um módulo de experimento virtual e um módulo de experimento remoto para o ensino de eletrônica. Uma característica do ISILab é apresentar uma estrutura escalar e modular, o que permite incorporar outras experiências através do desenvolvimento de placas dedicadas ao sistema desenvolvido [24].

Na Universidade Federal de São Carlos (UFSCAR) foram desenvolvidos diversos WebLabs, disponibilizados através da rede KyaTera, para auxiliar no ensino de graduação. Entre eles, pode-se destacar o WebLab de hidrólise enzimática da sacarose ( $C_{12}H_{22}O_{11}$ ), cujo objetivo é a execução remota de experimentos de inversão de sacarose em tempo real. Esse WebLab foi implementado através de uma solução híbrida que utiliza o Labview (National Instruments) e Java [25].

Na Universidade Estadual de Campinas (UNICAMP) encontram-se disponíveis, para acesso através da rede KyaTera, *WebLabs* na área de óptica, fotônica, engenharia química e bioquímica. Para integrar os *WebLabs*, pesquisadores do ComLab [26] desenvolveram um *framework* com base no paradigma Ajax (*Asynchronous Java Script And XML*). A proposta desse *framework* é uma arquitetura modular bastante flexível que permite adicionar, remover ou atualizar os *WebLabs* sem a necessidade de recompilar o núcleo da plataforma. Isso garante compartilhamento de recursos e facilidade de manutenção [27].

#### 2.5 O Trabalho Proposto no Contexto Educacional

Os laboratórios a distância apresentados, de maneira geral, são *softwares* desenvolvidos para que os usuários tenham acesso a equipamentos reais. Alguns desses laboratórios remotos possuem a característica de serem modulares, ou seja, permitem que sejam integrados novos laboratórios remotos aos já existentes. Outros possuem arquitetura pouco flexível, o que dificulta a inclusão de novas funcionalidades. No geral, o foco de desenvolvimento desses laboratórios a distância está no *software*

cliente-servidor. Depois do *software* finalizado, pouca ou nenhuma reconfiguração no programa pode ser realizada.

A proposta da plataforma REDLART é o desenvolvimento de um laboratório remoto utilizando uma plataforma em *hardware* reconfigurável (FPGA) que possibilite a interação entre os usuários e a plataforma em tempo real através do controle do experimento e da monitoração de fluxos de sinais multimídia. O foco dessa proposta é fornecer uma plataforma modular e que possua interface de usuário adequada para facilitar a comunicação homem-máquina. O objetivo é proporcionar um ambiente colaborativo que seja genérico e flexível para que o experimento possa ser executado remotamente e no local do laboratório.

A plataforma REDLART pode ser utilizada como uma ferramenta adicional para auxiliar no processo de ensino-aprendizagem de práticas de laboratório de engenharia. A intenção não é substituir as aulas práticas de laboratório convencionais, mas fornecer uma ferramenta que possibilite estender o conceito de laboratório real para que as experiências possam ser realizadas a distância.

Cursos da área de ciências exatas possuem a grade curricular fundamentada em ferramentas matemáticas tradicionais que são utilizadas para consolidar a formação acadêmica do aluno. Entre essas ferramentas matemáticas podem ser mencionadas, por exemplo, as transformadas de Laplace e de Fourier. Nos últimos anos, com o advento das tecnologias digitais, é imprescindível o uso de tais ferramentas matemáticas em algoritmos e sistemas com aplicações diversas. O ensino dessas ferramentas no contexto das tecnologias digitais é geralmente agrupado sob o nome de Processamento Digital de Sinais (PDS). Atualmente, PDS é um campo imenso e diversificado. Há milhares de profissionais que consideram processamento de sinais como sua área de especialidade e outras centenas de milhares cujo trabalho envolve essa área [28].

As mudanças curriculares nos cursos de ciências exatas, principalmente nos cursos da área de engenharia, que vêm ocorrendo nos últimos anos devido à introdução de PDS, trazem uma série de desafios. A existência de poucas obras em língua portuguesa e a ênfase dada a ferramentas matemáticas de tempo contínuo podem trazer dificuldades [29]. Esses problemas podem ser refletidos como falta de motivação por parte dos alunos.

De forma genérica, entende-se que a motivação é aquilo que move uma pessoa ou que a põe em ação ou a faz mudar o curso. Em sala de aula, os efeitos imediatos da motivação do aluno consistem em envolvê-lo ativamente nas tarefas pertinentes do processo de aprendizagem. Tal envolvimento consiste na aplicação de esforço no processo de aprender, com a persistência exigida por cada tarefa [30].

Uma forma eficiente de capturar a atenção do aluno e motivá-lo é demonstrando que o conhecimento adquirido nas aulas teóricas é efetivamente empregado em uma série de tecnologias presentes em seu dia a dia. Isso pode ser conseguido de forma prática através de aulas laboratoriais, uso de recursos computacionais e através de ferramentas de ensino a distância. É nesse cenário que a plataforma REDLART pode ser introduzida para auxiliar no processo de ensino de laboratório a distância.

Nas práticas de laboratório de sistemas digitais envolvem-se problemas reais referentes a processamento digital de sinais. Um conceito bastante difundido em PDS é a teoria dos filtros digitais. Esse conceito pode ser aplicado em vários problemas reais. Por exemplo, após uma aula sobre filtros digitais, suponha que a prática de laboratório envolva o problema descrito a seguir. O controle remoto por rádio-freqüência é comum em portas de garagens e alarmes de carros. O princípio de funcionamento consiste em transmitir ondas de rádio que correspondam a um comando binário referente ao botão que o usuário pressionou. Com base no conhecimento adquirido sobre filtros digitais pode ser requerido que se projete e teste um sistema para detecção do sinal de controle para acionamento do dispositivo alvo.

A plataforma REDLART pode ser utilizada para aplicar na prática os conceitos adquiridos sobre PDS, como no exemplo de filtros digitais citado acima. A plataforma é flexível o suficiente para permitir que novos experimentos possam ser incorporados a ela, abstraindo-se os detalhes de implementação que não são o foco do problema. Para a resolução de um problema como o citado acima, podem-se desenvolver experimentos que utilizem, por exemplo, filtros digitais diversos.

Após a integração do experimento na plataforma, os alunos podem ter acesso a dados reais, executados em tempo real na plataforma de *hardware* REDLART para aferir medidas, analisar os resultados e executar o experimento sem restrição de tempo e espaço físico. Esse é apenas um cenário no qual a plataforma REDLART pode ser utilizada. No Capítulo 6 é descrito outro cenário. Além disso, cenários diferentes poderão ser explorados posteriormente.

# Capítulo 3

# Programação de Dispositivos FPGA

Há diversos tipos de circuitos integrados digitais. No entanto, o foco deste trabalho encontra-se nos dispositivos lógicos programáveis, especificamente nas FPGAs. Por esse motivo, este capítulo apresenta uma visão geral dos *chips* FPGAs assim como as formas de desenvolvimento e implementação dos mesmos.

#### 3.1 Introdução a FPGA

Antes do advento das FPGAs as tecnologias disponíveis eram os Transistores, Circuitos Integrados (Integrated Circuits - IC), SRAMs (Static Random Access Memory) e DRAMs (Dynamic Random Access Memory), Microprocessadores, SPLDs (Simple Programmable Logic Device), CPLDs (Complex Programmable Logic Device) e ASICs (Application Specific Integrated Circuits). Para entender os motivos que levaram ao surgimento das FPGAs é importante considerá-las no contexto dessas tecnologias relacionadas. A Figura 3.1 mostra as datas aproximadas da cronologia das tecnologias relacionadas com FPGA [31]. A parte em cinza indica que embora a tecnologia estivesse disponível, no primeiro momento, não foi recebida com entusiasmo por parte dos profissionais que trabalhavam nesse setor [31]. Por exemplo, embora a primeira FPGA tenha surgido no início de 1984 os projetistas de hardware e os desenvolvedores não se motivaram a utilizar essa tecnologia de fato até o início de 1990.

Em 1947 pesquisadores da Bell Lab's conseguiram desenvolver o primeiro dispositivo transistor [32]. O transistor é um dispositivo semicondutor que controla ou amplifica sinais elétricos. Este dispositivo possui função semelhante às válvulas, de controlar o fluxo de corrente, mas com a vantagem de ter o tamanho reduzido em relação às mesmas. Os transistores não geram atrasos por aquecimento e podem funcionar como comutadores (chaves). Essa invenção representou um salto tecnológico na história. Isso substituiu definitivamente as válvulas e tornou possível reduzir consideravelmente o tamanho dos produtos eletrônicos [32].

Após a invenção dos transistores, as implementações de circuitos digitais tornavam-se cada vez mais complexas. O número de transistores empregados nos circuitos digitais aumentava rapidamente. Portanto, surgiu a necessidade de reduzir a eletrônica envolvida e desta forma surgiu o circuito in-

Fig. 3.1: Cronologia das tecnologias relacionadas com FPGA.

tegrado (CI). A cada novo CI lançado a complexidade dos projetos aumentava exponencialmente, possibilitando o desenvolvimento de aplicações que até então eram difíceis de serem implementadas [32].

No final de 1960 e início de 1970 surgiram novos desenvolvimentos na área de circuitos integrados digitais o que impulsionou o processo de expansão dos mesmos. Em 1970 foi anunciada a primeira DRAM. A memória RAM dinâmica é formada por pares de transistores e capacitores que consomem pouco espaço no silício. O atributo dinâmico é utilizado porque o capacitor perde a informação ao longo do tempo, de modo que cada célula da DRAM deve ser periodicamente atualizada para manter a informação armazenada. A memória SRAM difere da memória DRAM porque uma vez que a informação foi carregada para dentro da célula SRAM os dados permanecerão inalterados, a menos que seja especificamente alterado ou a energia elétrica seja removida do sistema.

Em 1971 surgiu o projeto de um microprocessador que incorporava as funções de uma unidade de processamento central em um único circuito integrado. Os microprocessadores substituíram milhões de transistores o que diminuiu o tamanho dos dispositivos. Eles são utilizados principalmente para processamentos complexos e dentre algumas aplicações estão presentes nos computadores e aparelhos eletrônicos. As tecnologias SRAM e de microprocessadores são largamente utilizadas na maioria das FPGAs.

Os primeiros circuitos integrados programáveis foram genericamente chamados de dispositivos lógicos programáveis (*Programmable Logic Devices* - PLDs). O PLD é um circuito integrado cuja arquitetura interna é determinada pelo fabricante, mas que é projetado de tal forma que pode ser configurado ou programado em campo, no local de trabalho do desenvolvedor, para executar diversas

funções. O termo PLD pode ser referenciado em duas subcategorias: os SPLDs (Simple Programmable Logic Devices) e os CPLDs (Complex Programmable Logic Devices). Os SPLDs referem-se aos primeiros PLDs fabricados, os quais originalmente continham um número modesto de unidades lógicas equivalentes e eram bastante simples. Os CPLDs são dispositivos que contêm uma determinada quantidade de funções SPLD que compartilham uma matriz de interconexões programáveis. Se comparado às FPGAs, esses dispositivos contêm um número relativamente limitado de unidades lógicas que podem ser utilizadas para implementar funções menores e menos complexas.

Por volta do início de 1980, houve uma lacuna no processo de expansão dos circuitos integrados. De um lado havia dispositivos programáveis como os PLDs que são criados de maneira que podem ser programados para executar diversas funções. Os dispositivos PLDs eram altamente configuráveis e demandavam pouco tempo desde a fase de planejamento até a fase de implementação. No entanto, os PLDs não forneciam suporte a funcionalidades complexas. Do outro lado estavam disponíveis os ASICs. Os ASICs são circuitos integrados personalizado projetados para uma aplicação específica. Esses dispositivos podem conter centenas de milhares de unidades lógicas e podem ser utilizados para a construção de funções aritméticas de funcionalidades extremamente complexas. Em geral, o ASIC é concebido e construído para fim empresarial. Além disso, uma vez que o projeto foi implementado em um ASIC ele é permanentemente gravado no silício. Portanto, as opções disponíveis para a construção de circuitos integrados eram ou a utilização de PLDs, altamente configuráveis, mas sem suporte a funcionalidades complexas ou a utilização de ASICs para aplicações específicas.

Para preencher essa lacuna no processo de expansão dos circuitos integrados, em meados de 1985, uma companhia chamada Xilinx introduziu a ideia de combinar o controle de usuário e o *time-to-market*<sup>1</sup> do PLD com a densidade e os benefícios de arranjo de unidades lógicas. Isso originou uma nova classe de circuito integrado chamado de FPGA. As FPGAs ocupam o meio-termo entre PLDs e ASICs, porque suas funcionalidades podem ser personalizadas na "programação em campo"como acontece com os PLDs, além disso, podem conter milhares de unidades lógicas utilizadas para a execução de funcionalidades extremamente grandes e complexas que anteriormente só poderiam ser realizadas utilizando ASIC. O custo de um projeto em FPGA é menor do que o de um projeto em ASIC (apesar de componentes ASICs serem mais barato quando utilizados na produção de grande escala). Ao mesmo tempo, implementar mudanças no projeto é mais fácil em FPGA e o tempo necessário para a especificação, desenvolvimento e implementação até a finalização do projeto é menor.

As FPGAs são circuitos integrados digitais que contêm blocos configuráveis de lógica com interconexões programáveis entre eles. Os projetistas podem configurar esses dispositivos de maneira que executem diferentes tarefas. A parte do nome FPGA referenciada como "Field Programmable" menciona o fato de que sua programação acontece "em campo", ou seja, no local do usuário, diferentemente de dispositivos cuja programação é feita apenas pelo fabricante. Isso significa que as FPGAs podem tanto ser configuradas no laboratório como podem ser modificadas depois de já estarem em seus locais definitivos de operação [31]. O termo gate array está relacionado ao conceito de arranjo de unidade lógica. As unidades lógicas são componentes padrão formados por transistores que podem ser configurados independentemente e interconectados a partir de uma matriz de trilhas

<sup>&</sup>lt;sup>1</sup>é o tempo de projeto e concepção de um produto até a disposição desse produto no mercado.

condutoras e switches programáveis [33].

Durante o início da década de 1990, o tamanho e a sofisticação das FPGAs começaram a aumentar. O grande mercado eram os consumidores das áreas de telecomunicação e redes, as quais envolviam o processamento de grandes blocos de dados. Mais tarde, em direção ao final da década de 1990, a utilização de FPGA em indústria automotiva e em aplicações industriais passou a ter um grande crescimento. No início do ano 2000, já se encontrava disponível FPGA de alto desempenho contendo milhares de unidades lógicas. Algumas das características desses dispositivos são a possibilidade de incorporar os núcleos de microprocessadores embarcados, além dos pinos de alta velocidade para serem usados como entradas e saídas [34] [31]. O resultado é que atualmente as FPGAs podem ser utilizadas para implementar praticamente qualquer circuito digital, incluindo *software* e dispositivos de comunicação como rádio, radar, processamento de imagem e outras aplicações de processamento digital de sinais.

O tipo de FPGA dominante tem base na tecnologia SRAM (*Static Random Access Memory*) e pode ser reprogramada quantas vezes for necessário [33]. Isso significa que, se as células lógicas SRAM forem programadas de maneira apropriada, cada bloco lógico do dispositivo pode ser configurado para executar uma função diferente. Uma FPGA que utiliza células SRAM é reprogramada toda vez que é ligada, pois o dispositivo FPGA é composto de uma memória volátil. Por essa razão, é necessário ter uma memória PROM (*Programmable Read-Only Memory*) em cada FPGA que utiliza a tecnologia SRAM.

Os primeiros dispositivos FPGA empregaram o conceito de bloco lógico programável. Os blocos lógicos programáveis podem ser vistos como componentes padrão que podem ser configurados independentemente. Atualmente, o bloco lógico programável é composto de vários recursos que podem implementar diversas funções aritméticas e lógicas. Esses recursos variam de acordo com o fabricante da FPGA, mas de maneira geral incluem LUTs (*Lookup Table*), registradores que podem atuar como um *flip-flops* ou como um *latch*, memórias, multiplicadores e acumuladores programáveis, gerenciamento de *clock* digital e lógica de transporte (*carry*) dedicado. Cada FPGA é formada por um grande número de blocos lógicos programáveis interconectados através de uma matriz de trilhas condutoras e *switches* programáveis. Para especificar a funcionalidade de cada bloco lógico programável, assim como seletivamente fechar os *switches* da matriz de interconexão, é necessário gerar um arquivo binário que indique as configurações da FPGA. Esse arquivo binário é gerado a partir de ferramentas de *software* seguindo um determinado fluxo de projeto. A hierarquia de *switches* programáveis em conjunto com os blocos lógicos programáveis permite que o sistema possa ser interconectado de acordo com a necessidade do projetista. A Figura 3.2 mostra a arquitetura geral de roteamento de uma FPGA.

Os blocos lógicos programáveis são conectados à matriz de trilhas condutoras através de circuitos responsáveis pelo interfaceamento das entradas e saídas. Estes circuitos são *buffers* que funcionam como pinos de entrada e saída bidirecionais de dados e de sinais. As trilhas são formadas por sequência de um ou mais segmentos de ligação em série. Os blocos de conexão permitem a conectividade das entradas e saídas de um bloco lógico com os segmentos de trilhas nos canais. Quando um canal é formado por um grupo de duas ou mais trilhas paralelas é chamado de canal de roteamento. Os *swit*-

Fig. 3.2: Visão geral da arquitetura de roteamento de uma FPGA.

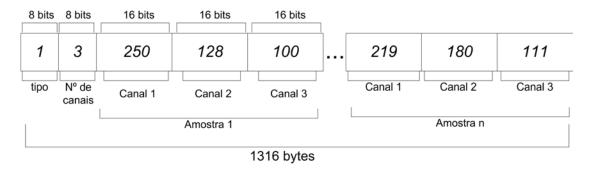

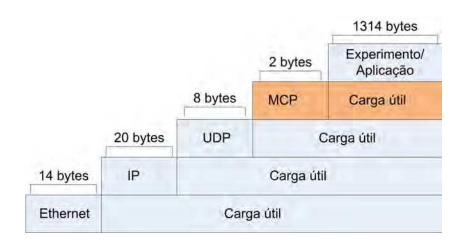

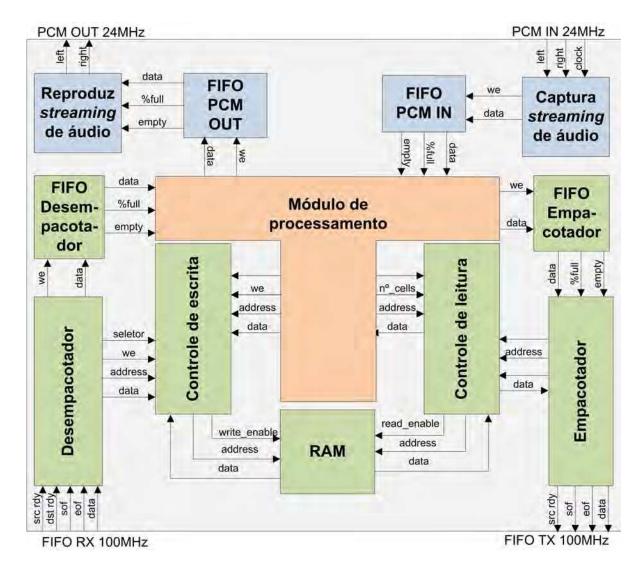

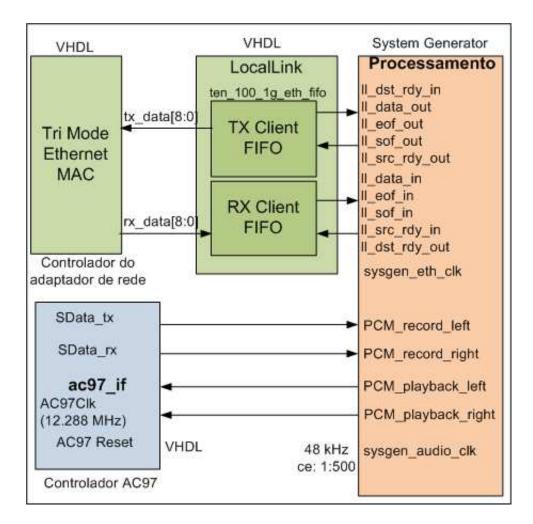

ches programáveis são organizados como trilhas de roteamento horizontal e vertical entre as linhas e colunas dos blocos lógicos programáveis. Em algumas arquiteturas tem-se que o bloco de conexão e os *switches* são encapsulados em uma mesma estrutura e em outras arquiteturas eles aparecem separados. Para que a interconexão aconteça de forma mais rápida, podem ser criados caminhos de interconexões globais os quais permitem transportar sinais através da FPGA, sem a necessidade de passar por múltiplos elementos de roteamento. Portanto, o arranjo de blocos lógicos programáveis e a matriz de interconexão formam a estrutura básica da FPGA para especificação de circuitos integrados complexos.